A.2.1.2.1. Reviewing Component Interfaces

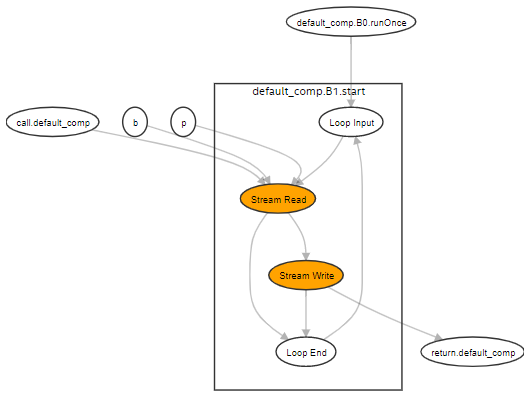

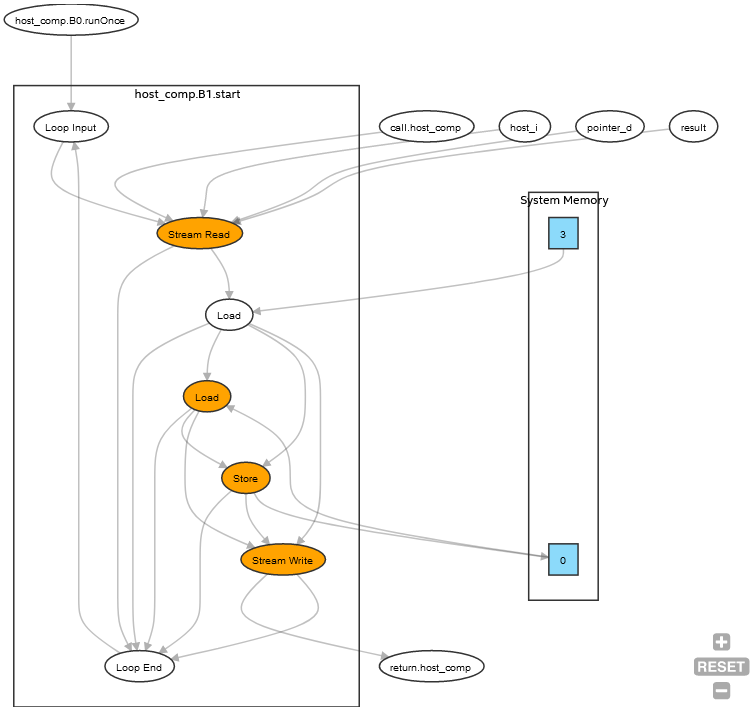

The Function View of the System Viewer shows a visual representation of the interfaces in your component.

Some parameters in your component can be marked as being stable. A parameter can be marked as stable if its argument does not change while your component executes, but the argument might change between component executions. In the Function View, a stable argument does not have any edge connection.

Default (Conduit) Interfaces

#include "HLS/hls.h"

struct coordinate_t {

int x;

int y;

};

component int default_comp(int b, coordinate_t p) {

return b + p.x;

}

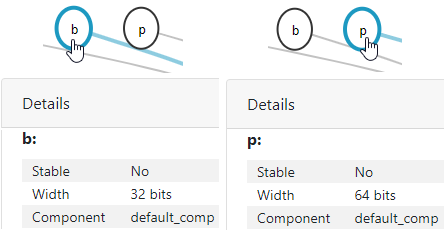

For each default interface argument node, you can view details about the node in the Details pane when you hover over the node:

Avalon® MM Host Interfaces

Pointer arguments, pass-by-reference arguments, ihc::mm_host<> argument, and global variables all correspond to addresses to memory outside of your component. They result in at least one Avalon® MM Host interface in your component.

#include "HLS/hls.h"

component int

host_comp(int *pointer_d,

ihc::mm_host<int, ihc::aspace<3>, ihc::awidth<4>, ihc::dwidth<32>,

ihc::latency<1>, ihc::align<4>> &host_i,

int &result) {

result = pointer_d[0] + host_i[0];

return result;

}

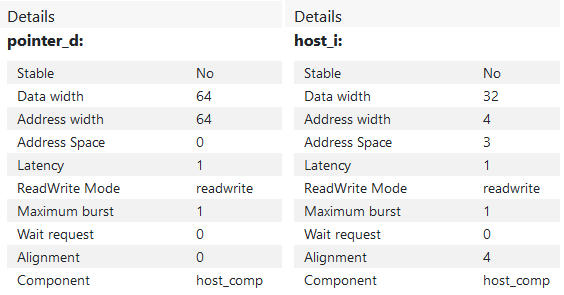

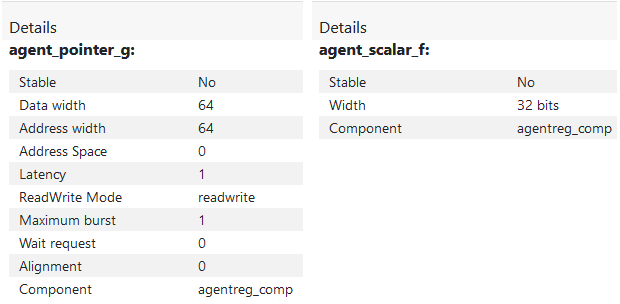

- Stable

- Describes whether the interface argument is stable. That is, whether the hls_stable_argument attribute was applied.

- Data width

- The width of the memory-mapped data bus in bits.

- Address width

- The width of the memory-mapped address bus in bits.

- Latency

- The guaranteed latency from when the read command exits the component to when the external memory returns valid read data. The latency is measured in clock cycles.

- Maximum burst

- The maximum number of data transfers that can associate with a read or write transaction. For fixed latency interfaces, this value is set to 1.

- Alignment

- The byte alignment of the base pointer address. The Intel® HLS Compiler uses this information to determine the amount of coalescing that is possible for loads and stores to this pointer.

- Memory address space number

- The memory address space number for Avalon® MM Host interface.

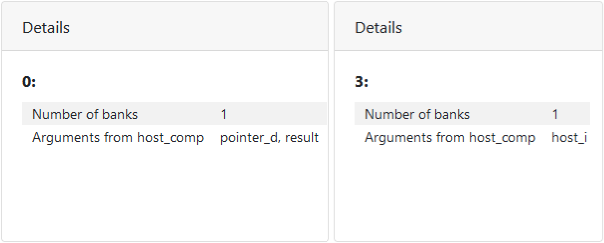

- Number of banks

- The number of memory banks contained in the memory.

- Argument Name:

- The names of arguments that access the Avalon® MM Host interface.

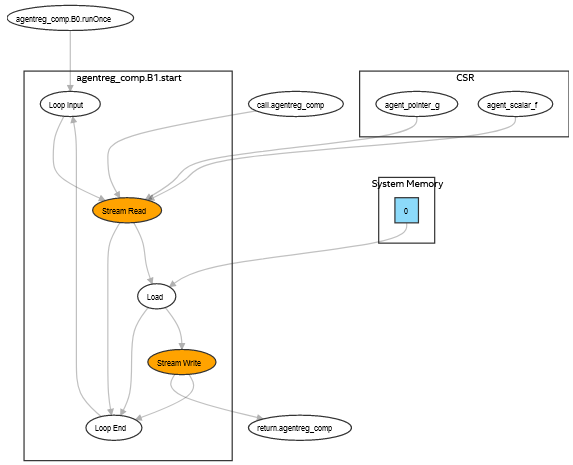

Avalon® MM Agent Register Interfaces

#include "HLS/hls.h"

component int agentreg_comp(

int hls_avalon_agent_register_argument agent_scalar_f,

int* hls_avalon_agent_register_argument agent_pointer_g

) {

return agent_scalar_f + *agent_pointer_g;

}

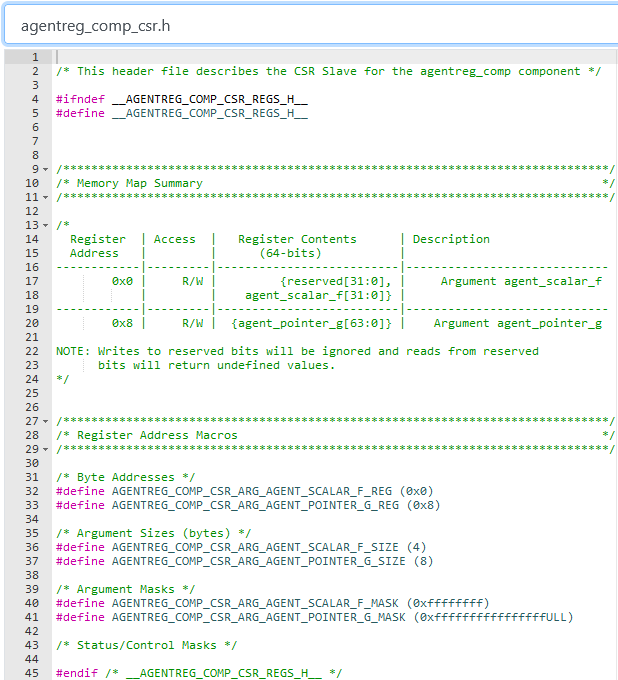

The resulting memory map is described in the automatically generated header file <component_name>_csr.h. This header file is available in the menu in the source code pane. Clicking on the CSR container node in the Function View of the System Viewer also opens up the header file:

#include "HLS/hls.h"

hls_avalon_agent_component

component int agentreg_comp(

int hls_avalon_agent_register_argument agent_scalar_f,

int* hls_avalon_agent_register_argument agent_pointer_g

) {

return agent_scalar_f + *agent_pointer_g;

}Avalon® MM Agent Memory Interfaces

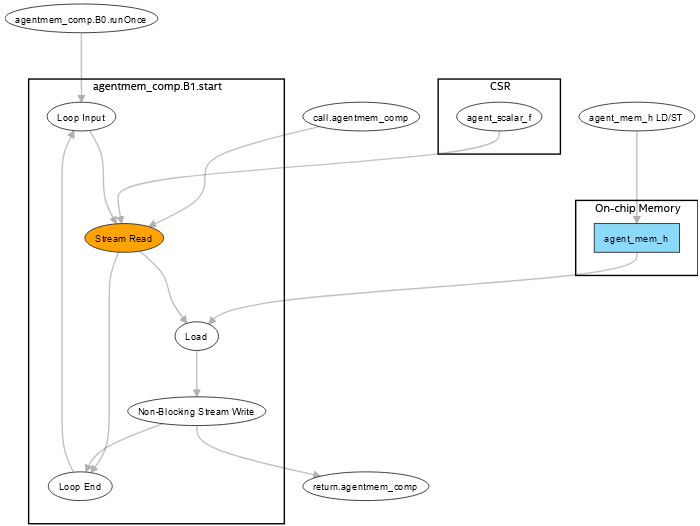

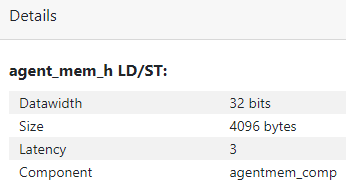

#include "HLS/hls.h"

hls_avalon_agent_component

component int agentmem_comp(

hls_avalon_agent_memory_argument(4096) int* agent_mem_h,

int hls_stable_argument index,

int hls_avalon_agent_register_argument agent_scalar_f

) {

return agent_mem_h[index] * agent_scalar_f;

}

Avalon® Streaming Interfaces

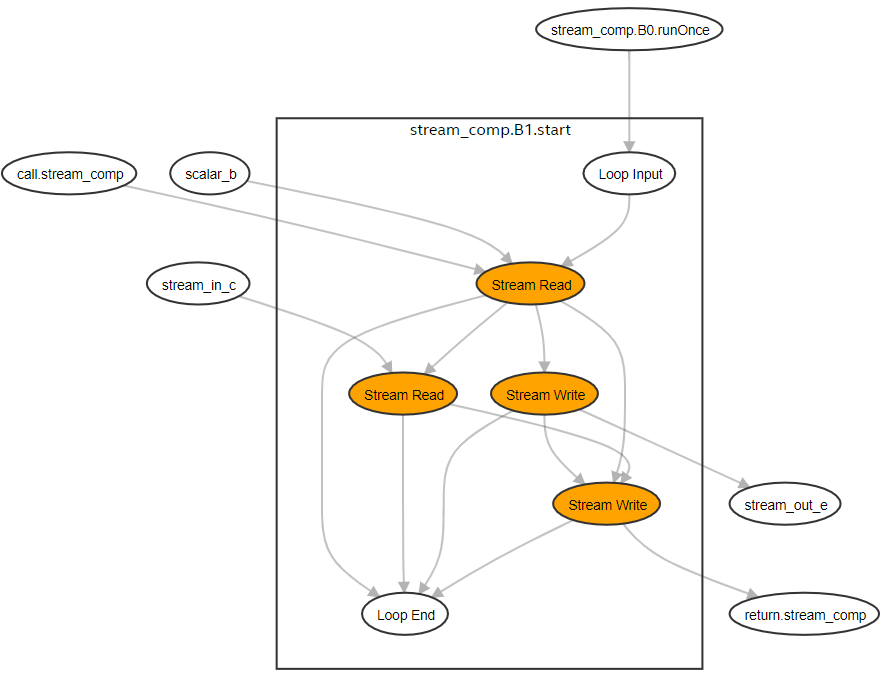

#include "HLS/hls.h"

component int stream_comp(

ihc::stream_in<int> &stream_in_c,

ihc::stream_out<int> &stream_out_e,

int scalar_b

) {

stream_out_e.write(scalar_b + 1);

return stream_in_c.read() + scalar_b * 2;

}

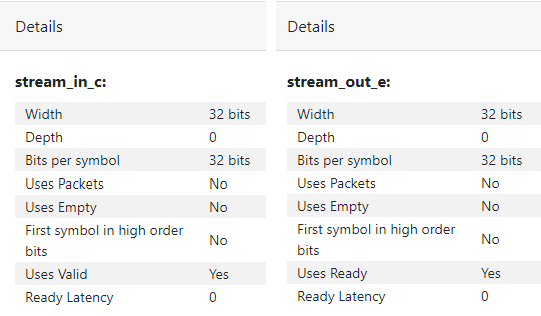

- Width

- The width of the data signal in bits.

- Depth

-

The depth of the stream in words

The word size of the stream is the size of the stream datatype.

- Bits per symbol

- Describes how the data is broken into symbols on the data bus.

- Uses Packets

- Indicates whether the interface exposes the startofpacket and endofpacket sideband signals on the stream interfaces. The signals can be access by the packet-based reads and writes.

- Uses Valid

- (stream_in) Indicates whether a valid signal is present on the stream interface. When Yes, the upstream source must provide valid data on every cycle that ready is asserted.

- Uses Ready

- (stream_out) Indicates whether a ready signal is present on the stream interface. When Yes, the downstream sink must be able to accept data on every cycle that valid is asserted.