F-Tile Serial Lite IV Intel® FPGA IP Design Example User Guide

ID

683287

Date

8/14/2025

Public

1. About the F-Tile Serial Lite IV Intel® FPGA IP Design Example User Guide

2. Quick Start Guide

3. Detailed Description for F-Tile Serial Lite IV Design Example

4. F-Tile Serial Lite IV Intel® FPGA IP Design Example User Guide Archives

5. Document Revision History for the F-Tile Serial Lite IV Intel® FPGA IP Design Example User Guide

3.8. Analog Parameters

Through this tab, you can configure FHT and FGT PMAs settings. Altera recommends the following FHT and FGT PMAs settings for Agilex™ 7 I-Series Transceiver-SoC development kit:

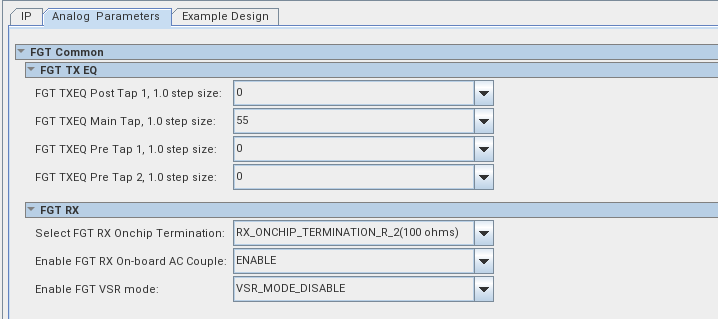

Figure 19. FHT PMA SettingsThe recommended FHT PMA settings are shown below.

- FHT TX

- Enable FHT TX P&N Invert: Enabled

- Select FHT TX Termination: TXTERM_OFFSET_M1(96.8 Ohms)

- FHT RX

- Enable FHT RX P&N Invert: Enabled

- Select FHT RX Termination: RXTERM_OFFSET_P0(90 Ohms)

- FHT PLL

- Select FHT external AC Cap: EXTERNAL_AC_CAP_DISABLE

- FHT TX EQ

- Post-Cursor 2, 0.25 step size: -2.0

- Post-Cursor 1, 0.5 step size: -2.0

- Main-Cursor, 0.5 step size: 18.0

- Pre-Cursor 1, 0.5 step size: -4.0

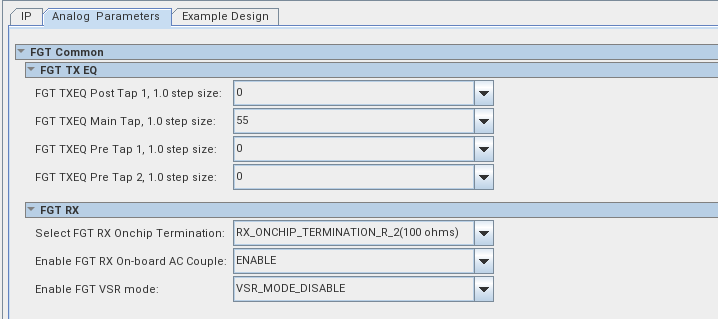

Figure 20. FGT PMA SettingsThe recommended FGT PMA settings are shown below.

Note: When the design configuration is PAM4 modulation with more than 8 lanes, set the FGT TXEQ Pre Tap 1 as 5.

Note: Depending on the data rate, use the following setting:

When the NRZ data rate is less than 7 Gbps, Altera recommends to set the following parameters to use 0s.

- For NRZ data rate of more than or equal to 23 Gbps, select VSR_MODE_LOW_LOSS.

- For NRZ data rate of less than 23 Gbps, select VSR_MODE_DISABLE.

- For PAM4 with number of lanes less than or equal to 8, select VSR_MODE_LOW_LOSS.

- For PAM4 with number of lanes more than 8, select VSR_MODE_HIGH_LOSS.

- RXEQ VGA Gain

- RXEQ High Frequency Boost

- RXEQ DFE Data Tap1

Figure 21. RXEQ Settings