Quartus® Prime Pro Edition User Guide: Design Constraints

ID

683143

Date

7/07/2025

Public

1.1.2.1. Specify Instance-Specific Constraints in Assignment Editor

1.1.2.2. Specify NoC Constraints in NoC Assignment Editor

1.1.2.3. Specify Dual Simplex Assignments in DS Assignment Editor

1.1.2.4. Specify I/O Constraints in Pin Planner

1.1.2.5. Plan Interface Constraints in Interface Planner and Tile Interface Planner

1.1.2.6. Adjust Constraints with the Chip Planner

1.1.2.7. Constraining Designs with the Design Partition Planner

3.2.1. Assigning to Exclusive Pin Groups

3.2.2. Assigning Slew Rate and Drive Strength

3.2.3. Assigning I/O Banks

3.2.4. Changing Pin Planner Highlight Colors

3.2.5. Showing I/O Lanes

3.2.6. Assigning Differential Pins

3.2.7. Entering Pin Assignments with Tcl Commands

3.2.8. Entering Pin Assignments in HDL Code

1.1.4. Specifying Timing Constraints

You must specify timing constraints that describe the clock frequency requirements, timing exceptions, and I/O timing requirements of your design for comparison against actual conditions observed during timing analysis. You define timing constraints in one or more Synopsys* Design Constraints (.sdc) files that you add to the project.

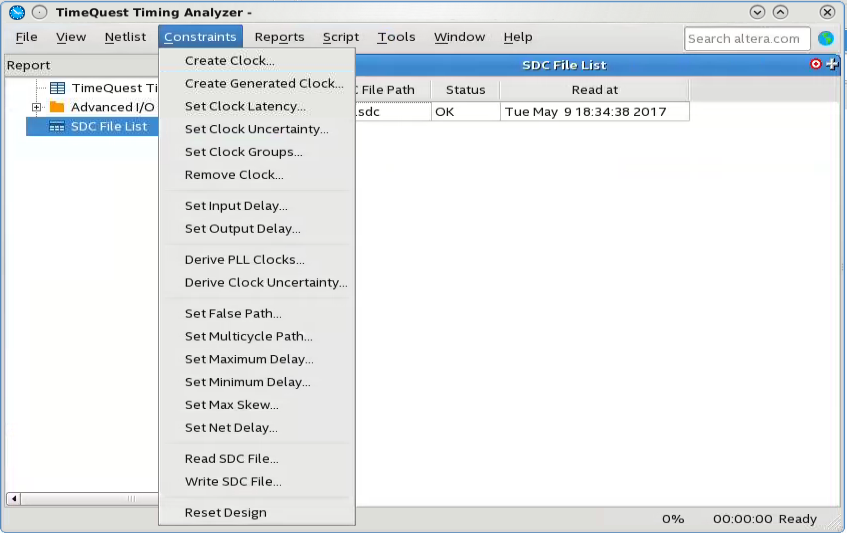

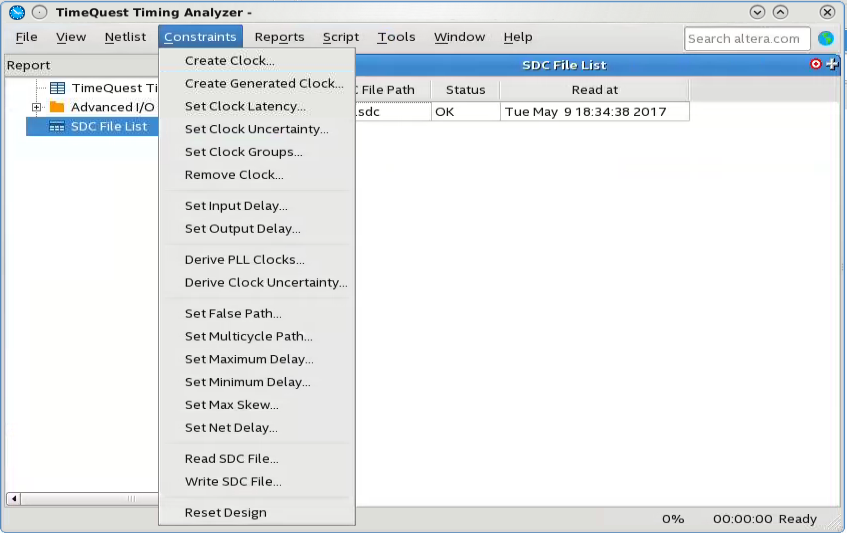

You can specify timing constraints in the Timing Analyzer GUI, which automatically generates an .sdc based on your inputs. Click the Constraints menu in the Timing Analyzer to specify timing constraints that you can apply to your project.

Alternatively, you can create an initial .sdc with provided .sdc file templates, or manually in any text editor and then add the .sdc to the project.

In addition, generation of IP or Platform Designer systems may also automatically generate and add to your project .sdc constraints.

Figure 13. Constraint menu in Timing Analyzer

When you specify a constraint in the GUI, the dialog box displays the equivalent SDC command syntax.

Create Clock Dialog Box

Individual timing assignments override project-wide requirements.

- To avoid reporting incorrect or irrelevant timing violations, you can assign timing exceptions to nodes and paths.

- The Timing Analyzer supports point-to-point timing constraints, wildcards to identify specific nodes when making constraints, and assignment groups to make individual constraints to groups of nodes.

Refer to the following Related Information: