Introduction

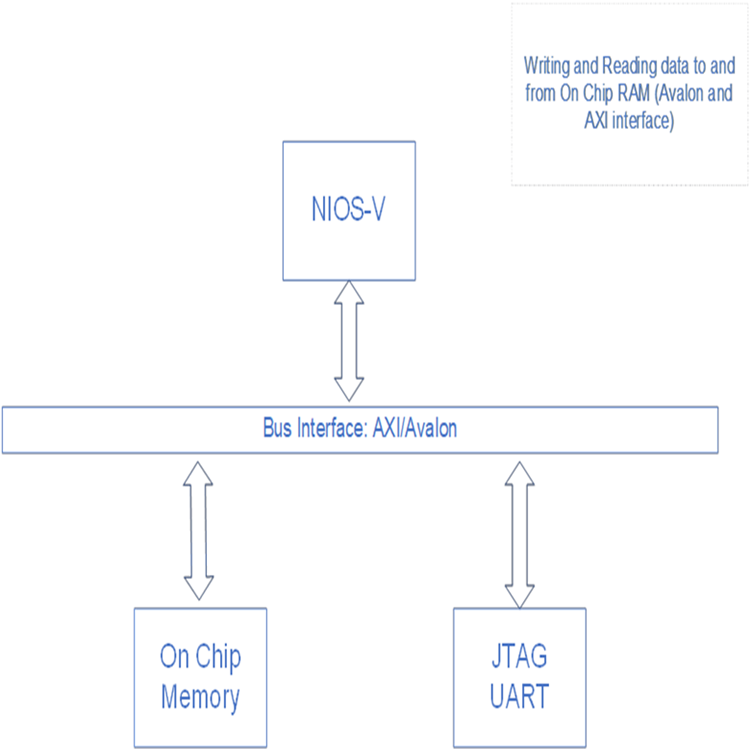

Nios® V/m processor-based Hello World and OCM memory test design example on the Agilex™ 5 FPGA

IP Cores

(6)

| IP Core | IP Core Category |

|---|---|

| Nios V/m Processor Intel FPGA IP | Embedded Processor |

| Configuration Clock Intel FPGA IP | Other |

| In-System Sources & Probes Intel FPGA IP | Other |

| On Chip RAM-II | Other |

| JTAG UART | Other |

| System ID | Other |

Detailed Description

Please refer to the document for details about the design.

Prepare the design template in the Quartus Prime software GUI

Note: After downloading the design example, you must prepare the design template. The file you downloaded is of the form of a <project>.par file which contains a compressed version of your design files (similar to a .qar file) and metadata describing the project. The combination of this information is what constitutes a <project>.par file. You can simply double click on the <project>.par file and Quartus will launch that project.