Introduction

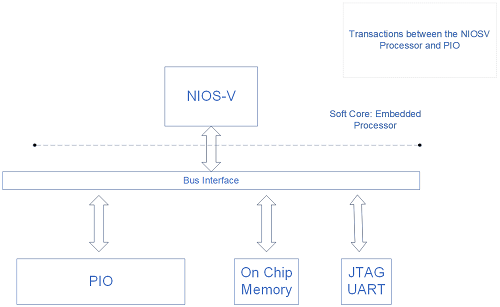

The design example demonstrates the transaction between the Nios® V processor and the parallel input/output (PIO) IP core.

IP Cores

(4)

| IP Core | IP Core Category |

|---|---|

| Nios V/m Processor Intel FPGA IP | EmbeddedProcessors |

| Configuration Clock Intel FPGA IP | ConfigurationAndProgramming |

| Reset Release Intel FPGA IP | ClocksPLLsResets |

| In-System Sources & Probes Intel FPGA IP | SimulationDebugVerification |

Detailed Description

The PIO IP is configured for output ports only and the outputs are connected to the LED on the dev kit.

The application which runs atop of this design toggles these output registers of the PIO IP. The application writes and reads back the content from the IP location.