Description

You might see performance degradation in Partial Reconfiguration (PR) implementation revision when compared with the base revision because in the PR implementation revision the placement and routing are fixed in the static region. This affects the flexibility of placement and routing in the PR region.

Resolution

To reduce the performance degradation in PR implementation revision, follow these steps:

- Ensure that the periphery resources are placed close to the associated logic.

- Minimize the number of signals between periphery resources crossing the PR region.

- For the remaining signals:

- Add enough pipelining registers.

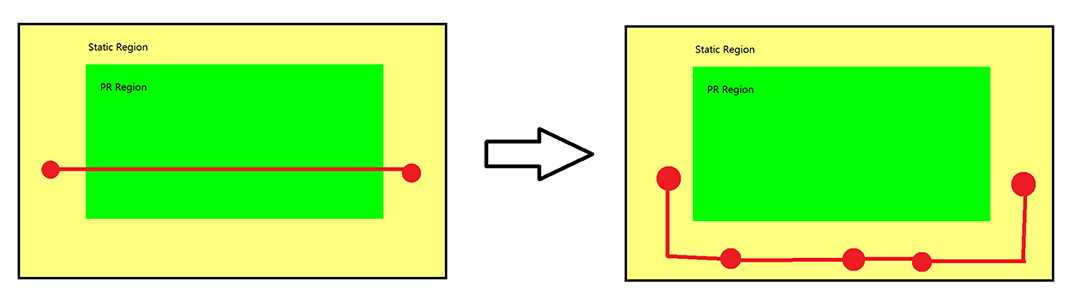

- Create a floor plan for the interconnection logic crossing PR region so that it runs along the PR region boundary like a channel.

- Lock down the PR boundary port wire-LUT (suffix ~IPORT/~OPORT) on the side of PR region that connects to the static region. Also ensure it is close to the boundary of the PR region.