Description

In the Quartus® Prime software, you may see that the Pin Planner creates extra signals beyond the dimension of 2D array declared in SystemVerilog file.

For example,

In .sv file: input [2:0][1:0] Pin_A,

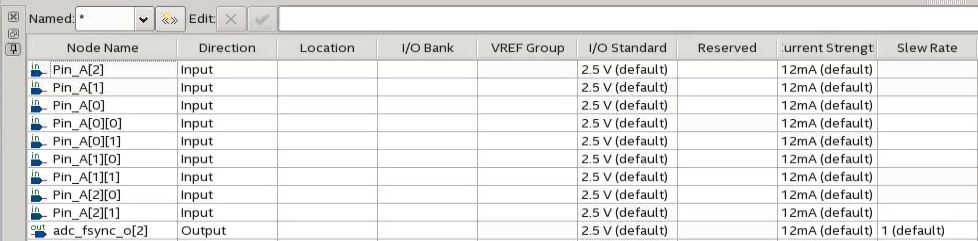

Pin Planner:

Resolution

The group pins Pin_A[0], Pin_A[1] and Pin_A[2] can be safely ignored.