Critical Issue

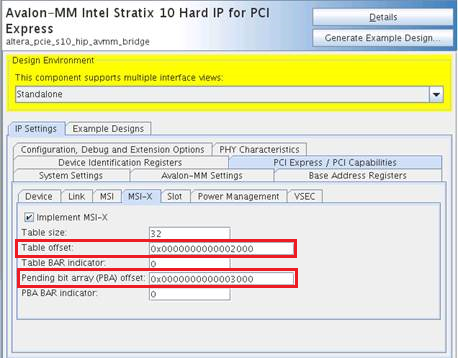

Due to a problem in the Intel® Quartus® Prime Pro Edition software version 19.2 or earlier, the MSI-X parameters below shown in the GUI do not match the params in the generated RTL.

- Table offset

- Pending bit array (PBA) offset

To work around this problem, modify the parameters below in the "altera_pcie_s10_hip_avmm_bridge.v".

parameter [28:0] pf0_pci_msix_pba_offset = 29'h2000 ,

parameter [28:0] pf0_pci_msix_table_offset = 29'h3000

This problem is fixed in the Intel® Quartus® Prime Pro software version 19.3 and beyond.