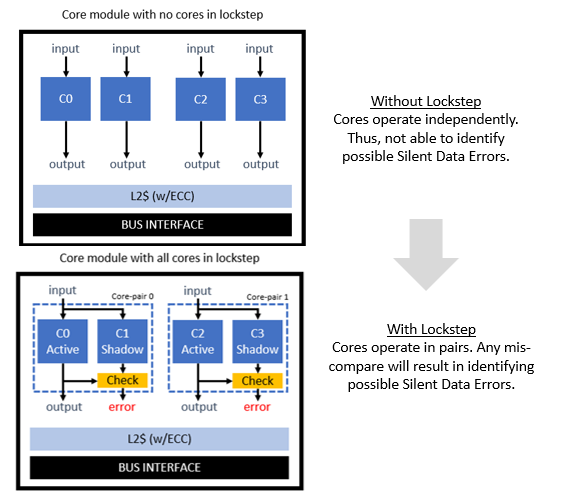

Static Core Lockstep Mode (LSM) is a sophisticated operational mode designed to maintain the highest level of data integrity. At its core, LSM works by comparing the outputs of two cores within the same module, ensuring that their operations are identical and accurate.

How LSM Operates

LSM functions by pairing two cores, known as the active core and the shadow core, which run in lockstep. This means that both cores execute the same instructions simultaneously, with identical inputs. To achieve this, the LSM mode is restricted to cores within the same module that share the same L2 cache.

Key Components of LSM

- Identical Inputs: Both cores in the pair receive the same inputs, ensuring that their operations are comparable.

- Checksum Logic: A checksum logic is used to compare the outputs of the paired cores every cycle, detecting any discrepancies.

- Physical Routing: The same inputs are physically routed to both cores, enabling a direct comparison of their outputs.

Error Detection and Handling

If a mismatch, or divergence, is detected between the outputs of the paired cores, it is signaled as an error. In such cases:

- The active core continues to progress, while the shadow core is dropped after comparison.

- Any core miscompare, which could indicate possible Silent Data Errors, triggers a system reset.

- Errors are logged for further investigation, allowing for prompt action to be taken.

By leveraging the capabilities of LSM, you can ensure the highest level of data integrity and reliability in your critical computing environments.

Key Benefits:

- Error Detection and Prevention: SLSM can detect and mitigate up to 100% of errors that would otherwise result in silent data corruption, providing unparalleled reliability and data integrity.

- Configurability and Flexibility: The feature is configurable, allowing for flexibility in how E-core pairs are utilized, and can be enabled via a BIOS configuration option.

- Enhanced Reliability, Availability, and Serviceability (RAS): SLSM enhances the RAS features of the Intel Xeon 6 processor, making it an ideal solution for environments where computational accuracy is critical, such as autonomous vehicles, industrial control systems, and aerospace applications.

How Static Core Lockstep Mode Works:

- Core Pairing: In Static Core Lockstep Mode, two processor cores are paired together to execute the same instructions simultaneously. This means that each core in the pair performs identical operations on the same data at the same time.

- Error Detection: The outputs of the paired cores are continuously compared to detect any discrepancies. If the outputs match, the system proceeds as normal. If there is a mismatch, it indicates a potential error in one of the cores.

- Error Handling: When a discrepancy is detected, the system can take corrective actions to handle the error. This might involve retrying the operation, logging the error for further analysis, or, in some cases, isolating the faulty core to prevent further errors.

- Benefits of Static Core Lockstep Mode: Enhanced Reliability: By running two cores in lockstep and continuously comparing their outputs, Static Core Lockstep Mode can detect and correct errors that might otherwise go unnoticed. This significantly enhances the reliability of the system.

- Fault Tolerance: The ability to detect and handle errors in real-time helps to prevent system crashes and data corruption, making Static Core Lockstep Mode particularly valuable in environments where uptime and data integrity are critical.

- Data Integrity: Ensuring that operations are executed correctly and consistently helps to maintain the integrity of data processed by the system, which is crucial for applications such as financial transactions, medical records, and other sensitive data.

- Mission-Critical Applications: Static Core Lockstep Mode is especially beneficial for mission-critical applications that require the highest levels of reliability and fault tolerance, such as aerospace, defense, telecommunications, and high-performance computing.

- Trade-offs and Considerations: Performance Overhead: Running two cores in lockstep can introduce some performance overhead, as each operation is effectively duplicated. This can result in lower overall performance compared to running the cores independently.

- Resource Utilization: Using cores in lockstep mode means that fewer cores are available for other tasks, which can impact the overall computational capacity of the system.

- Specific Use Cases: Static Core Lockstep Mode is typically used in scenarios where reliability and fault tolerance are more important than raw performance. It may not be necessary or beneficial for all types of workloads.

This architecture provides applications with a high diagnostic fault coverage at the hardware level. It reduces the effort needed in writing complex software to do loosely coupled lockstep operations in software.

The Static Core Lockstep Mode is enabled via the BIOS configuration option. It provides a powerful tool for detecting silent data errors and is often used in data center fleet management to identify Silent Data Error occurrences during regular maintenance activities.

For more information, please visit Post-Silicon Validation of Static Lockstep Mode on Intel® Xeon® 6 Processor E-Core Architecture