5.3.1. PCIe AXI-ST TX Interface (ss_tx_st)

5.3.2. PCIe AXI-ST RX Interface (ss_rx_st)

5.3.3. Control and Status Register Interface (ss_csr_lite)

5.3.4. Flow Control Credit Interface

5.3.5. Configuration Intercept Interface (CII)

5.3.6. Completion Timeout Interface (ss_cplto)

5.3.7. Function Level Reset Interface

5.3.8. Control Shadow Interface (ss_ctrlshadow)

5.4.1. H2D AXI-ST Source (h2d_st_initatr)

5.4.2. D2H AXI-ST Sink (d2h_st_respndr)

5.4.3. H2D/D2H AXI-MM Master

5.4.4. BAM AXI-MM Master (bam_mm_initatr)

5.4.5. BAS AXI-MM Slave (bas_mm_respndr)

5.4.6. PIO AXI-Lite Master (pio_lite_initiatr)

5.4.7. HIP Reconfig AXI-Lite Slave (user_csr_lite)

5.4.8. User Event MSI-X (user_msix)

5.4.9. User Event MSI (user_msi)

5.4.10. User Function Level Reset (user_flr)

5.4.11. User Configuration Intercept Interface - EP Only

5.4.12. Configuration Slave (cs_lite_respndr) - RP Only

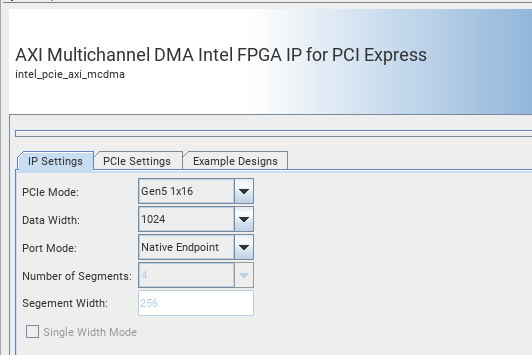

4.1. IP Settings

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| PCIe Mode | Gen5 1x16 Gen4 1x16 Gen3 1x16 Gen5 1x8 Gen4 1x8 Gen3 1x8 Gen5 1x4 Gen4 1x4 Gen3 1x4 |

Gen5 1x16 | Selects the width of the data interface between the transaction layer and the application layer implemented in the PLD fabric, the lane data rate and the lane rate.

Note:

|

| Data Width | 1024 512 256 128 |

1024 |

Supported data widths per the PCIe mode:

|

| Port Mode | Native Endpoint Root Port |

Native Endpoint | Selects port mode. |

| Number of Segments | 4 2 1 |

4 |

Number of segments in data interface. IP Parameter Editor automatically selects a value per the Data Width:

|

| Segment Width | 256 128 |

256 | Segment data width. Fixed at 256 bits for x16 and x8 modes, and 128 bits for x4 mode. |

| Single Width Mode | Off | Sets the Single Width Mode. IP Parameter Editor automatically sets this to On based on the PCIe Mode and Data Width settings. |