1.1. Configuration Methods

1.2. Specifications

1.3. FIFO Functional Timing Requirements

1.4. SCFIFO ALMOST_EMPTY Functional Timing

1.5. FIFO Output Status Flag and Latency

1.6. FIFO Metastability Protection and Related Options

1.7. FIFO Synchronous Clear and Asynchronous Clear Effect

1.8. SCFIFO and DCFIFO Show-Ahead Mode

1.9. Different Input and Output Width

1.10. DCFIFO Timing Constraint Setting

1.11. Coding Example for Manual Instantiation

1.12. Design Example

1.13. Gray-Code Counter Transfer at the Clock Domain Crossing

1.14. Guidelines for Embedded Memory ECC Feature

1.15. FIFO Intel® FPGA IP User Guide Archives

1.16. Document Revision History for the FIFO Intel® FPGA IP User Guide

1.8. SCFIFO and DCFIFO Show-Ahead Mode

You can set the read request/rdreq signal read access behavior by selecting normal or show-ahead mode.

For normal mode, the FIFO Intel® FPGA IP core treats the rdreq port as a normal read request that only performs read operation when the port is asserted.

For show-ahead mode, the FIFO Intel® FPGA IP core treats the rdreq port as a read-acknowledge that automatically outputs the first word of valid data in the FIFO Intel® FPGA IP core (when the empty is low) without asserting the rdreq signal. Asserting the rdreq signal causes the FIFO Intel® FPGA IP core to output the next data word, if available.

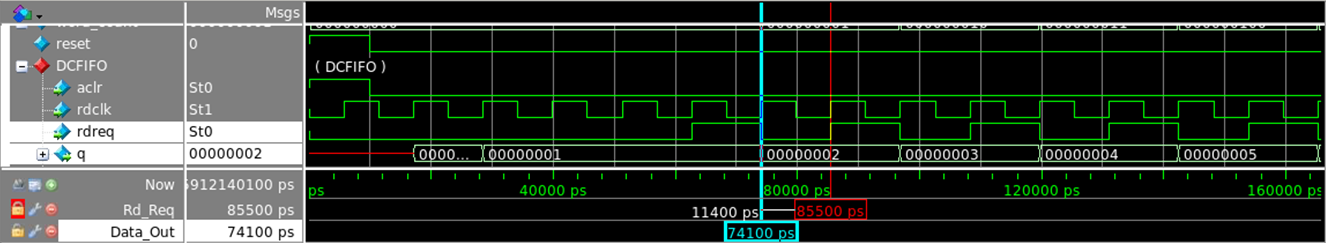

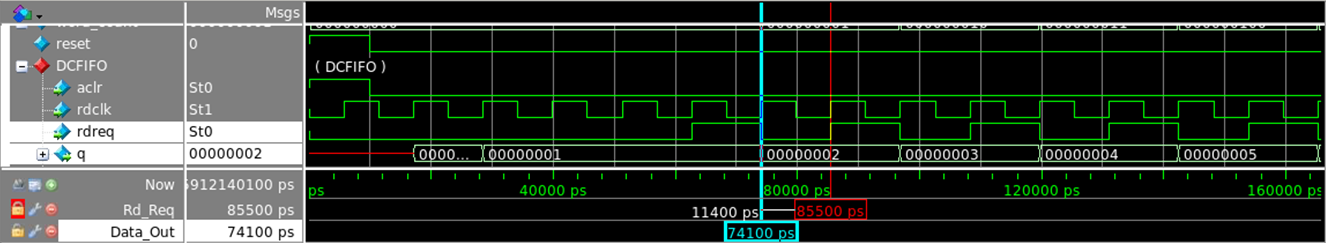

Figure 5. Normal Mode Waveform

Data appears after the rdreq asserted.

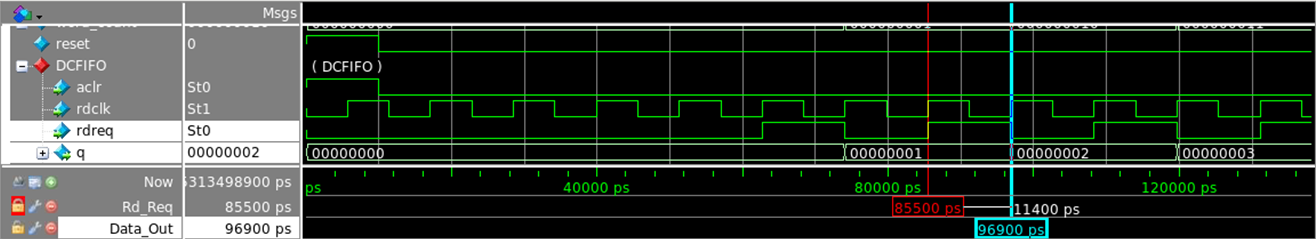

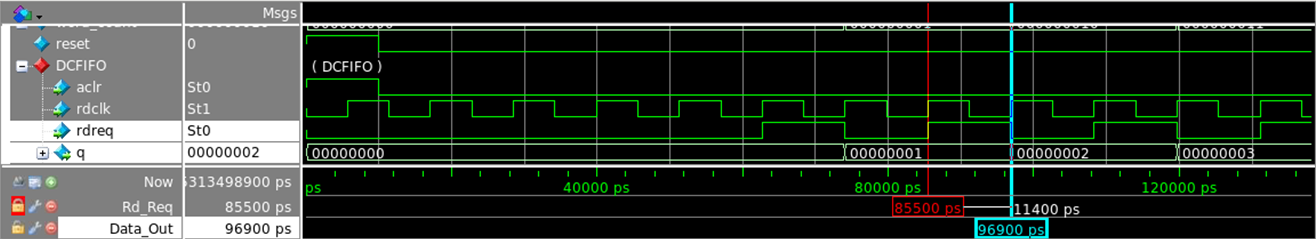

Figure 6. Show-Ahead Mode Waveform

Data appears before the rdreq asserted.