R-Tile Avalon® Streaming FPGA IP for PCI Express* User Guide

ID

683501

Date

8/11/2025

Public

1. About the R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express

2. IP Architecture and Functional Description

3. Advanced Features

4. Interfaces

5. Parameters

6. Troubleshooting/Debugging

7. R-Tile Avalon® Streaming FPGA IP for PCI Express* User Guide Archives

8. Document Revision History for the R-Tile Avalon® Streaming FPGA IP for PCI Express* User Guide

A. Configuration Space Registers

B. Root Port Enumeration

C. Implementation of Address Translation Services (ATS) in Endpoint Mode

D. Packets Forwarded to the User Application in TL Bypass Mode

E. Margin Masks for the R-Tile Avalon Streaming FPGA IP for PCI Express

F. Using the Avery BFM for R-Tile PCI Express Gen5 Simulations

3.2.2.5.1. VirtIO Common Configuration Capability Register (Address: 0x012)

3.2.2.5.2. VirtIO Common Configuration BAR Indicator Register (Address: 0x013)

3.2.2.5.3. VirtIO Common Configuration BAR Offset Register (Address: 0x014)

3.2.2.5.4. VirtIO Common Configuration Structure Length Register (Address 0x015)

3.2.2.5.5. VirtIO Notifications Capability Register (Address: 0x016)

3.2.2.5.6. VirtIO Notifications BAR Indicator Register (Address: 0x017)

3.2.2.5.7. VirtIO Notifications BAR Offset Register (Address: 0x018)

3.2.2.5.8. VirtIO Notifications Structure Length Register (Address: 0x019)

3.2.2.5.9. VirtIO Notifications Notify Off Multiplier Register (Address: 0x01A)

3.2.2.5.10. VirtIO ISR Status Capability Register (Address: 0x02F)

3.2.2.5.11. VirtIO ISR Status BAR Indicator Register (Address: 0x030)

3.2.2.5.12. VirtIO ISR Status BAR Offset Register (Address: 0x031)

3.2.2.5.13. VirtIO ISR Status Structure Length Register (Address: 0x032)

3.2.2.5.14. VirtIO Device Specific Capability Register (Address: 0x033)

3.2.2.5.15. VirtIO Device Specific BAR Indicator Register (Address: 0x034)

3.2.2.5.16. VirtIO Device Specific BAR Offset Register (Address 0x035)

3.2.2.5.17. VirtIO Device Specific Structure Length Register (Address: 0x036)

3.2.2.5.18. VirtIO PCI Configuration Access Capability Register (Address: 0x037)

3.2.2.5.19. VirtIO PCI Configuration Access BAR Indicator Register (Address: 0x038)

3.2.2.5.20. VirtIO PCI Configuration Access BAR Offset Register (Address: 0x039)

3.2.2.5.21. VirtIO PCI Configuration Access Structure Length Register (Address: 0x03A)

3.2.2.5.22. VirtIO PCI Configuration Access Data Register (Address: 0x03B)

4.3.1. Avalon® Streaming Interface

4.3.2. Precision Time Measurement (PTM) Interface (Endpoint Only)

4.3.3. Hot Plug Interface

4.3.4. Interrupt Interface

4.3.5. Hard IP Reconfiguration Interface

4.3.6. Error Interface

4.3.7. Completion Timeout Interface

4.3.8. Configuration Intercept Interface

4.3.9. Power Management Interface

4.3.10. Hard IP Status Interface

4.3.11. Page Request Services (PRS) Interface (Endpoint Only)

4.3.12. Function-Level Reset (FLR) Interface (Endpoint Only)

4.3.13. SR-IOV VF Error Flag Interface (Endpoint Only)

4.3.14. General Purpose VSEC Interface

5.2.3.1. Device Capabilities

5.2.3.2. VirtIO Parameters

5.2.3.3. Link Capabilities

5.2.3.4. Legacy Interrupt Pin Register

5.2.3.5. MSI Capabilities

5.2.3.6. MSI-X Capabilities

5.2.3.7. Slot Capabilities

5.2.3.8. Latency Tolerance Reporting (LTR)

5.2.3.9. Process Address Space ID (PASID)

5.2.3.10. Device Serial Number Capability

5.2.3.11. Page Request Service (PRS)

5.2.3.12. Access Control Service (ACS)

5.2.3.13. Power Management

5.2.3.14. Vendor Specific Extended Capability (VSEC) Registers

5.2.3.15. TLP Processing Hints (TPH)

5.2.3.16. Address Translation Services (ATS) Capabilities

5.2.3.17. Precision Time Measurement (PTM)

F.3. Integrate the Avery BFM Testbench Components

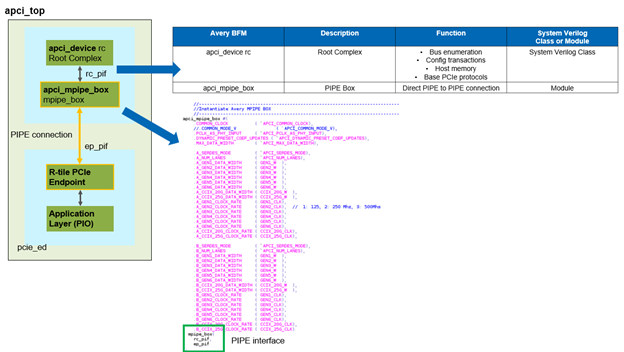

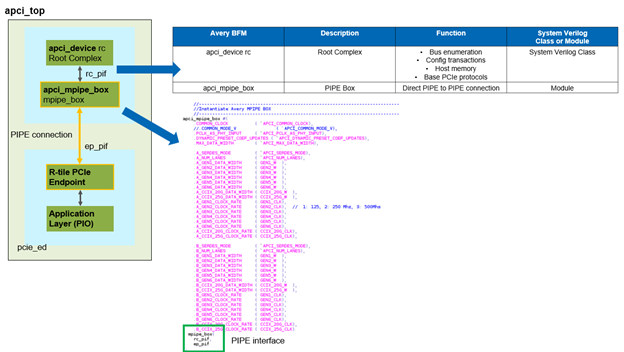

The R-Tile FPGA IP for PCI Express supports serial mode and PIPE mode simulation for the endpoint design example. The example testbench provides the option to select between the Avery BFM Root Complex instantiation for serial and PIPE mode simulations respectively.

The apci_mpipe_box module is instantiated for PIPE mode simulation, exposing a PIPE interface to connect to the R-Tile PIO design example.

Figure 87. PIPE Mode Simulation Testbench

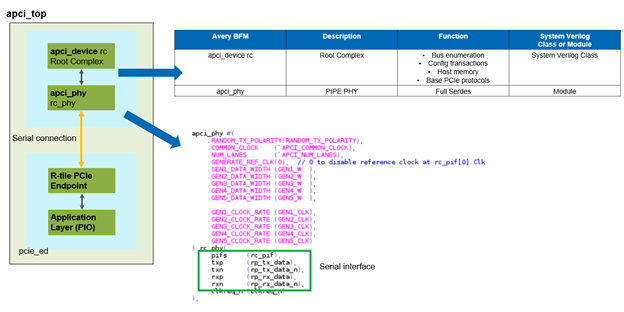

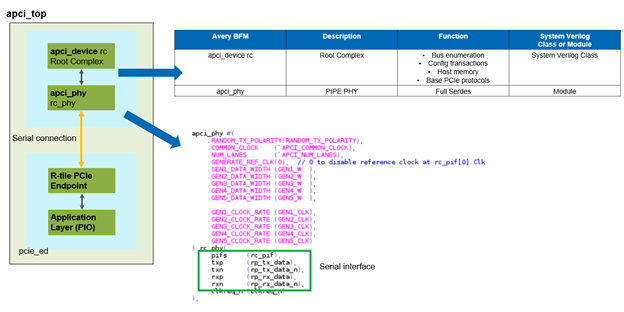

The apci_phy module is instantiated for the serial mode simulation, exposing a Serial interface to connect to the R-Tile PIO design example.

Figure 88. Serial Mode Simulation Testbench