Introduction

Overview

This guide provides the information required to become familiar with the Intel® Quark™ SoC S1000 ASIC firmware infrastructure components and principles of operation.

Audience and Purpose

This document is intended for audio firmware engineers integrating algorithms on Intel Quark SoC S1000 ASIC.

Terminology

| Term | Description |

|---|---|

| ADSP | Audio DSP |

| Canonical format | 32-bit MSB samples |

| DMA | Direct Memory Access |

| DMIC | Digital Microphone (PDM Mems) |

| DP | Data Processing (EDF scheduled tasks) |

| DSP | Digital Signal Processing |

| EDF | Earliest Deadline First |

| Endpoint | Device associated with gateway |

| FW | Firmware |

| Gateway | Unidirectional (input OR output) DMA gateway |

| Graph | Set of pipelines |

| IPC | Inter-Process Communication |

| Library | Dynamically loadable set of the modules |

| LL | Low Latency (1ms, 0.33ms-8ms considered) |

| Loadable module | Dynamically loadable module |

| Management service | A service in FW that manages the communication, configuration, and processing pipelines. |

| Module | Processing component |

| Pipeline | Linear chain of modules |

| Queue | Both Sink and Source |

| RT | Real Time (works as prefix) |

| Sink | Interface for write operation |

| Source | Interface for read operation |

| SW | Software |

| SysTick | System Tick, main interrupt asserted every LL |

Reference Documents

| Document | Document Number / Revision |

|---|---|

| Intel® Quark™ S1000 ASIC Datasheet | 570159 |

Intel® Intel® Quark™ SoC S1000 ASIC Architecture Overview

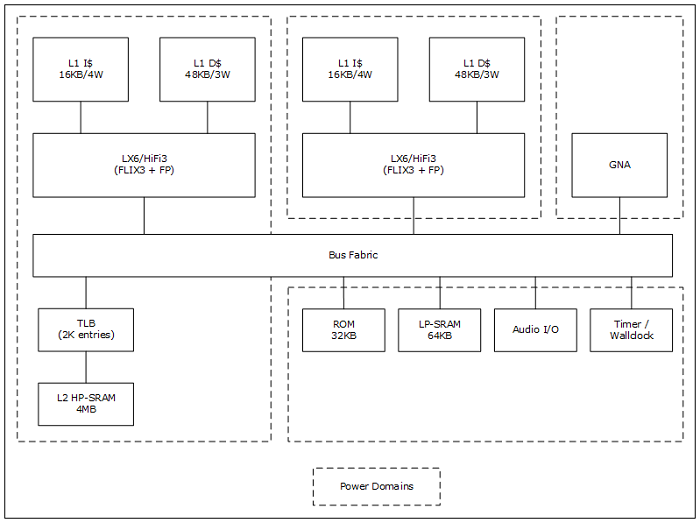

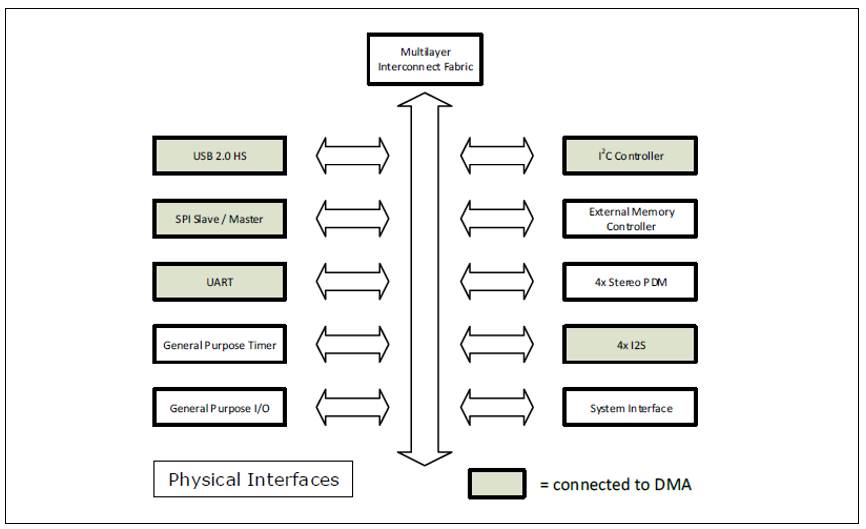

The Intel Quark SoC S1000 ASIC offers the ability to do far-field speech recognition in various smart devices. The Intel Quark SoC S1000 ASIC is designed for complex far-field signal processing algorithms that use high dimensional microphone arrays to do beamforming, cancel echoes, and reduce noise. A pair of DSPs, a neural network accelerator, internal memory, and a set of I/Os provide the necessary resources for speech processing solutions.

Figure 1. Intel Quark SoC S1000 ASIC High-Level Block Diagram

Note For full technical specifications, see the Intel Quark SoC S1000 ASIC Datasheet.

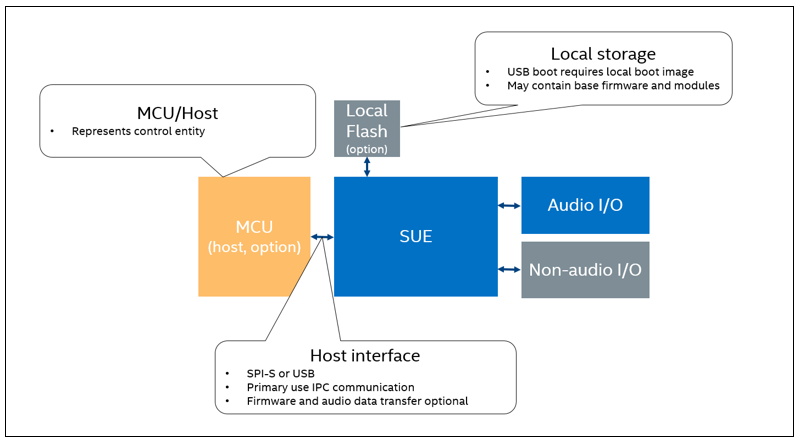

System Model

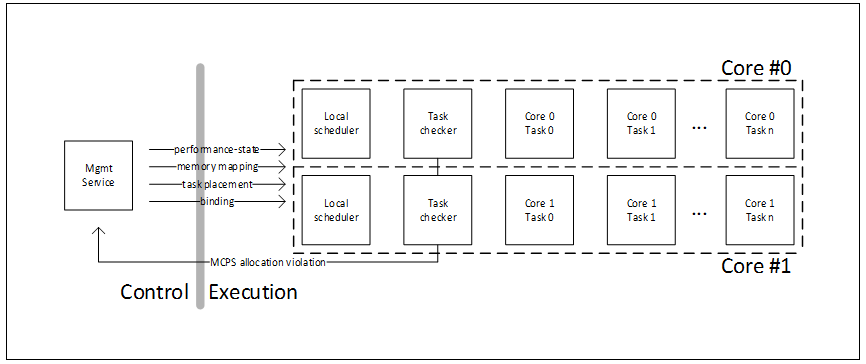

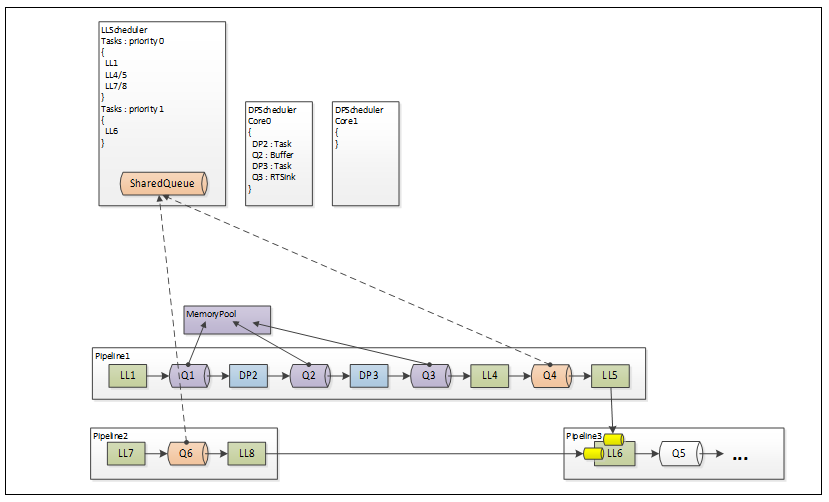

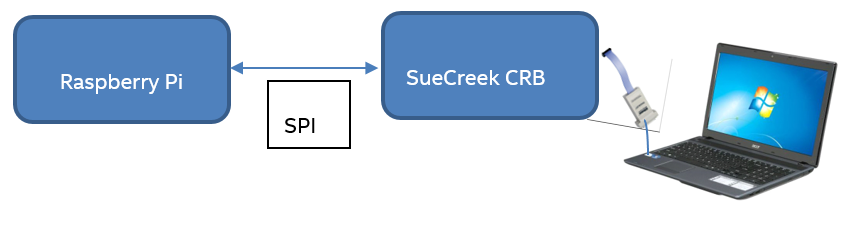

Figure 2. System Model

IPC Communication Over SPI-S

SPI is a protocol that is fully controlled by the master of the SPI bus. The Intel Quark SoC S1000 ASIC is a slave on the SPI bus. Therefore, it cannot initiate any bus transactions or perform flow control when the master performs a transaction.

The DSP in the Intel Quark SoC S1000 ASIC gets notifications of received data only when a receive transfer is configured a priori by the DSP. That is, to get notifications of received data when the threshold is exceeded, the DSP firmware must program a specific data size threshold up front.

The DSP can prepare a response and setup for transfer to the Host, however, the transfer can only be initiated by the Host that is the master on the SPI bus.

The DSP indicates SPI-S readiness by asserting IRQ high. The Host may only start the transfer after a rising edge is observed on the IRQ. The Host may not initiate a transfer when the IRQ is deasserted.

To perform an asynchronous notification, the DSP toggles IRQ line by deasserting it low for minimum 1µs. The notification message (payload) is transmitted as a response when the master performs an SPI transfer on receiving the notification.

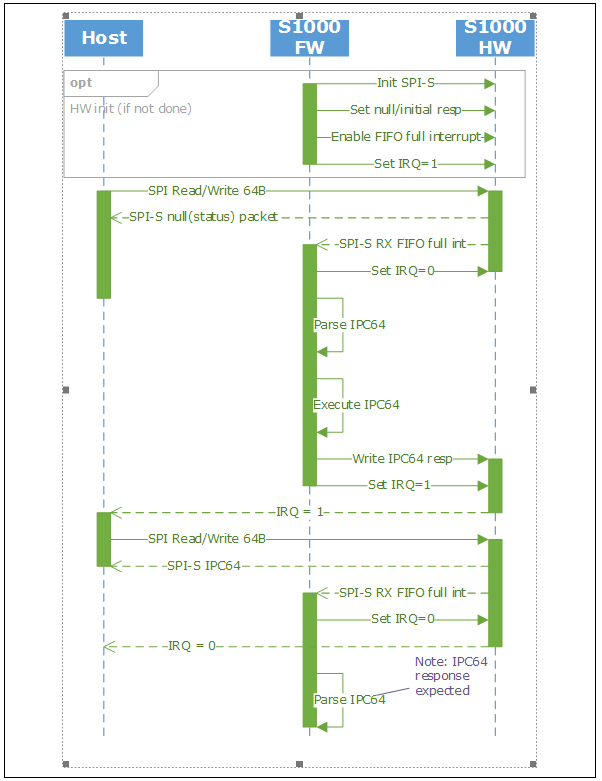

IPC Protocol

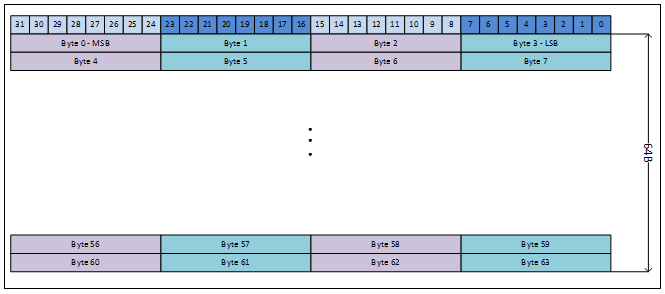

The IPC protocol defaults to the short version of the message called IPC64 that is 64 bytes long. This mode assumes the use of SPI-S IP FIFO to store transmitted data.

On explicit request, IPC64 protocol may be switched to IPC4K protocol. This allows a 4KB IPC transfer in one or both directions.

Note The ROM does not support IPC4K message protocol.

IPC64 Protocol

The IPC64 protocol is default after initialization, and after any other transfer that does not select an alternative protocol.

IPC64 uses SPI-S RX FIFO and FIFO full interrupt to receive data.

IPC64 uses SPI-S TX FIFO to store IPC response data. Data is placed into FIFO before transaction state.

Note ROM implementation of IPC64 uses polling instead of interrupts.

Figure 3. IPC64 Protocol

Receive routines on both the host and DSP side must be ready to receive a “null” message containing all zero bits in the first 32 bits of the message. A null response sent from DSP may have the RSP bit set (optionally). Since behavior may vary between messages, the host should accept both forms of the message.

If the DSP side has nothing more to send, it must post a “null” message and rise IRQ. This action is required to enable the host to perform a transaction, if required.

To enter protocol idle state, the host side must ignore this interrupt. To differentiate between interrupts/states, the host shall not initiate a transaction after receiving a “null” status in response to a “null” request. If host attention is required, the DSP side must toggle IRQ once again.

Note Although starting a transaction while IRQ is 0 violates the defined protocol, the host is not required to actively track this signal. In this case, setting IRQ to 0 by DSP is not related to the fact that data for transmission is not ready. It is necessary only to create the rising edge of the IRQ signal.

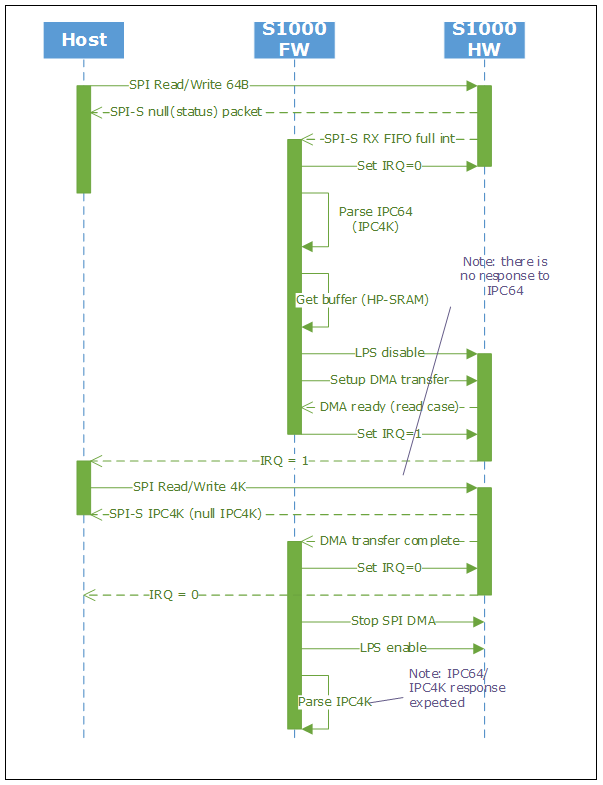

IPC4K Protocol

IPC4K protocol is selected via IPC 4K mode IPC. IPC4K IPC mode selects the direction of transfer via flags.

Figure 4. IPC4K Protocol

IPC4K protocol may be selected for single or multiple transfers. There is no response to protocol switch IPC. Also, the IPC4K response format depends on the format selected for the next IPC. By default, this format is IPC64.

IPC4K uses a DMA buffer pre-allocated in HP-SRAM (LP-SRAM is size constrained). Since LP-GPDMA cannot wake the HP domain, the IPC routine must prohibit the use of LPS for the time that DMA is armed (HP domain power gating).

Receive routines on both host and DSP side must be ready to receive a “null” message containing all zero bits in the first 32 bits of the message. The response size must adhere to the currently selected format. A DSP request to switch to IPC4K must, in all cases, prepare an IPC4K response. It may be any of the following:

- IPC4K null packet (assume that hardware supports this function)

- IPC4K data packet that was scheduled for transmission to Host

- IPC64 packet placed into IPC4K DMA buffer and padded with zeros

Note This assumption is made to avoid FIFO underrun from an IPC64 packet being sent in an IPC4K transaction. An underrun that cannot be differentiated from other underrun cases is not acceptable, as it would prevent diagnosis of actual issues.

Byte Packing/Byte Order Assumptions

IPC communication over SPI-S uses plain (no designated fields) bit transfer. The receive/transmit FIFOs are 32 bits wide. Bytes within a 32-bit word are transferred starting from MSB.

Figure 5. Byte Ordering - IPC64 Example

Certain SPI-M controllers may not be able to generate raw transactions, or transactions that are 64 bytes long. For such hosts, you can send IPC message in portions with the following assumptions:

- Each transaction frame (assertion of SS signal) must be a minimum of 32-bits or a multiple of 32-bits

- The number of bytes must match the expected transfer size

- No padding between transactions, all data is valid on both transmit and receive

To allow operation both with and without toggling the slave select signal during frame transfer, the slave controller uses mode 3 as default.

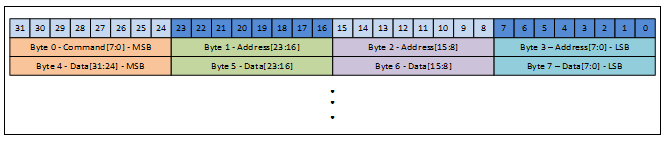

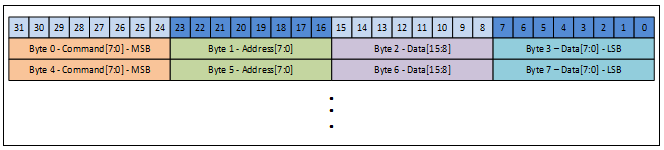

Figure 6 contains examples of data formatting from a controller that supports command, address fields, and 32-bit data. To keep 32-bit alignment, the example shows an 8-bit command and a 24-bit address, followed by various 32-bit wide data values.

Figure 6. SPI Data Layout Example — Command, 24-bit Address, and 32-bit Data

Depending on the number of supported data values, the transaction may need to be repeated multiple times. If only a single 32-bit value is supported, the host must generate eight 64-bit SPI transactions to send IPC64.

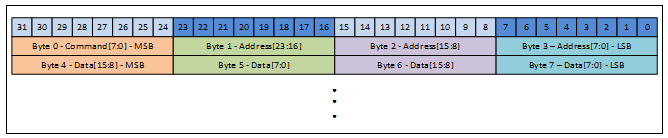

Figure 7. SPI Data Layout Example — Command, 24-bit Address, and 16-bit Data

Figure 7 depicts a similar case, with 16-bit long data values. An even number of data transactions is required (two, at minimum) to keep 32-bit alignment.

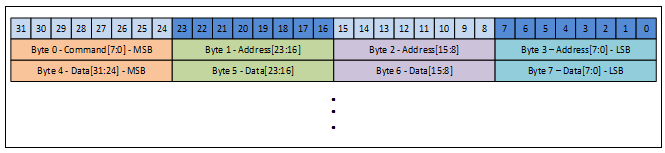

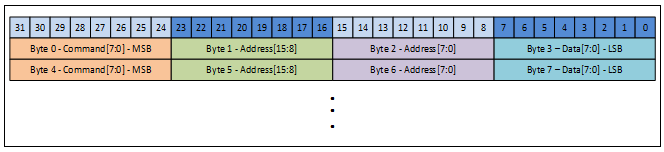

Figure 8. SPI Data Layout Example — Command, 24-bit Address, and 8-bit Data

Figure 8 differs only in the payload size. Here, the data is only one byte long. To keep the transaction, four data cycles or a multiple of four is required.

Figure 9. SPI Data Layout Example — Command, 8-bit Address, and 16-bit Data

Figure 9 shows an example of generating IPC with a simple host controller that can send only 32-bit transactions. The example uses a command, 8-bit address, and 16-bit data to create a 32-bit transaction. A separate transaction generates each 32-bit message data.

Figure 10. SPI Data Layout Example — Command, 16-bit Address, and 8-bit Data

The example in Figure 10 differs in field partitioning. The example uses a command, 16-bit long address, and 8-bit long data.

Depending on the capabilities of the host controller, other combinations are possible. In all the provided examples, the controller must be able to capture data while sending command and address bytes.

IPC64/IPC4K Message Format

IPC communication over SPI must be adapted to media-specific requirements. The design goal is to minimize the change scope and allow transparent translation messages in lower level of firmware and software.

IPC specifics include:

- Must use predefined (announced earlier message size)

- Must advertise message size to remote side

- Asynchronous notification method

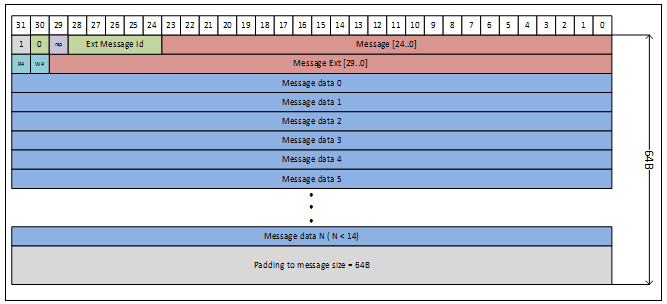

Figure 11. IPC64 Generic Message Format

Figure 11 depicts a generic IPC64 message. The low-level routine that transmits the message must ensure that the size of the message submitted to SPI hardware is exactly 64 bytes. If required, the low-level routine shall add padding (filled with zeros) to achieve the required size.

R4 and W4 bit fields are used to reduce transmission overhead. Both fields reuse B/E fields that are not used in a given version of the protocol. The R4 field requests the DMA buffer setup for SPI Read. For a master transaction initiated from the host, this means that the subsequent transaction is expected to read a 4KB message. The same field in the response message indicates to the SPI master a request for a 4KB transaction (for example, to return a long message response). Similarly, the W4 field defines the buffer transaction setup in the opposite direction.

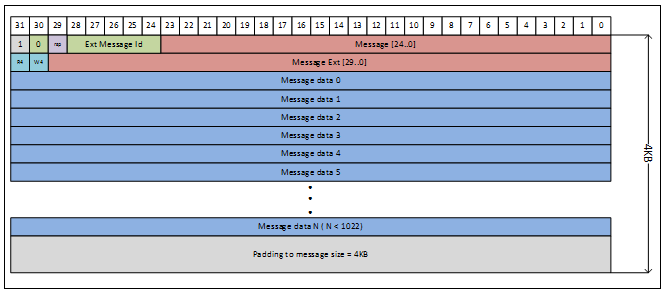

Figure 12. IPC4K Generic Message Format

The format of a 4KB message is shown in Figure 12. The only difference in this situation is the amount of allowed payload or required padding.

The protocol allows independent setting of the R4 and W4 fields. However, if one bit is set, the host performs a 4KB R/W transaction. This means that an unselected buffer must either be disabled (null transfer), or adhere to the selected format.

A similar situation occurs when both the R4 and W4 bits are set. In this situation, a 4KB transfer is executed in both directions.

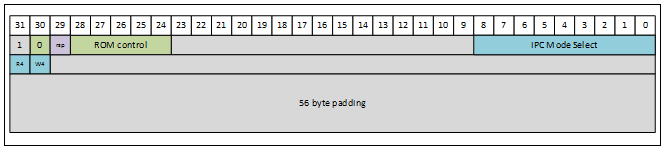

Figure 13. IPC Mode Select IPC

The explicit message IPC Mode Select (Figure 13) is used when the host or device must switch to 4K mode without data for transmitting/receiving. IPC Mode Select is essentially a “null” IPC64 message that allows mode selection for the next transaction. The message can be used in both directions. Specifically, the SPI slave may choose to return this message to indicate that the returning data requires a larger buffer.

IPC Mode Select IPC with both R4 and W4 messages is used as a “null” message. It is useful for the host to pull a pending message from SPI-S hardware.

Note In general, the master side shall request IPC4K transfers for transactions expected to return more than 60 bytes of data.

Note Intel recommends that you fit asynchronous notification data in IPC64 format. Otherwise, notification handling may require three messages.

Asynchronous Notification Support

Asynchronous notification requires the generation of a minimum of two interrupt events using the IRQ line.

During the first interrupt, the host transfers previously a configured (typically null) response according to selected protocol. In a typical case (idle/waiting for event scenario), the hardware IPC selects IPC64 protocol version.

This approach is required because, once firmware determines the need for an asynchronous response, the “current” (typically empty) response is already submitted to hardware. Since hardware does not allow the safe substitution of a response, the firmware must force a flush of the current response.

Since the host is expected to be idle at a time when asynchronous notification is received, it issues IPC Mode Select IPC.

Note The host may choose to request IPC64 mode (the default and recommended mode), or IPC4K mode (if majority of notifications are expected to be in IPC4K format).

The firmware parses the received data to determine the next transaction buffer size. In a typical case, the firmware submits an IPC64 response. However, as the host may choose IPC4K format, the firmware must also handle the case of sending an IPC64 response in the 4K buffer.

Yet another case is created when the upper firmware layers request the IPC4K notification format (message size >60 bytes), while the host selects IPC64 mode. To handle this situation, the firmware responds with IPC Mode Select, with the R4 field set, to force the host to select 4K mode.

Independently of the previous case, the firmware attempts to put response data and rise interrupt over the IRQ line, as long as asynchronous notification data remains unsubmitted.

Intel recommends that the host suppresses sending messages while previous operations are incomplete. Although such concurrency cannot be eliminated, both sides of the protocol must handle messages asynchronously. Specifically, the host must not block forward receive progress while waiting for a request response, because the asynchronous notification inserted in front of the expected response must be comprehended.

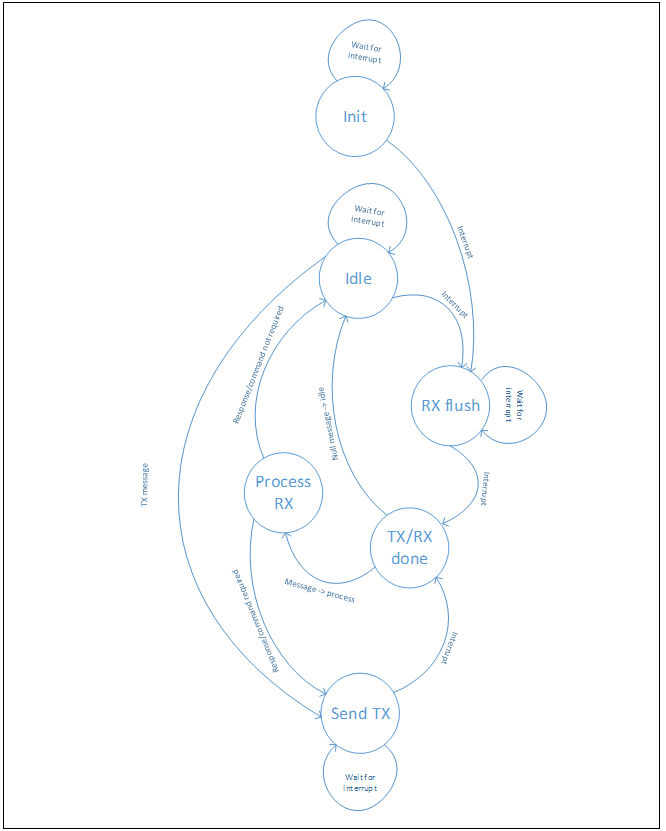

Host State Machine

Figure 14 shows the host state machine. After deasserting, a reset triggers ROM to put a status message in the RX FIFO. To read the message, the host must either send some message. Typically, this message is a null message that allows determination of the SoC version (status). For clarity, the figure does not include opportunistic transfers that may happen on both sides, nor does it include IPC format selection.

Figure 14. Host State Machine

Flows

Boot Options

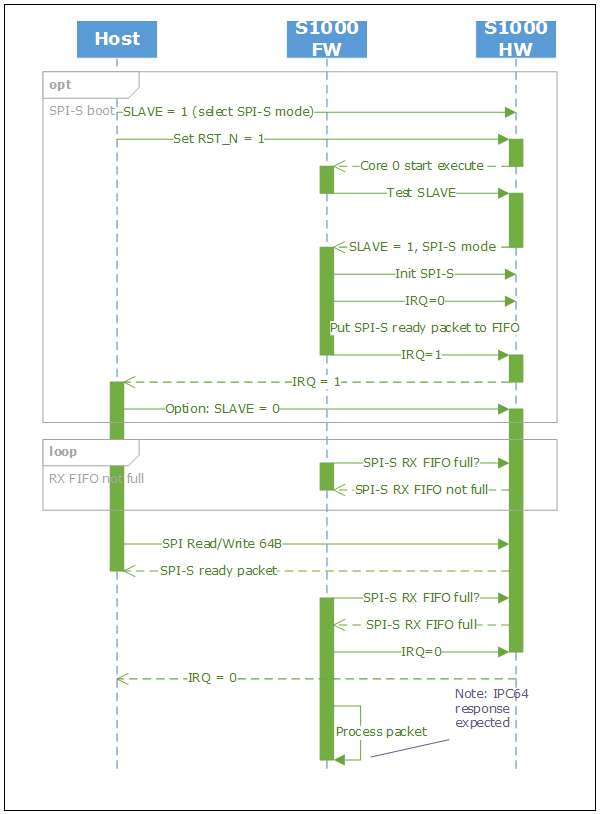

SPI-S Mode Operation

Boot from SPI-S is used in configurations where the firmware for the Intel Quark SoC S1000 ASIC is downloaded from a host. This configuration does not usually have a flash memory attached to the SPI-M of the Intel Quark SoC S1000 ASIC.

SPI-S Mode Selection

SPI-S mode is selected by asserting high (statically or dynamically) strap option connected to SPI_SLAVE_MST_N_BOOT. The Intel Quark SoC S1000 ASIC samples the strap during de-assertion of the HOST_RST_N input. If the sampled strap value is 1, the ROM code attempts to initialize the SPI-S controller and start polling for messages from the host.

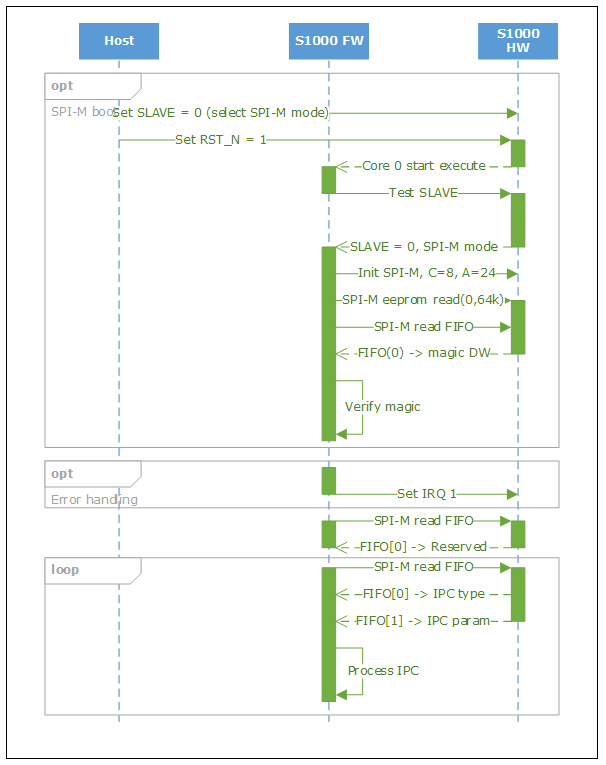

Figure 15. Interactions Between Host and Intel Quark SoC S1000 ASIC in SPI-S Mode

Figure 15 shows the SPI-S mode support. After early initialization and boot mode detection, the firmware enters a wait loop for the initial IPC64 command packet. Once the RX FIFO ready state is determined, the firmware starts reading the necessary DWORDs from the FIFO. By reading the first one or two DWORDs, the ROM implementation can determine and properly dispatch the command.

IPC Protocol

The defined messages use the Count field to indicate the number of message DWORDS present after the header. The IPC message send function provides padding between the current message size, (Count+2)*4, and the currently selected IPC mode. The IPC processing function consumes the padding DWORDs from the SPI-S FIFO. In the current definition, the ROM supports IPC64 messages only.

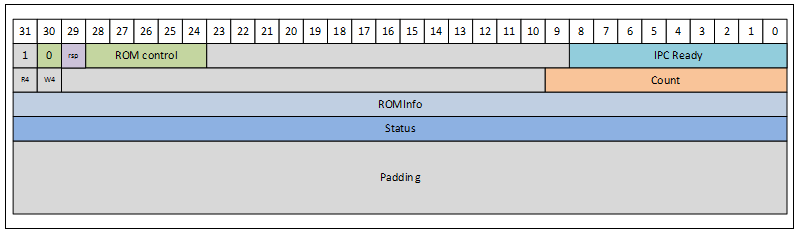

ROM Ready IPC

As part of early boot process ROM, puts ROM Ready IPC in SPI-S TX FIFO. The message indicates that the ROM is ready to receive IPC commands, and provides information about the ASIC version.

Figure 16. ROM Ready IPC

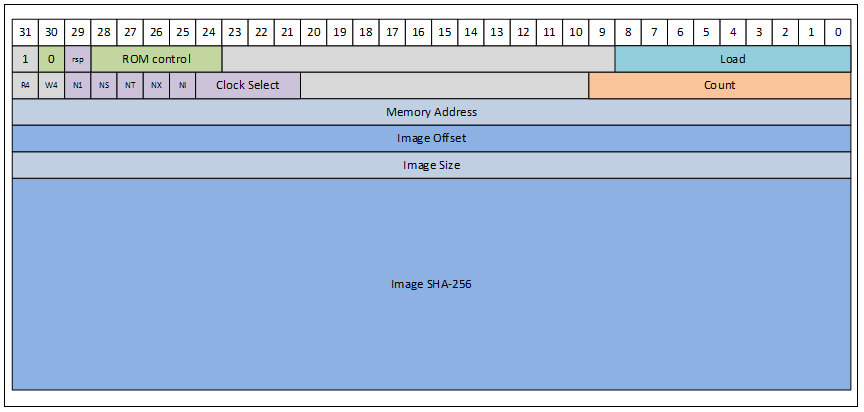

Firmware Load Messages

Regardless of framing, the payload is expected to contain only data up to the number of messages defined in the Image Size field. The address field is expected to reside in HP-SRAM. The memory address and image size must be aligned to a minimum of 64B.

The image offset field is not used in SPI-S mode. Set it to 0.

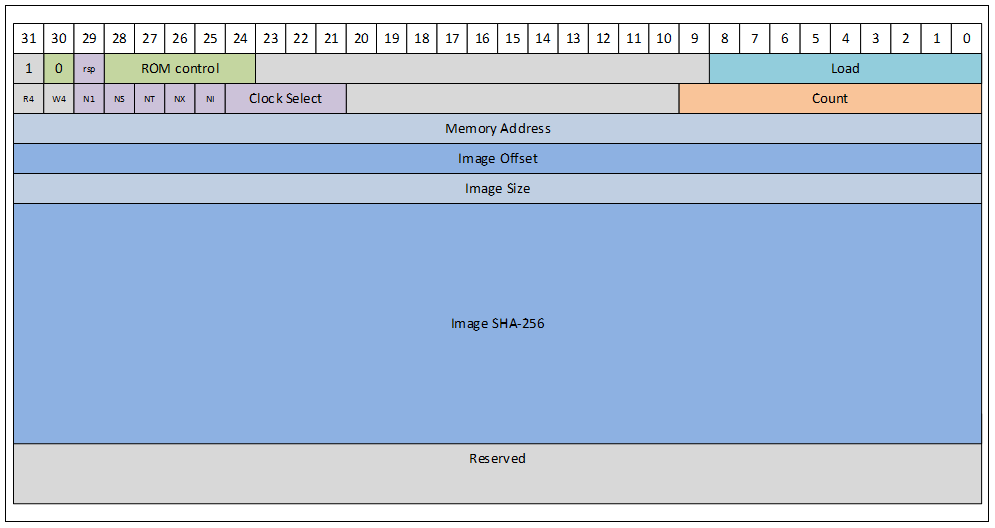

Figure 17. Load Firmware IPC

By default, the message carries the valid Memory Address, Image Size, and SHA-256 checksum of the image.

All N* fields are reserved and shall be set to 0.

The Clock Select field allows the host to select an alternative SPI-S clock source. The currently defined encodings are as follows:

- 0 – use default clock

- 1 – use high-performance clock

All other values for this field are reserved.

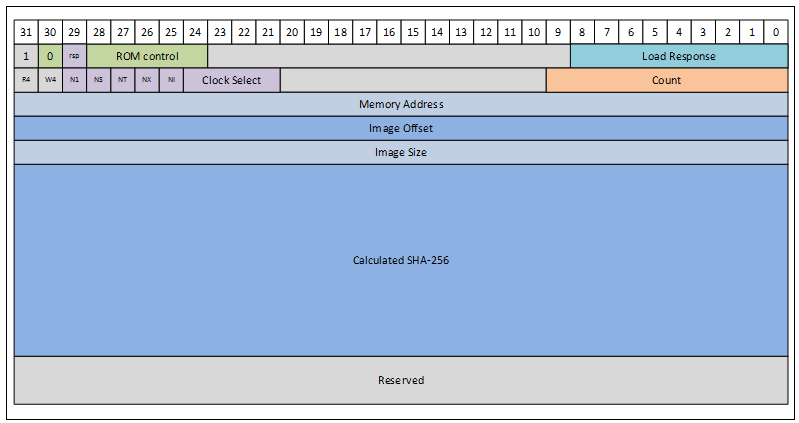

Figure 18. Load Firmware Response IPC

The Load Firmware response IPC is placed in the TX FIFO of the controller. It contains a copy of the original IPC with the RSP bit set, and an updated SHA-256 value.

The firmware entry point is the same as the load memory address. This allows maximum flexibility of internal image implementation.

SPI-M Mode Operation

Boot from SPI-M connected flash is used in configurations where the Intel Quark SoC S1000 ASIC is operating independently or with the host connected via USB/SPI-S. In these configurations, a valid firmware image must be stored in the connected flash from which the Intel Quark SoC S1000 ASIC can boot.

SPI Part Assumptions

To boot successfully, the SPI slave device (presumably a non-volatile memory type) must meet the following criteria:

- Connection SPI-M interface of Intel Quark SoC S1000 ASIC as slave #0

- VIO 1.8V, SPI clock min 19.2MHz

- Support mode 0 (ROM uses mode 0)

- Support read command 3 with 24-bit address and w/o need for dummy cycles

- Support for linear read burst (no size constrains)

Boot Mode Selection

Select SPI-M mode by platform driving (pulling down) the SPI_SLAVE_MST_N_BOOT signal low before HOST_RST_N is deasserted.

Boot in SPI-M Mode

Figure 19 depicts the interactions between firmware (in ROM) and hardware.

Figure 19. Boot From Locally Attached SPI Device

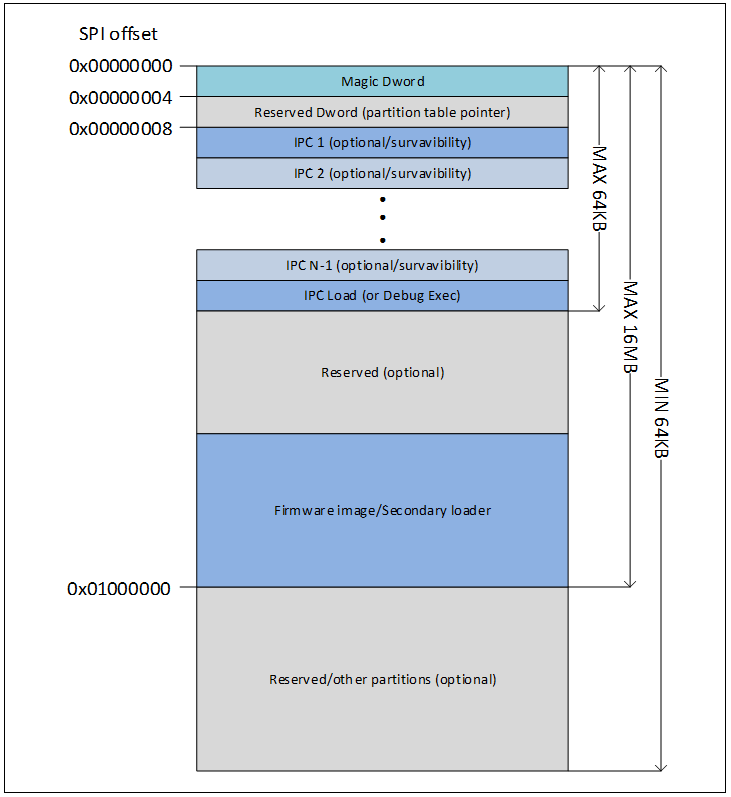

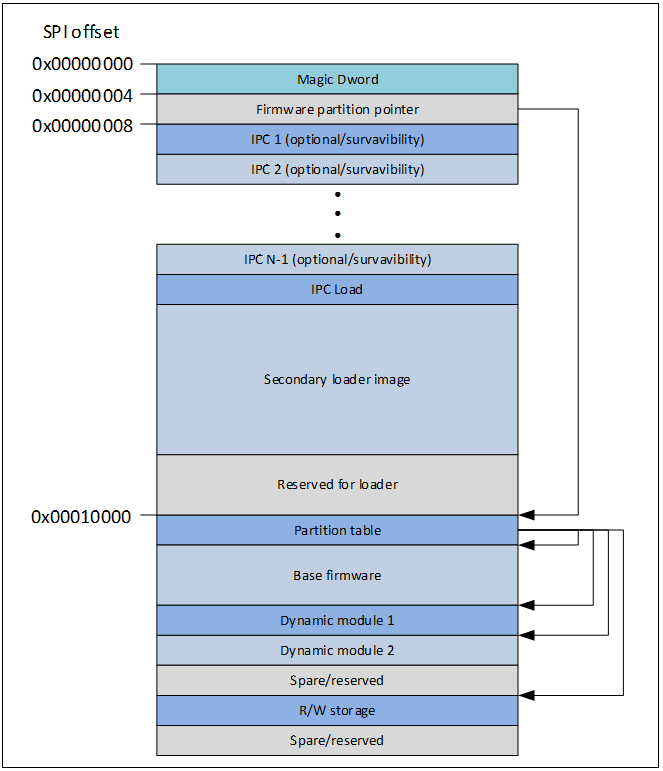

SPI Memory Layout

The initial portion of flash is organized as a linear block of DWORD values. Starting from address 0, DWORD values can be read one by one and processed sequentially. This approach simplifies the ROM interpretation routine that must be assembly coded (SRAM is not available during initial parsing).

Figure 20. SPI Memory/Flash Layout

Figure 20 depicts the SPI memory (Flash) layout, as interpreted by ROM.

The SPI memory starts from the magic DWORD (0x30504353, the value used if flash is attached and programmed). This magic DWORD mechanism differentiates between a valid image and an invalid image, and takes fallback action if the image is invalid.

Next there is a single DWORD, not parsed by ROM. This DWORD is intended to be the partition pointer/flash file system pointer. In the example in Figure 21, the pointer references the partition table at 64 KB offset. This type of organization allows you to keep some reserved space for the hardware initialization or loader portion of the flash, and to update it without repartitioning the entire device. The pointer is used by the secondary loader to quickly locate the table without parsing the initial portion of the flash again.

After the two initial DWORDs, the IPC script starts. The entire script, including the initial DWORDs and Load command, fits in 64KB.

The minimum configuration is just 64B: 8 bytes of initial words, and a 56 byte load command.

The firmware image or secondary loader image is located entirely in the first 16 MB of SPI space.

Figure 21. Memory Partitioning Example

IPC Protocol

Firmware Load Messages

Regardless of framing, the payload is expected to contain only data up to the number of messages defined in the Count field. By default, the Address field is expected to reside in HP-SRAM. The Memory Address and Image Size must be aligned to a minimum of 64B.

Figure 22. Load Firmware IPC

By default, the message carries a valid memory address, DWORD aligned image size, and SHA-256 checksum of the image.

All N* fields are reserved and shall be set to 0.

The Clock Select field selects an SPI-M clock source and divider to be used during firmware load.

The currently defined encodings are as follows:

- 0 – Use default clock

All other values of this field are reserved.

If there is SHA-256 hash check failure, the ROM enters a fatal error state.

Creating Streams

To create a stream, the management service must build the list of module instances that will be part of the stream processing logic. Each module instance affinity must be assigned to a core by the management service. If any instance that is on the list requires a loadable module to be available, the management service must check if the module is already loaded. Otherwise, it must execute the module loading flow before sending the module instance list to the firmware. The firmware expects that all resources, including processing code, memory, and core bandwidth, are verified by the management service before the module instance list arrives.

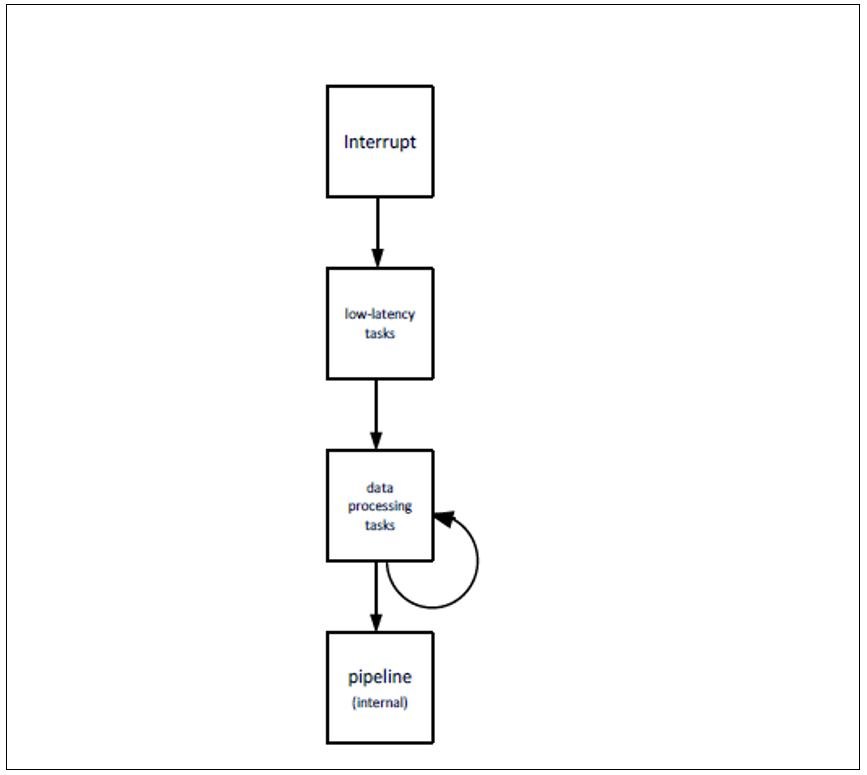

A stream may consist of one or more pipelines. The firmware supports up to four pipelines connected via Mixers in a single render stream. Each pipeline is a sequence of module instances. Each module instance may execute in either Low Latency or Data Processing domain. Each subsequence of consecutive Data Processing module instances must be assigned to the same Core.

For example, a pipeline that consists of the following module instances LL0-LL1-DP2-DP3-LL4-DP5-DP6-LL7 must be distributed among the cores so that the subsequence DP2…DP3 has the same affinity (for example, Core0) and DP5…DP6 also has the same affinity (for example, Core1).

Note Modules must be instantiated in their data processing order within the pipeline. That is, if mod1 produces data for mod2, then IPC Init Instance (mod1) must be called before IPC Init Instance (mod2).

Retrieving FW/HW Configuration and Topology Information

The management service may query firmware and hardware configuration, and topology information, by requesting the values of the following parameters:

- Base FW parameters:

- Firmware Config

- Hardware Config

- Modules Info

- Pipeline List Info

- Pipeline Properties

- Module Instances Info

- Gateways Info

- Memory State Info

- Power State Info

- Module instance parameters:

- Module Instance Properties

The management service may also set some of the firmware configuration parameters.

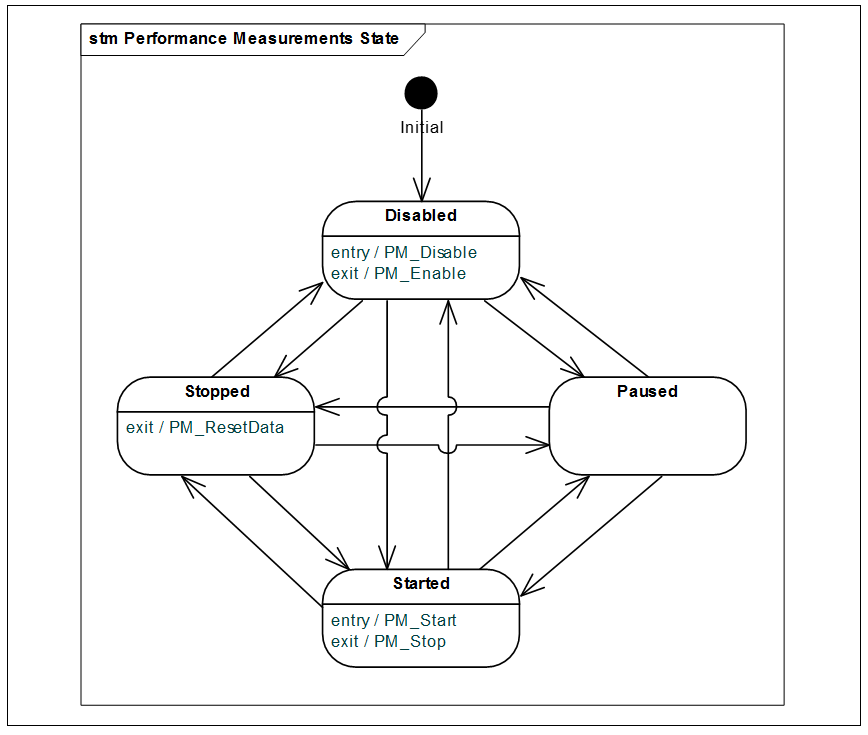

Retrieving Performance Data

Performance data collecting is disabled by default in the firmware.

To retrieve capture performance data, the management service must execute following steps:

- Enable performance measurements by setting Base FW’s PERF_MEASUREMENTS_STATE parameter to either Stopped or Started (in the latter, data collecting starts immediately).

- Start performance measurements by changing the state to Started (if not done in the previous step).

- Execute the scenario to be measured.

- Pause performance measurements by changing state to Paused. Changing the state to Stopped erases all collected data immediately.

- Retrieve performance measurements data, including global items provided by the Base FW’s GLOBAL_PERF_DATA parameter, and the pipeline and module instance properties.

- Now, performance measurements may be either resumed (Paused → Started), restarted (Paused → Stopped → Started) or disabled completely (Paused → Disabled).

To see all possible transitions between states of performance data collection mechanism, refer to Introduction.

Fatal Error Reporting

The DSP ROM implements a fatal error handling mechanism. All unexpected errors, such as L1 or L2 double-bit errors, result in firmware halt and set the IRQ line to 1. More detailed reasons can be determined only using JTAG.

If the firmware is not responsive, the host-based software must reset the Intel Quark SoC S1000 ASIC by asserting the HOST_RST_N pin low.

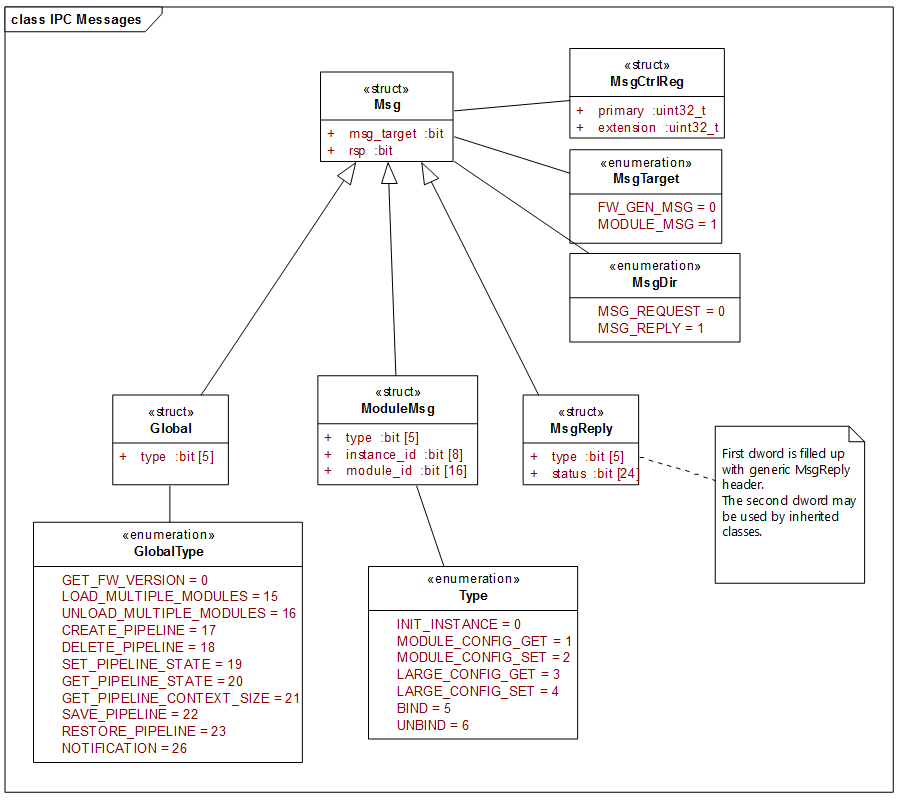

IPC Interface

The IPC interface enables message exchange between firmware and the software running on host.

IPC communication may be initiated by either side, as follows:

- The management service sends an IPC request – either a Global message directed to the firmware infrastructure (Base FW), or a Module message directed to a module instance running in firmware – and the firmware replies with an IPC response.

- Firmware sends an IPC Notification (one way, not replied to by the host) that is a Global message of NOTIFICATION type.

An IPC message consists of a header exchanged through SPI interface, and an optional payload.

It applies to the following IPC messages:

- Load Module

- Unload Module

- Init Module

- Large Config Set

- Large Config Get

Figure 23. IPC Message Header

There are three types of IPC message headers:

- Global Message – a request from the management service directed to the firmware infrastructure

- Module Message – a request from the management service directed to one of firmware module instances

- Message Reply – a reply to the management service sent by the firmware in response to either request

IPC Base Structures

MsgCtrlReg Structure

Note The Msg structure and all derived structures preserve the upper level bit definition. The Msg structure breaks down MsgCtrlReg::payload_primary and MsgCtrlReg::payload_extension, preserving other fields of MsgCtrlReg. Derived messages break down Msg::Bits::rsvd0 and Msg::Bits::rsvd1, preserving other fields of Msg::Bits.

struct MsgCtrlReg

{

union

{

struct

{

uint32_t primary;

uint32_t extension;

} dw;

struct

{

// primary register fields

uint32_t payload_primary : 31;

uint32_t _busy : 1;

// extension register fields

uint32_t payload_extension : 30;

uint32_t _done : 1;

uint32_t _error : 1

} bits;

} regs;

};

Msg Structure

This is a base structure for all IPC message headers. It defines common bits that are used in both communication directions.

Syntax

struct Msg

{

enum MsgTarget

{

FW_GEN_MSG = 0, // Global message

MODULE_MSG = 1 // Module message

};

enum MsgDir

{

MSG_REQUEST = 0, // Request

MSG_NOTIFICATION = 0, // Notification

MSG_REPLY = 1 // Reply

};

struct Bits

{

// primary register

uint32_t rsvd0 : 29;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

// extension register

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

};

Members

rsp

Indicates that an upstream message is a response to some request (and not a notification). This bit lets the management service dispatch the message appropriately avoiding a race condition in the following scenario:

- Host sends a request down to FW.

- FW (at the same time sends a notification).

- Host receives upstream message and is able to qualify it as an unsolicited notification rather than a response to the request just sent to FW.

- FW receives a request, processes it and sends a response.

One of MsgDir values.

msg_tgt

Used by FW to dispatch Global (infrastructure directed) messages and messages directed to module instances. One of MsgTarget values.

Global Request

Global::Bits Structure

This structure is a base class for all messages handled by the Base FW.

Syntax

struct Bits

{

uint32_t rsvd0 : 24;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Members

msg_tgt

Set to Msg::FW_GEN_MSG

rsp

Set to Msg::MSG_REQUEST

type

Indicates type of the Global message (one of Global::Type).

ModuleMsg Request

This structure is a base class for all messages directed to the modules and handled inside the modules. There are some exceptions of module messages that are handled by the Base FW, but this is transparent for host IPC.

Every Module Message specifies the ID of the module and instance to which the message is dispatched.

ModuleMsg::Bits Structure

Syntax

struct Bits

{

uint32_t module_id : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Members

msg_tgt

Set to Msg::MODULE_MSG

rsp

Set to Msg::MSG_REQUEST

type

Indicates type of the Module message (one of ModuleMsg::Type).

instance_id

ID of the target module instance.

module_id

ID of the target module.

MsgReply Response

This structure is a base class for replies sent back to the originator once handling of a request is completed.

Due to the new asymmetric nature of request and response, the status field is now 24-bits wide. Therefore, the first DWORD of the message control register is filled. If message-specific data must be sent back, it may be packed into either the second DWORD or into the Data payload. If there is no message type-specific data to be sent back, the message handler may send a reply of MsgReply type directly. Otherwise, a defined inherited structure is used to construct a reply.

Note Due to the same width and position of the type field in both Global and ModuleMsg requests, you do not need to define separate reply structures. MsgReply may be used for messages of both types.

MsgReply Structure

Syntax

struct MsgReply : Msg

{

struct Bits

{

uint32_t status : IXC_STATUS_BITS;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

};

Members

msg_tgt

Same as the request target. Either Msg::FW_GEN_MSG or Msg::MODULE_MSG.

rsp

Set to Msg::MSG_REPLY.

type

One of message types.

status

One of IxcStatus values.

Remarks

The MsgReply::status is set by FW to one of IxcStatus values. There is one flat space of status values used by all FW components that reports the status of the operation in the IPC reply.

See the adsp_ixc_status.h header file for the most up-to-date complete documentation. The following sections outline some message-specific status values.

General IPC Error Codes

Table 3. IPC General Error Codes

| Error Code | Value | Description |

|---|---|---|

| ADSP_IPC_SUCCCESS | 0 | The operation was successful. |

| ADSP_IPC_ERROR_INVALID_PARAM | 1 | Invalid parameter specified. |

| ADSP_IPC_UNKNOWN_MESSAGE_TYPE | 2 | Unknown message ID specified. |

| ADSP_IPC_OUT_OF_MEMORY | 3 | No memory to complete the request. |

| ADSP_IPC_BUSY | 4 | System or resource is busy. |

| ADSP_IPC_PENDING | 5 | The request was scheduled for asynchronous processing. |

| ADSP_IPC_FAILURE | 6 | Unknown error while processing the request. |

| ADSP_IPC_INVALID_REQUEST | 7 | Unsupported operation requested. |

| <reserved> | 8 | N/A to SKU2-LP (was ADSP_STAGE_UNINTIALIZED). |

| ADSP_IPC_INVALID_RESOURCE_ID | 9 | Specified resource not found. |

| <reserved> | 10 | N/A to SKU2-LP (was ADSP_SOURCE_NOT_STARTED). |

| ADSP_IPC_OUT_OF_MIPS | 11 | No MCPS to complete the request. |

| ADSP_INVALID_RESOURCE_STATE | 12 | Required resource is in invalid state. |

| ADSP_IPC_UNAVAILABLE | 15 | Requested service or data is unavailable on the target platform. |

General IPC Messages

Static and dynamic runtime FW infrastructure properties are retrieved using module configuration messages addressed to module ID 0 (Base FW). See Section 5.6.4, “Base FW”.

Performance Measurements Command

The management service sends this message to execute the performance measurements command.

Request Message Control Header

struct Bits

{

uint32_t command : 8;

uint32_t rsvd0 : 16;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _reserved_0 : 1; // HW ctrl reserved bits

uint32_t rsvd1 : 30;

uint32_t _reserved_2 : 2; // HW ctrl reserved bits

};

Table 4. Performance Measurements Command – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REQUEST |

| type | Global::PERF_MEASUREMENTS_CMD |

| command |

Command to be executed by FW, one of:

|

Input Data

There is no input data.

Reply Message Control Header

struct Bits

{

uint32_t status : IXC_STATUS_BITS;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 5. Performance Measurements Command – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REPLY |

| type | Global::PERF_MEASUREMENTS_CMD |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_STATE ADSP_IPC_INVALID_REQUEST |

Output Data

There is no output data.

Library & Module Management IPC Messages

Load Library

The management service sends this message to initiate loading of a library into the ADSP memory.

Request Message Control Header

struct Bits

{

uint32_t dma_id : 5;

uint32_t rsvd0 : 11;

uint32_t lib_id : 4;

uint32_t rsvd1 : 4;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _reserved_0 : 1; // HW ctrl reserved bits

uint32_t rsvd1 : 30;

uint32_t _reserved_2 : 2; // HW ctrl reserved bits

};

Table 6. Load Library – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REQUEST |

| type | Global::LOAD_LIBRARY |

| lib_id | Identifier of the library assigned by the management service at runtime. Numbering should be simple and starts from 1 for the first library, incremented by 1 for each subsequently loaded library. |

| dma_id | Not used in S1000 Firmware. |

Input Data

None.

Reply Message Control Header

struct Bits

{

uint32_t status : IXC_STATUS_BITS;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 7. Load Multiple Modules – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REPLY |

| type | Global::LOAD_LIBRARY |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_ERROR_INVALID_PARAM ADSP_IPC_OUT_OF_MEMORY ADSP_IPC_INVALID_TARGET_ADDRESS ADSP_IPC_UNTRUSTED_PUBLIC_KEY ADSP_IPC_INVALID_SIGNATURE |

Output Data

None.

Init Instance

The management service sends this message to create a module instance. The new instance is a child element of the pipeline, and is identified by the ppl_id specified by the management service.

The module_id should be set to an index of the module entry in the FM Image Manifest.

The instance_id should be one of the 0..ModuleEntry.max_instance_count defined in the FM Image Manifest.

Initial configuration of the module instance is provided by the management service in the param_data array. The size of the array is specified in param_block_size field of the message header.

For details on module-specific initial configuration parameters, see Section 5.6, “Module Configuration”.

Request Message Control Header

struct Bits

{

uint32_t module_id : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t param_block_size : 16;

uint32_t ppl_instance_id : 8;

uint32_t core_id : 4;

uint32_t proc_domain : 1;

uint32_t rsvd1 : 1;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 8. Init Instance – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| Rsp | Msg::MSG_REQUEST |

| type | ModuleMsg::INIT_INSTANCE |

| instance_id | ID of module instance assigned by the management service (if it exists) |

| module_id | ID of module (0-based index of the module entry in the FM Image Manifest) |

| proc_domain | Module’s target processing domain. Either Low Latency (0) or Data Processing (1). |

| core_id | ID of core that instance will run on |

| ppl_instance_id | ID of module instance’s parent pipeline |

| param_block_size | Size of Data::param_data[] (in dwords) |

Input Data

struct Data

{

uint32_t param_data[0];

};

The actual size of param_data is specified by the param_block_size field of the control header.

Reply Message Control Header

Standard MsgReply is sent back.

Table 9. Init Instance – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REPLY |

| type | ModuleMsg::INIT_INSTANCE |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_MOD_INVALID_ID ADSP_IPC_MOD_INST_INVALID_ID ADSP_IPC_CORE_INVALID_ID ADSP_IPC_OUT_OF_MEMORY ADSP_IPC_MOD_INST_EXISTS ADSP_IPC_MOD_NOT_INITIALIZED |

Output Data

No additional output data.

Module Config Set

Using the Module Config Set command, the management service (if it exists) may send a parameter that fits into the header, packed with the parameter ID. Larger parameters require fragmentation and a series of Large Config Set commands.

For details on module specific runtime parameters, see “Module Configuration”.

Request Message Control Header

struct Bits

{

uint32_t module_id : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t param_id_data : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 10. Module Config Set – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REQUEST |

| type | ModuleMsg::MODULE_CONFIG_SET |

| instance_id | ID of module instance assigned by the management service (if it exists) |

| module_id | ID of module (0-based index of the module entry in the FM Image Manifest) |

| param_id_data |

Specifies both ID of the parameter, defined by the module and value of the parameter. It is up to the module how to distribute bits to ID and value of the parameter. If there are more bits required than available to value, then Input Data may be used to pass the value. |

Input Data

None

Reply Message Control Header

Standard MsgReply is sent back.

Table 11. Module Config Set – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REPLY |

| type | ModuleMsg::MODULE_CONFIG_SET |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID ADSP_IPC_INVALID_CONFIG_PARAM_ID ADSP_IPC_INVALID_CONFIG_DATA_LEN |

Output Data

There is no output data.

Module Config Get

Symmetric to the Module Config Set.

Reply Message Control Header

struct Bits

{

uint32_t status : IXC_STATUS_BITS;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t param_id_data : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 12. Module Config Get – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REPLY |

| type | ModuleMsg::MODULE_CONFIG_GET |

| param_id_data | Value of this field may be changed by the module if parameter value fits into the available bits, or stay intact if the value is copied to the Output Data. |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID ADSP_IPC_INVALID_CONFIG_PARAM_ID |

Output Data

None.

Large Config Set

Using the Large Config Set command, the management service may send configuration data that cannot fit into Module Config Set.

Note All documentation in this section applies to the symmetric Large Config Get as well.

The management service may send internally defined configuration parameters declared by Intel modules. The format of the message payload is module-specific and agreed between the management service and the module.

However the Large Config Set can be also used to tunnel parameters coming through Module Configuration API. Then, the large_param_id is set to APPLICATION_PARAM (formerly known as VENDOR_CONFIG_PARAM), with the valuE 0xFF. The message payload is populated with one or more configuration parameters submitted to the management service by a client software component. The firmware reads the parameters one by one and passes them to the addressed module instance. The structure of a single external parameter transported inside message data appears as follows:

Syntax

struct ModConfParam

{

uint32_t param_id;

uint32_t param_size;

uint32_t param_data[ceil(param_size/sizeof(uint32_t))];

};

Members

param_id

ID of the parameter, transparent to FW, passed to the module’s configuration routine.

param_size

Size of the param_data, specified in bytes.

param_data

Parameter data.

Note Multiple tunneled parameters cannot span across multiple messages. They must fit into a single request/response pair. Sending a series of Large Config Set is allowed for a single parameter payload (still tunneled using APPLICATION_PARAM).

Request Message Control Header

struct Bits

{

uint32_t module_id : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t data_off_size : 20;

uint32_t large_param_id : 8;

uint32_t final_block : 1;

uint32_t init_block : 1;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 13. Large Config Set – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REQUEST |

| type | ModuleMsg::LARGE_CONFIG_SET |

| instance_id | ID of module instance assigned by the management service (if it exists) |

| module_id | ID of module (0-based index of the module entry in the FM Image Manifest) |

| init_block | Indicates whether this is the first block |

| final_block | Indicates whether this is the final block |

| large_param_id |

ID of the parameter. |

| data_off_size |

In case of the first data fragment (init_block = 1) this field specifies total size of the parameter (in bytes). In case of subsequent data fragments it specifies offset (in bytes) of the fragment within the fragment blob. |

Input Data

If large_param_id is set to APPLICATION_PARAM, the message data contains an array of module configuration parameters.

struct Data

{

ModConfParam param[];

};

Otherwise, the message data contains a chunk of parameter’s value.

struct Data

{

uint32_t param_data[];

};

Reply Message Control Header

Standard MsgReply is sent back.

Table 14. Large Config Set – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REPLY |

| type | ModuleMsg::LARGE_CONFIG_SET |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID ADSP_IPC_INVALID_CONFIG_PARAM_ID ADSP_IPC_INVALID_CONFIG_DATA_LEN ADSP_IPC_LARGE_CONFIG_SET_ERROR |

Output Data

If the returned status is set to ADSP_IPC_CONFIG_SET_ERROR, the message data specifies the index of the failed parameter and the vendor-specific error code returned by the module instance.

struct Data

{

uint32_t failed_param_index;

uint32_t vendor_error_code;

};

Large Config Get

This message is set by the management service (if it exists) to retrieve one or more configuration parameters from specified module instance.

If the Large Config Get is used to tunnel parameters requested through Module Configuration API, the message payload is expected to contain an array of parameter descriptors in the following format:

Syntax

struct ModConfParamGet

{

uint32_t param_id;

uint32_t param_max_size; // in bytes

};

Members

param_id

ID of the parameter to retrieve, transparent to FW, passed to the module’s configuration API.

param_max_size

Maximum size of the parameter data to be retrieved (in bytes).

Note The previous reference to tunneling multiple vendor parameters within a single request/response pair in the Large Config Set documentation applies symmetrically to the Large Config Get. The total size of param_max_size, specified in the request, must not exceed IPC_UPLINK_MAILBOX_SIZE (as retrieved by the Get ADSP Properties IPC message).

Request Message Control Header

struct Bits

{

uint32_t module_id : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t data_off_size : 20;

uint32_t large_param_id : 8;

uint32_t final_block : 1;

uint32_t init_block : 1;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 15. Large Config Get – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REQUEST |

| type | ModuleMsg::LARGE_CONFIG_GET |

| instance_id | ID of module instance assigned by the management service (if it exists) |

| module_id | ID of module (0-based index of the module entry in the FM Image Manifest) |

| init_block | Indicates whether this is the first block |

| final_block | Indicates whether this is the final block |

| large_param_id |

ID of the parameter. |

| data_off_size |

In case of the first data fragment (init_block = 1) this field specifies total size (in bytes) of message data containing array of parameter specifiers. In case of subsequent data fragments it specifies offset (in bytes) of the fragment within the fragment blob. |

Input Data

If large_param_id is set to APPLICATION_PARAM, the message data of the first command in the series contains an array of parameter specifiers:

struct Data

{

ModConfParamGet param_get[];

};

Otherwise there is no input data.

Reply Message Control Header

struct Bits

{

uint32_t status : IXC_STATUS_BITS;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t data_off_size : 20;

uint32_t large_param_id : 8;

uint32_t final_block : 1;

uint32_t init_block : 1;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 16. Large Config Get – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REPLY |

| type | ModuleMsg::LARGE_CONFIG_GET |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID ADSP_IPC_INVALID_CONFIG_PARAM_ID ADSP_IPC_LARGE_CONFIG_GET_ERROR |

Output Data

If large_param_id is set to APPLICATION_PARAM, the message data contains an array of module configuration parameters.

struct Data

{

ModConfParam param[];

};

If the firmware failed to retrieve one of vendor-specific parameters, the status is set to ADSP_IPC_CONFIG_GET_ERROR, and the message data contains the following information:

struct Data

{

uint32_t failed_param_index;

uint32_t vendor_error_code;

};

If large_param_id is set to one of the Intel internal parameter IDs, the parameter data is copied directly to the response data buffer.

struct Data

{

uint32_t param_data[];

};

Bind/Unbind

The management service sends the Bind IPC message to connect two module instances and create a data processing path between them.

The Unbind IPC message is sent to destroy a connection between two module instances (belonging to different pipelines) that were created previously with a Bind call.

Note When both module instances are parts of the same pipeline, firmware ignores Unbind IPC because firmware does not support changing the internal topology of a pipeline during runtime. The only way to change pipeline topology is to delete the whole pipeline and create it in modified form.

Request Message Control Header

struct Bits

{

uint32_t module_id : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t dst_module_id : 16;

uint32_t dst_instance_id : 8;

uint32_t dst_queue : 3;

uint32_t src_queue : 3;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 17. Bind/Unbind – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REQUEST |

| type |

ModuleMsg::BIND, or |

| instance_id | ID of source module instance assigned by the management service (if it exists) |

| module_id | ID of source module (0-based index of the module entry in the FM Image Manifest) |

| src_queue | ID of source queue (pin). |

| dst_queue | ID of destination queue (pin). |

| dst_instance_id | ID of destination module instance to be bound/unbound with the source module instance. |

| dst_module_id | ID of destination module |

Input Data

There is no input data.

Reply Message Control Header

Table 18. Bind / Unbind – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REPLY |

| type |

ModuleMsg::BIND, or |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID ADSP_IPC_QUEUE_INVALID_ID ADSP_IPC_QUEUE_DST_INVALID_ID ADSP_IPC_BIND_UNBIND_DST_SINK_UNSUPPORTED |

Output Data

There is no output data.

Enter Module Restore

This message is sent by the management service (if it exists) to indicate that it is beginning to restore the module instance state. This message is expected to be followed by series of Large/Module Config messages. Once all configuration parameters are sent to the module instance, the management service sends the Exit Module Restore message.

On Enter Module Restore, the target module instance performs the following actions:

- Retrieves the state (enabled or disabled) of the internal logic and stores it internally. If the state cannot be retrieved, it is set to ‘enabled’ by default.

- “Disables” processing logic (that is, triggers pass through mode).

- Activates parameter filtering. The filtering means that enable/disable parameter is not applied. Instead, its value is cached (overriding the value retrieved earlier). All other parameters are applied instantly.

On Exit Module Restore, the target module instance applies the cached value of the enable/disable parameter and exits parameter filtering mode.

Request Message Control Header

struct Bits

{

uint32_t module_id : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 19. Enter Module Restore – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REQUEST |

| type | ModuleMsg::ENTER_MODULE_RESTORE |

| instance_id | ID of module instance assigned by the management service (if it exists) |

| module_id | ID of module (0-based index of the module entry in the FM Image Manifest) |

Input Data

None

Reply Message Control Header

Standard MsgReply is sent back.

Table 20. Enter Module Restore – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| Rsp | Msg::MSG_REPLY |

| Type | ModuleMsg::ENTER_MODULE_RESTORE |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID |

Output Data

None

Exit Module Restore

This message is sent by the management service (if it exists) to complete the module restore sequence (see Section “Enter Module Restore”).

Request Message Control Header

struct Bits

{

uint32_t module_id : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 21. Exit Module Restore – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REQUEST |

| type | ModuleMsg::EXIT_MODULE_RESTORE |

| instance_id | ID of module instance assigned by the management service (if it exists) |

| module_id | ID of module (0-based index of the module entry in the FM Image Manifest) |

Input Data

None.

Reply Message Control Header

Standard MsgReply is sent back.

Table 22. Exit Module Restore – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::MODULE_MSG |

| rsp | Msg::MSG_REPLY |

| type | ModuleMsg::EXIT_MODULE_RESTORE |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID |

Output Data

None.

Pipeline Management IPC Messages

Create Pipeline

The management service sends this message to create a new pipeline inside the firmware.

The pipeline priority assigned by the caller determines the priority of tasks associated with the pipeline’s module instances. A pipeline with priority 0 is executed before a pipeline with priority 1. The management service may assign priority 0 to the decode pipeline and priority 1 to the mixer pipeline to make sure that the decode pipeline’s low latency part runs first and delivers data to the low latency part of the mixer pipeline. The low latency part of the mixer pipeline, in turn, delivers data to the link within a single system tick.

Memory Requirements

Before sending this request, the management service (if it exists) must estimate the amount of memory that the pipeline will require to allocate its object and other associated buffers, as follows:

- Pipeline object

- Queues that are persistent (that is, queues attached to a DP task at least at one end)

- Buffers allocated for instances of built-in child modules, and optionally their additional buffers

- Task objects created for LL and DP module instances associated with the pipeline

The estimated memory size, expressed in pages, is specified by the management service in the ppl_mem_size parameter.

Table 23. Pipeline Memory Requirements

| Component | Size (bytes) | Remarks |

|---|---|---|

| Pipeline object | 320 | |

| Child module instance list item | 12 | Per each child module instance. |

|

Data queue buffer + data queue object |

2 * max(IBS,OBS) + min(IBS,OBS) or 3 * max(IBS,OBS) + 92 |

Per each binding between child module instances where at least one module instance is created in DP domain. Data queue buffer is extended to 3*max(IBS,OBS) if at least one module instance requires extended queue. |

| LL task object | 40 | One per chain of contiguous child modules running in LL domain. |

|

DP task object + DP task list item + DP task stack |

84 + 8 [+ <size specified in the Manifest>] |

One per each child module running in DP domain. Module descriptor contained by the FM Image Manifest specifies size of the stack (in bytes) required by the module instance (see Note1 below) |

|

DP task list + list collection item |

12 + 8 |

One per chain of contiguous child modules running in DP domain. |

Request Message Control Header

struct Bits

{

uint32_t ppl_mem_size : 11;

uint32_t ppl_priority : 5;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t lp : 1;

uint32_t rsvd1 : 29;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 24. Create Pipeline – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REQUEST |

| type | Global::CREATE_PIPELINE |

| instance_id | ID of the pipeline assigned by the management service |

| ppl_priority | Pipeline priority. One of 0..7. |

| ppl_mem_size | Size of memory (in pages) required for pipeline and its data. |

| lp |

Indicates whether the pipeline should kept on running in Low-Power mode. The management service should set this flag to 1 for a WOV pipeline. |

Input Data

There is no input data.

Reply Message Control Header

Standard MsgReply is sent back.

Table 25. Create Pipeline – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REPLY |

| type | Global::CREATE_PIPELINE |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID ADSP_IPC_OUT_OF_MEMORY ADSP_IPC_PIPELINE_ALREADY_EXISTS |

Output Data

There is no output data.

Delete Pipeline

The management service sends this IPC message to delete a pipeline from ADSP memory. All module instances and tasks that are associated with the pipeline are deleted also.

For this command to complete successfully, there must be no existing binding from any pipeline’s module instance to another pipeline.

Request Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 26. Delete Pipeline – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REQUEST |

| type | Global::DELETE_PIPELINE |

| instance_id | ID of the pipeline assigned by the management service |

Input Data

There is no input data.

Reply Message Control Header

Standard MsgReply is sent back.

Table 27. Delete Pipeline – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REPLY |

| type | Global::DELETE_PIPELINE |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID ADSP_IPC_INVALID_RESOURCE_STATE |

Output Data

There is no output data.

Set Pipeline State

Note Task Creation/Registration is part of first state transition. There is no other dedicated call for this.

Request Message Control Header

struct Bits

{

uint32_t state : 16;

uint32_t ppl_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t multi_ppl : 1;

uint32_t rsvd1 : 29;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 28. Set Pipeline State – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REQUEST |

| type | Global::SET_PIPELINE_STATE |

| ppl_id | ID of the pipeline assigned by the management service. If multi_ppl is set to 1 this field is ignored and list of pipelines’ identifiers is read from the message payload. |

| state |

Target pipeline state. One of: 3 – PAUSED, 4 – RUNNING, 5 – END_OF_STREAM. |

| multi_ppl |

Indicates if state should be set to a single pipeline or multiple pipelines. 0 – single pipeline specified by ppl_id field, 1 – multiple pipelines specified by the payload. |

Input Data

The input data is optional. It occurs only when multi_ppl is set to 1.

struct Data

{

pipelines_count;

ppl_id[1]; // actual size specified by pipelines_count

};

Reply Message Control Header

Standard MsgReply is sent back.

Table 29. Set Pipeline State – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REPLY |

| type | Global::SET_PIPELINE_STATE |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_PIPELINE_NOT_EXIST ADSP_IPC_PIPELINE_STATE_NOT_SET ADSP_IPC_INVALID_REQUEST |

Output Data

There is no output data.

Get Pipeline State

This IPC message is sent to the firmware to retrieve a pipeline state.

Request Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t instance_id : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 30. Get Pipeline State – Request Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REQUEST |

| type | Global::GET_PIPELINE_STATE |

| instance_id | ID of the pipeline assigned by the management service |

Input Data

There is no input data.

Reply Message Control Header

struct Bits

{

uint32_t status : IXC_STATUS_BITS;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t state : 5;

uint32_t rsvd1 : 25;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 31. Get Pipeline State – Reply Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_REPLY |

| type | Global::GET_PIPELINE_STATE |

| status |

ADSP_IPC_SUCCESS ADSP_IPC_INVALID_RESOURCE_ID |

| state |

Pipeline state. One of: |

Output Data

There is no output data.

Notifications

FW Ready Notification

This notification is reported by the Base FW immediately after the initialization phase completes.

Notification Message Control Header

struct Bits

{

uint32_t rsvd2 : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 32. FW Ready Notification – Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::FW_READY |

Input Data

There is no input data.

Voice Cmd Notification

This notification is reported by the WOV module on key phrase detection.

Notification Message Control Header

struct Bits

{

uint32_t word_id : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t sv_score : 16

uint32_t rsvd1 : 14;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 33. Voice Cmd Notification –Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::PHRASE_DETECTED |

| word_id | ID of detected keyword |

| sv_score | Final speaker verification score in range of 0..8192. |

Input Data

Depending on the running WOV implementation, optional data may be provided. The data may be provided as a BLOB to a client by the management service.

Intel® Wake on Voice (Intel® WOV)

struct Data

{

uint16_t kpd_score;

uint16_t reserved;

};

Refer to the Intel® WOV documentation for details.

MCPS Budget Violation Notification

This notification is reported by the resource verifier after either LL or DP task finished processing and measured number of consumed cycles exceeded number declared in associated module instance configuration sent by the management service along with module instance initialization request.

The module stores the peak value of cycles consumed reported to the management service during runtime. If the measured value is less than reported peak, then notification is not sent even if the current measurement exceeds the budget.

Notification Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 34. MCPS Budget Violation Notification –Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::RESOURCE_EVENT |

Input Data

struct Data

{

uint32_t resource_type;

uint32_t resource_id;

uint32_t event_type;

uint32_t event_data[6];

};

Table 35. MCPS Budget Violation Notification –Data

| Field | Value |

|---|---|

| resource_type | Message::ResourceType::MODULE_INSTANCE |

| resource_id | Module ID (MS word) + Module Instance ID (LS word) |

| event_type | Message::ResourceEventType::BUDGET_VIOLATION |

| event_data[0] | Cycles consumed by last processing data routine. |

Mixer/Gateway Underrun Detected Notification

This notification is sent by the mixer or copier attached to a gateway on stream underrun detection.

The frequency of sending this notification by the mixer depends on the MixIn settings (see Section “Runtime Parameters”).

Notification Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 36. Mixer/Gateway Underrun Detected Notification – Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::RESOURCE_EVENT |

Input Data

struct Data

{

uint32_t resource_type;

uint32_t resource_id;

uint32_t event_type;

uint32_t event_data[6];

};

Table 37. Mixer/Gateway Underrun Detected Notification – Data

| Field | Value |

|---|---|

| resource_type | Message::ResourceType::PIPELINE |

| resource_id | Pipeline ID |

| event_type |

Message::ResourceEventType::MIXER_UNDERRUN_DETECTED or Message::ResourceEventType::GATEWAY_UNDERRUN_DETECTED |

Gateway Overrun Detected Notification

This notification is sent by the copier attached to a gateway on stream overrun detection.

Notification Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 38. Gateway Overrun Detected Notification – Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::RESOURCE_EVENT |

Input Data

struct Data

{

uint32_t resource_type;

uint32_t resource_id;

uint32_t event_type;

uint32_t event_data[6];

};

Table 39. Gateway Overrun Detected Notification – Data

| Field | Value |

|---|---|

| resource_type | Message::ResourceType::PIPELINE |

| resource_id | Pipeline ID |

| event_type | Message::ResourceEventType::GATEWAY_OVERRUN_DETECTED |

Process Data Error Notification

Note Formerly known as DECODER_ERROR.

This notification is sent by a shim of module instance on error raised by data processing function.

Notification Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 40. Process Data Error Notification – Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::RESOURCE_EVENT |

Input Data

struct Data

{

uint32_t resource_type;

uint32_t resource_id;

uint32_t event_type;

uint32_t event_data[6];

};

Table 41. Process Data Error Notification – Data

| Field | Value |

|---|---|

| resource_type | Message::ResourceType::MODULE_INSTANCE |

| resource_id | Module ID (MS word) + Module Instance ID (LS word) |

| event_type | Message::ResourceEventType::PROCESS_DATA_ERROR |

| event_data[0] | Set to the error code raised by the data processing function. If there is 3rd party IP, it is set to its native error code returned by the 3rd party library. |

End of Stream Notification

This notification is a variant of underrun notification. It is reported by the mixer immediately after the last sample from a stream, marked by the management service as EoS pending, is sent to the link.

Data::event_data[0] is set to 1 to indicate that this is EoS Underrrun.

Log Buffer Status Notification

This notification is reported by the tracing facility when the write pointer passes either half of the trace buffer (of either core).

Notification Message Control Header

struct Bits

{

uint32_t core_id : 4;

uint32_t rsvd0 : 12;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 42. Log Buffer Status Notification – Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::LOG_BUFFER_STATUS |

| core_id | ID of DSP core that crossed its buffer boundary. |

Input Data

There is no input data.

Timestamp Captured Notification

This notification is reported by a gateway management service when timestamping request sent by the management service (if it exists) is completed and timestamping data is available.

Node ID of the gateway is specified in the event data.

Notification Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 43. Timestamp Captured Notification – Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::TIMESTAMP_CAPTURED |

Input Data

Syntax

struct Data

{

uint32_t module_instance_id;

uint32_t node_id;

uint32_t timestamp_data[7];

};

Members

module_instance_id

Module ID (MS word) + module instance ID (LS word).

node_id

ID of gateway (see ConnectorNodeId).

timestamp_data

Value of <ifc>_ISOFFSET (32 bits),

Value of <ifc>_LOCAL_SAMPLE (64 bits),

Value of <ifc>_LOCAL_WALCLK (64 bits),

Value of <ifc>_Time Stamp Counter Captured (64 bits).

Refer to DSP Timestamping Registers for detailed description.

Stream Data Segment Notification

This notification is reported by an instance of a Copier when the amount of data transferred through an attached Gateway exceeds the configured data segment size.

Event data contains the linear position (in bytes) of the segment beginning and end, where the linear counter starts from the last gateway reset.

Notification Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 44. Stream Data Segment Notification – Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::RESOURCE_EVENT |

Input Data

struct Data

{

uint32_t resource_type;

uint32_t resource_id;

uint32_t event_type;

uint32_t event_data[6];

};

Table 45. Stream Data Segment Notification – Data

| Field | Value |

|---|---|

| resource_type | Message::ResourceType::PIPELINE |

| resource_id | Pipeline ID |

| event_type | Message::ResourceEventType::STREAM_DATA_SEGMENT |

| event_data[0] | Copier instance ID. |

| event_data[1] | Gateway Node ID. |

| event_data[2-3] | 64-bit linear position (in bytes) of the segment beginning. Linear counter starts from the last gateway reset. |

| event_data[4-5] | 64-bit linear position (in bytes) of the segment end. |

Buffering Mode Changed Notification

This notification is reported by an instance of KPBUF once buffered data was transferred through the speech pipeline and the buffer is freed. The management service (if it exists) should use this information to update its internally maintained FW resource allocation record.

Notification Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 46. Buffering Mode Changed Notification – Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::RESOURCE_EVENT |

Input Data

struct Data

{

uint32_t resource_type;

uint32_t resource_id;

uint32_t event_type;

uint32_t event_data[6];

};

Table 47. Buffering Mode Changed Notification – Data

| Field | Value |

|---|---|

| resource_type | Message::ResourceType::MODULE_INSTANCE |

| resource_id | Module ID (MS word) + Module Instance ID (LS word) |

| event_type | Message::ResourceEventType::BUFFERING_MODE_CHANGED |

| event_data[0] | New buffering mode (see KPBUF’s BUFFERING_MODE parameter documentation). |

Module Callback Notification

This notification is reported by a module instance when it encapsulates a library that requires a callback to report events to a software component residing on the host.

Notification Message Control Header

struct Bits

{

uint32_t rsvd0 : 16;

uint32_t notif_type : 8;

uint32_t type : 5;

uint32_t rsp : 1;

uint32_t msg_tgt : 1;

uint32_t _busy : 1;

uint32_t rsvd1 : 30;

uint32_t _done : 1;

uint32_t _error : 1;

};

Table 48. Module Callback Notification – Parameters

| Field | Value |

|---|---|

| msg_tgt | Msg::FW_GEN_MSG |

| rsp | Msg::MSG_NOTIFICATION (0) |

| type | Global::NOTIFICATION |

| notif_type | Notification::MODULE_CALLBACK_EVENT |

Input Data

Syntax

struct Data

{

uint32_t module_instance_id;

uint32_t event_id;

uint32_t event_data_size;

uint32_t event_data[1];

};

Members

module_instance_id

Module ID (MS word) + Module Instance ID (LS word)

event_id

Module’s specific event ID.

event_data_size

Size of event_data array in bytes. May be set to 0 in case there is no data.

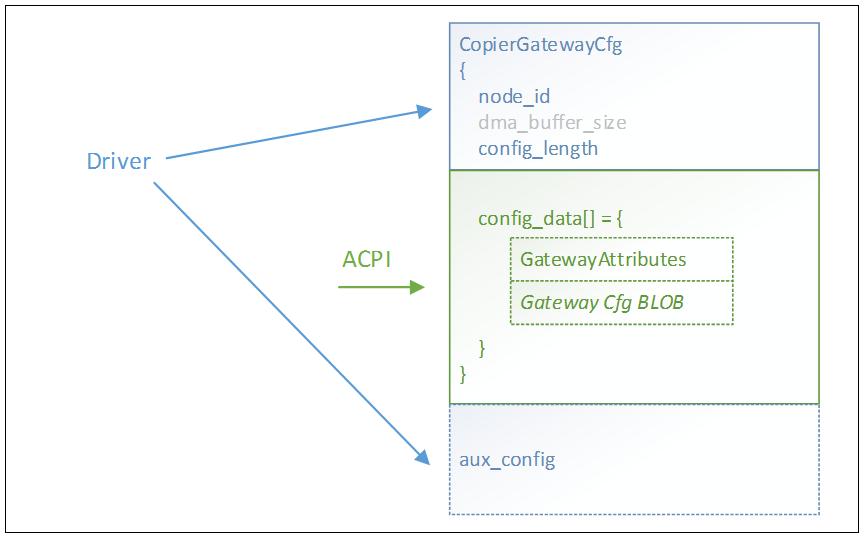

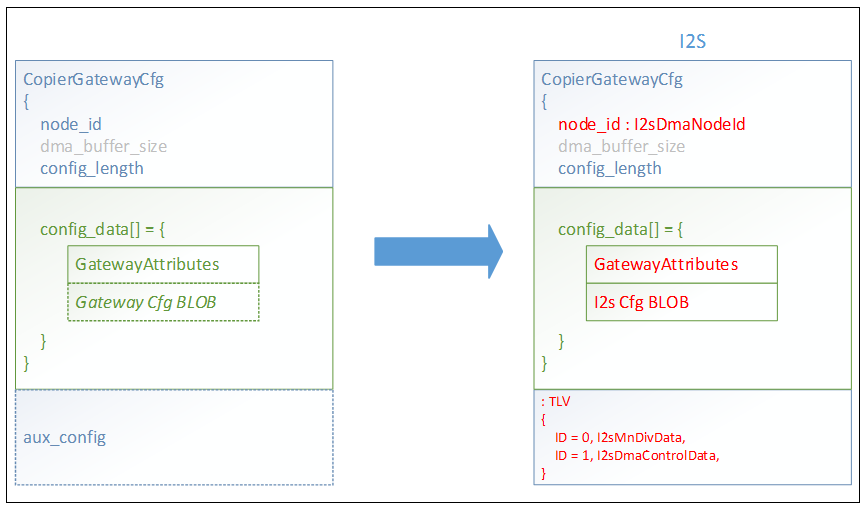

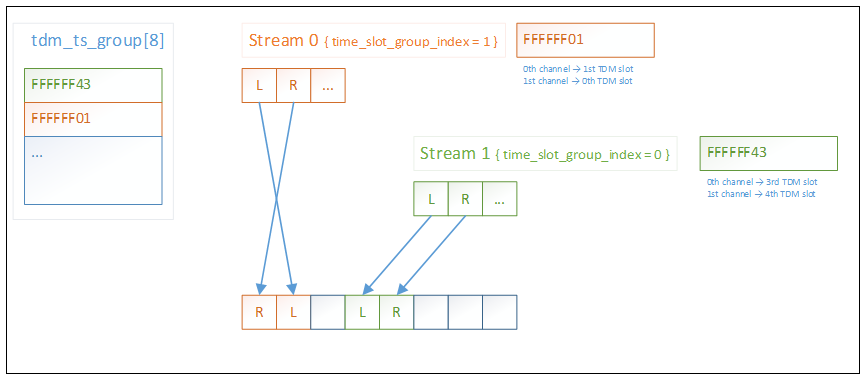

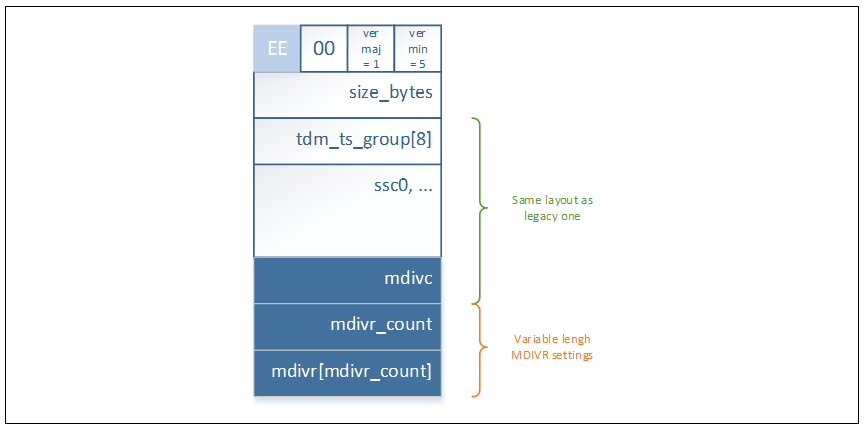

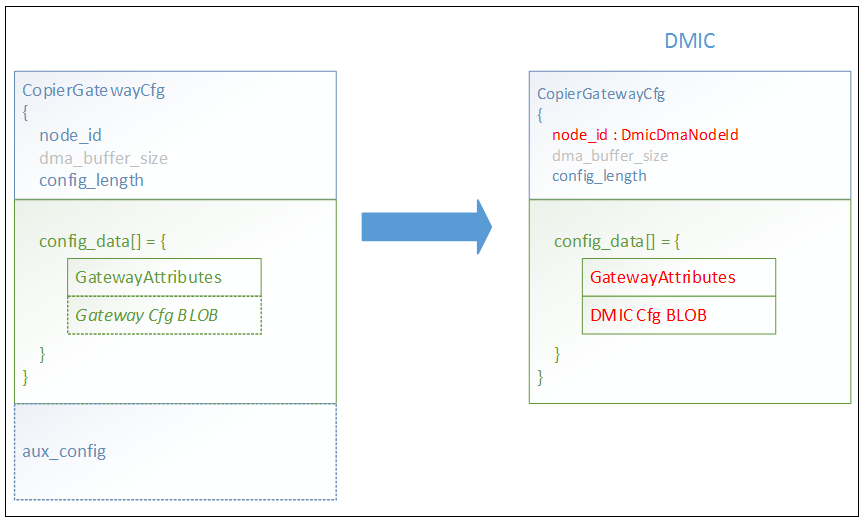

event_data