仅对英特尔可见 — GUID: eis1414475131951

Ixiasoft

仅对英特尔可见 — GUID: eis1414475131951

Ixiasoft

4.3.10. 不同的输入和输出宽度

如果宽度比率有效,那么DCFIFO_MIXED_WIDTHS功能支持不同的写输入数据和读输出数据宽度。如果输入和输出数据宽度的组合产生无效比率,则FIFO参数编辑器将提示错误消息。支持的宽度比率为2的幂,并取决于RAM。

IP核支持具有狭窄读端口的宽阔写端口,反之亦然。下表列出了 Intel® Agilex™ 器件当前支持的混合宽度比率:

| 器件系列 | 有效宽度比率 |

|---|---|

| Intel® Agilex™ | 1, 2, 4, 8, 16和32 |

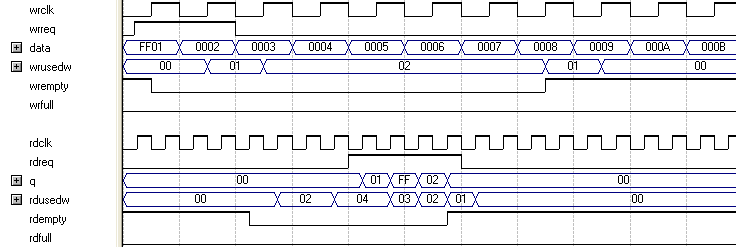

在此实例中,读端口的运行频率是写端口的两倍。将两个16-bit字写入到FIFO缓存中,wrusedw标记增加到2,rusedw标记增加到4。四个8-bit读操作清空FIFO缓存。读取从写入的16-bit字的最低有效8比特开始,然后是最高有效8比特。

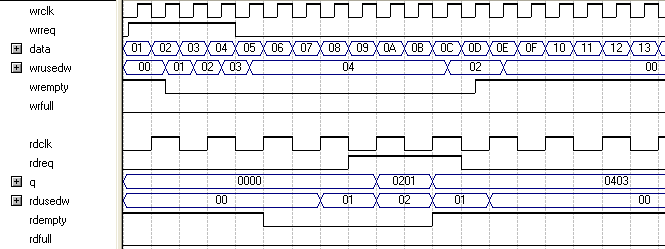

在此实例中,读端口的工作频率为写端口的一半。将四个8-bit字写入到FIFO缓存中,wrusedw标记增加到4,rusedw标记增加到2。两个16-bit读操作清空FIFO。写入的第一个和第二个8-bit字分别等于16-bit输出字的LSB和MSB。rdempty信号保持置位状态,直到在狭窄写端口上写入足够的字以填满宽阔读端口上的整个字为止。