# Intel<sup>®</sup> Technology Journal

**MARCH 2009**

# Advances in Embedded Systems Technology

# INTEL® TECHNOLOGY JOURNAL ADVANCES IN EMBEDDED SYSTEM TECHNOLOGY

| Ar | ticles                                                                                                                                                                              |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                                                                                     |

| 01 | Performance Analysis of the Intel® System Controller Hub (Intel® SCH) US15W6                                                                                                        |

| 02 | Configuring and Tuning for Performance on Intel <sup>®</sup> 5100 Memory Controller<br>Hub Chipset Based Platforms                                                                  |

| 03 | Solid State Drive Applications in Storage and Embedded Systems 29                                                                                                                   |

| 04 | Fanless Design for Embedded Applications 54                                                                                                                                         |

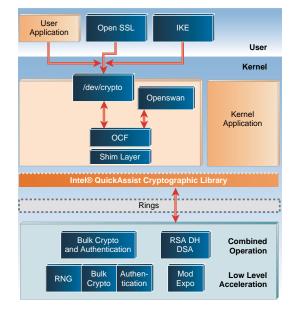

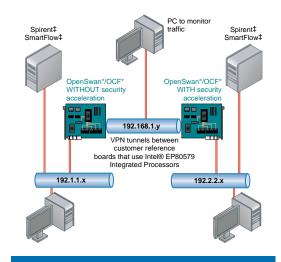

| 05 | Security Acceleration, Driver Architecture and Performance Measurements for Intel <sup>®</sup><br>EP80579 Integrated Processor with Intel <sup>®</sup> QuickAssist Technology       |

| 06 | Methods and Applications of System Virtualization Using Intel <sup>®</sup> Virtualization Technology (Intel <sup>®</sup> VT)                                                        |

| 07 | Building and Deploying Better Embedded Systems with Intel <sup>®</sup> Active Management<br>Technology (Intel <sup>®</sup> AMT)                                                     |

| 08 | Implementing Firmware for Embedded Intel <sup>®</sup> Architecture Systems: OS-Directed Power<br>Management (OSPM) through the Advanced Configuration and Power Interface (ACPI) 96 |

| 09 | A Real-Time HPC Approach for Optimizing Intel Multi-Core Architectures 108                                                                                                          |

| 10 | Digital Signal Processing on Intel <sup>®</sup> Architecture 122                                                                                                                    |

| 11 | IA-32 Features and Flexibility for Next-Generation Industrial Control 146                                                                                                           |

| 12 | Low Power Intel® Architecture Platform for In-Vehicle Infotainment 160                                                                                                              |

### Intel Technology Journal

Publisher Richard Bowles Managing Editor David King

Program Manager Marleen Lundy Technical Editor David Clark Content Architect Todd Knibbe

Technical Illustrators Richard Eberly Margaret Anderson

#### **Content Design**

Peter Barry Marcie M Ford Todd Knibbe Atul Kwatra

#### **Technical and Strategic Reviewers**

Steven Adams Peter Barry Mark Brown Tom Brown Jason M Burris Lynn A Comp John Cormican Pete Dice Richard Dunphy Jerome W Esteban Dennis B Fallis Al Fazio Rajesh Gadiyar Javier Galindo Gunnar Gaubatz Byron R Gillespie Marc A Goldschmidt Knut S Grimsrud Chris D Lucero Lori M Matassa

Michael G Millsap Udayan Mukherjee Staci Palmer Michael A Rothman Lindsey A Sech Shrikant M Shah Brian J Skerry Durgesh Srivastava Edwin Verplanke Chad V Walker

#### Intel Technology Journal

Copyright © 2009 Intel Corporation. All rights reserved. ISSN: 1535-864X ISBN 978-1-934053-21-8 Intel Technology Journal Volume 13, Issue 1

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4744. Requests to the Publisher for permission should be addressed to the Publisher, Intel Press, Intel Corporation, 2111 NE 25th Avenue, JF3-330, Hillsboro, OR 97124-5961. E mail: intelpress@intel.com.

This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold with the understanding that the publisher is not engaged in professional services. If professional advice or other expert assistance is required, the services of a competent professional person should be sought. Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Intel may make changes to specifications, product descriptions, and plans at any time, without notice.

Third-party vendors, devices, and/or software are listed by Intel as a convenience to Intel's general customer base, but Intel does not make any representations or warranties whatsoever regarding quality, reliability, functionality, or compatibility of these devices. This list and/or these devices may be subject to change without notice.

Fictitious names of companies, products, people, characters, and/or data mentioned herein are not intended to represent any real individual, company, product, or event.

Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel, the Intel logo, Celeron, Intel Centrino, Intel Core Duo, Intel NetBurst, Intel Xeon, Itanium, Pentium D, MMX, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>†</sup>Other names and brands may be claimed as the property of others.

This book is printed on acid-free paper. 🞯

Publisher: Richard Bowles Managing Editor: David King

#### Library of Congress Cataloging in Publication Data:

Printed in

10 9 8 7 6 5 4 3 2 1

First printing March 2009

# INTEL® TECHNOLOGY JOURNAL ADVANCES IN EMBEDDED SYSTEM TECHNOLOGY

| Ar | ticles                                                                                                                                                                              |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                                                                                     |

| 01 | Performance Analysis of the Intel® System Controller Hub (Intel® SCH) US15W6                                                                                                        |

| 02 | Configuring and Tuning for Performance on Intel <sup>®</sup> 5100 Memory Controller<br>Hub Chipset Based Platforms                                                                  |

| 03 | Solid State Drive Applications in Storage and Embedded Systems 29                                                                                                                   |

| 04 | Fanless Design for Embedded Applications 54                                                                                                                                         |

| 05 | Security Acceleration, Driver Architecture and Performance Measurements for Intel <sup>®</sup><br>EP80579 Integrated Processor with Intel <sup>®</sup> QuickAssist Technology       |

| 06 | Methods and Applications of System Virtualization Using Intel <sup>®</sup> Virtualization Technology (Intel <sup>®</sup> VT)                                                        |

| 07 | Building and Deploying Better Embedded Systems with Intel <sup>®</sup> Active Management<br>Technology (Intel <sup>®</sup> AMT)                                                     |

| 08 | Implementing Firmware for Embedded Intel <sup>®</sup> Architecture Systems: OS-Directed Power<br>Management (OSPM) through the Advanced Configuration and Power Interface (ACPI) 96 |

| 09 | A Real-Time HPC Approach for Optimizing Intel Multi-Core Architectures 108                                                                                                          |

| 10 | Digital Signal Processing on Intel <sup>®</sup> Architecture 122                                                                                                                    |

| 11 | IA-32 Features and Flexibility for Next-Generation Industrial Control 146                                                                                                           |

| 12 | Low Power Intel® Architecture Platform for In-Vehicle Infotainment 160                                                                                                              |

## FOREWORD

Pranav Mehta Sr. Principal Engineer & CTO Embedded & Communications Group Intel Corporation

"An embedded device is a differentiated compute platform that is either invisible, being part of a larger infrastructure, or predetermined to expose limited capabilities in deference to a dominant usage."

"The Intel multi-core processor architecture and related technologies ensure continuation of the performance treadmill famously articulated by Moore's Law, which is critical for the majority of embedded platforms that constitute the Internet infrastructure as new usage models involving video, voice, and data create an insatiable demand for network throughput and cost efficiency."

"So, what do you mean by an embedded device?" is a question I get asked frequently. Many in academia and industry alike have offered and debated versions of its definition. While many achieve varying degrees of admirable brevity, insight, and accuracy, often these definitions leave an impression that embedded devices are somewhat less capable, outdated technology. Having been associated with Intel's embedded products group for almost two decades, I find such characterizations lacking. Yes, embedded devices have their special requirements, from technical as well as business perspectives, but less capable technology is certainly not one of them. At the risk of inflaming the definition debate, here is my version as an Intel technologist: An embedded device is a differentiated compute platform that is either invisible, being part of a larger infrastructure, or predetermined to expose limited capabilities in deference to a dominant usage. Implicit in this definition are the notion of an embedded device having its unique requirements, its inconspicuous pervasiveness throughout infrastructures supporting modern lifestyle, as well as an allusion to the underlying platform capable of much more than what is exposed in service of a primary set of use functions.

This edition of Intel Technology Journal marks the intersection of several major trends and events in the embedded world. As eloquently articulated in the ITU paper Internet of Things, embedded devices appear poised to lead the next wave of evolution of the Internet as they add Internet connectivity as a key platform attribute. Against this backdrop, two groundbreaking technology innovations from Intel—Power efficient Intel® Core™ microarchitecture with an increasing number of cores and the introduction of the Intel® Atom<sup>™</sup> processor, both benefitting immensely from the breakthrough High-K/Metal gate process technology-create a unique opportunity to accelerate this embedded transformation with Intel® architecture. The Intel multi-core processor architecture and related technologies ensure continuation of the performance treadmill famously articulated by Moore's Law, which is critical for the majority of embedded platforms that constitute the Internet infrastructure as new usage models involving video, voice, and data create an insatiable demand for network throughput and cost efficiency. On the other hand, the Intel Atom processor opens up possibilities for a completely new class of ultra low power and highly integrated System-on-a-Chip (SoC) devices with Intel architecture performance that were unimaginable before.

Over the last several years, Intel's Embedded and Communications Group has introduced several products that achieve the best-in-class "power efficient performance" and push the boundaries of integration for SoC devices. We have done that while preserving the fundamental premise of Intel architecture—software scalability. Now, equipped with these new technologies and product capabilities, we are delighted to have the opportunity to accelerate the phenomenon of the embedded Internet.

While I am proud to offer technical articles from members of Intel ECG's technical team, I am equally proud to offer articles from developers who have embraced our embedded systems platforms and put them to use. Finally, I look forward to revisiting embedded systems technology in a few years' time. I believe that we will witness enormous progress over the years to come. "Finally, I look forward to revisiting embedded systems technology in a few years' time. I believe that we will witness enormous progress over the years to come."

# PERFORMANCE ANALYSIS OF THE INTEL® SYSTEM CONTROLLER HUB (INTEL® SCH) US15W

#### Contributor

Scott Foley Intel Corporation

#### **Index Words**

Intel<sup>®</sup> System Controller Hub US15W Intel<sup>®</sup> Atom<sup>™</sup> processor I/O performance analysis optimization

"The article provides an overview of the different use cases and their effects on I/O performance, including memory bandwidth utilization from video decoding applications."

#### Abstract

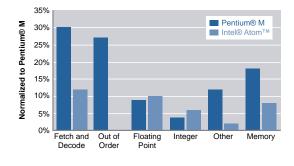

The platform comprising the Intel® Atom<sup>™</sup> processor and Intel® System Controller Hub (Intel® SCH) US15W has recently been introduced into the embedded systems marketplace, for a wide range of uses. And with this pairing, Intel now has an incredibly low power (<5W maximum thermal design power [TDP]) platform built on Intel® architecture. This compares favorably to other platforms, such as ones based on Intel® Core<sup>™</sup>2 Solo processors, which have processor TDP's alone of 5.5W. Given the wide range of applications this new platform encompasses though, some design tradeoffs are inevitable. Performance is a notable tradeoff, and the performance of the Intel SCH is a good example to look at.

Instead of looking into processing performance, this article takes a systematic look at the architecture of the Intel SCH US15W. It investigates the performance of the Intel SCH backbone and the effects that that backbone has on PCI Express\* (PCIe\*) bandwidth in particular. This includes not just empirical data, but also theoretical analysis of the Intel SCH internals. Furthermore, the article provides an overview of the different use cases and their effects on I/O performance, including memory bandwidth utilization from video decoding applications. With this knowledge in hand, platform, hardware, and software engineers can better design systems that work efficiently with the Intel Atom processor's low power offerings.

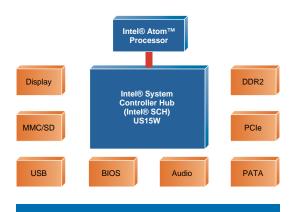

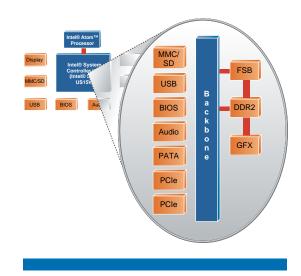

#### Intel<sup>®</sup> System Controller Hub (Intel<sup>®</sup> SCH) US15W Architecture

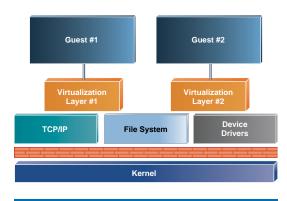

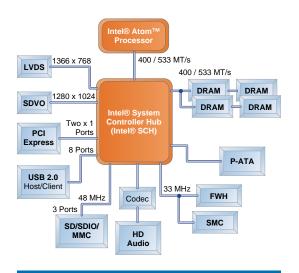

The Intel<sup>®</sup> System Controller Hub (Intel<sup>®</sup> SCH) US15W is the chipset used in small, low power Intel<sup>®</sup> Atom<sup>™</sup> processor-based platform designs. It connects the Intel Atom processor and various I/O devices to system memory. At the heart of the Intel SCH and any platform is the memory controller. All of the various peripherals are vying for its attention, as can be seen in Figure 1. The processor's Front Side Bus (FSB) is a constant consumer of memory bandwidth, as is the integrated graphics controller. These receive priority in the Intel SCH. Then comes everything else: USB, PATA, SDIO, PCIe, Audio, Legacy, and so on. Most of these devices have sporadic memory bandwidth needs. The possible exception would be PCI Express\* (PCIe\*), which we will discuss later. Before we understand how everything is connected though, we need to further understand the design goals of the Intel SCH.

#### **Tradeoffs**

Power, performance, size, features—these are just some of the things designers have to balance when designing a chipset like the Intel SCH US15W. Each of these metrics interoperates with the others, and must be carefully considered. With the Intel SCH, the balance has shifted significantly towards power optimization, with power to performance efficiency being the utmost importance.

Media applications, in particular, are given more of the power budget in this platform. Thus, graphics are given more bandwidth and higher priority to access memory. The processor, via the FSB, is also given more of the memory controller's time for running applications and/or performing software-based DSP functions and the like. The processor is the general purpose controller, and is expected to do most of the heavy lifting. Finally, the I/O devices were considered to typically require low to medium amounts of bandwidth and, as we will see, that is what they get.

Another requirement was to fit a large number of I/O types (features) in and still keep power low. To make a balance between features and power, tradeoffs must be made compared to more traditional Intel<sup>®</sup> architecture designs. The I/O devices' connection to the memory controller reflects as much. As this article will show, all the I/O devices on the Intel SCH run on two equally shared unidirectional busses called the backbone, which has less access to memory bandwidth than either the integrated graphics controller or the FSB. How much bandwidth? Each bus of the backbone has a little more than the original PCI bus could handle. But of course PCIe allows for higher bandwidths than that, right? To know for sure, let us take a look at how PCI Express\* works.

#### PCI Express\* (PCIe\*) Details

PCI Express, or PCIe, is a serialized/packetized implementation of the Peripheral Component Interconnect (PCI). While they share the same name and software concepts, the implementation of the two couldn't be more different. PCI is parallel while PCIe is serial; PCI has a shared bus while PCIe employs a switched point-topoint topology.

At a high level, PCIe looks a lot like a typical network stack. It has many of the same or similar layers as found in the OSI model for networked communications. Lower layers consist of physical transmission—the electrical/signaling aspects— and eventually progresses all the way up to transaction-based packets.

The transaction layer is responsible for all of the read/write transactions, or packets, implicit in data communication. And, among many other things, it also contains concepts for tracking buffer space. Technically this is done at a lower layer via Flow Control (FC) credits, but the concepts are very similar. These credits allow end points to know when to transmit data, and how much data they can safely transmit. They do this by updating each other on how much buffer space is available to the receiver. This eliminates wasted time and bandwidth by sending packets that cannot be accepted, and allows end points to speak to each other with a high degree of confidence.

"With the Intel SCH, the balance has shifted significantly towards power optimization, with power to performance efficiency being the utmost importance."

"To make a balance between features and power, tradeoffs must be made compared to more traditional Intel<sup>®</sup> architecture designs."

"PCIe looks a lot like a typical network stack. It has many of the same or similar layers." "Lanes are bidirectional serial interconnects (physically, two differential pairs) of a specific bandwidth."

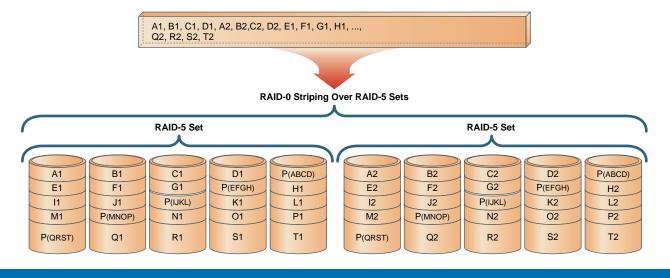

"Data is striped among all the possible lanes, much like with RAID-0 disk arrays or memory accesses to DIMMs with many DRAM devices." As we move further down the PCIe protocol stack, we see how the end points are actually connected. PCIe uses the concepts of links and lanes.

Lanes are bidirectional serial interconnects (physically, two differential pairs) of a specific bandwidth. For the first generation of PCIe, as in the Intel SCH US15W, this bandwidth is 2.5 Gbps in each direction of the lane thanks to a 2.5-GHz signaling rate. Since lanes use 8/10-bit encoding, a single 8-bit byte requires 10 encoded bits of transmission bandwidth. This makes our effective bandwidth calculation easy; dividing by ten we end up with 250 MBps of bandwidth in each direction, for any given lane.

Links are built of one or more lanes. A link may have four lanes, eight lanes, or even sixteen. Data is striped among all the possible lanes, much like with RAID-0 disk arrays or memory accesses to DIMMs with many DRAM devices. This way, hardware PCIe devices can scale their bandwidth accordingly. Links on the Intel SCH US15W only consist of one lane, and there are two links. Therefore we say both links are x1 (by-one).

While each PCIe lane is capable of 250-MBps data rates in each direction, some of the data transmitted consists of control and other useful information. Like the transaction layer's overhead, we can't expect even theoretical applications to hit 250-MBps data throughputs on a link. This additional overhead can be taken into account of course. Because the maximum payload size on the Intel SCH US15W is 128 bytes and the header and other packet/framing overhead typically consumes 20 "bytes" (STP=1, sequence=2, header=12, LCRC=4, END=1) on a x1 link, our maximum posted transaction bandwidth would actually be closer to 216 MBps in each direction in this absolutely best-case scenario.

#### PCI Express\* (PCIe\*) Performance Measurements

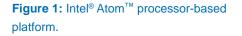

Performance data collection and analysis on the Intel SCH US15W was performed using a combination of custom PCIe traffic generators and off-the-shelf PCIe logic analyzers. The traffic generators are highly configurable DMA engines, with a collection of custom software to create various traffic patterns and execute them. All tools are running on Linux. While these tools are capable of some data collection, data was validated using the logic analyzer. The test setup is shown in Figure 2.

As we can see, Figure 2 shows two traffic generators each connected to the Intel SCH via a x1 PCIe link; between are logic analyzers. In actual testing, only one analyzer was used. Initial test runs on both ports showed only one analyzer was needed for the tests presented in this article.

This article will call transactions moving data from a traffic generator to the Intel SCH *writes* to memory. They are also called *upstream* transactions. *Reads* from memory are initiated by the traffic generator and are completed by moving data from the Intel SCH's memory to the traffic generator. These completions are also called *downstream* transactions.

Test patterns were generated using random physical memory addresses above a certain limit. That limit is also passed to the kernel at boot time to prevent conflicts. This eliminates the operating system overhead having much of an affect on our measurements. Four different test patterns were used for these tests: two write patterns and two read patterns. One write pattern generates 64-byte writes, while the other generates 128-byte writes. Similarly, one of the read patterns generates 64-byte requests, while the other generates 128-byte requests.

These test patterns are then used in various combinations to generate a test series. A test series consists of patterns from the same packet size, but enumerates all possible states for each port. There are three states: reading (RD), writing (WR), and sitting idle (N/A). After enumerating all possible state combinations, duplicates and the double idle test case are ignored. This leaves five tests per series.

Lastly, two different systems were tested, each with production stepping engineering samples. One system with a Z530 processor running at 1.6 GHz, and the other with a Z510 processor running at 1.1GHz. Both use the Intel SCH US15W as the chipset, but with appropriate memory speeds for their respective processor.

#### PCI Express\* (PCIe\*) Performance of 1.1-GHz Intel<sup>®</sup> Atom<sup>™</sup> Processor-based Platform

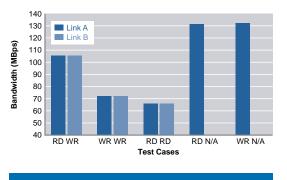

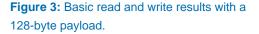

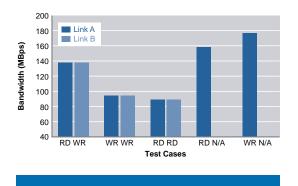

The first test series collected on a 1.1GHz Intel Atom processor and the Intel SCH US15W for 128-byte packets is shown in Figure 3.

Looking at this series running on the Intel SCH US15W, we see some interesting traits straight away. First of all, as expected, the PCIe link doesn't reach the full 216-MBps PCIe line rates we calculated earlier. This system reaches no more than about 133 MBps for reads and writes individually on a single link. When utilizing both links for reads we see a combined throughput of about 133 MBps as well, also evenly split. Yet with both links performing simultaneous writes we see 145 MBps, but again, evenly split. Finally, when performing reads on one link and writes on the other, the combined bandwidth is 212 MBps split evenly between the two links. These consistently even splits are clear evidence of round robin arbitration. Next let us look at the 64-byte packet series, shown in Figure 4.

This series does not just look about the same. For all practical purposes, it is the same. This is good, as it reinforces our assumptions thus far. Let us review the second platform's results before digging in any deeper.

"A test series consists of patterns from the same packet size, but enumerates all possible states for each port."

**Figure 4:** Basic read and write results with a 64-byte payload.

"On the 1.6-Ghz platform we see noticeable bandwidth increases over the 1.1-Ghz platform."

#### PCI Express\* (PCIe\*) Performance of 1.6-GHz Intel<sup>®</sup> Atom<sup>™</sup> Processor-based Platform

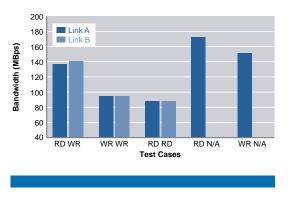

Now let us try running the two test series on a 1.6-GHz Intel Atom processor with the same Intel SCH US15W. Figure 5 shows the results for a 64-byte test series and Figure 6 shows the results for a 128-byte test series.

On the 1.6-GHz platform we see noticeable bandwidth increases over the 1.1-GHz platform. In fact, it increases proportional to the FSB speed. On the 1.1-GHz platform, the FSB was 400 MT/s, and on the 1.6-Ghz platform it is 533 MT/s. For throughputs, the two-link read test case (RD RD) measures in at 177 MBps combined bandwidth. On the 400 MT/s FSB we saw 133 MBps for the same test case. Setting up the equality between FSB ratios and PCIe throughput ratios matches up closely. We'll see why this is later.

There's one other major observation. There's an obvious delta between the single link read and single link write cases. With the 400 MT/s FSB part we saw equivalent bandwidths for the equivalent cases, but with the higher speed FSB we see that neither case matches. In fact they practically alternate between the two packet sizes. Read throughputs at 64 bytes equal those of 128-byte write case and vice versa. We'll look into why that may be later.

Figure 5: 64-byte test series on 1.6-GHz platform.

Figure 6: 128-byte test series on 1.6-GHz platform.

#### Intel<sup>®</sup> System Controller Hub (Intel<sup>®</sup> SCH) US15W Backbone

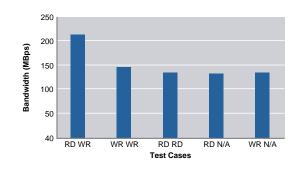

We now have enough data to start to make detailed inferences as to the structure of the Intel SCH US15W's backbone, shown in Figure 7, by analyzing the 1.1-GHz platform. We'll start with the combined bandwidth of each test case for a series as shown in Figure 8. This data, the higher bandwidth Read/Write (RD WR) case in particular, is a good indicator that the internal bus consists of two independent buses, one for upstream and another for downstream.

Now, ignoring the RD WR test case, each direction (upstream and downstream) appears to have equal bandwidth: 133 MBps. If this is the case, that each bus has equal bandwidth, why is the read/write (RD WR) case not double the other cases? That is because the dual independent bus backbone comprises two simple parallel buses, each conceptually similar to PCI. Each of those busses share address and data on the same wires (so it is at least a 32-bit bus). Therefore, read requests take up additional bandwidth on this bus, limiting the write requests. Since we would expect 133 MBps for each stream and we only see about 106 MBps, that additional bandwidth for the requests works out to roughly 27 MBps of useable bandwidth. We'll touch on this later.

Another oddity when looking at the combined bandwidth chart is the slightly higher bandwidth of the dual-link writes (WR WR) case: 145 MBps versus 133 MBps for all others. This could be an artifact of the arbitration scheme used, or, possibly, a flow control buffer effect. Assuming each link has buffers that get filled quickly and only empties when a full transaction has completed internally over the backbone, ping ponging between the two (doubling the buffers) should allow each end point to feed data to the Intel SCH US15W at the highest rate the backbone supports: 145 MBps.

#### **Backbone Clock Frequency**

Analyzing the bus further, we should be able to determine the clock rate of the backbone. This may provide us with clues to the width and efficiency of the backbone, in addition to understanding its clock rate.

First of all, the clock rate is 25 MHz for the 1.1-GHz platform. While this article will not go into the full details, one way to determine this frequency is by adding delays via the traffic generator and sweeping across a number of different delays. By analyzing the resulting traffic captures, one can see the latencies, on average, lining up into specific quanta or averages. Measuring the delta in delays between the different quantum levels provides a good guess as to the period of the internal clock—in the case of the platform with the 1.1-GHz Intel Atom processor, approximately 40 nanoseconds, corresponding to the 25-MHz clock. This analysis is not always feasible of course, but it is one possible approach. Repetitive patterns in the trace captures also reveal this periodicity or multiples of it.

**Figure 7:** Intel<sup>®</sup> System Controller Hub (Intel<sup>®</sup> SCH) US15W backbone architecture

**Figure 8:** 64-byte transactions on 1.1-GHz platform.

"A slower clock is good for reducing design and validation time among other things."

mon sense. At 64 bits, the theoretical maximum bandwidth is 200 MBps for a bus running at 25 MHz. Higher or lower than that, but by powers of two, and you either get bandwidths that are too low or too high. At 128 bits, for example, the theoretical bandwidth doubles to 400 MBps. That would mean the efficiency of the backbone is approximately 36 percent given the 145 MBps maximum we were able to achieve empirically. This efficiency is simply far too low to be practical. And at 32 bits, we are left with a maximum bandwidth lower than we observed. Thus, 64 bits it is.

Next, we can guess a transaction's burst size. Since we know the backbone is a parallel bus, similar to PCI, transactions can vary in size. For each address phase, we want to determine the number of data phases. Assuming a 64-byte transaction takes as long to setup as a 128-byte transaction (address/control/turnaround phases),

This begs the question—why the relatively slow 25-MHz clock? The answer is that a slower signaling rate reduces power significantly (P-kfV^2 after all). This is one

of those tradeoffs we mentioned earlier. It also minimizes high frequency noise and

other negative signal integrity effects. Furthermore, a slower clock is good for reducing design and validation time among other things. But power appears to be the

Now that we know the clock frequency we can predict the backbone's data bus width. This one was determined by a process of elimination and a bit of com-

we want to determine the number of data phases. Assuming a 64-byte transaction takes as long to setup as a 128-byte transaction (address/control/turnaround phases), it seems obvious from the data collected that 64-byte bursts are the only logical option. If they were larger than that, we should have seen an increase in bandwidth at the 128-byte write packet sizes where efficiency increases. Note that this means running smaller than 64-byte packet sizes should show lower bandwidth.

Further evidence of 64-byte bursts are also seen when analyzing read transactions. When making 128-byte or larger requests, multiple 64-byte completions are always returned. The hardware simply completes the transactions on the PCIe side as soon as the internal 64-byte transaction (a full cache line) is completed.

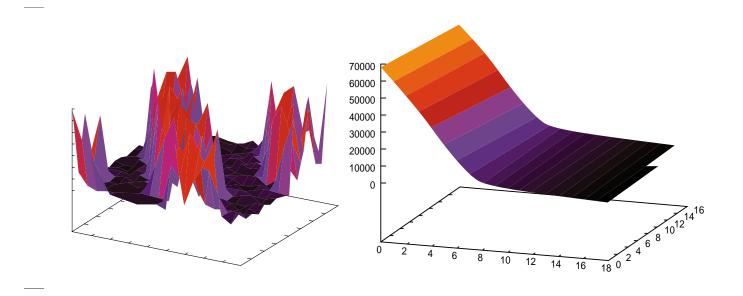

#### Backbone Model

main reason.

Backbone Bus Width and Burst Length

Knowing the backbone burst transaction size can help us understand efficiency, but we already know that. What it really helps us do is map out the backbone. We can create a chart of all the possible bandwidths that are feasible when PCIe is bursting. As a confirmation, this data should match up with data we have collected. With this affirmation, the additional insight gained will allow us to make better predictions of bandwidths at other transaction sizes, or when other devices are accessing the backbone. Figure 9 shows what a model of this looks like visually.

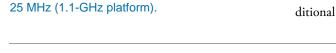

In Figure 9 we see a list of times measured in clock cycles and equivalent time in nanoseconds (assuming a 40-ns period). For each time we list the instantaneous bandwidth if transmitting 64 bytes given by the equation: 64 bytes/time.

Many of the bandwidths we have measured on the 1.1-GHz Intel Atom processor with the 400-MT/s FSB part show up in this graph. This graph also tells us additional information about what is happening in the Intel SCH. If we look back at

Figure 9: Possible backbone bandwidths based

on 64-byte transfers over a 64-bit bus clocked at

the combined bandwidth analysis we did for Figure 8, we saw read requests requiring overhead of 27 MBps for the (RD WR) test. What we were really measuring was the number of clock cycles taken by a read request. In Figure 9, 106 MBps is about 15 cycles and 133 MBps is about 12 cycles. Thus we see a read request, on average, takes three backbone clock cycles to transmit. With this kind of knowledge we can start breaking down each transaction type to make better predictions of more complex test cases.

So what about the 1.6-GHz platform with the 533-MT/s FSB? We noticed earlier that the FSB frequency changes created equally proportional changes in PCIe throughputs. Basically the backbone operates at one quarter the FSB BCLK rate, which is itself one quarter the FSB data transfer rate. As such, similar analysis and charts can be created using a 30-ns period of the 33.3-MHz clock in this platform instead of the 40-ns period of the 25-MHz clock in the 1.1-GHz platform. Digging deeper into test results for the 1.6-GHz platform will show more instability compared to the predicted model. It is believed this is due to clock boundary crossing of the 30-ns backbone with the 4-ns based transfer rate of PCIe, but no additional effort was taken to verify this.

Further, this model does not predict the change in bandwidth between the RD N/A and WR N/A cases of the 1.6-GHz platform. Typically we would expect throughputs to increase or remain the same as transaction sizes increase. With the writes, we see the opposite behavior. This might be best explained as an effect caused by full flow control buffers. Once these buffers fill up, transactions are allowed only when enough buffer space for a new transaction is free. The buffers should be sized to a multiple of the cache line size (64 bytes), with at least enough buffer to handle the maximum payload size (128 bytes). When write transactions are performed though, it is likely that the transaction size determines when buffers are free. That is, if 128-byte PCIe transactions have been posted to the buffers, the backbone performs two 64-byte internal transactions before buffer space is freed, the flow control update is sent, and another PCIe transaction is permitted. In the 64-byte case, a form of pipelining can take place. Here, when one internal transaction has completed, an update can be sent and another packet generated with a relatively short latency. At 33.3 MHz, the backbone can complete 64-byte transactions about as fast as the PCIe link can generate them (not so for the 25-MHz backbone). With 128-byte transactions though, the PCIe device must wait. This time spent waiting on the two backbone transactions to complete offsets the gains brought by the improved efficiency on the PCIe link.

#### Intel<sup>®</sup> System Controller Hub (Intel<sup>®</sup> SCH) US15W Under Pressure

Because the backbone is a shared bus, multiple simultaneous accesses have significant impacts to instantaneous bandwidth (also known as latency). This means that for high bandwidth applications, any other traffic on the bus will diminish the bandwidth temporarily, but by a significant amount. Disk accesses, for example, may not change the overall bandwidth that much on average, but it will halve the available bandwidth for short durations/bursts. "With this kind of knowledge we can start breaking down each transaction type to make better predictions of more complex test cases."

"Basically the backbone operates at one quarter the FSB BCLK rate, which is itself one quarter the FSB data transfer rate."

"The buffers should be sized to a multiple of the cache line size (64 bytes), with at least enough buffer to handle the maximum payload size (128 bytes)." "Most transactions by I/O devices occur in bursts."

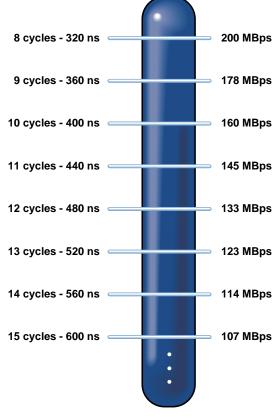

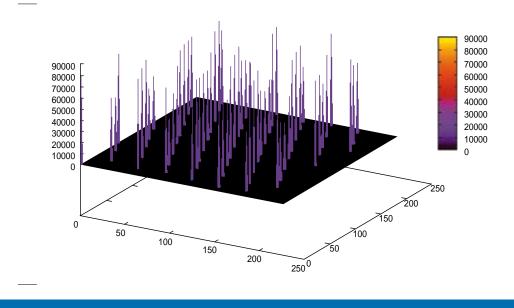

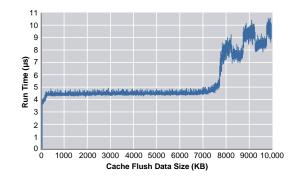

**Figure 10:** 720P video decode impacts PCIe\* traffic—each frame decoded corresponds to one of the dips as highlighted.

"Thus, 64-byte data transactions take at least 11 clock cycles to complete on the backbone for a maximum efficiency that is almost 73 percent." Why? Most transactions by I/O devices occur in bursts. As such, even "low" bandwidth applications will request the full bandwidth of the bus for short times. For these short periods, "low" and "high" bandwidth requirements are indeterminable. This means that average bandwidth does not necessarily guarantee a consistent bandwidth. If three devices all require the full bandwidth of the bus at the same time, each is only going to get one third of it for that time given round-robin arbitration. But this is not the only way the bandwidth may be impacted.

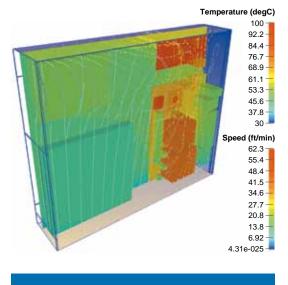

Even when the backbone is completely free for a given I/O device, bandwidth can be robbed at the memory controller level, as, for example, with video decoding, as shown in Figure 10.

Here we see our PCIe traffic generator writing data to memory. When decoding high definition video using the Intel SCH US15W's hardware decoder, we see regular dips in PCIe traffic (highlighted in Figure 10). These blips occur at regular intervals that align to each frame in the video being decoded (approximately 41 ms for 24P video). After eliminating all possible I/O impacts, it was confirmed that memory bandwidth was the culprit.

Decoding high definition video is fairly memory intensive it turns out. Each uncompressed frame of video is bounced to and from memory several times. Adding additional CPU accesses for memory on top of this will only exacerbate things.

#### **Applying Architecture to Optimization**

Putting together all of the architecture and performance information we have uncovered so far, we can now see what optimization is possible, starting with a recap of the architecture.

The Intel SCH US15W chipset employs a shared backbone architecture, not unlike PCI. Rather than a single shared bus as in PCI though, the Intel SCH US15W's backbone consists of two independent 64-bit buses, each running at 1/16 the system's front side bus transfer rate (25 MT/s or 33.3 MT/s). One bus is used for writes and requests to memory, while the other is dedicated to read completions.

Transactions on the backbone's bus take, at best, three backbone clock cycles for the address, request, and arbitration phases, and allow for a maximum payload size of 64 bytes. Given the 64-bit width of the bus, 64 bytes of data adds an additional 8 clock cycles to the transaction. Thus, 64-byte data transactions take at least 11 clock cycles to complete on the backbone for a maximum efficiency that is almost 73 percent.

How can this architectural understanding be used for optimizations? Because of the shared parallel bus nature of the backbone, PCIe hardware running on this platform performs better when conforming to certain parallel bus (think PCI) concepts. For example, PCIe devices on the Intel SCH cannot expect constant bandwidth at all times since they must share it equally with other peripherals. As such, PCIe devices that can vary their requirements (throttle) to maintain an average throughput will

work very well. Devices that do not throttle and instead enforce overly rigid bandwidth requirements with inadequate buffers will suffer. Devices must also be able to operate under the maximum throughputs uncovered earlier.

Beyond hardware, drivers may be optimized much like they would be on a shared PCI bus. Driver tweaks can further improve the ability of the hardware to adapt to differing bandwidth conditions. Application software also plays a role here because applications can be created to minimize concurrent activities on the bus.

PCIe device performance can also be optimized with packet size changes and memory use. Read requests should be made 128 bytes or larger for maximum throughput. Writes should be 64 bytes for optimal performance, even though 128 bytes would historically be better. Because of odd differences like this, hardware flexibility is ideal to maintain high performance on a wide range of platforms.

Last, but not least, even memory organization can affect performance. Though not discussed in this article, aligning transactions to cache line boundaries is very important, and this applies to all Intel architecture platforms.

#### Conclusion

All of the discussed topics—architecture, performance, optimization—are vital aspects to consider when developing platforms with the Intel Atom processor and the Intel SCH US15W. As we work to develop high performance systems with small power budgets, closer attention needs to be paid to a full system understanding. All aspects of a platform impact each other, and that becomes very clear when we push opposing design goals to their limits with new technologies. This analysis and uncovering of the backbone architecture hopefully imparts a better understanding of the platform such that software and drivers can be written efficiently, hardware can be designed efficiently, and the platform as a whole can be used as efficiently and effectively as possible.

#### **Author Biography**

Scott Foley: Scott Foley is a technical marketing engineer (TME) in Intel's Low power Embedded Division (LEPD). He has been working on platforms based on the Intel® Atom™ processor for a little over a year, and has been at Intel for over three years. He has lectured inside and outside of Intel about various topics, including most recently a lecture at the Univeristy of Colorado at Boulder on the microarchitecture of the Intel® Atom™ processor. Before being a TME he spent time working in an embedded performance architecture group and helped in the development of tools used for this article. He can be reached via email at scott.n.foley at intel.com. Spreadsheet versions of the data presented may be requested at this address.

#### Copyright

Copyright © 2009 Intel Corporation. All rights reserved. Intel, the Intel logo, and Intel Atom are trademarks of Intel Corporation in the U.S. and other countries. \*Other names and brands may be claimed as the property of others. "PCIe devices that can vary their requirements (throttle) to maintain an average throughput will work very well."

"Read requests should be made 128 bytes or larger for maximum throughput. Writes should be 64 bytes for optimal performance, even though 128 bytes would historically be better."

"As we work to develop high performance systems with small power budgets, closer attention needs to be paid to a full system understanding."

# CONFIGURING AND TUNING FOR PERFORMANCE ON INTEL<sup>®</sup> 5100 MEMORY CONTROLLER HUB CHIPSET BASED PLATFORMS

#### Contributor

#### Perry Taylor

Intel Corporation

#### **Index Words**

Intel® 5100 Memory Controller Hub chipset Intel<sup>®</sup> 5100 MCH performance tuning memory bandwidth single channel dual channel dual-rank single-rank single socket dual socket quad-core dual-core DDR2-533 DDR2-667 I/O device placement platform tuning thermal throttle electrical throttle global throttle processor prefetching hardware prefetch second sector prefetch adjacent sector prefetch **BIOS** settings

"The information provided is intended to help designers and end users make performance aware decisions in regards to these three areas, allowing them to balance cost, power and thermals with performance needs on the Intel 5100 MCH chipset."

#### Abstract

A system architect must make platform configuration choices based on multiple architecture tradeoffs between cost, power, and performance. Understanding the end impact on performance that these configuration decisions have is critical in designing competitive solutions around the Intel<sup>®</sup> 5100 Memory Controller Hub chipset (Intel<sup>®</sup> 5100 MCH chipset).

This article presents performance-related architecture topics for the Intel 5100 MCH chipset to assist system architects in designing a high performance solution. It will help engineers and architects make decisions with an awareness of performance implications, such as CPU population, memory configuration, and I/O device placement. This article also addresses performance tuning options for the Intel 5100 MCH chipset that can help increase performance for specific usage models.

#### Introduction

Intel<sup>®</sup> 5100 Memory Controller Hub chipset (Intel<sup>®</sup> 5100 MCH chipset) solutions provide board designers with a "blank slate," allowing flexible design and layout of memory, front side bus, generation 1 PCI Express\* capability and legacy I/O. While this design flexibility is desirable, it also allows for less than optimal performance configurations. Likewise, even with a board laid out for optimal performance, designers or end users can cripple system performance by populating the platform with lower performing processors, low throughput memory configurations, and poorly placed I/O endpoints. Not only the hardware selection but also hardware placement is important to system performance. Memory placement and I/O placement can have significant impact on performance as we will later demonstrate. Once all hardware choices have been made, some additional performance may be possible with platform tuning for specific usage models.

This article attempts to help with these three areas related to performance:

- Intel<sup>®</sup> 5100 MCH configuration

- Hardware configuration

- Platform tuning

The information provided is intended to help designers and end users make performance aware decisions in regards to these three areas, allowing them to balance cost, power and thermals with performance needs on the Intel 5100 MCH chipset.

#### **Performance Test Configuration**

Performance data presented in this article is collected on the following system configuration:

- Williamsport Customer Reference Board (revision B)

- Dual Socket Intel® Xeon® processor E5410 2.33GHz (Quad-Core)

- Dual Socket Intel® Xeon® processor E5220 2.33GHz (Dual-Core)

- 2 memory channels, 2 DIMMs per channel, 4GB of system memory

- 4x1GB DDR2-667, dual rank, CL5

- BIOS version WSPTG015

- 32 Bit Linux\* (Cent OS 4.4)

# Intel<sup>®</sup> 5100 Memory Controller Hub Chipset Feature and Technology Overview

The Intel 5100 Memory Controller Hub (Intel 5100 MCH) chipset) is a low power memory controller hub designed specifically for embedded applications. The Intel 5100 MCH chipset is derived from the Intel<sup>®</sup> 5000P Memory Controller Hub chipset (Intel<sup>®</sup> 5000P MCH chipset), a high performance server class chipset and as such, the Intel 5100 MCH chipset has many of the same features, technologies, and performance capabilities as the Intel 5000 Memory Controller Hub chipset (Intel<sup>®</sup> 5000 MCH chipset). The primary difference with the Intel 5100 MCH chipset as compared to the Intel<sup>®</sup> 5000 MCH chipset is the removal of the fully buffered DIMMs (FBDs) that were replaced with a native DDR2 controller. This architecture change reduces the total cost of platform ownership by reducing the overall platform power consumption while still delivering high performance.

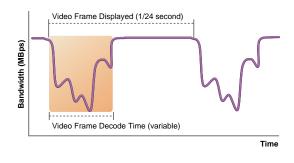

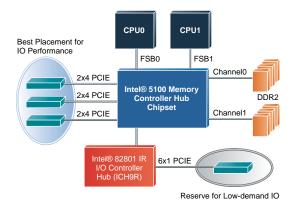

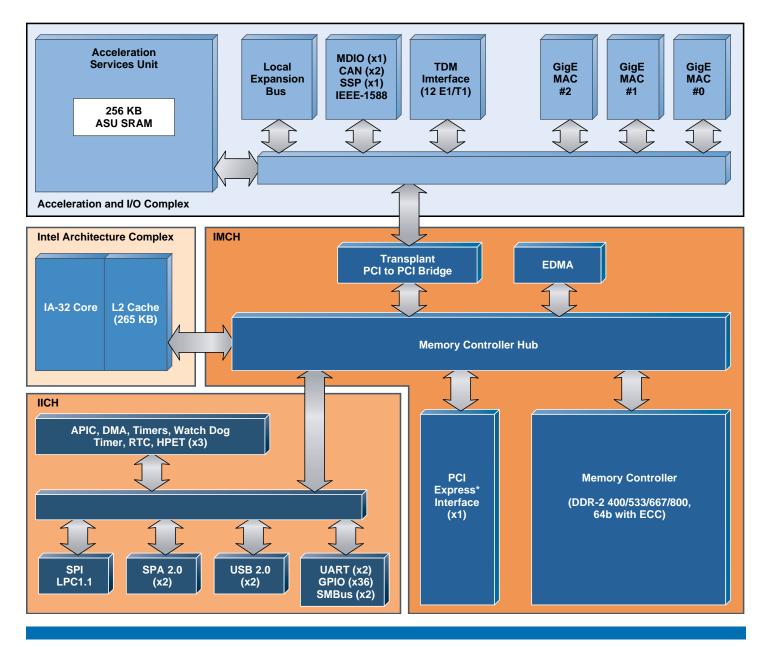

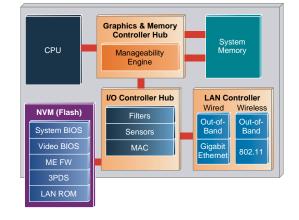

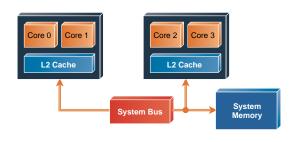

Figure 1 details the platform block diagram.

Like the Intel 5000 MCH chipset, the Intel 5100 MCH chipset is designed with a dual independent front side bus (FSB) for improved bandwidth and efficiency over previous generations, supporting 667, 1066, and 1333 MT/s. There are six x4 (pronounced "by four") Generation 1 PCI Express GB links available for direct connect I/O and a x4 direct media interface (DMI) link available to interface with an I/O Controller Hub (ICH). The six x4 PCI Express links can be combined to form various combinations of x8 links and/or x16.

The Intel 5100 MCH chipset is designed with a native DDR2 memory controller supporting registered ECC DDR2533 and DDR2-667. Dual independent memory channels provide improved bandwidth and efficiency supporting up to 3 DIMM modules per channel. Intel 5100 MCH chipset supports singe rank, dual rank, and quad rank DIMMs up to a maximum of 6 ranks per channel and a total capacity of 48 GB.

For more information on the Intel 5100 MCH chipset features, see: http://www.intel.com/Assets/PDF/datasheet/318378.pdf [2]

Figure 1: Intel<sup>®</sup> 5100 Memory Controller Hub chipset. Source: Intel Corporation, 2008

"Intel 5100 MCH chipset supports singe rank, dual rank, and quad rank DIMMs up to a maximum of 6 ranks per channel and a total capacity of 48 GB." "Platform hardware and software tuning can help extract the last bit of performance out of a system, but the hardware configuration ultimately determines the performance potential (or pitfalls) of a platform."

#### **Performance-Related Architecture Considerations**

The most important and often overlooked factor attributing to system performance is the hardware configuration. Platform hardware and software tuning can help extract the last bit of performance out of a system, but the hardware configuration ultimately determines the performance potential (or pitfalls) of a platform.

System architects may unintentionally end up designing a lower performing solution by choosing a less than desirable configuration in an attempt to save cost, power, thermals or design time. These sections address architecture considerations to help system architects and end users understand the performance impact of various tradeoffs when selecting CPU, memory, and I/O configurations.

#### CPU

The best processor configuration for computation performance will be the CPU with the maximum possible CPU frequency, cores/threads, sockets, and FSB speed. However this configuration does not always fit into the end budget, thermal, and power constraints. In this section we will explore performance impacts of choosing FSB frequency, dual-core versus quad-core; single socket versus dual socket, and finally a single socket quad-core compared to a dual socket dual-core on the Intel 5100 MCH chipset architecture.

#### FSB Frequency

As explained earlier, the Intel 5100 MCH chipset supports FSB of 667, 1067, and 1333 MT/s. For the best performance, processors supporting FSB of 1333 MT/s should be used. Note that higher FSB frequency not only results in higher effective FSB bandwidth and lower latency to memory but also makes the Intel 5100 MCH chipset core frequency proportionally faster. We will review FSB and memory frequency performance data later in the article.

#### Quad-Core versus Dual-Core

Here we illustrate the performance benefit of the quad-core architecture versus dual-core with the benchmark SPEC CPU2006. SPEC CPU2006 is a suite of tests many of which are CPU compute–bound while some are CPU to memory bandwidth–bound. For complete information on SPEC CPU2006 refer to: *http://www.spec.org.* [3]

The performance gain on quad-core will vary per sub-test and depends on the limiting factors mentioned above. Sub-tests limited by CPU-memory path bandwidth see little to no benefit from quad-core while those limited by CPU computation scale almost perfectly. The end score is an averaging of these sub-tests.

Lab testing shows that the quad-core platform configuration improves the SPECfp\_rate\_base2006(est.) score by an average of 40 percent and the SPECint\_rate\_base2006(est.) score by an average of 57 percent over the dual-core platform configuration. As expected, some computation-heavy sub-tests show nearly perfect scaling from dual-core to quad-core while memory intensive sub-tests show no scaling from dual-core to quad-core.

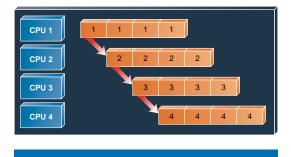

#### Single Socket versus Dual Socket

Now we show the performance benefit of a single socket architecture with a quad core CPU versus dual socket architecture with a quad-core CPU again using the benchmark SPEC CPU2006. This configuration compares four cores on one socket against eight cores across two sockets. Again, the scaling results come down to CPU computation power and memory bandwidth. Our computation power is doubling so we can expect about the same scaling here as with dual-core versus quad-core, but we also expect higher bandwidth with the additional FSB.

Tests show a 48 percent benefit on SPECfp\_rate\_base2006(est.) and 59 percent for SPECint\_rate\_base2006(est.) for this configuration.

#### Dual-Core and Dual Socket versus Quad-Core and Single Socket

Here we examine the performance difference between platforms configured with two dual-core processors versus a single socket populated with a quad-core. This is an interesting comparison since we are comparing an equal number of processor cores, but varying the number of physical processors and FSBs used.

Generally, the dual-core dual socket configuration yields higher performance but also increases system cost and power consumption. At first glance, the performance seems very similar with a 6 percent increase for SPECfp\_rate\_base2006(est.) and SPECint\_rate\_base2006(est.) is within test noise of 3 percent.

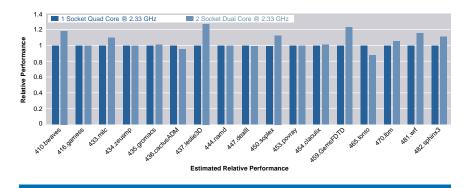

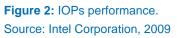

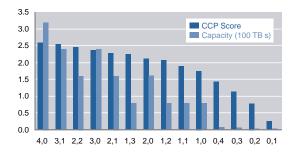

To better understand this we need to look at the sub-tests of SPEC CPU2006 Floating Point. Many of the tests perform the same on the two configurations. These tests are CPU-bound and performance is dependent on the processor core count and frequency. Some of the tests perform significantly better on the dual socket configuration. These tests are not CPU-bound, but rather memory-bound and dual socket configuration gives higher CPU-memory throughput. Figure 2 shows the tests and percentage of increase for those tests sensitive to CPU-memory throughput such as: 410.bwaves, 433.milc, 437.leslie3d, 450.soplex, 459.GemsFDTD, 470.lbm, 481.wlf, and 482.sphinx3. The remaining floating point tests are those that are computation-bound.

Figure 2: CPU2006fp performance, single socket quad-core versus dual socket dual-core. Source: Intel Corporation, 2009

"The memory subsystem is a vital component to platform performance and often becomes the limiting factor of benchmark throughput."

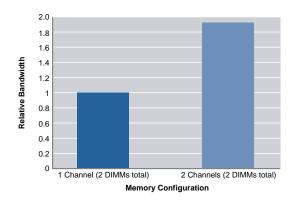

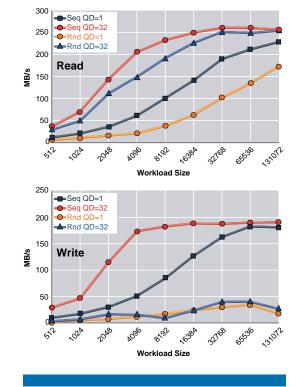

**Figure 3:** One channel versus two channel memory performance with 66% read 33% write Source: Intel Corporation, 2009

"These data points indicate that utilizing both memory channels is much more important than populating multiple DIMMs on just one channel." Based on SPEC CPU2006, we see that the computation performance of dual core with dual socket design when compared to a quad core single socket design is similar, but memory throughput improves on the dual socket design compared to single socket, showing a 27 percent improvement using 2 sockets on 437.leslie3d(est.).

#### Memory

The memory subsystem is a vital component to platform performance and often becomes the limiting factor of benchmark throughput. Therefore it is critical to populate memory with end performance in mind. This section explores the performance impact of populating one versus two channels, one DIMM per channel, two DIMMs per channel, three DIMMs per channel, dual rank DIMMs, single rank DIMMs, and memory frequency.

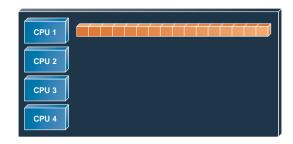

#### **Channel Population**

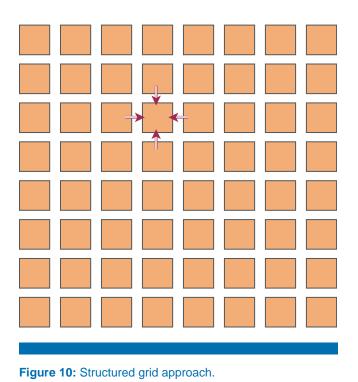

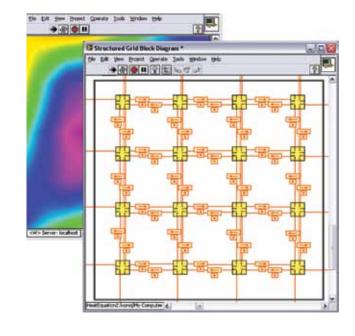

The Intel 5100 MCH chipset features two independent DDR2 channels with each channel having its own independent memory controller. In order to get the most benefit out of the memory system, it is vital to populate both channels. Memory configurations with two or more DIMMs should divide DIMMs equally between the channels.

Figure 3 illustrates the performance delta when two DIMMs are placed in one channel versus divided between channels. Memory bandwidth tests results are from an Intel internal benchmark that behaves much like Stream Benchmark, with higher memory efficiency. A 92 percent increase is observed from one channel to two channels with 1-GB, dual rank, DDR2-667 modules when CPU is issuing 66 percent read 33 percent write requests. From this data it is clear that utilizing both memory channels of the MCH is vital for memory performance. Based on the data in Figure 3, populating both memory channels is highly recommended.

#### **DIMMs per Channel**

Each memory channel on the Intel 5100 MCH chipset supports up to three DDR2 DIMMs. It is important to understand the performance impact of using one, two, or three DIMMs per channel to design a cost-effective product with high performance.

The estimated performance gains from one to two to three DIMM configurations with 1-GB, dual rank, 667 DDR2 modules is a 4.5 percent improvement from one DIMM to two DIMMs. Adding a third DIMM per channel does not typically increase bandwidth potential unless a benchmark is memory capacity limited. Populating three DIMMs per channel may potentially yield higher application/benchmark performance for capacity limited usage, but actually memory bandwidth will not increase. These data points indicate that utilizing both memory channels is much more important than populating multiple DIMMs on just one channel. Usage models requiring high memory throughput should populate two DIMMs per channel to gain the additional bandwidth while models with strict power and cost limits may consider using only one DIMM per channel. One must also consider the target software applications that will be executing on the platform. If maximum memory capacity is required then all three DIMMs per channel should be populated to achieve 4848 GB of total system memory.

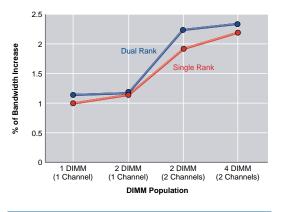

#### Dual Rank versus Single Rank

Dual rank DIMMs are recommended over single rank for performance and to enable full rank interleaving of 4:1. Figure 4 shows the measured benefit of dual rank with 66 percent read 33 percent write traffic on various memory configurations. For the maximum configuration the dual rank memory provides an additional 6.5 percent throughput. Note: Three DIMMs per channel provides additional capacity, but not bandwidth (not shown in Figure 4).

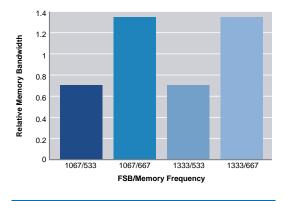

#### DDR2-533 versus DDR2-667

When selecting memory frequency, the FSB frequency must also be considered due to the impact of memory gearing. Memory gearing refers to the frequency ratio between the front side bus and memory interface. When the ratio is not 1:1, additional memory latency occurs. Table 1 shows possible frequency ratios related to memory gearing.

| FSB Frequency | B Frequency DDR2 Frequency |                 |  |

|---------------|----------------------------|-----------------|--|

| 1067 MT/s     | 533 MHz                    | 1:1 Ratio       |  |

| 1067 MT/s     | 667 MHz                    | Not a 1:1 Ratio |  |

| 1333 MT/s     | 533 MHz                    | Not a 1:1 Ratio |  |

| 1333 MT/s     | 667 MHz                    | 1:1 Ratio       |  |

**Figure 4:** Single rank versus dual rank performance. Source: Intel Corporation, 2009

Figure 5: FSB and memory frequency bandwidth with 66% read 33% write. Source: Intel Corporation, 2009

#### Table 1: Memory gearing table

Testing shows that the reduced memory latency of 667 MHz over 533 MHz makes up for the negative impact of memory gearing. So a simple rule of thumb is that higher memory frequency provides higher performance. Figure 5 reports the relative CPUmemory bandwidth recorded with each combination in dual socket configuration. Note that there is no gain from a 1067/533 configuration to 1067/667, but we show an estimated 22 percent bandwidth improvement with the 1333/667 configuration.

#### **PCI Express\***

Recall from the block diagram in Figure 1 that the PCI Express (PCIe) ports of the Intel 5100 MCH chipset can be configured in many ways. There are six x4 PCIe lanes available directly from the MCH. These can be configured as: a single x16 link with a 1x8 link, three x8 links, or six x4 links. There are also six x1 links available from the I/O controller hub (ICH), which can be combined for form one x4 and two x1 links. This section addresses performance related to these choices.

#### Lane Width

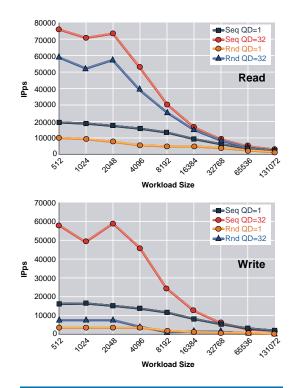

PCI Express lane width should be chosen based on required bandwidth of the I/O device. Peak PCI Express bandwidth efficiency is about 81 percent for reads and 86 percent for writes on the Intel 5100 MCH chipset.

Another important concept with link width is transaction latency. Transmit time of PCI Express packets increases as the link width decreases. For this reason, performance can benefit from link width even when higher bandwidth is not demanded.

Figure 6: I/O device placement recommendation. Source: Intel Corporation, 2009

"Populate PCI Express slots with the intent of balance loading traffic between the IOUs."

#### I/O Device Placement

For best performance, place I/O devices as close to the Intel 5100 MCH chipset as possible. Hence the use of direct MCH attached PCIe interfaces is recommended for performance sensitive IO devices. On the other hand, having relatively higher latency to memory, the PCIe slots on the I/O Controller Hub are recommended for less performance-sensitive applications. Note that increased latency also impacts throughput; how much will depend on how many outstanding transactions are pending. Tables 2 and 3 show the relative latency and bandwidth measured on a x4 PCI Express link via Intel 5100 MCH chipset and I/O Controller Hub. Note: The bandwidth measurement are carried out with up to 32 outstanding requests, hiding much of the latency impact on bandwidth while latency measurements are carried using one outstanding transaction at a time. Figure 6 illustrates recommended at IO device placement for best performance.

| X4 PCI Express*<br>(PCIe*) 64-B Memory<br>Read | Intel <sup>®</sup> 5100 Memory<br>Controller Hub Chipset<br>PCIe Slot | via I/O Controller Hub<br>PCIe Slot |

|------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------|

| Relative Latency                               | 1                                                                     | 2.07                                |

Table 2: x4 PCI Express\* (PCIe\*) latency (lower is better)

| X4 PCI Express*<br>(PCIe*) 2-KB Requests<br>to Memory | via Intel <sup>®</sup> 5100 Memory<br>Controller Hub<br>Chipset PCle Slot | via I/O Controller Hub<br>PCle Slot |

|-------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------|

| Relative Read                                         | 1                                                                         | .90                                 |

| Bandwidth                                             |                                                                           |                                     |

| Relative Write Bandwidth                              | 1                                                                         | .99                                 |

| Relative Read/Write                                   | 1                                                                         | .866                                |

| Bandwidth                                             |                                                                           |                                     |

Table 3: x4 PCI Express\* (PCIe\*) bandwidth (higher is better)

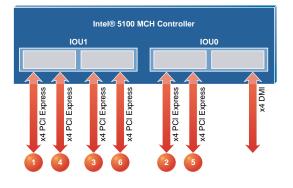

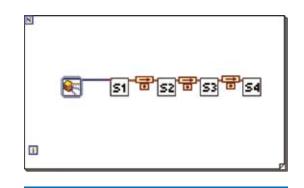

Another important concept in I/O device placement is I/O Unit (IOU) balance within the MCH. As shown in Figure 7, the Intel 5100 MCH chipset's available PCI Express slots are divided between IOU0 and IOU1. IOU0 contains the x4 DMI link and 2x4 or 1x8 PCI Express links. IOU1 contains 4x4 or 2x8 PCI Express links. Populate PCI Express slots with the intent of balance loading traffic between the IOUs. Figure 7 also illustrates an example ordering preference to ensure IOU balance.

#### **Out of the Box Performance**

Prior to product release, Intel conducts performance testing and analysis to determine ideal default chipset and processor settings. This work results in the best "out of the box" performance for general usage models and in most cases additional tuning is not necessary.

Additional performance might be achieved depending on the CPU and memory configuration used, or the specific usage model of interest. Some of these additional tuning options are presented in the following section.

Figure 7: I/O unit layout. Source: Intel Corporation, 2009

#### Accessing the Intel<sup>®</sup> 5100 Memory Controller Hub Chipset Control Registers

The following sections about hardware tuning require an understanding of chipset control registers. Inside the Intel 5100 MCH chipset there are registers related to status, capabilities and control. These registers are defined in the datasheet [2]. Changing values within these registers can control specific behaviors of the Intel 5100 MCH chipset. Registers are mapped to the PCI configuration space and they can be accessed with the correct physical address. The addressing nomenclature of the PCI configuration space is: bus, device, function, offset, and bits.

Linux provides the commands "lspci" and "setpci" for listing and changing the PCI configuration space. For example, let us say we want to disable FSB1. According to Table 4 we need to set bit 30 for bus 0, device 16, function 0 at offset 78h.

"Inside the Intel 5100 MCH chipset there are registers related to status, capabilities and control."

| Register | Field    | Bus | Device | Function | Offset | Bit | Value | Result        |

|----------|----------|-----|--------|----------|--------|-----|-------|---------------|

| FSBC[1]  | FSB1_dis | 0   | 16     | 0        | 78h    | 30  | 1     | FSB1 Disabled |

Table 4: Disable FSB 1 example. Source: Intel Corporation, 2009

lspci –s 0:10.0 –xxx dumps config space for bus 0, device 10h, function 0. From this output we can locate the register at offset 78h (highlighted below in bold text).

[root]# lspci -s 0:10.0 -xxx

00:10.0 Host bridge: Intel Corporation: Unknown device 65f0 (rev 90)

00: f0 10: 20: 30: ff fe 40: 50: ff ff ff ff 60: e0 c0 e2 0f 8c c0 e2 0f 70: 8c 80: 90: a0: b0: 5a 5a 5a 5a 5a 5a 5a 5a c0: 2c d0: 0ce0: dc 7f f4 d8 f0:

"Remember that this is little endian, requiring us to flip it backwards per byte."

"Intel<sup>®</sup> Core<sup>™</sup> microarchitecture has two hardware level prefetch mechanisms to help reduce CPU memory read latency."

"It is beneficial to test with HW Prefetching ON and also OFF in order to determine the optimal performance for the specific usage model." Remember that this is little endian, requiring us to flip it backwards per byte, resulting in: 0F E2 C0 8C. For completeness, this is broken down to bit level with bit 30 highlighted:

| Default Setting: | 0 <b>0</b> 00 | 1111 | 1110 | 0010 | 1100 | 0000 | 1000 | 1100 |

|------------------|---------------|------|------|------|------|------|------|------|

| New Setting:     | 0100          | 1111 | 1110 | 0010 | 1100 | 0000 | 1000 | 1100 |

Working backwards, the result is 4F E2 C0 8C, showing that we need to set offset 7Bh = 4Fh as follows:

setpci -s 0:10.0 7b=4f

#### **Hardware Tuning Recommendations**

There are several hardware level settings that can be changed through BIOS menus or chipset control registers that can help improve performance. Here we discuss a few of these options for the Intel 5100 Memory Controller Hub.

#### Intel<sup>®</sup> Processor Prefetching

Intel<sup>®</sup> Core<sup>™</sup> microarchitecture has two hardware level prefetch mechanisms to help reduce CPU memory read latency. These prefetchers bring data into processor L2 cache before the processor requires it in an attempt to produce a cache hit rather than a miss, resulting in increased performance.

There are two prefetchers available within the CPU architecture and can be set within BIOS, the hardware prefetch, also known as Data Prefetch Logic or DPL and the L2 Streaming Prefetch (L2S), also known as Adjacent Sector Prefetch.

Tuning processor prefetching is a topic within itself and is beyond the scope of this article. Please refer to the following paper for further information on processor prefetching:

http://software.intel.com/en-us/articles/optimizing-application-performance-onintel-coret-microarchitecture-using-hardware-implemented-prefetchers [4]

#### Hardware Prefetch

The default recommendation is to enable hardware prefetch. However, depending on individual usage models, hardware prefetch may also fetch more cache lines than are needed by an application. This can result in increased memory bus utilization and may affect performance under usage models that require heavy memory bandwidth. It is left to the user to choose hardware prefetch settings that best suit the application under consideration. It is beneficial to test with HW Prefetching ON and also OFF in order to determine the optimal performance for the specific usage model.

#### L2 Streaming Prefetch

L2S improves performance under some usage models with sequential memory addressing and/or spatial locality. L2S may be enabled/disabled via BIOS setting. Again, the effect of L2S on the performance is application-specific.

#### FSB Tuning for Single Socket Configurations

In single socket configurations, the second, unused socket should not be populated with a processor and BIOS should disable the unused FSB. The motivation is to improve performance by allowing the bus to switch to in-order mode rather than deferred mode; this reduces transaction latency and protocol overhead.

Table 4 above shows the bit in the FSBC[1] register that can be checked to verify that BIOS is disabling the second FSB in single socket configurations. For complete register definition, please see the Intel 5100 MCH Chipset Datasheet [2].

#### Memory Tuning

Memory timing settings are set to optimum values by default, providing the best performance possible within specification. DRAM timing registers should not be modified by end users except through preset BIOS settings.

For recommended memory settings, the following parameters should be selected in BIOS:

- MCH Channel Mode: Channel Interleave

- Channel Dependent Sparing: Disabled

- Channel Specific Sparing: Disabled

- Rank Interleave = 4:1

- Channel 0: Enabled

- Channel 1: Enabled

- DIMM Calibration Reuse: Enabled

- Read Completion Coalesce: Auto

#### PCI Express\* Tuning with Maximum Payload Size

The Intel 5100 MCH chipset supports a PCI Express Maximum Payload Size (MPS) of 128 bytes and 256 bytes. The default and recommended setting is 128. A 128 byte payload size allows opportunistic split completion combining (coalescing) for read requests, a feature not supported with a 256-byte MPS.

Under specific I/O usage models that perform high percentages of inbound writes with large payloads and few inbound reads, it will benefit performance to disable coalescing and increase MPS to 256 bytes. This allows I/O devices to send up to 256 bytes of data per write packet, improving write throughput but limits the maximum read completion size to 64 bytes, reducing read throughput potential.

Table 5 defines the register changes required in the Intel 5100 MCH chipset to implement a 256-byte MPS tweak. Note that end devices must also be changed to 256-byte MPS.

"Under specific I/O usage models that perform high percentages of inbound writes with large payloads and few inbound reads, it will benefit performance to disable coalescing and increase MPS to 256 bytes."

| Register          | Field       | Bus | Device | Function | Offset | Bit(s) | Value |

|-------------------|-------------|-----|--------|----------|--------|--------|-------|

| PEXCTRL[7:2,0]    | COALESCE_EN | 0   | 7-2,0  | 0        | 48h    | 10     | 0     |

| PEXDEVCTRL[7:2,0] | MPS         | 0   | 7-2,0  | 0        | 74h    | 5-7    | 001b  |

Table 5: Enable 256-byte maximum payload size. Source: Intel Corporation, 2009

#### **Throttling Mechanisms**

During performance benchmarking it is sometimes useful to disable the throttling technologies of the Intel 5100 MCH chipset to verify that performance limits are not throttle related.

#### **Thermal Throttle**

Thermal throttle allows for dynamic frequency scaling based on defined thermal thresholds, but the Intel 5100 MCH chipset does not implement thermal throttling.

Other platform components may support thermal throttle, such as the CPU. Please refer to component-specific documentation on how to disable thermal throttle.

#### Global Throttle

Global throttle allows for software controlled throttling on memory activations for a long time window, as shown in Table 6. If the number of activations to a memory rank exceeds the specified limit, then further requests are blocked for the remainder of the activation window. Setting the following bit values to zero will disable global throttle features.

| Register | Field      | Bus | Device | Function | Offset | Bit(s) | Value |

|----------|------------|-----|--------|----------|--------|--------|-------|

| THRTHIGH | THRTHIGHLM | 0   | 16     | 1        | 65h    | 7-0    | 0     |

| THRTLOW  | THRTLOWLM  | 0   | 16     | 1        | 64h    | 7-0    | 0     |

| GBLACT   | GBLACTLM   | 0   | 16     | 1        | 60h    | 7-0    | 0     |

Table 6: Disable global throttle. Source: Intel Corporation, 2009

#### **Electrical Throttle**

Electrical throttling is a mechanism that limits the number of activations within a short time interval that would otherwise cause silent data corruption on the DIMMs. Disable electrical throttle with the configuration settings listed in Table 7.

| Register      | Field      | Bus | Device | Function | Offset | Bit(s) | Value |

|---------------|------------|-----|--------|----------|--------|--------|-------|

| MTR[1:0][3:0] | ETHROTTLE0 | 0   | 22     | 0        | 15Ah   | 9      | 0     |

| MTR[1:0][3:0] | ETHROTTLE0 | 0   | 22     | 0        | 158h   | 9      | 0     |

| MTR[1:0][3:0] | ETHROTTLE0 | 0   | 22     | 0        | 156h   | 9      | 0     |

| MTR[1:0][3:0] | ETHROTTLE0 | 0   | 22     | 0        | 154h   | 9      | 0     |

| MTR[1:0][3:0] | ETHROTTLE0 | 0   | 21     | 0        | 15Ah   | 9      | 0     |

| MTR[1:0][3:0] | ETHROTTLE0 | 0   | 21     | 0        | 158h   | 9      | 0     |

| MTR[1:0][3:0] | ETHROTTLE0 | 0   | 21     | 0        | 156h   | 9      | 0     |

| MTR[1:0][3:0] | ETHROTTLE0 | 0   | 21     | 0        | 154h   | 9      | 0     |

Table 7: Disable electrical throttle. Source: Intel Corporation, 2009

#### Conclusion

When designing a solution with the Intel 5100 MCH chipset the designer should make architecture decisions based on CPU population, FSB frequency, memory population, memory frequency, I/O device selection, and placement with an understanding of how it will impact end performance. All areas of architecture should be carefully thought out with the end solution in mind to balance power, performance, cost and thermals.

#### **Disclaimers**

Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of Intel products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. Buyers should consult other sources of information to evaluate the performance of systems or components they are considering purchasing. For more information on performance tests and on the performance of Intel products, visit Intel Performance Benchmark Limitations at:

http://www.intel.com/performance/resources/limits.htm

Intel, and the Intel logo, Intel Core, and Xeon are trademarks of Intel Corporation in the U.S. and other countries.

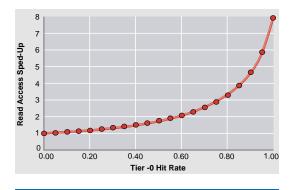

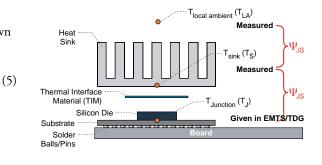

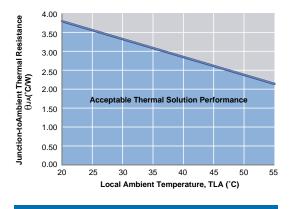

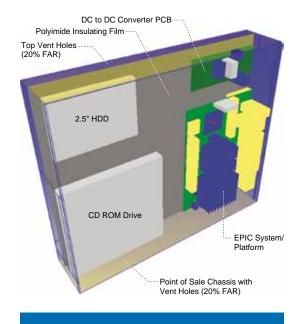

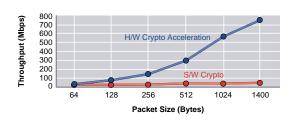

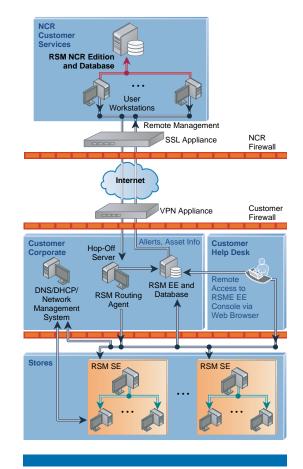

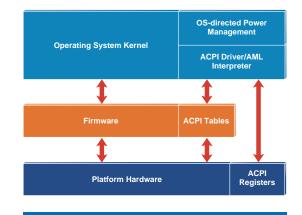

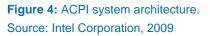

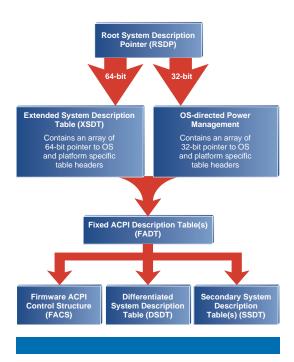

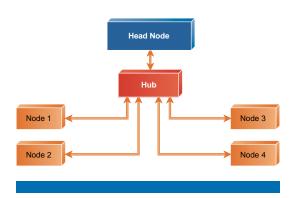

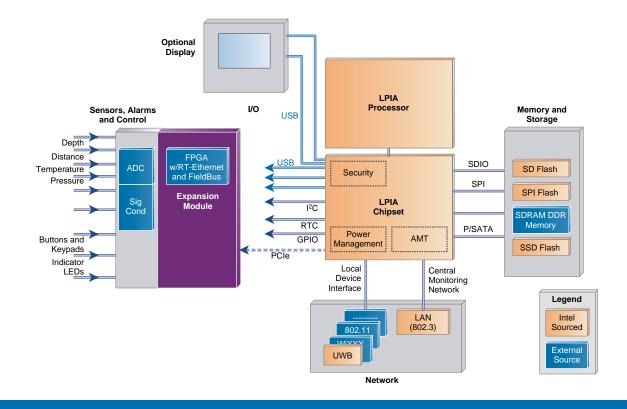

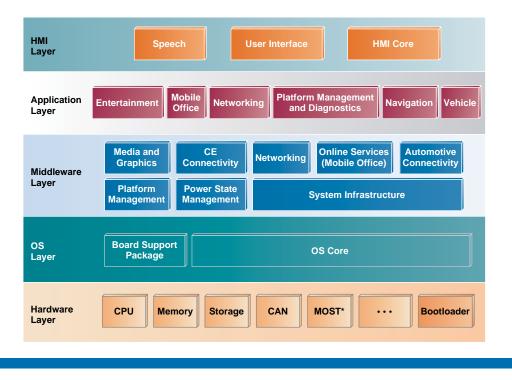

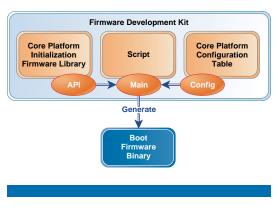

Intel processor model numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families.