Volume 12

Issue 03

Published October 2008 ISSN 1535-864X DOI: 10.1535/itj.1203

# Intel® Technology Journal

# The Original 45nm Intel Core<sup>™</sup> Microarchitecture

Intel Technology Journal Q3'08 (Volume 12, Issue 3) focuses on Intel® Processors Based on the Original 45nm Intel Core™ Microarchitecture: The First Tick in Intel's new Architecture and Silicon "Tick-Tock" Cadence

Original 45nm Intel<sup>®</sup> Core<sup>™</sup> 2 Processor Performance

Power Management Enhancements in the 45nm Intel<sup>®</sup> Core<sup>™</sup> Microarchitecture Greater Mobility Through Lower Power

Improvements in the Intel® Core™ 2 Penryn Processor Family Architecture and Microarchitecture

Power Improvements on 2008 Desktop Platforms

Mobility Thin and Small Form-Factor Packaging for Intel® Processors Based on Original 45nm Intel Core™ Microarchitecture

The First Six-Core Intel® Xeon™ Microprocessor

More information, including current and past issues of Intel Technology Journal, can be found at: http://developer.intel.com/technology/itj/index.htm

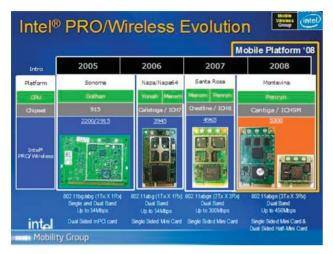

The Technical Challenges of Transitioning Intel<sup>®</sup> PRO/Wireless Solutions to a Half-Mini Card Volume 12

lssue 03

# Intel<sup>®</sup> Technology Journal The Original 45nm Intel Core<sup>™</sup> Microarchitecture

# **Articles**

| Preface                                                                                                                     | iii |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Foreword                                                                                                                    | V   |

| Technical Reviewers                                                                                                         | vii |

| Original 45nm Intel® Core™ 2 Processor Performance                                                                          | 157 |

| Power Management Enhancements in the 45nm Intel® Core™ Microarchitecture                                                    | 169 |

| Improvements in the Intel® Core™ 2 Penryn Processor Family Architecture<br>and Microarchitecture                            | 179 |

| Mobility Thin and Small Form-Factor Packaging for Intel® Processors<br>Based on Original 45nm Intel Core™ Microarchitecture | 193 |

| The Technical Challenges of Transitioning Intel® PRO/Wireless Solutions to a Half-Mini Card                                 | 199 |

| Greater Mobility Through Lower Power                                                                                        | 211 |

| Power Improvements on 2008 Desktop Platforms                                                                                | 219 |

| The First Six-Core Intel® Xeon® Microprocessor                                                                              | 229 |

#### THIS PAGE INTENTIONALLY LEFT BLANK

# Preface

#### Richard Bowles, *Publisher* David King, *Managing Editor*

Intel (R) processors based on original 45nm Intel Core<sup>TM</sup> microarchitecture is the focus of this *Intel Technology Journal* (Vol. 12, Issue 3). This family of processors was originally referred to by the codename Penryn. Improvements in the Penryn processor family are numerous and lead to benefits for mobile, desktop, and server platforms. Penryn processors are the first to exploit the advantages of Intel's 45nm process technology.

The issue marks a transition in the Journal's management. After a dozen years of success under the leadership of Lin Chao, the Journal is now going to be a part of Intel Press, where it will join with reference books that are *by engineers, for engineers*. For now, the mission of the Journal remains the same: to provide a Web-based journal to publish state-of-the-art perspectives written by Intel engineers. Lin Chao is rightfully proud of the Journal she created. My Intel Press team and I intend to maintain and enhance the Journal's reputation.

Overall performance improvements for the original 45nm Intel Core Microarchitecture is the topic of the first article. Taking a broad perspective, the article explains improvements in SSE4.1 instructions, larger caches, faster divide techniques, and better load balancing across cache boundaries. Advances are reported in dynamic acceleration technology, silicon-level support for virtualization, and deep power down technology to improve performance per watt.

The content architect for this issue of the Journal is Varghese George, who is a member of the Mobility Group at Intel Corporation and co-author of an article that drills down on power management enhancements for processors in the Penryn family. Improvement in performance per watt is a primary design criterion at Intel, and elements of the Penryn architecture enable progress on this front.

The second paper drills down on changes in the Penryn processor microarchitecture aimed at speeding up super scalar processing. Named SSE4.1, new shuffle procedures join with additional SSE instructions to improve performance for graphics and video applications. Extending Intel processors to match emerging media requirements is a longstanding tradition, and this paper marks further progress.

Greater miniaturization leads to design challenges for packaging, which is the focus of the next article. These engineers explain how they designed a solution that balanced requirements for compatibility with predecessor design, cost-efficient manufacturing for Intel and for OEMs, and for thorough validation. Along the way, these members of a global Intel team shifted work following the sun to create a 24 hour work cycle.

The trend to further miniaturization is discussed in a paper about the design challenges in building a Wi-Fi Wireless communications daughter board in a smaller form factor. The paper stands as an example of Intel's focus on platforms and not just processors, and the need to keep platform components well integrated and balanced. And, as is typical, the new design is not 10-percent smaller, but rather just half the size of its predecessor.

In the last two articles of this Journal, Intel engineers explain the impact of the Penryn processor family on mobile systems and desktop systems. Miniaturization, performance, power consumption, and packaging issues all come together to describe how the Penryn processor family will influence the next generation of Intel platforms and, in turn, the next generation of computer systems.

#### THIS PAGE INTENTIONALLY LEFT BLANK

## Foreword

### Ofri Wechsler, Intel Fellow, Manager, MG CPU Architecture

A few years ago Intel Corporation decided to base our entire IA microprocessor product line on the Intel<sup>®</sup> Core<sup>m</sup> microarchitecture. The essence of the decision was to utilize the Core technology that was originally designed for mobile computing and to enhance Core in ways that would allow it to span both the desktop and server markets. In conjunction with the converged core decision, we have also outlined a new development model for Intel<sup>®</sup> IA microprocessors which we named the "Tick-Tock" model.

Improvements in compaction (Tick) would be followed with improvements in the microarchitecture (Tock). The fundamental objective of the Tick-Tock model was to allow Intel to take advantage of the converged core in its processor development and to synchronize and maximize the utilization and output of our development teams. Our thought was that this model will enable Intel to produce significant, predictable microprocessor improvements year after year.

The new Intel® Core<sup>™</sup> processors (code-named Penryn) represent the first Tick for the Tick-Tock model. Based on historical track records, one might have expected Penryn processor improvements to be primarily caused by the shift to our new 45nm process technology (the "Tick"). That is, this first implementation would be a process technology lead vehicle with only moderate improvements attributed to changes other than process technology.

Surprisingly, this is far from being the case. The Penryn development team internalized the Tick-Tock strategy and was able to deliver an enormous number of improvements above and beyond a traditional "compaction" project. The Penryn processor development teams have set a very high bar for future Intel Tick processors.

The new Penryn processor family is marching in the footsteps of its predecessor, codename Merom, and continuing to improve the computation efficiency. The novel new hardware divider and super-shuffle units, the SSE4.1 instruction set, as well as many more microarchitectural enhancements of the Penryn processor are all aimed at the same goal: deliver more and more performance to the end user within the same or even lower power envelopes.

In addition to the performance and performance efficiency improvements that the Penryn processor family provides, it is also demonstrating a revolution in power and thermal management. Penryn processors introduce the novel Deep Power Down state, which allows the processor to draw minimal current when the processor is idling. The technological foundation that was put in the Penryn processor will allow future Intel processors to eliminate the idle power component completely from the energy equation as we move into more advanced power delivery schemes. And finally, with Penryn processors, we are introducing Intel® Dynamic Acceleration Technology that allows power and thermal budgets to move dynamically within the dual- and quad-core complexes and to boost single-thread performance even further in a restricted power envelope.

I am very proud of the newest and youngest member of the Intel Core microarchitecture family. The Penryn processor implementation teams have demonstrated for the first time what a Tick processor should look like and have expanded Intel's unquestioned leadership across the mobile, desktop and server market segments.

#### THIS PAGE INTENTIONALLY LEFT BLANK

# Technical Reviewers for Q3 2008 ITJ

Subramani Bhamidipati, Digital Enterprise Group Martin G. Dixon, Digital Enterprise Group Stephen A. Fischer, Mobility Group Benny Getz, Mobility Group Steve Ghasemi, Digital Enterprise Group Steve Gunther, Digital Enterprise Group Sanjeev Jahagirdar, Mobility Group Jason Ku, Mobility Group Rob Milstrey, Mobility Group Rajiv Mongia, Mobility Group Asim Nisar, Mobility Group Gunjan Pandya, Digital Enterprise Group Shmuel Ravid, Mobility Group Ronak Singhal, Digital Enterprise Group John Wallace, Mobility Group

#### THIS PAGE INTENTIONALLY LEFT BLANK

### Original 45-nm Intel<sup>®</sup> Core<sup>™</sup> 2 Processor Performance

Asim Nisar, Mobility Group, Intel Corporation Mongkol Ekpanyapong, Mobility Group, Intel Corporation Antonio C Valles, Software Solution Group, Intel Corporation Kuppuswamy Sivakumar, Server Platform Marketing Group, Intel Corporation

Index words: PenrynA, 45-nm Core 2 processor, Performance, SSE4.1, EDAT

Citations for this paper: Asim Nisar, Mongkol Ekpanyapong, Antonio C Valles, Kuppuswamy Sivakumar "Original 45nm Intel<sup>®</sup> Core<sup>™</sup>2 Processor Performance" Intel Technology Journal. http://www.intel.com/technology/itj/2008/v12i3/1-paper/1-abstract.htm (October 2008).

#### ABSTRACT

The 45nm Intel<sup>®</sup> Core<sup>™</sup>2 family of processors, codename Penryn $\Delta$ , improves upon the performance of Intel Core 2 processors through new microarchitecture features, a larger cache, new instructions, and enhanced power- and thermal-management schemes. This paper presents measured performance data that show the microarchitectural benefits of the Penryn family of processors on key applications and benchmarks. In addition, this paper showcases performance improvements achieved by new SSE4 instructions on a variety of media, imaging, and 3D workloads. The Penryn family of processors also introduced new power- and thermal-management schemes. This paper discusses performance improvements achieved by these enhanced thermal-management features in thermally limited platforms such as mobile thin and light and small form-factor computers.

#### **INTRODUCTION**

Performance is an integral part of product definition and success. Intel sets very aggressive performance targets to deliver products with compelling performance to the end user. While considerable effort is placed on functional validation of Intel® processors, Intel also employs significant time and effort to ensure that the processor performance meets expectations at every stage of the product development cycle from concept to silicon arrival to product launch. All design decisions are weighed against performance impact, and appropriate tradeoffs are made. As a result of this extensive effort, Intel delivered a product with recordbreaking performance on a wide range of client and server applications.

In this paper, we present information on performance delivered by products based on the 45nm Intel® Core<sup>™</sup>

2 family of processors, codename Penryn $\Delta$ . Please see [1] for a detailed architectural description of some of the new microarchitectural features. We begin with an overview of major performance features and then provide an in-depth discussion of measured performance improvements on a wide range of mobile and desktop products. We conclude by presenting performance and energy-efficiency improvements achieved on server platforms built with Penryn processors.

#### PENRYN MICROARCHITECTURE ENHANCEMENTS

The Penryn $\Delta$  family of processors is the next generation of Intel® processors based on the Intel® Core<sup>TM</sup> 2 microarchitecture, implemented on Intel's 45nm, Hi-k metal gate process technology. Frequency improvements, within existing power and thermal envelopes, over previous-generation processors, a larger L2 cache, microarchitectural enhancements, and improvements in power- and thermal-management schemes deliver improved performance per watt and energy efficiency for a broad range of client and server applications. The Penryn family of processors also added 47 new SSE4 instructions that can improve the performance of audio, video, image-editing applications, video encoders, 3-D applications, and games.

Microarchitecture enhancements that improve performance in the Penryn family of processors include the following:

• Larger Cache: Penryn processors include up to a 50 percent larger L2 cache with a higher degree of associativity that further improves the hit rate, maximizing its utilization. Dual-core Penryn processors feature up to a 6-MB L2 cache and quad-core processors up to a 12-MB L2 cache.

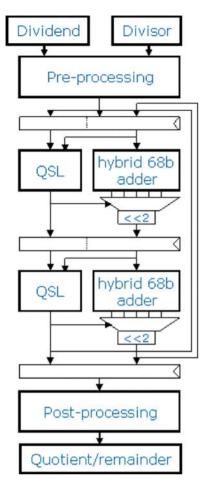

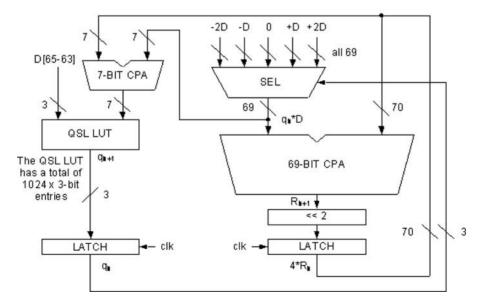

- Faster Divider: Penryn processors provide faster divider performance, roughly doubling the divider speed over previous generations through the inclusion of a new, faster divide technique called Radix 16.

- Super Shuffle Engine: Shuffles (the repositioning of bits) is a common operation in image- and video-editing applications. By implementing a fullwidth, single-pass, 128-bit-wide shuffle unit, a processor from the Penryn family of processors can perform full-width shuffles in a single cycle and is 3 times faster than previous-generation processors. The Super Shuffle Engine improves the performance of Intel Streaming Single Instruction Multiple Data (SIMD) Extensions (SSE), Streaming SIMD Extensions 2 (SSE2), Supplemental Streaming SIMD Extensions 3 (SSSE3), and Streaming SIMD Extensions 4 (SSE4) instructions, and this will benefit a wide range of applications including imaging and video applications, games, 3D modeling, and high-performance computing.

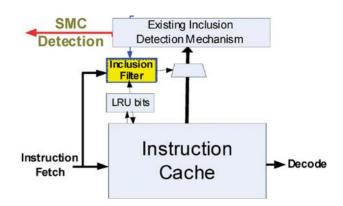

- **Inclusion Filter**: An Inclusion Filter was added in the Penryn family of processors to enhance the existing inclusion logic that was limiting server performance.

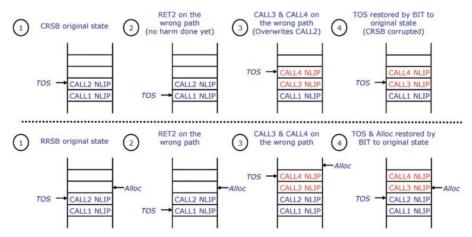

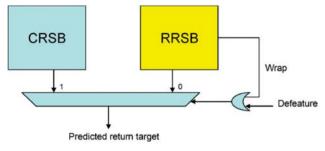

- **Renamed RSB:** The Renamed Return Stack Buffer (RRSB) increases return prediction accuracy and improves performance.

- CLI STI Performance Tuning: In the Penryn family of processors, the Clear Interrupt Flag (CLI) and Set Interrupt Flag (STI) macroinstructions were optimized to perform an execution pipeline serialization only when a new IF value is consumed and only if the new value is not yet updated, instead of post-serializing on every CLI or STI. This improves throughput of CLI-STI pairs by 2.5 times over previous-generation technology.

- Enhanced Intel® Dynamic Acceleration Technology (EDAT): EDAT is a power-management feature added to mobile processors that improves energy efficiency by dynamically increasing the performance of active core(s) when not all cores are utilized.

- Enhanced Intel® Virtualization Technology: Virtualization partitions or compartmentalizes a single computer so that it can run separate operating systems and software. This virtual partitioning better leverages multi-core processing power, increases efficiency, and cuts costs by letting a single machine act as many virtual 'mini' computers. The Penryn family of processors speeds up virtual machine transition (entry exit) times by an average

of 25 percent to 75 percent. This is all done through microarchitecture improvements and requires no virtual machine software changes.

#### **NEW INSTRUCTIONS (SSE4.1)**

While many of the microarchitecture enhancements in the Penryn $\Delta$  family of processors can be utilized without recompilation, media-related kernels will achieve the maximum performance and power-efficiency gains by recompiling with the Intel compiler and or manually optimizing code, using the new SSE4.1 instructions introduced in the Penryn family of processors.

Intel works closely with industry partners including independent software vendors (ISVs) to understand their performance needs and to improve their applications' performance. The Penryn family of processors' new instructions, SSE4, are a customer-driven response to improve performance on audio-, video-, and image-editing applications, video encoders, 3-D applications, and games. In this section we discuss performance results achieved by using the SSE4 instructions.

#### Intel<sup>®</sup> HD Boost technology

Intel HD Boost, the combination of SSE4 instructions and the Penryn family of processors' Super Shuffle Engine, can provide large speedups on a wide range of applications. The following instructions in particular can provide significant benefits to video, imaging, and audio applications.

- There are twelve new integer format conversions that can perform a conversion such as Byte-> Double-Word in one cycle with one instruction.

- The new MPSADBW instruction performs eight sums of absolute differences (SAD) in one instruction. This is twice what the SSE2 PSAD instruction can do.

- The new PHMINPOSUW instruction can be used to perform a horizontal minimum search to locate a minimum unsigned word in an XMM register or a \_\_m128 data type.

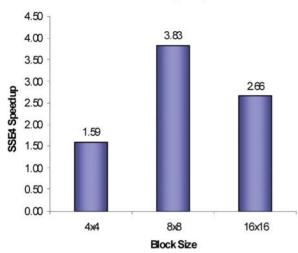

The MPSADBW and PHMINPOSUW SSE4 instructions can be used to significantly improve motion vector search algorithms (also known as block matching) used in motion estimation for video applications. An Intel whitepaper [2] showcases how to use these two instructions for block matching. The whitepaper reports a  $1.6 \times$  to  $3.8 \times$  performance improvement (see (Figure 1)).

Figure 1: SSE4.1 function-level speedups to motion vector search, also known as block matching, used in motion estimation.

The integer format conversions are commonly used in imaging and video applications. For example, they can be used when converting RGBA from four bytes to four floats prior to computation on a pixel. One SSE4 convert instruction can do the same thing as four SIMD instructions did previously, as shown.

SSE2:

pmovd xmm0, m32 pxor xmm7, xmm7 punpcklbw xmm0, xmm7 punpcklwd xmm0, xmm7 cvtdq2ps xmm0, xmm0

SSE4: pmovzxbd xmm0, m32 cvtdq2ps xmm0, xmm0

#### Conditional moves, blends, early outs

Branches have always been one of the limitations of SIMD code. SSE4 provides new instructions (six Blend instructions plus a PTEST instruction) that can be used to replace either some branches or existing lengthy SIMD code written to get around branches.

The Blend instructions can be used to replace conditional move flows. For example, the PBLENDVB instruction can replace the PAND PANDN POR instructions commonly used in conditional moves where masks are created from a comparison instruction. Another SSE4 instruction, PTEST, can be used as an early out. It is able to compare the entire 128-bit register in one pass. This instruction can be used for conditions that are meant to be infrequent such as divide-by-zero exceptions. One of the benefits of these new instructions is that they provide the compiler more vectorization opportunities; that is, they provide more opportunities to optimize the high-level code by compiling it to use the SIMD instructions.

However, the real benefit of the Blend and PTEST instructions is when multiple branches in a loop can be replaced with multiple Blend and PTEST instructions. The Mandlebrot [3] code shown in Figure 2 is an example that demonstrates how multiple branches can be replaced with multiple PTEST and Blend instructions. In the SSE4 implementation (Figure 3) notice the use of two PTEST instructions:

if(\_mm\_test\_all\_ones(\_mm\_castps\_si128(vmask)))

if(\_mm\_test\_all\_zeros(\_mm\_castps\_si128(vmask),

\_mm\_castps\_si128(vmask)))

and 3 Blend instructions:

iter = I32vec4(\_mm\_blendv\_epi8(iter + \_I\_ONE\_, iter,\_mm\_castps\_si128(vmask)));

```

void mandelbrot C()

{

int i,j;

float x,y;

for (i=0,x=-1.8f;i<DIMX;i++,x+=X_STEP) {

for (j=0,y=-0.2f;j<DIMY/2;j++,y+=Y_STEP) {

float sx, sy;

int iter = 0;

sx = x;

sy = y;

while (iter < 256)

ł

if (sx^*sx + sy^*sy \ge 4.0f)

break;

float old sx = sx;

sx = x + sx^*sx - sy^*sy;

sy = y + 2*old_sx*sy;

iter++:

}

map_C[i][j] = iter;

}

}

}

```

Figure 2: C implementation of Mandlebrot.

#### Motion Vector Search: SSE4 speedup over SSE2

```

declspec(align(16)) float INIT Y 4[4] = {0,Y STEP,2*Y STEP,3*Y STEP};

F32vec4 F STEP Y(4*Y STEP)

I32vec4 | ONE = _mm_set1_epi32(1);

F32vec4 F FOUR (4.0f);

F32vec4 F_TWO_(2.0f);

void mandelbrot F32vec4() {

intij

F32vec4 x,v;

for (i=0 x=F32vec4(-1.8f);i<DIMX;i++,x+=F32vec4(X_STEP)) {

for (i=0,y=F32vec4(-0.2f)+*(F32vec4*) INIT Y 4;i<DIMY/2;i+=4,y+= F STEP Y) {

F32vec4 sx.sv.

132vec4 iter = mm setzero si128();

int scalar iter = 0;

SX = X

SV = V.

while (scalar iter < 256) {

int mask = 0;

m128 vmask = mm cmpnlt ps(sx*sx + sv*sy, F FOUR );

if ( mm_test_all_ones(_mm_castps_si128(vmask)))

break

F32vec4 old sx = sx;

if (mm test all zeros(mm castps si128(vmask), mm castps si128(vmask))) {

SX = X + SX^*SX - SY^*SY

sy = y + F TWO *old sx*sy;

iter += I ONE ;

else {

sx = mm blendv ps(x + sx*sx - sy*sy,sx,vmask);

sy = mm blendy ps(y + F TWO *old sx*sy,sy,vmask);

iter = I32vec4(_mm_blendv_epi8(iter + _I_ONE_, iter, mm_castps_si128(vmask)));

scalar iter++;

mm storeu si128(( m128i*)&map SSE4[i][i].iter);

1

```

Figure 3: SSE4 (using F32VEC4) implementation of Mandlebrot.

By using the new SSE4 instructions on the Mandlebrot code, the Mandlebrot performance improves by 2.8 times over the C implementation.

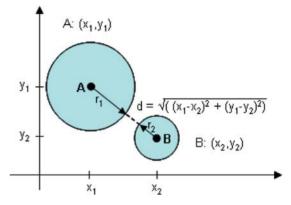

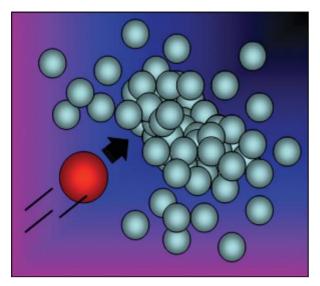

#### Graphics building blocks

SSE4 instructions can be used to speed up graphical applications such as games. The DPPS DPPD instruction can be used to speed up collision detection and common vector matrix operations such as vector normalization. A detailed example of collision detection and usage guidelines of the DPPS DPPD instructions is discussed in [1]. The example showcases a 1.5x speedup in collision detection by using the DPPS instruction and the EXTRACTPS instruction.

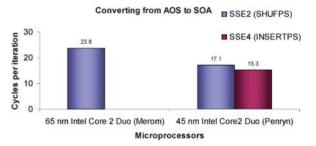

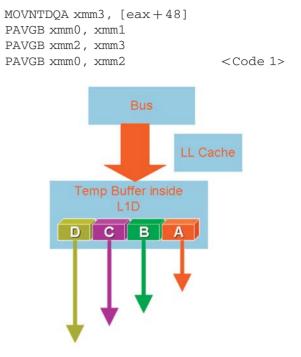

A common problem in graphics applications is 'Data Swizzling' or converting from an Array-of-Structures (AOS) data layout implementation to a more SIMDfriendly Structures-of-Array (SOA) data layout in order to use SIMD. Users have to weigh the cost of these conversions before deciding if it is worth using SIMD. By using the INSERTPS instruction, the dataswizzling operation on the next-generation, Penryn microprocessors now take fifteen cycles per four vertices, down from 23 cycles on the Intel 65-nm Core 2 Duo microprocessors, codename Merom. [5] (see Figure 4).

Figure 4: Data swizzling improvements per four vertices (one iteration converts four vertices).

Another potential game improvement is the streaming load instruction MOVNTDQA. This instruction provides a fast method to execute a 16-byte aligned load from Write Combining (WC) memory, such as graphics memory, with a non-temporal hint such that the cache is not polluted.

This instruction can provide a  $5 \times$  to  $7 \times [6]$  memory throughput performance increase.

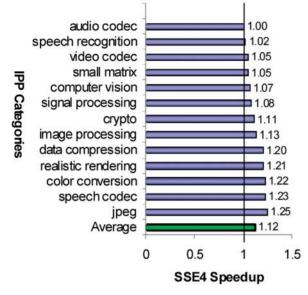

#### Intel tools

Intel's Integrated Performance Primitives (IPPs), Version 6.0 has over a thousand functions optimized with SSE4. The average speedup across all SSE4-optimized IPP functions vs. SSSE3-optimized IPP functions is  $1.12 \times$ . Figure 5 shows which IPP categories have been optimized with SSE4 and their SSE4 speedup over SSSE3.

#### IPP: SSE4 Speedup over SSSE3

Figure 5: Intel Performance Primitive categories and their SSE4 speedups over SSSE3 versions.

SSE4 instructions also enhance the compiler's ability to vectorize certain loops. Vectorization is when the compiler optimizes a loop to use SIMD instructions including SSE4 instructions. The Intel Compiler, Version 10.0 and later, can be used with the QxS compiler flag to generate SSE4-optimized code specifically for the Penryn family of processors.

SSE4 instructions combined with the Super Shuffle Engine can significantly improve the performance of imaging, video, audio, multimedia, and high-performance computing applications. Users can add these instructions to their applications via assembly code or use Intel tools such as the Intel Compiler 10.0 and IPPs. For detailed information on the SSE4 instructions, including throughput, latency, and optimization guidelines, please see the Intel 64 and IA-32 Architectures Optimization Reference Manual [5] and the instruction manuals [7,8].

#### $INTEL^{\textcircled{R}} CORE^{TM} PROCESSOR$

#### **Desktop and Mobile**

The Penryn $\Delta$  family of processors, including dual- and quad-core desktop processors and a dual- and quad-core mobile processor are branded as 'Intel Core processors.'

Desktop and mobile systems built with 45nm Intel® processors, based on Penryn Core architecture, give gamers, researchers, and serious multitaskers a significant performance boost over previous-generation

processors. In this section of the paper we present measured performance data on next-generation Intel Core<sup>TM</sup> 2 Extreme processors, the new addition to Intel's high-end desktop product line-up. We compare this processor with previous-generation Intel Core 2 Extreme processors on key client benchmarks and real-world applications.

#### Microarchitectural performance

#### Improvements

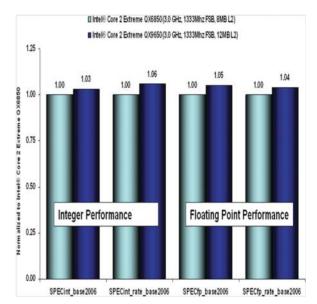

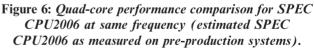

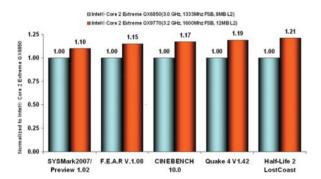

Figure 6 shows a comparison between the Intel Core 2 Extreme QX6850 processor (3.00 GHz, 1333 MHz FSB, 8 MB L2) and the next-generation 45nm Intel Core 2 Extreme QX9650 (3.00 GHz, 1333 MHz FSB, 12 MB L2) on an Asus\* P5EX38 board at the same frequency and platform configuration. 45nm quadcore performance is up to 6 percent faster than previous-generation technology on SPEC 2006.

Video and audio encoding are becoming increasingly important in the world of personal computing. Homeediting of videos and sound recordings are among the popular applications as is standard archiving of DVD material. As shown in Figure 7, the 45nm Intel Core 2 Extreme QX9650 provides a significant boost over previous-generation processors at the same frequency and platform configuration for some of the mediaencoding applications. For example, Premiere\* Pro CS3 software from Adobe is used to create highquality visual and editorial effects; it allows users to add color correction, lighting, and other effects such as audio filters and more, with fast, flexible, built-in tools. As shown in Figure 7, the new Qx9650 is 20 percent faster than the Qx6850 in rendering 210 frames to the disk using this Adobe software. Fathom\* is an advanced encoding platform product from Inlet Technologies that is used by media companies to encode content for streaming over the Internet or broadcasting over the air. As shown in Figure 7, Intel measures a 23-percent improvement with new 45nm processors for Fathom to transcode 1080i YV12 highdefinition video (HDV) to a 1080i VC1 format. Intel measures a 40-percent improvement for Qx9650 over previous-generation technology for a Pegasys\* TMPGenc XPress 4.4 encoder to convert original Variable Bit Rate encoded, 76 second, 29.97fps,  $1440 \times 1080$  video clips into HDV format MPEG video with  $1440 \times 1080$  resolution, 29.97 fps, and 25000 Kbs Constant Bit Rate encoding. Another example is VirtualDub\* software, which is a video capture processing utility that uses the DivX\* 6.7 software for encoding movies. Virtualdub\* 1.7.1 and later with DivX 6.7 are optimized for SSE4 instructions and provide a very noticeable 60-percent performance gain over previous-generation processors that use encoding in SSE2 to convert to the highercompression DivX format.

Figure 7: Quad-core performance comparison for video encoders at same frequency.

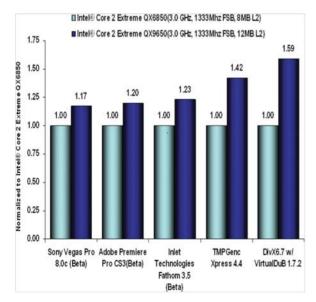

Figure 8 shows a similar comparison for some of the popular games. The new 45nm Intel® Core<sup>TM</sup> 2 Quad processor is roughly 10 percent faster than previous-generation processors at  $1024 \times 768$ . Even when looking at just the two quad-core processors that run at the same FSB and clock speeds, the Intel 45nm Core

2 processors have a clear lead over previous-generation processors. The larger cache, new microarchitectural features, the Penryn high-definition boost, the Super Shuffle unit, and the SSE4 instructions that were discussed in the previous sections all contribute to the increased performance.

Figure 8: Quad-core performance comparison for games at same frequency.

#### Frequency and platform improvements

Figures 9 and 10 compare the Intel Core 2 Extreme OX6850 processor (2.93 GHz, 1066 MHz FSB, 8 MB L2) on an Intel 975BX2 board with DDR2 800 RAM with an Intel Core 2 Extreme OX9770 processor (3.20 GHz, 1600 MHz FSB, 12 MB L2 Penryn). Please see Table 1 for a detailed system configuration. This is a more realistic comparison as it takes into account core enhancements, frequency improvements achieved with new 45nm technology, and other platform improvements that were added to support core enhancements. A new 45nm Intel Core 2 Ouad-based platform provides double-digit gains on computeintensive workloads such as SPEC 2006 and the Sysmark 07 Preview that reflect usage patterns of business users in the areas of video creation, Elearning, 3D modeling, and office productivity. Intel measures a 17 percent improvement for Cinebench's multi-threaded rendering test and roughly a 20 percent improvement for Quake 4\* and Half Life 2\*. A videoencoding application such as DivX and TMPGenc\* see a 50 percent to 80 percent gain. The increased frequency and 1600-MHz FSB improves the system bus and memory bandwidth and are the significant contributors to the performance difference. The enhancements in the Penryn family of processors are setting milestones in desktop computing performance.

| Processors    | Intel <sup>®</sup> Core <sup>™</sup> 2 Extreme QX6850 | Intel <sup>®</sup> Core <sup>™</sup> 2 Extreme QX9770 |

|---------------|-------------------------------------------------------|-------------------------------------------------------|

|               | 8 MB L2, 3.0 GHz, 1333 MHz FSB                        | 12 MB L2, 3.2 GHz, 1600 MHz FSB                       |

| Memory        | Deluxe Dual channel DS Corsair 2GB                    | Dual channel DS Corsair CM3X1024-1600                 |

| -             | (2 × 1 GB) DDR3-1333 9-9-9-24                         | C7DHXIN XMP 2 GB $(2 \times 1 \text{ GB})$            |

|               |                                                       | DDR3-1600 7-7-7-20                                    |

| Graphics card | $1 \times G8800$ GTZPCle graphics                     |                                                       |

| Motherboard   | Asus* P5E3 X38 Deluxe board                           |                                                       |

| Hard disk     | Seagate 320 GB NCQ SATA                               |                                                       |

| BIOS          | Beta 0504, INF:8.4.0.1016, Graphic: NV163.69          |                                                       |

Table 1: Detailed system configuration for the results shown in Figures 9 and 10.

Figure 9: *QX9770 (45 nm) comparison with QX6850 (65 nm) or SPEC 2006.*

Figure 10: QX9770 comparison with QX6850 for games and general purpose applications.

# Enhanced Intel<sup>®</sup> Dynamic Acceleration Technology

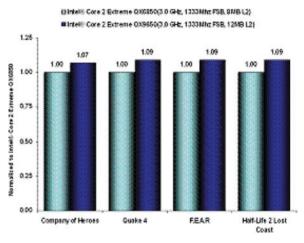

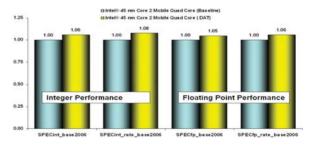

Performance data presented in Figures 6–10 are based on desktop system measurements, but mobile platforms built with 45nm cores will see similar performance improvements over previous-generation platforms. Mobile processors, however, operate at lower frequencies because of tighter power and thermal limitations. In this section we illustrate how 45nm enhancements in Intel® Dynamic Acceleration Technology (DAT) improve mobile platform performance. DAT is a power-management feature that can improve system performance by increasing the frequency of active core(s) when at least half of the cores in a multicore processor are inactive and thermal headroom is available. DAT was introduced in the 65-nm Intel Core 2 mobile processors, but in the Penryn family of processors we further enhanced DAT performance and energy efficiency by reducing the number of transitions in and out of DAT, reducing transition overhead in high-interrupt-rate scenarios. In the Penrvn family of processors, we also extended DAT support to quadcore mobile processors. Architectural implementations and more details about these enhancements in Intel's Enhanced Dynamic Acceleration Technology (EDAT) are discussed in [4]. Single-threaded applications running on a dual-core or quad-core processor based on the Penryn family of processors, or two single applications (or a two-threaded application) on a quad-core processor, can take advantage of EDAT.

Figures 11-12 illustrate EDAT performance on an Intel Core 2 Quad processor for SPEC 2006, games, and multimedia applications on pre-production mobile platforms with 2 GB of DDR3 memory, a 1066 MHz FSB, a 120 GB hard disk, and a baseline frequency of 2.4 GHz.

Figure 11: EDAT performance improvements (estimated SPEC 2006 as measured on pre-production hardware).

Figure 12: EDAT performance improvements (multimedia and games as measured on pre-production hardware)

To fit QC processors into the mobile Thermal Design Power (TDP) envelope, Intel had to reduce the processor's operating frequency, which in turns gives a wider dynamic range in terms of thermal headroom to operate at EDAT frequencies for one- and two-core operations. The performance gains for EDAT are solely from frequency scaling. The amount of frequency improvement varies from product to product. Single-threaded applications, or two single-threaded applications, or an application with two worker threads with good frequency scaling running on a quad-core processor, can see up to a 10 percent performance boost from EDAT.

#### INTEL XEON® PROCESSORS

New servers, workstations, and high performance computing (HPC) systems are built with new quadcore Intel Xeon processors 5400 series that are based on the 45nm Penryn $\Delta$  core technology. Intel's 45nm technology packs 820 million transistors into the Intel Xeon processor 5400 series. The chip is smaller than the previous-generation Intel Xeon processor 5300 series (214 mm<sup>2</sup> vs. 286 mm<sup>2</sup>), which had 582 million transistors. More transistors on new 45nm technology means more capability, performance, and energy efficiency.

#### **Increased performance**

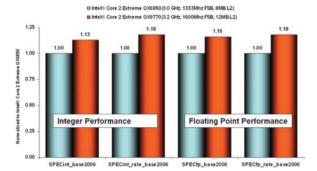

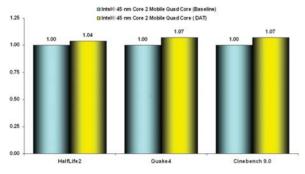

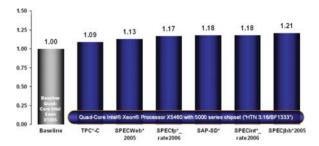

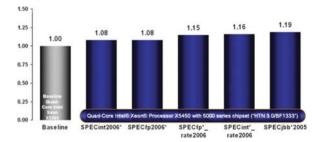

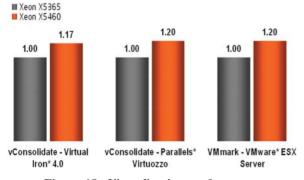

The Intel Xeon 5400 series, based on technology from the Penryn family of processors, featuring a larger 12-MB L2 cache, delivered a strong performance gain to the already stable and shipping server platform based on the Intel 5000 series chipset. A drop-in into the existing platform, the 5400 series, added up to a 21 percent performance increase over the previous-generation, quad-core Intel Xeon processor 5300 series for mainstream server benchmarks at the highest frequency level (comparing Xeon X5460 at 3.16 GHz to Xeon X5365 at 3 GHz). Figure 13 shows the comparison on a range of server benchmarks. Figure 14 shows performance comparisons to the previous generation at the same clock frequency (3 GHz) achieving up to a 19 percent performance increase and highlighting the benefits of the improvements in the Penryn family of processors.

Figure 13: Comparison of server benchmarks with those of the previous generation.

Figure 14: Comparison of server benchmarks to those of the previous generation at the same frequency on the same platform.

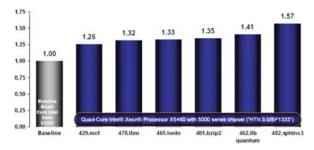

The Penryn family of processors' architecture presents several compiler optimization opportunities. These opportunities include tuning for the new ISA, a larger cache, and hardware pre-fetching. The overall gain for the SPEC CPU2006 benchmark suite is shown in Figure 14 as 15–16 percent on the 'rate' benchmark. But gains across the individual components could be as high as 57 percent. Figure 15 shows some of the highlights across the Integer and Floating-point component workloads. All the results shown are on the peak result metric (SPECint\_rate2006 and SPECfp\_rate2006).

Figure 15: Gains on specific SPEC CPU2006 'rate' components at same frequency.

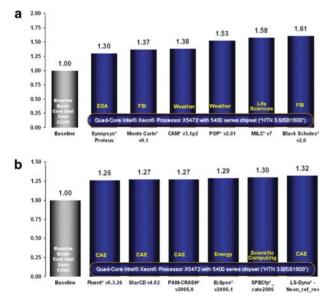

To leverage the full potential of the 45nm microarchitecture, a new platform targeting the HPC market segment was launched with the new Intel 5400 chipset that could run at the faster FSB speed of 1600 MHz. The additional bandwidth delivered by the platform is critical for the HPC segment. Figures 16a and b show results on key HPC workloads on segments such as manufacturing, financial services, energy, weather and climate modeling, electronic design automation (EDA), and life sciences. It is important to note that the gains achieved by these applications were due to a combination of microarchitectural enhancements and the increased platform bandwidth.

Figure 16: (a) HPC benchmarks. (b) HPC benchmarks.

#### Improved energy efficiency

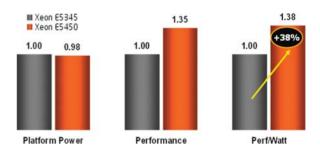

Servers based on the quad-core Intel Xeon processor 5400 series also maximize data centers performance and density through improved energy efficiency. As shown in Figure 17, these processors can deliver up to 38 percent more performance per watt in the same platforms and at the same system power level. The platform power in this chart is based on measured average power value at the steady-state window of the benchmark run. For this comparison we used the most energy-efficient mainstream processor SKU from each of the processor families. In this case, that would mean the Intel Xeon E5450 running at 3 GHz compared to the Intel Xeon E5345 running at 2.33 GHz, both at an 80 W TDP rating. The 45-nm, Hi-k-based processor also lowers the idle power significantly. Results on the new industry standard SPECpower\*s ssj2008 benchmark, which is the first comprehensive benchmark to measure energy-efficient performance across a load-line including idle power, highlights the energyefficient performance of the Penryn family of processors. Table 2 shows the top-10 list for this benchmark, all occupied by platforms based on the Penryn family of processors' architecture.

Figure 17: Energy efficiency-SPECjbb2005 Benchmark.

| Rank | s Sponsor | Overall<br>ssj_ops/<br>Watt | Platform | # of<br>Sockets | Processor(s)                                 | Processor Microarchitecture |

|------|-----------|-----------------------------|----------|-----------------|----------------------------------------------|-----------------------------|

| 1    | FSC       | 1124                        | TX150 S6 | 1               | Intel <sup>®</sup> Xeon <sup>®</sup> X3360   | Intel <sup>®</sup> "Penryn" |

| 2    | IBM       | 1054                        | X3200 M2 | 1               | Intel <sup>®</sup> Xeon <sup>®</sup> X3360   | Intel <sup>®</sup> "Penryn" |

| 3    | FSC       | 1018                        | TX150 S6 | 1               | Intel <sup>®</sup> Xeon <sup>®</sup> X3360   | Intel <sup>®</sup> "Penryn" |

| 4    | HP        | 930                         | DL180 G5 | 2               | Intel <sup>®</sup> Xeon <sup>®</sup> L5420   | Intel <sup>®</sup> "Penryn" |

| 5    | IBM       | 926                         | X3350    | 1               | Intel <sup>®</sup> Xeon <sup>®</sup> X3360   | Intel <sup>®</sup> "Penryn" |

| 6    | IBM       | 913                         | X3250 M2 | 1               | Intel <sup>®</sup> Xeon <sup>®</sup> X3350   | Intel <sup>®</sup> "Penryn" |

| 7    | Inspur    | 910                         | NF290D2  | 2               | Intel <sup>®</sup> Xeon <sup>®</sup> L5420   | Intel <sup>®</sup> "Penryn" |

| 8    | IBM       | 854                         | X3450    | 2               | Intel <sup>®</sup> Xeon <sup>®</sup> E5462   | Intel <sup>®</sup> "Penryn" |

| 9    | Dell      | 800                         | PE R300  | 1               | Intel <sup>®</sup> Xeon <sup>®</sup> L5410   |                             |

| 10   | HP        | 778                         | DL180 G5 | 2               | Intel <sup>®</sup> $Xeon^{\mathbb{R}}$ E5450 |                             |

Table 2: Top ten results on the first Industry Standard benchmark for energy efficiency-SPECPower\*\_ssj2008 (as of June 10, 2008).

SPECpower results from http://www.spec.org/power\_ssj2008/results/power\_ssj2008.htmlas of June 10, 2008.

#### **Enhanced virtualization**

Virtualization partitions or compartmentalizes a single computer so that it can run separate operating systems and software. These partitions can better leverage multi-core processing power, increase efficiency, and cut costs, by letting a single machine act as many virtual 'mini' computers. Consolidating applications onto fewer systems not only results in better multi-core utilization but improves performance density. In the Penryn family of processors, virtual machine transition (entry exit) times show an improvement of between 25 percent and 75 percent. Based on virtualization benchmark results on different VMMs, the Penryn family of processors provide up to a 20 percent performance gain when compared to previous-generation platforms. Figure 18 shows comparisons of different benchmarks such as VMmark and vConsolidate running various VMMs such as VMware ESX Server, Parallels Virtuozzo, and Virtual Iron 4.0.

Figure 18: Virtualization performance.

#### CONCLUSION

The Penryn $\Delta$  family of processors brings record levels of performance to the end user through its larger cache, new microarchitectural features, new instructions, and enhanced power- and thermal-management schemes. These processors, manufactured on Intel's 45nm, Hi-k metal gate process technology, not only provide significant performance improvements over the previous-generation processors, but they also provide building blocks for software to be created to take advantage of this power and deliver new levels of functionality to end users.

#### ACKNOWLEDGEMENTS

The authors thank all the researchers, architects, designers, validators, and software engineers who took the Penryn $\Delta$  family of processors from a vision to a real product. Special thanks go to Mike Fard, Jeff Reilly, Ronen Zohar, Daniel Shea, and Eric Palmer who provided performance data and or examples used in this paper.

#### REFERENCES

- Coke, Jim. "Improvements in the Intel<sup>®</sup> Core<sup>™</sup> 2 Penryn∆ Processor Family Architecture and Microarchitecture." Intel Technology Journal, Volume. 12, Issue. 3, 2008.

- [2] Kuah, K. "Motion Estimation with Intel® Streaming SIMD Extensions 4 (Intel® SSE4)," at http://softwarecommunity.intel.com/articles/ eng/1246.htm.

- [3] Mandelbrot set. http://en.wikipedia.org/wiki/ Mandelbrot\_set.

- [4] Jahagirdar, S. "Power-Management Enhancements in 45 nm Intel®Core<sup>™</sup> Microarchitecture." *Intel Technology Journal*, Volume 12, Issue 3, 2008.

- [5] Intel® 64 and IA-32 Architectures Optimization Reference Manual. http://www.intel.com/ products/processor/manuals/.

- [6] Jha, A. and Yee, D. "Increasing Memory Throughput With Intel<sup>®</sup> Streaming SIMD Extensions 4 (Intel(4) SSE4) Streaming Load." At http://softwarecommunity.intel.com/articles/eng/ 1248.htm.

- [7] Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2A: Instruction Set Reference, A-M. At http://www.intel.com/ products/processor/manuals/.

- [8] Intel® 64 and IA-32 Architectures Software Developer's Manual, Volume 2B: Instruction Set Reference, N-Z. At http://www.intel.com/ products/processor/manuals/.

#### **AUTHORS' BIOGRAPHIES**

Asim Nisar is a Senior Architect with Intel's Mobile Microprocessor Group in California, USA. He led the 45nm Intel® Core<sup>M</sup> 2 performance modeling, analysis, performance projections, pre-silicon and post-silicon performance validation activities. Prior to this, he was involved in defining and enhancing several microarchitectural features. He has an M.S. degree from the Georgia Institute of Technology, USA. His e-mail is asim.nisar at intel.com.

**Mongkol Ekpanyapong** is a Senior Architect with Intel's Mobility Microprocessor Group in California, USA. He received his B.E. degree from Chulalongkorn University, Thailand, his M.E. degree from the Asian Institute of Technology, Thailand, his M.S. and Ph.D. degrees from the Georgia Institute of Technology, USA. Mongkol was involved in performance modeling and validation for the Intel<sup>®</sup> Core<sup>TM</sup> 2 Duo processor architectures. His current focus is on performance modeling for the next-generation Intel microprocessor. His e-mail is mongkol.ekpanyapong at intel.com.

Antonio C Valles is a Senior Software Engineer in Intel, Chandler, AZ focusing on broad and in-depth presilicon and early-silicon tests of Intel microprocessors and chipsets. Antonio has created multiple internal pre-silicon and post-silicon tools and kernels for performance analysis and coordinates development of tuning guidelines for the processors. He received his B.S. degree in Electrical Engineering from Arizona State University in 1997. His email is antonio.c.valles at intel.com.

**Kuppuswamy Sivakumar (Siva)** is a Marketing Manager for Intel's Server Platforms Group in California, USA. He received his B.E. degree from the University of Madras, India, his M.S. degree from the University of Kentucky, Lexington, and his MBA from the University of California, Berkeley. Siva manages performance marketing activities for Intel® Xeon® server products. His e-mail is kuppuswamy.sivakumar at intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel Strata-Flash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Intel's trademarks may be used publicly with permission only from Intel. Fair use of Intel's trademarks in advertising and promotion of Intel products requires proper acknowledgement.

Any codenames featured in this document are used internally within Intel to identify products that are in development and not yet publicly announced for release. For ease of reference, some codenames have been used in this document for products that have already been released. Customers, licensees, and other third parties are not authorized by Intel to use codenames in advertising, promotion or marketing of any product or services, and any such use of Intel's internal codenames is at the sole risk of the user.

\*Other names and brands may be claimed as the property of others.

Microsoft, Windows, and the Windows logo are trademarks, or registered trademarks of Microsoft Corporation in the United States and/or other countries.

Bluetooth is a trademark owned by its proprietor and used by Intel Corporation under license.

Intel Corporation uses the Palm OS<sup>®</sup> Ready mark under license from Palm, Inc.

LEED - Leadership in Energy & Environmental Design (LEED  ${}^{{}_{\mathrm{I\!E}}}$ )

Copyright © 2008 Intel Corporation. All rights reserved.

This publication was downloaded from http://www.intel.com.

Additional legal notices at: http://www.intel.com/sites/corporate/tradmarx.htm.

### Power Management Enhancements in the 45nm Intel® Core<sup>™</sup> Microarchitecture

Jose Allarey, Mobility Group, Intel Corporation Varghese George, Mobility Group, Intel Corporation Sanjeev Jahagirdar, Mobility Group, Intel Corporation

Index words: power management, CPU Sleep, C states, idle power, frequency

Citations for this paper: Jose Allarey, Varghese George, Sanjeev Jahagirdar "Original 45nm Intel® Core™ 2 Processor Performance" Intel Technology Journal. http://www,intel.com/technology/itj/2008/ v12i3/2-paper/1-abstract.htm (October 2008).

#### ABSTRACT

Intel<sup>®</sup> processors based on the original 45nm Intel Core<sup>TM</sup> microarchitecture, originally referred to by the codename Penryn, improved the energy efficiency and performance per watt of the Intel Core microarchitecture. This paper discusses the new technologies introduced in the Penryn family of processors that enabled lower idle power and higher performance levels.

The Penryn family of processors builds on the powermanagement capabilities of the Intel processors based on 65nm Intel Core microarchitecture, originally referred to by the codename Merom, and takes them to the next level of idle power reduction and multi-core Enhanced Dynamic Acceleration Technology performance. The Penryn family of processors took very aggressive goals for idle power reduction in mobile, desktop, and server platforms. All features have been demonstrated to be fully functional on silicon and meet or beat the expectations of power reduction and increased performance. In fact, most of these features have already been enabled on the products that are currently shipping. Furthermore, the Penryn family of processors introduced new processor sleep states and Dynamic Acceleration mode on Intel Core 2 Quad processors for the first time in Intel to enable the acceptance of quad core as a mainstream product.

#### **INTRODUCTION**

The Penryn family of processors, implemented in a 45nm high-k metal gate silicon process technology, is designed to fit a wide range of power envelopes and market segments. Energy efficiency (energy consumed for doing a unit of work) is significantly improved due to

process power scaling and innovative architectural power-management features. Power scaling enables better performance and higher power efficiency in most workloads, and the power-management features primarilv enable lower idle power that leads to an overall reduction of platform energy consumption. Lower idle power helps improve battery life in mobile platforms, allows platforms based on the Penryn family of processors to meet or exceed Energy Star and other regulatory requirements for idle power consumption in desktop PCs, and lowers electricity and cooling costs for servers. The details of the 45nm high-k metal gate process technology and its power benefits are discussed in the last issue of the Intel Technology Journal [1,2] and hence are not covered here in detail. In this paper we focus on the architectural innovations in the powermanagement domain of the Penryn family of processors.

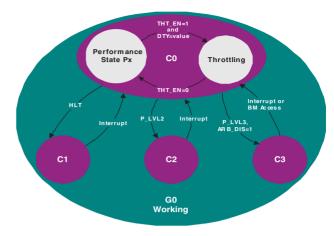

The Penryn family of processors builds upon the power-management capabilities of the core microarchitecture. The Advanced Configuration and Power Interface (ACPI) specification [3] describes the processor sleep states and performance states in detail. When the processor is executing instructions, it is in the C0 active state. The C1, C2 states, etc. are successively lower-power processor sleep states in which no instructions are being executed. P states are processor performance states defined by the processor frequency. The Penryn family of processors supports the Core Microarchitecture C states, P states, and thermal monitoring functions. In addition, the Penryn family of processors introduces several new key features and extends some of the existing mobile platform capabilities to desktop systems. Two key features introduced in the Penryn family are as follows:

• Deep Power Down (DPD), a new idle power state.

- Enhanced Dynamic Acceleration Technology (EDAT), a feature to increase Single Threaded (ST) performance by using the power headroom of the idle core. A simpler version of this feature is also available in the later versions of the Intel<sup>®</sup> Core<sup>™</sup> 2 Duo 65nm processor.

- Power Management features extended to other segments are as follows:

- The Deeper Sleep state is now available in desktop platforms and in quad-core products.

- A version of the Deep Sleep state (called CC3 or Core-C3) state is now available in server platforms.

- The Enhanced Dynamic Acceleration Technology (EDAT) and Deeper Sleep state technology were extended to the mobile Quad-Core Extreme Edition product.

#### CHALLENGES

The Penryn family of processors was developed as a common core for the mobile, desktop client, workstation, and DP MP server platforms. The processor Thermal Design Power (TDP) in these segments ranges from 25 watts to 130 watts. Each platform has some common and some independent goals in power and thermal management. The challenge to the core development team is to anticipate the various requirements and design the support for all these platforms into the common core. For example, generic improvements such as reducing peak power and idle power consumption are applicable to all platforms. On the other hand, reducing energy usage during run time is a primary concern for the mobile and server platforms more than the desktop platform. Additionally, the mobile platform has tighter constraints on the peak power dissipation due to its form factor. Server platforms demand higher peak performance and are also capable of supplying and dissipating the power to support the peak demand conditions. The desktop platform usage mode has a lot of idle-ON time and standby time. Hence this platform has a specific requirement to reduce the idle and standby energy usage so that the end user will have a more energyefficient, always-on always-available experience.

#### **IDLE POWER IMPROVEMENTS**

#### **DPD** technology

In mobile systems, battery life is an extremely important consideration. This is driving the need for low "average power" consumption in mobile processors. Designing high-performance mobile processors that consume approximately 30–40 watts during normal operation but have extremely low-power consumption during idle is challenging. The leakage in the millions of transistors in a processor design adds up to several watts if not several tens of watts. Consuming several watts of power while idle degrades the battery life significantly.

In the days of the Intel 486<sup>™</sup> processor there was only one type of idle state—the Autohalt state. Most of the clocks to the processor were stopped in this state; active power was cut down significantly, and this brought the total processor power consumption down because leakage was not an issue. Since then, however, leakage has gotten worse with every new process generation, and more aggressive power-management states (C states) have been added to processors to combat this issue while idle.

A brief outline of the various C states follows as an introduction to the DPD technique.

The processor running state is called the "C0 state" in Advanced Configuration Power Interface (ACPI) [3] nomenclature. The processor is not executing any instructions in C states other than C0. A highernumbered C state generally consumes lower power at the expense of higher exit latencies than a lowernumbered one.

In the C3 state, the processor Phased Locked Loop (PLL) is shut down to turn off all the clocks in the chip. This, however, does not lower the leakage, since voltage is not changed. In the C4 state, the voltage applied to the processor in C3 is lowered to reduce leakage. Here, the voltage is lowered only to the point where state can be retained in both the core and the caches. Intermediate states such as C1E, which achieve lower leakage with Vcc reduction yet maintain the advantages of a cache coherent state with low exit latency, have been implemented in recent processors.

The mobile product of the Merom processor family has added a state called Enhanced Deeper Sleep state (referred to as the C5 state), in which Vcc is reduced even further, that is, below the cache retention voltages. In C5, the Vcc to the core is just high enough that the processor core retains its state. At these voltage levels, leakage per transistor is low; however, given that the processors have millions of such leaky devices, it still adds up to a significant power loss.

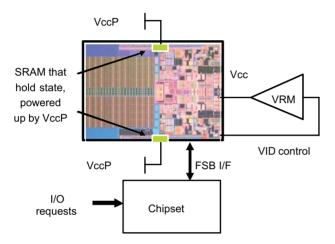

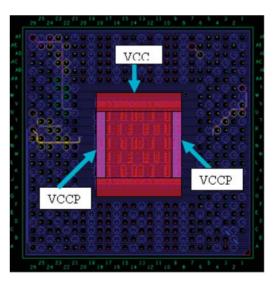

In DPD the critical state of the processor is saved in a dedicated SRAM on-chip that is powered by the I O power supply for the chip (VccP), and then the core voltage is reduced to a very low level via the Voltage Regulator Module (VRM). Figure 1 shows the processor-VRM connectivity. At this point, it is

equivalent to the Vcc core being powered off, i.e., not consuming any power. Upon a break event such as an interrupt, the processor signals the VRM to ramp the Vcc back up, relock its PLLs, and turn clocks on. It then does an internal RESET to clear the states, restore the state of the processor from the dedicated SRAM, and open up the L2 cache. It then continues program execution from where it left off in the execution stream. All of these steps are completed in 150–200 us, all in the processor hardware, thereby making it transparent to the operating system and the existing power-management software infrastructure.

Figure 1: Voltage control for processor.

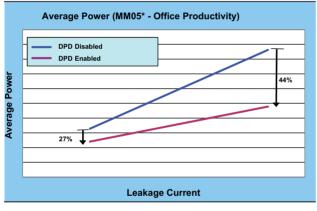

Because the entry and exit are managed entirely by the processor and do not require software assistance, DPD can be enabled under existing operating systems and platforms. DPD achieves a breakthrough for idle power since it is agnostic to Vcc min and provides a minimal power consumption state with a short exit latency. Preliminary results on silicon show that the DPD feature reduces processor average power by 27 percent to 44 percent as measured by the Mobile Mark 05 battery life benchmark.

#### Quad-Core idle power improvements

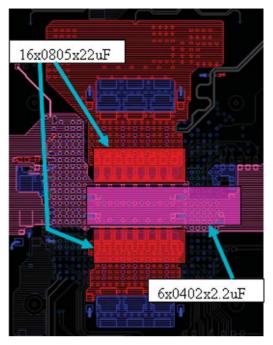

Until a few years ago, quad-core processors were used only in server platforms. Now they are available as mainstream desktop processors. In the Penryn family of processors, the Intel Core 2 Extreme processor offers four cores for the mobile platforms. To provide users with a battery life of greater than 2.5 h for DVD playback, it was necessary to reduce the idle power of the quad-core processor. Previous-generation quadcore processors supported only the Autohalt state and hence were not optimal for the mobile market segment.

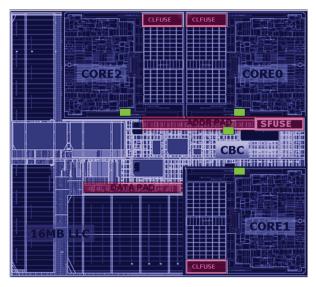

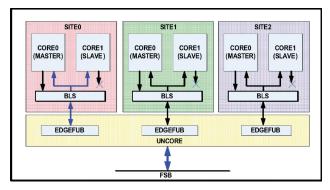

Quad-core processors are implemented in a multi-chip package (MCP) configuration. The two dual-core

processor dice, referred to as the "Master" and "Secondary" sites, have independent PLLs, so the dice can run at different frequencies but share a common voltage plane. The Master die controls the voltage sent to the VRM and the voltage supplied to both dice. The secondary site coordinates its voltage requirements with the master die. The Penryn family of processors expands this coordination functionality for Deeper Sleep state support by using the same interface to communicate information regarding the sleep states of the cores. Each core pair on a die will resolve the correct idle state to enter. They will wait for the core pair on the other die to be ready to enter an idle state. At that point the Master die determines the resolved idle state and puts the package and the platform into that state.

#### Server idle power improvements (CC3)

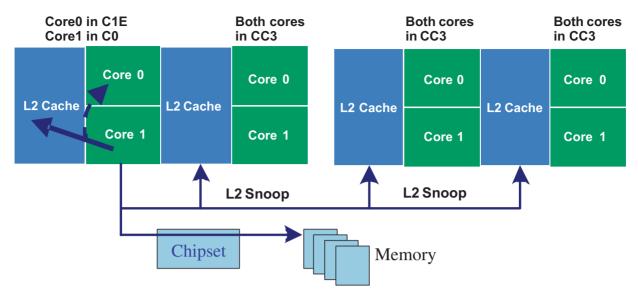

The server versions of the Penryn family of processors are targeted for single-socket and multi-socket workstations and servers. In multi-socket platforms, a memory access from any core generates snoops to all other cores and sockets. Activity related to snoops of processor caches burns about 30 percent of active core power. If a core is in the idle state, it has to be woken up so that its caches can be queried for the data being requested by the snoop. After the snoop data has been returned to the requesting core, the woken core can return to the idle state. The wakeup and reentry negatively affects the idle residence and energy usage. By avoiding snoops into idle cores, this power can be saved.

In processors that predate the Penryn family of processors, the idle cores were put into Core C1 (CC1), which is a snoop-able state.

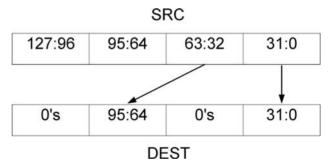

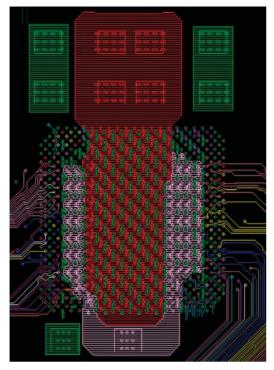

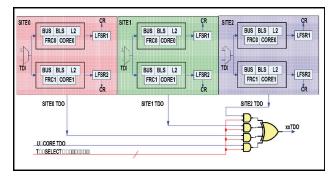

In the Penryn family of processors, idle cores can be put into Core C3 (CC3), which is a non-snoop-able state. The first-level caches are flushed into the L2 cache before putting cores into CC3. This prevents cross-core snoops and therefore the additional power burnt for snoops. Figure 2 shows how snoops are routed based on the cores' CC states. The additional latency to enter CC3 is insignificant (less than 1 us). This allows CC3 to be used as a replacement for CC1 with no affect on software and operating systems. In cases in which the additional latency cannot be tolerated, the CC3 state can be exposed by the ACPI interface as C2 [3]. This lets the Operating System Power Management (OSPM) layer pick either CC1 or CC3, based on the latency and policy settings.

Figure 2: CC3 and cache snoops.

The estimated savings of CC3 relative to CC1 are directly proportional to the number of snoops that occur during the sleep state. In an idle scenario, the snoops in the system are very low. In a fully-loaded scenario, the residence in CC1 CC3 is very low. Hence, the savings in idle and fully-loaded scenarios is less than when the system is lightly loaded. On average, the expected power savings from this feature is about 10 percent.

Even though we have been discussing this as an idle power improvement, it is more than that. In today's typical server platform there are two, four, or more cores. Chances are one or more of these cores is in Idle, except for periods when the servers are under peak load conditions. The idle cores will enter CC3 and reduce the system power.

The other important aspect for server power savings is the fact that there are hundreds or thousands of servers in a server farm. A 10 percent reduction in energy usage not only translates into reduced energy costs but also increases the performance watt cubic feet ratio of the server farm.

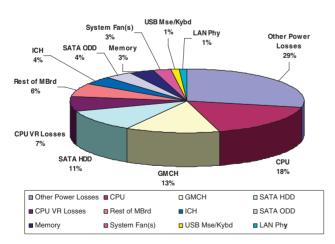

#### Desktop idle power improvements

Battery-life requirements spurred the innovations and enhancements to the sleep states in the mobile platform. Non-mobile platforms do not have a battery life requirement; instead, the focus there is to reduce overall energy usage. Energy Star requirements in the United States and similar requirements elsewhere in the world specify the maximum energy usage under various idle conditions for compliance. The energy usage in Idle is directly determined by the deepest idle power sleep state. When the processor is in a deep sleep state, the activity on the platform is very low. Hence, the total power and energy savings on the platform will be equal to the sum of the savings in the processor, the chipset, the VRM, et cetera [5].

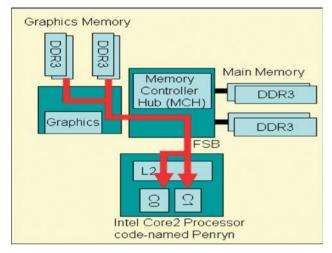

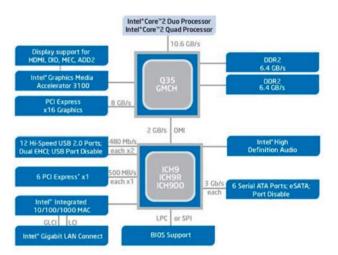

The desktop processors that predate the Penryn family of processors used the Autohalt and Stop Grant states for the processor. The Penryn family of processors adds support for Deeper Sleep state in desktop platforms to lower the processor and platform idle power. The processor communicates to the platform (via the Graphics Memory Controller Hub (GMCH) and I O Controller Hub (ICH)) that it is in the Deeper Sleep state. This allows the GMCH and ICH to power off portions that are required to service the processor requests. This enables further reduction of the platform power when the processor is idle.

The Deeper Sleep state reduces processor power consumption by reducing the voltage of the processor to a lower level. At this level, the processor cannot execute instructions, but its state is retained. When in a sleep state, the power is determined by the amount of leakage in the processor. Leakage is a strong function of the voltage, and hence it is lower in the sleep states in which voltage is reduced. The idle power in the Deeper Sleep state was estimated to be significantly lower than the power in Autohalt or Stop Grant state due to the associated voltage reduction. The target power in the Deeper Sleep state is about 50 percent lower than the power in the Autohalt and Stop Grant states.

The Penryn family of processors' desktop platform also implemented one more platform power-saving

feature along with the Deeper Sleep state. The VRM losses can amount to more than 10 percent of the platform power when in idle state. Most VRMs are optimized to work at medium to highly-loaded conditions. This means that they are less efficient when they are lightly loaded as in the case of the processor being in Deeper Sleep state. The Penryn processor family communicates to the VRM when it enters the Deeper Sleep state, and it lets the VRM shut down all but one phase. This reduces the efficiency of the single active phase.

Desktop platforms use both the quad-core and dualcore processors of the Penryn family. Support for the Deeper Sleep state is available in both the dual- and quad-core configuration. The challenges of extending Deeper Sleep state support to the quad-core configuration are described in the previous section.

#### Enabling deeper sleep state on desktops

The Deeper Sleep state was exposed in the ACPI tables [3] as the C3 state. The Deeper Sleep state has a longer latency to memory traffic and interrupt response compared to the Autohalt and Stop Grant state as a result of its having to ramp up the voltage to the processor before responding to memory snoops and interrupts. There was a concern that this increased exit latency could have two undesirable consequences. Firstly, devices that were not designed to tolerate the latency to memory accesses could have buffer overruns and fail. Secondly, specific applications could suffer performance degradation due to the increased interrupt latency. To address the concerns, the exit latency was tuned down to the minimum value possible in the platform timers via a BIOS configuration. Various peripherals such as USB and Firewire (IEEE 1394) were tested for memory access latency increases. Benchmarks such as Sysmark were tested to understand the implications of increased interrupt latency. The results showed that the device functionality was unaffected, and the benchmark score differences were within the normal run-to-run variations. Performance benchmarks such as SPEC\* do not have to be tested with Deeper Sleep because the processor is never idle during those benchmark runs.

The conclusion was that introducing Deeper Sleep state to the desktop platform did not have any noticeable adverse impact.

# Power constrained performance in multi-core processors

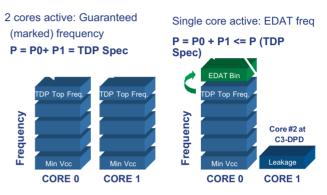

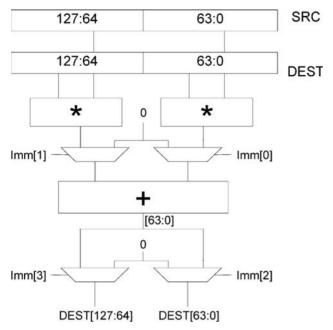

EDAT takes advantage of the power headroom of the idle core to boost the performance of the active core

while running an ST application. The EDAT frequency, which is pre-programmed in the chip, is chosen such that the total power still remains within the specified TDP as illustrated in Figure 3. In the Penryn mobile platforms, this optimization provides a 10 percent frequency boost for ST applications. The Penryn family of processors also implements a hysteresis mechanism that allows it to tolerate short wake-up intervals of the idle core without having to exit the EDAT frequency. This helps minimize performance loss in high-interrupt-rate workloads.

Figure 3: EDAT power budget reallocation.

Multi-core architectures with two, four, or more cores are the standard for power-efficient computing. However, software is lagging in terms of being able to employ all available cores, either because applications have limited threading potential or because tools are not readily available to (re-)write or (re-)build code into threaded applications. As the number of cores within a package grows, many platforms, mobile in particular, become thermally constrained because they are designed to a power target primarily based on form factor. For multi-core designs, this power target usually assumes a workload that pushes the TDP envelope of all the cores. This implies that workloads that do not utilize all the cores underutilize the thermal capacity of the platform. This phenomenon will only grow more prevalent as the computer industry heads towards enabling smaller and cooler form factors.

The Penryn family of processors implemented EDAT in dual-core and dual EDAT in quad-core configurations to intelligently utilize the power headroom from idle cores and opportunistically boost the performance of applications that do not utilize all available cores, without exceeding the system thermal design constraints.

#### **EDAT** principles

EDAT operation is based on the following assumptions:

#### List Item (Number Type: 1,2,3,...)

- 1. The EDAT frequency  $(f_{EDAT})$  for dual-core and quad-core processors is one frequency bin—typically 267 MHz or 333 MHz—over the maximum TDP-limited (guaranteed) frequency.

- 2. In dual-core processors, running one core at EDAT frequencies while the other core is idle will not exceed the TDP limit of the processor. Similarly, in quad-core processors, running one or two cores at EDAT frequencies while the other cores are idle will not exceed the TDP limit of the processor.

- 3. The EDAT frequency is requested by software via the legacy SpeedStep interface that sets the processor's frequency and voltage (F V) operating point.

- 4. The processor will transition to  $f_{EDAT}$  only if the appropriate number of processors is idle and if the operating system requests the highest performance state (P-state).

- 5. If there are not enough idle cores available to meet the EDAT criteria when the operating system requests the highest P-state, then the processor will run at the guaranteed operating point.

Assumptions 1 and 2 allow worst-case power assumptions to be applied to running cores during EDAT operation without having to worry about violating TDP limits.

Assumptions 3 and 4 ensure that EDAT will not be activated independently by hardware, without an operating system request, to enter a high-performance state; therefore these assumptions prevent the processor from consuming high power while lightly loaded. These assumptions also ensure that the processor will deliver at least the guaranteed performance level regardless of whether EDAT can be activated.

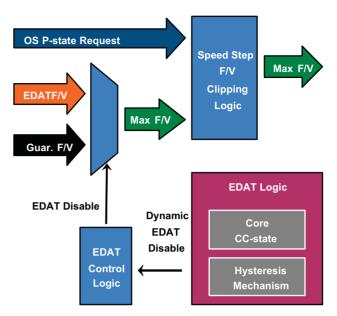

(Figure 4) depicts how the SpeedStep mechanism normally takes operating system P-state requests (i.e., F V operating point) and compares them against a fixed guaranteed F V operating point before determining the processor's "resolved" F V operating point. If the requested operating point is above the guaranteed operating point, the request is clipped to the guaranteed operating point. It also shows how EDAT dynamically changes the F V limit between the guaranteed and EDAT limit. The additional logic lets the processor run at the higher EDAT frequency based on how many cores are active, and a hysteresis mechanism ensures the hardware does not switch too often between the guaranteed and EDAT operating points.

Figure 4: EDAT control mechanism.

#### Idle cores and wake-up rates

The number of idle cores is one of the inputs to the EDAT decision logic. For the Penryn family of processors, cores are considered idle when their CC state is CC3, CC4, or CC6. In these states, cores consume only leakage power, and their clock distribution networks are shut off, which frees up TDP headroom for any active cores to use to run at  $f_{EDAT}$ . Furthermore, dedicated caches/buffers are flushed in these states, which allows any active cores to operate without having to wake up the idle core for cache snooping.

The hysteresis mechanism is the second input into the EDAT decision logic. It permits the processor to run at  $f_{EDAT}$  even if the number of idle cores does not meet the minimum requirement for a limited time, and it ensures that the processor stays within power and thermal constraints. This addresses a performance glass jaw that could be encountered if EDAT is simply disabled as soon as idle cores wake up.

Without the hysteresis mechanism, it is possible for idle cores to be frequently woken up by break events but remain active just long enough to service them before going idle again. Service times can be as short as 10 us to 20 us for Timer Interrupt Service Routines. This can cause rapid transitions in and out of the EDAT operating point and result in performance degradation due to SpeedStep transition overhead and from running the processor at the guaranteed frequency while servicing the break event. A common example of this is when multimedia applications set the timer interrupt rate to 1000 interrupts per second. Having two cores active for 10 us to 20 us at a time is not likely to cause any thermally significant change on the platform since thermal time constants are in milliseconds. This means that EDAT does not have to be deactivated every time idle cores wake up. The hysteresis mechanism detects these situations and avoids unnecessary SpeedStep transitions.

An example of how the hysteresis mechanism works in a dual-core scenario is illustrated in Figure 5.

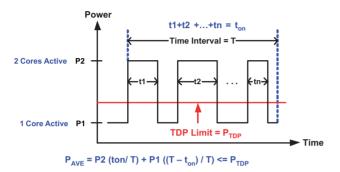

Figure 5: Hysteresis mechanism and average TDP.

• P1 is the worst-case power usage when one core is active at  $f_{EDAT}$ , and P2 is the worst-case power usage when two cores are active at  $f_{EDAT}$ . PTDP can be arbitrarily chosen to be some small percentage, less than 5 percent, higher than the TDP of a top-bin, non-EDAT processor. In order to allow two

cores to run at  $f_{EDAT}$ , platform voltage regulators need to be able to supply the current for two cores active at that frequency for short durations. The cost of supplying the larger current for short durations is usually small and is expected to add an insignificant cost to the platform.

- The time interval, T, is in milliseconds and is based on platform thermal time constants. Using this definition of T, along with the power data above, it is possible to compute the time that two processors can be at  $f_{EDAT}$ , ton, such that the average power, PAVE, over the interval, T, is less than or equal to PTDP.

- If two processors are active at  $f_{EDAT}$  for more than ton in any interval, T, the hysteresis mechanism "expires" and EDAT is disabled. The hysteresis mechanism also gates re-entering  $f_{EDAT}$  to avoid pathological cases in which a core immediately goes into CC3 right after exiting  $f_{EDAT}$ , the processor reenters  $f_{EDAT}$ , and the idle core comes out of CC3. In this example, the total time that two cores are active at  $f_{EDAT}$  could exceed ton across the two  $f_{EDAT}$ periods.

#### EDAT extension into quad-core architecture

EDAT support in Penryn quad-core processors dubbed Dual EDAT—was achieved in the same way that we enabled Deeper Sleep State in quad-core processors. The quad-core power-management coordination functionality was extended for Dual EDAT to

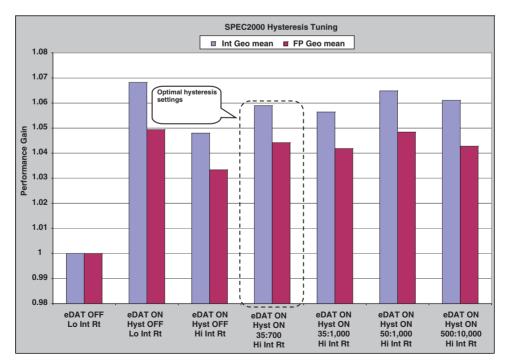

Figure 6: EDAT hysteresis mechanism tuning (Estimated SPEC\* CPU2000 as measured on pre-production systems).

share core idleness information and if EDAT was enabled by BIOS and or software. Each site locally resolved whether or not to allow the processor to run at EDAT frequencies, and it was expected that, in steady-state, they would both either allow or disallow the processor to run at  $f_{EDAT}$  frequencies.

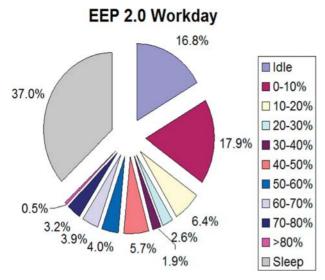

#### RESULTS

#### DPD

Average power on the Penryn mobile processor was benchmarked using the MobileMark (R) 2005 (MM05) battery life benchmark. The benefit of DPD is shown in Figure 7. These measurements were done on multiple Penryn processor parts with varying leakage power behavior. DPD reduced the average power by approximately 40 percent or more on most of the parts tested. This testing was done on Intel Customer Reference Board platforms using a fresh build of Windows XP\* and the MM05 benchmark according to the guidelines specified by BAPCO\* [6]. The processor power was measured by sensing the processor voltage and current during the MM05 run and averaging it.

Figure 7: DPD power savings.

#### Deeper sleep in mobile quad core processors

The same measurements as for DPD (listed above) were done for mobile quad-core processors. The average power on MM05 under Windows XP\* was within 15–30 percent of the dual-core processors.

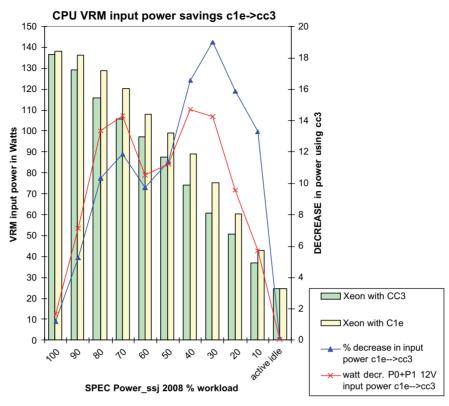

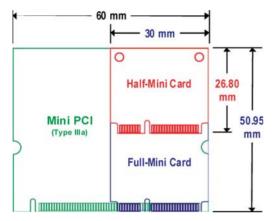

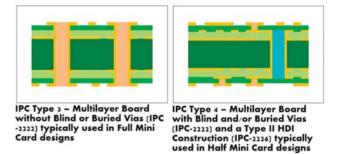

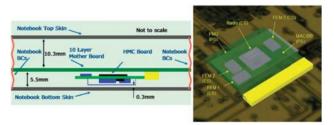

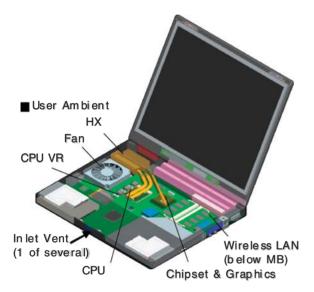

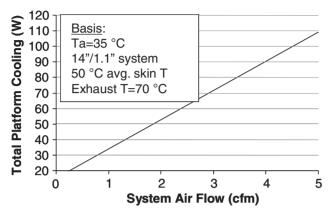

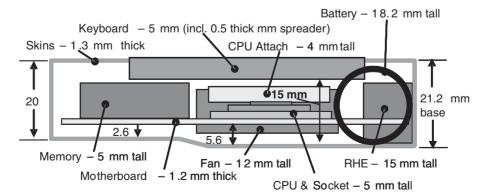

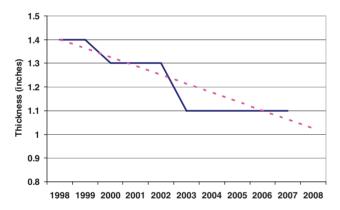

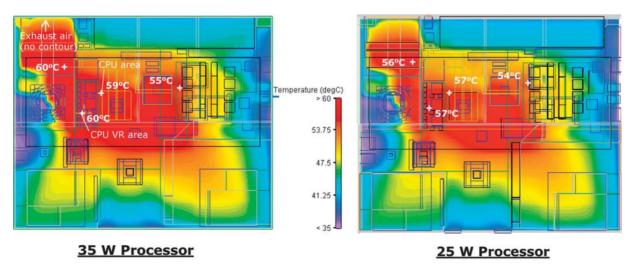

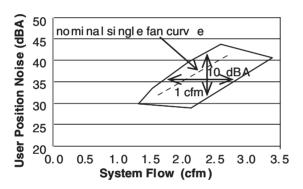

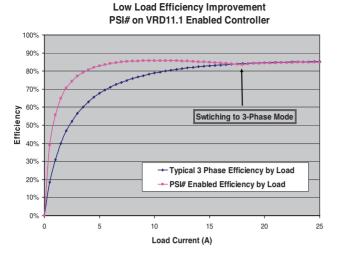

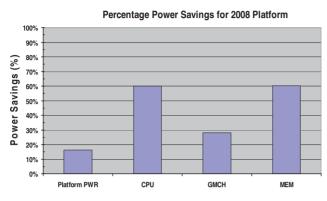

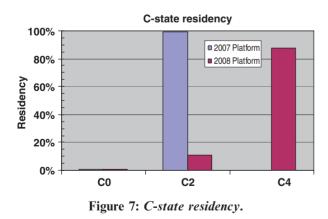

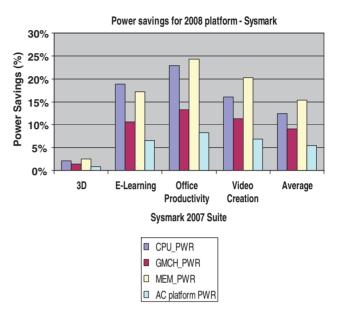

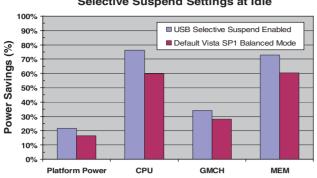

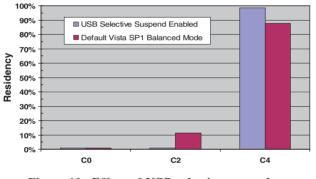

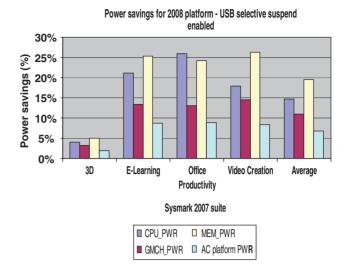

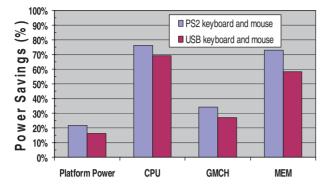

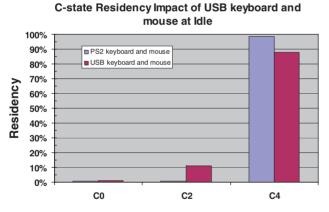

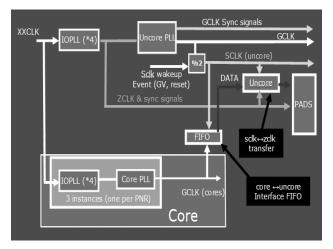

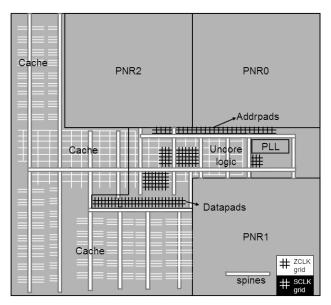

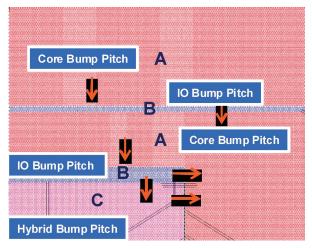

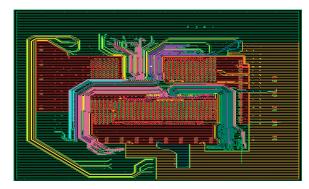

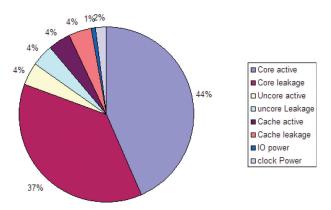

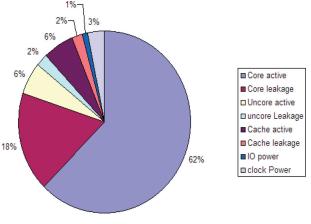

#### CC3 in servers