# Intel's 45nm CMOS Technology

Intel Technology Journal Q2'08 (Volume 12, Issue 2) focuses on Intel® 45nm high-k metal gate silicon technology. To quote Gordon Moore, co-founder of Intel, "this is the biggest change in transistor technology in 40 years." In this journal are seven papers that cover the details of transistors and interconnects, variation and design for manufacturability, and packaging and reliability.

#### Inside you'll find the following articles:

45nm High-k+Metal Gate

Strain-Enhanced Transistors

45nm SRAM Technology Development and Technology Lead Vehicle

Process and Electrical Results for the On-die Interconnect Stack for Intel's 45nm Process Generation 45nm Design for Manufacturing

45nm Transistor Reliability

Managing Process Variation in Intel's 45nm CMOS Technology

Flip-Chip Packaging Technology for Enabling 45nm Products

Volume 12 Issue 02 Published June 17, 2008 ISSN 1535-864X DOI: 10.1535/itj.1202

# Intel® Technology Journal Intel's 45nm CMOS Technology

## **Articles**

| Preface                                                                                                 | iii |

|---------------------------------------------------------------------------------------------------------|-----|

| Foreword                                                                                                | V   |

| Technical Reviewers                                                                                     | vii |

| 45nm High-k+Metal Gate Strain-Enhanced Transistors                                                      | 77  |

| Process and Electrical Results for the On-die Interconnect<br>Stack for Intel's 45nm Process Generation | 87  |

| Managing Process Variation in Intel's 45nm CMOS Technology                                              | 93  |

| 45nm SRAM Technology Development and Technology Lead Vehicle                                            | 111 |

| 45nm Design for Manufacturing                                                                           | 121 |

| 45nm Transistor Reliability                                                                             | 131 |

| Flip-Chip Packaging Technology for Enabling 45nm Products                                               | 145 |

| Intel Technology Journal, Volume 12, Issue 2, 2008 |  |

|----------------------------------------------------|--|

| inter recimology Journal, Volume 12, Issue 2, 2000 |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

| THIS PAGE INTENTIONALLY LEFT BLANK                 |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

|                                                    |  |

#### **Preface**

#### By Lin Chao Editor and Publisher, *Intel Technology Journal*

Hello. This Q2'08 Intel Technology Journal (Vol. 12, Issue 2) covers Intel's 45nm CMOS technology which proved pivotal to the advancement in silicon processes technology by extending Moore's Law.

On a personal note, it has been a privilege for the past 12 years to serve as your publisher and editor for this *Intel Technology Journal* (ITJ). This is my last issue as publisher and editor. My thanks to the many of you who have read ITJ since it went online in 1997. ITJ was a pioneer and was among the first technical journals to publish on the Web, and use the Web as its sole publishing means. I remember in 1996 making the decision to publish the ITJ solely online and at the time thinking the Web is risky, but worth trying. Time has shown that the Web was the right decision!

In future, this Journal will be integrated into Intel Press publications.

ITJ has been a repository of Intel technical advancements. ITJ started in 1979 and we are making preparations to make some of the earliest papers available for sharing. I wish to thank the authors who shared with a world-wide community their knowledge and insights about how the technology came into being; after all, who knows better than the actual people who worked on it? Indeed, the authors are also the people who worked directly on the technology. To the authors, I am proud and grateful to have gotten to know you and shared your passions and the heights and lows of advancing the forefront of technology. Thank you to this journal's dedicated team, to Intel's management for your support, and the world-wide community of readers and authors; I am very proud of what we created together. Thank you.

This *Intel Technology Journal* (Vol. 12, Issue 2) focuses on Intel® 45nm high-k metal gate silicon technology. To quote Gordon Moore, co-founder of Intel Corporation, "this is the biggest change in transistor technology in 40 years." In this journal there are seven papers that give in-depth coverage to three key aspects of the technology's transistors and interconnects, variation and design for manufacturability, and packaging and reliability. The new process also produces Intel's first completely lead-free microprocessor products.

Two papers look at transistors and interconnects. The first paper reviews, for 45nm technology, the details of the high-k+metal gate transistors that have been introduced for the first time into high-volume manufacturing. The second paper introduces the issues associated with on-die interconnects and describes how they are addressed on Intel's 45nm high-performance logic process technology. The on-die interconnect stack for Intel's 45nm process generation delivers a 2X higher area density, a 10% lower average capacitance, and improved power distribution.

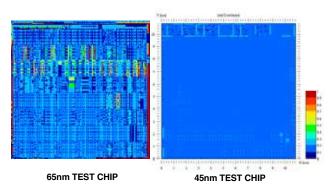

The next three papers look at manufacturing issues related to variations and designs. The third paper states that process variation is not an insurmountable barrier to Moore's law, but is simply another challenge to be overcome. This is illustrated with data from the 45nm process generation where process variation is shown to be at least equivalent to (and in many cases better than) process variation in the 65nm- and 90nm-process generations.

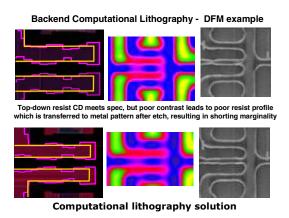

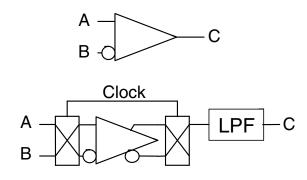

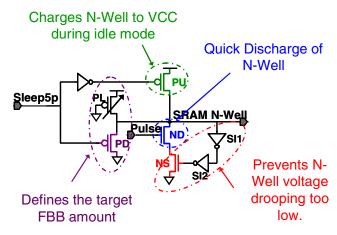

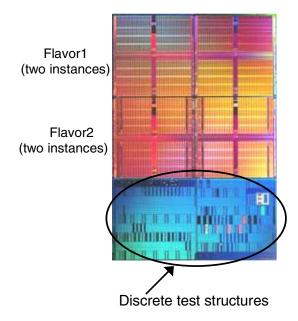

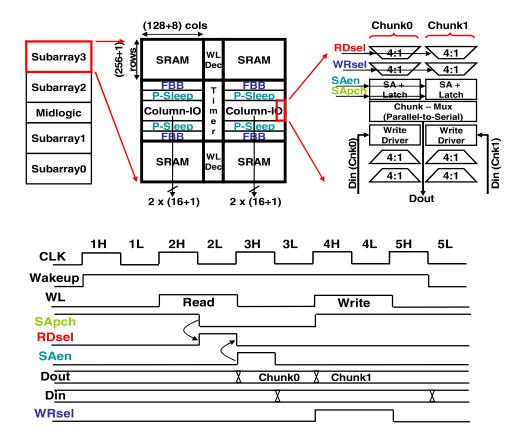

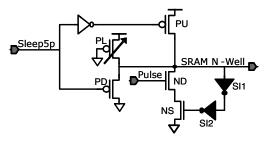

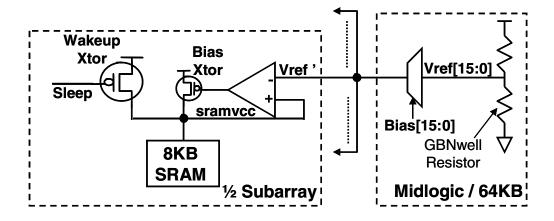

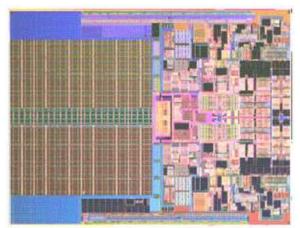

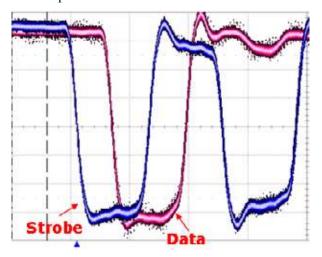

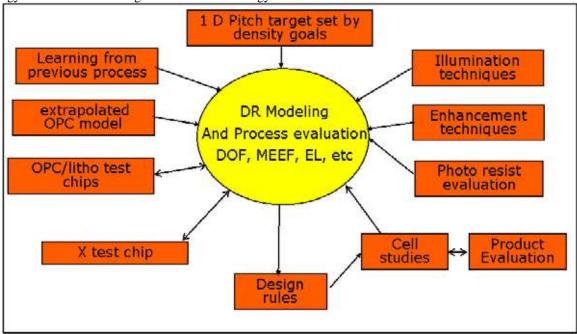

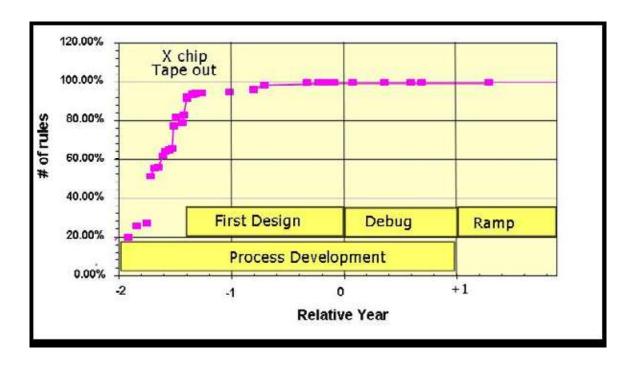

The fourth paper looks at 45nm SRAM as a lead test vehicle. Every new generation of process technology at Intel is developed and certified using an SRAM-based "X-chip." X6 is the technology lead vehicle used for the 45nm technology serving as a platform for the co-optimization of circuit design and process technology for SRAMs as well as critical design evidence for products. The fifth paper reviews the complex dependencies of design and process to be able to manufacture into microprocessor products. Co-optimization between design

and process is required for a highly manufacturable process technology. This paper discusses how cooperation between design and process meets the challenges for maintaining Moore's Law while delivering fast ramp-up and high yields. The variation, density, and yields on the 45nm process show the success of this Design for Manufacturing (DFM) methodology.

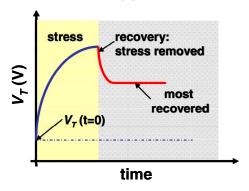

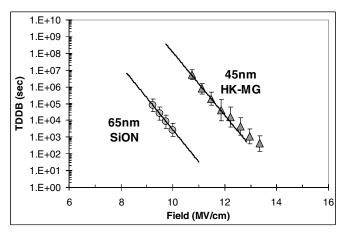

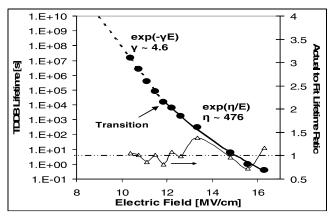

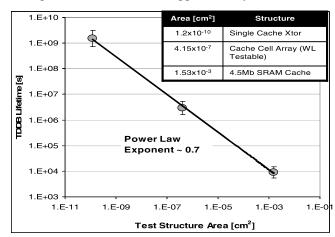

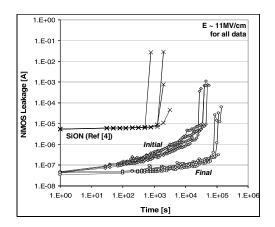

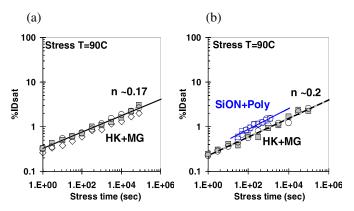

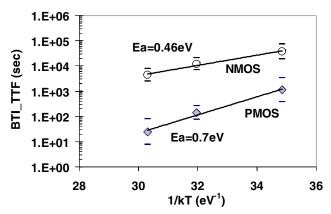

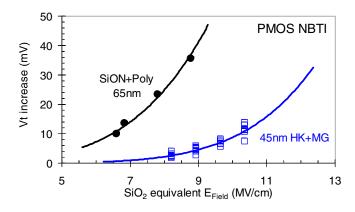

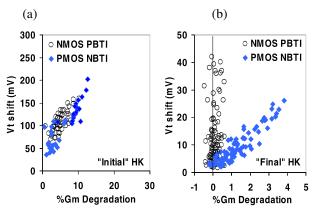

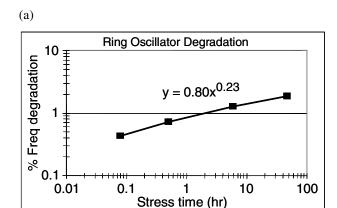

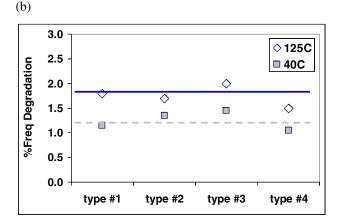

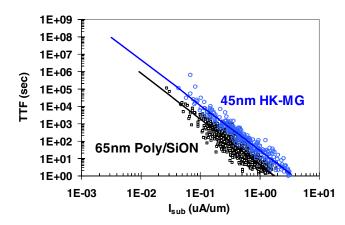

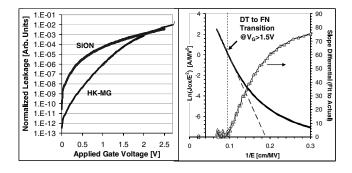

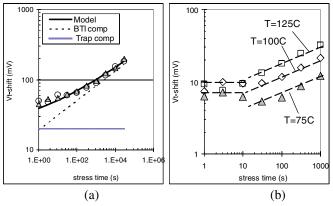

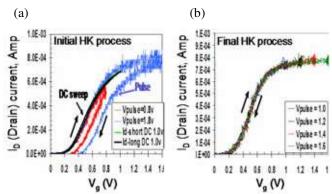

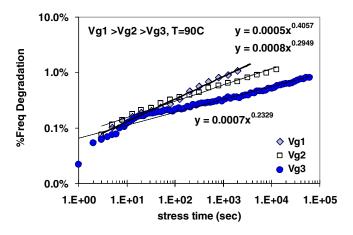

The final two papers look at packaging and reliability. The sixth paper reviews in depth the reliability of Intel's 45nm HK+MG transistors demonstrating that these devices deliver reliability comparable to conventional SiO<sub>2</sub> devices at ~30% higher operating fields with negligible stress-induced leakage current (SILC) degradation.

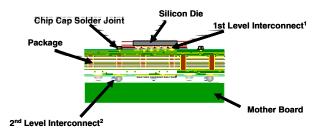

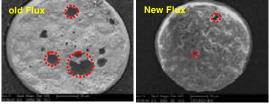

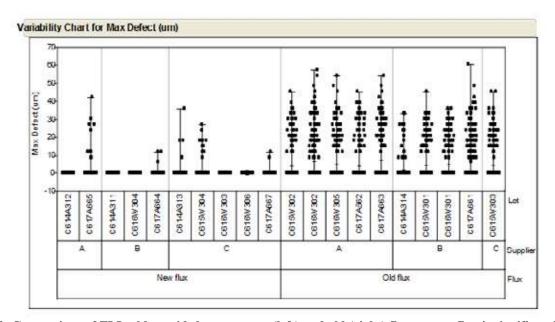

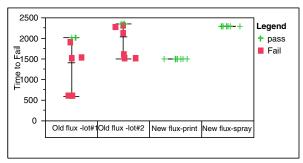

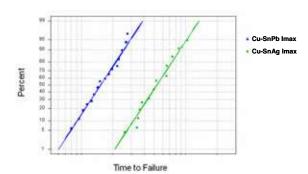

In the seventh and final paper, we shared some of the key challenges associated with the development of a high-volume manufacturing compatible assembly process for packaging Intel's 45nm, completely lead-free devices. Key technical challenges were addressed through development of novel FLI solders, fluxing material, and process solutions. Small form-factor packaging challenges were overcome by a series of innovative materials and process changes to achieve a reduction in form factor while meeting the technology reliability goals. This enables Intel's continuing leadership in thin and light notebooks and smart phone devices.

We are very proud to have eliminated the use of lead in this technology which also makes Intel a leader in achieving environmentally green products.

#### Foreword

By Bill Holt

Senior Vice President, General Manager, Technology and Manufacturing Group

In 1965, as the first integrated circuit products entered the marketplace, Intel co-founder Gordon Moore made the now famous observation that the number of transistors on a chip doubled periodically. Not only would Moore's dictum prove true, its longevity has surprised everyone, including Moore himself. The most powerful chips today have over two billion transistors each, up from less than a hundred components per chip when Moore made his observation. This steady, relentless increase in transistor density has made computing powerful, affordable, and ubiquitous. It has enabled the internet age.

While Intel's 45nm technology represents the next step in this continual evolution, lurking under the hood are some revolutionary changes in materials and structures. As the transistor was scaled, fundamental limits of some of the building blocks were reached. One component of the transistor, the gate insulator, had been thinned successively to the point that in the prior generations it was a scant 5 atomic layers thick and could be scaled no further. In anticipation of this issue, Intel began a program in the 1990s to find a new material to replace silicon dioxide, the material used for the gate insulator for over 40 years. The result was a new insulator material based on the element hafnium. This new high k (high dielectric constant) gate insulator needed to be coupled with a change to another component of the transistor, the gate electrode, which was changed from silicon to a proprietary set of metals. Intel's 45nm CMOS technology is the first in the world to feature these new materials, in what Gordon Moore has called "the biggest change in transistor technology since the introduction of the polysilicon gate MOS transistors in the late 1960s." Interestingly, Intel led the move to manufacturing polysilicon gate electrodes in the 1960s and now is leading the move back to metal gate electrodes. Intel's ability to lead the industry in delivering this exciting new technology is a reflection of a strong research and development pipeline, and the dedication, discipline, and hard work of hundreds of talented engineers.

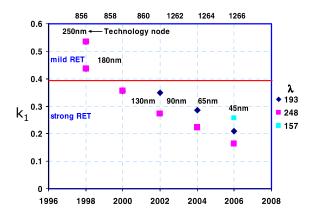

Beyond the significant changes to the transistors, this technology also features improved interconnects, the wires that link the transistors together on a chip. Ideally, these wires transit signals across the chip with rapid speed and low power consumption. 45nm interconnects are, on average, 10% faster than those of the previous generation. The technology also needs to be affordable. Intel's unique low-cost patterning techniques allowed the extension of proven 193nm dry lithography to 45nm at a lower cost than immersion lithography. The technology also supports Intel's green computing initiative. In addition to the lower power consumption levels that result from the new transistors and interconnects, Intel's 45nm technology features another first: a lead-free process and enablement of lead-free packaging.

A key strength that allows Intel to bring new technologies to market quickly lies in its advantage as an integrated device manufacturer to co-optimize the product design and the manufacturing process. Design for manufacturability techniques, methods for dealing with variation, and the ability to prototype circuits early in the development cycle all lead to a technology that is ready to enter the market early and ramp to high volumes quickly. The details of these aspects of Intel's groundbreaking 45nm CMOS technology are covered in this issue of the *Intel Technology Journal*.

| Intel Technology Journal, Volume 12, Issue 2, 2008 |

|----------------------------------------------------|

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

| THIS PAGE INTENTIONALLY LEFT BLANK                 |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

### Technical Reviewers for Q2 2008 ITJ

Mohsen Alavi, Technology and Manufacturing Group

Sridhar Balakrishnan, Technology and Manufacturing Group

Ken Brown, Technology and Manufacturing Group

Udi Gavish, Technology and Manufacturing Group

Michael L. Hattendorf, Technology and Manufacturing Group

Debendra Mallik, Technology and Manufacturing Group

Kaizad Mistry, Technology and Manufacturing Group

Gunjan H. Pandya, Digital Enterprise Group

Stephen M. Ramey, Technology and Manufacturing Group

Sunit Rikhi, Technology and Manufacturing Group

Chris Rumer, Technology and Manufacturing Group

Michael J. Smith, Digital Enterprise Group

Krishnamurthy Soumyanath, Corporate Technology Group

Michael R. Stark, Technology and Manufacturing Group

Andrew W.H. Yeoh, Technology and Manufacturing Group

| Intel Technology Journal, Volume 12, Issue 2, 2008 |

|----------------------------------------------------|

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

| THIS PAGE INTENTIONALLY LEFT BLANK                 |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

|                                                    |

## 45nm High-k+Metal Gate Strain-Enhanced Transistors

Chris Auth, Technology and Manufacturing Group, Intel Corporation Mark Buehler, Technology and Manufacturing Group, Intel Corporation Annalisa Cappellani, Technology and Manufacturing Group, Intel Corporation Chi-hing Choi, Technology and Manufacturing Group, Intel Corporation Gary Ding, Technology and Manufacturing Group, Intel Corporation Weimin Han, Technology and Manufacturing Group, Intel Corporation Subhash Joshi, Technology and Manufacturing Group, Intel Corporation Brian McIntyre, Technology and Manufacturing Group, Intel Corporation Matt Prince, Technology and Manufacturing Group, Intel Corporation Pushkar Ranade, Technology and Manufacturing Group, Intel Corporation Justin Sandford, Technology and Manufacturing Group, Intel Corporation Christopher Thomas, Technology and Manufacturing Group, Intel Corporation

Index words: CMOS transistor, logic technology, high-k gate dielectric, metal gate

#### **ABSTRACT**

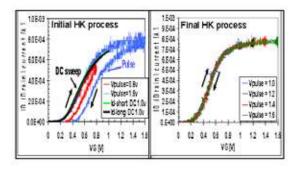

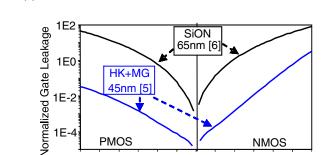

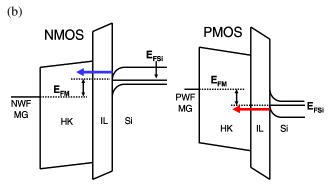

For the 45nm technology node, high-k+metal gate transistors have been introduced for the first time in a high-volume manufacturing process [1]. The introduction of a high-k gate dielectric enabled a 0.7x reduction in Tox while reducing gate leakage 1000x for the PMOS and 25x for the NMOS transistors. Dual-band edge workfunction metal gates were introduced, eliminating polysilicon gate depletion and providing compatibility with the high-k gate dielectric.

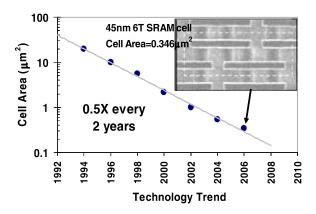

In addition to the high-k+metal gate, the 35nm gate length CMOS transistors have been integrated with a third generation of strained silicon and have demonstrated the highest drive currents to date for both NMOS and PMOS. An SRAM cell size of  $0.346\mu^2$  has been achieved while using 193nm dry lithography. High yield and reliability has been demonstrated on multiple single-, dual-, quad-, and six-core microprocessors.

#### INTRODUCTION

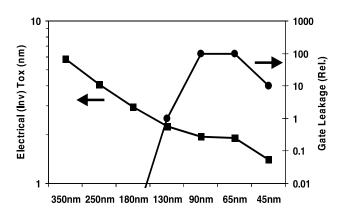

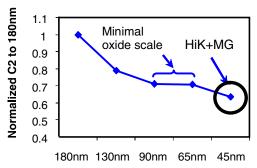

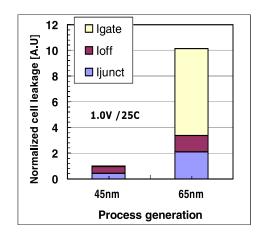

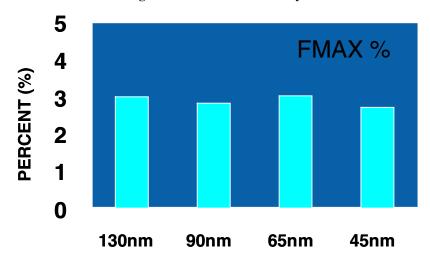

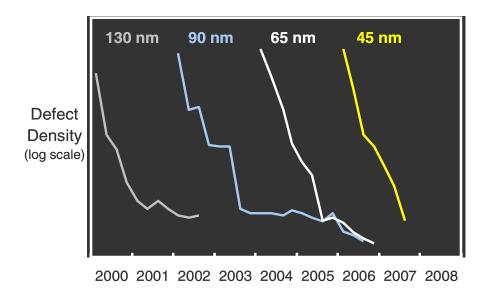

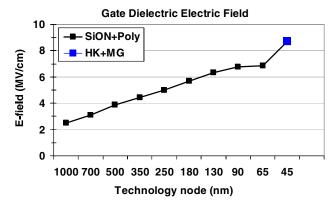

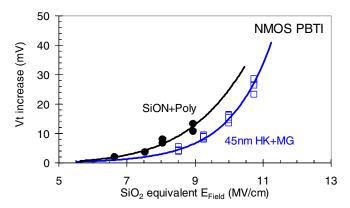

One of the key methods to enable transistor gate length scaling over the past several generations has been to scale the gate oxide. This improves the control of the gate electrode over the channel, enabling both shorter channel lengths and higher performance. As the gate oxide was scaled the gate leakage increased; this increase in gate leakage was insignificant until the 90nm technology node (Figure 1). At the 90nm and 65nm nodes, the scaling of

the gate oxide slowed as a result of the power limitations from the increase in gate leakage. In order to overcome this at the 45nm technology, a gate dielectric with a higher dielectric constant (high-k) has been introduced. This enabled a >25x gate leakage reduction while scaling the Tox by 0.7x.

Figure 1: Trend of inversion Tox and gate leakage vs.

Intel technology node

The introduction of high-k gate dielectrics has been slowed by several issues [2–4]. The first was the interaction by the high-k material with the existing polysilicon gates. This interaction led to high trap densities at the interface that pinned the Vt of the transistor to an undesirable value. The second was the

degradation of the channel mobility in the presence of high-k dielectrics. The third issue was the poor reliability of the high-k dielectric.

The gate electrode effectiveness has also been increasingly impacted by poly depletion effects. This has led to lower drive currents when the transistor is turned on. By selecting a compatible metal gate electrode with the high-k gate dielectric, both the poly depletion effects and the Vt pinning at the high-k/polysilicon interface can be eliminated while providing higher channel mobilities [5].

In introducing high-k+metal gate transistors for the 45nm generation, these significant challenges needed to be overcome. First, we had to determine which material to use for the high-k dielectric and find dual-band edge metals that were compatible with that high-k dielectric. Second, an integrated CMOS flow needed to be developed that matched the channel mobility of SiO<sub>2</sub> while meeting the reliability requirements for the technology. The development of this CMOS flow was complicated by the need to mesh the process requirements of the metal gate process with both the thermal limitations of the junction formation steps and the uniaxial strain-inducing steps, both of which have become central to the transistor architecture.

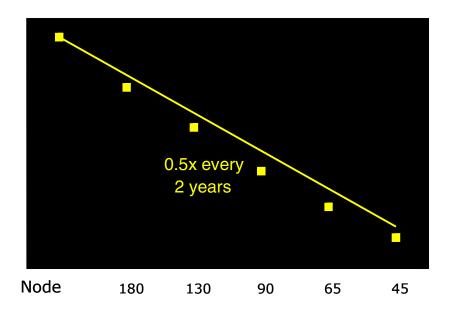

Along with the above-mentioned improvements in performance and gate leakage with high-k+metal gate, a key requirement of the technology node was an increased packing density for the transistors. For each node, an ~50% area scaling is expected, and this technology continues that trend. A key challenge to overcome in this scaling is the loss of performance due to scaling of the stress-inducing features of the technology. Use of 193nm dry lithography for critical layers at the 45nm technology node was preferred over moving to 193nm immersion lithography, due to lower cost and greater maturity of the toolset. In order to achieve the tight 160nm gate and contact pitch requirements, unique gate and contact patterning process flows were developed implemented.

#### TRANSISTOR PROCESS FLOW

The two common methods for introducing a metal gate to the standard CMOS flow include either a "gate-first" or "gate-last" process. Most comparisons of these two process flows focus on the ability to select the appropriate workfunction metals, the ease of integration, or the ability to scale; however, these comparisons typically fail to comprehend the interaction of the process flows with the strain-inducing techniques. By use of a high-k first and metal gate-last flow, it is possible to maximize the benefits of the stress-inducing steps and high temperature junction

formation, while minimizing the thermal processing of the workfunction metals.

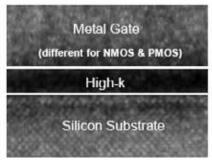

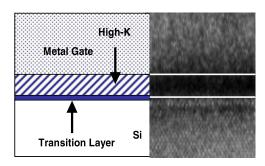

In the metal gate-first flow (Table 1), the high-k dielectric and dual-metal processing are completed prior to the polysilicon gate deposition. The dual metal gates are then subtractively etched along with the poly gates prior to Source/Drain (S/D) formation. In contrast, for the high-k first and metal gate-last flow used in this work, a standard polysilicon gate is deposited after the hafnium-based, high-k gate dielectric deposition (Figure 2). This is followed by a standard polysilicon processing flow through the salicide formation steps.

Table 1: Comparison of unique steps in gate-first and high-k first, metal gate-last process flows. Key differences are highlighted in bold.

| Gate-First                                            | High-k first, Gate-Last                 |  |

|-------------------------------------------------------|-----------------------------------------|--|

| Isolation                                             | Isolation                               |  |

| High-k gate deposition                                | High-k gate deposition                  |  |

| Dual Metal-Gate<br>Deposition                         | Poly-Silicon gate deposition/patterning |  |

| Poly-Silicon gate deposition  Poly-Silicon/metal etch | S/D formation                           |  |

| S/D formation                                         | Salicide/Contact etch stop              |  |

| Salicide/Contact etch stop                            | Poly-Silicon gate removal               |  |

| 1 <sup>st</sup> ILD deposition/polish                 | Dual-Metal Gate<br>deposition           |  |

| Contact formation                                     | Contact formation                       |  |

Figure 2: TEM of high-k/metal gate stack

After deposition of the contact etch stop and the first Interlayer Dielectric (ILD) films, a polish step is used to expose the poly gates and enable removal of the dummy poly. The PMOS workfunction metal is then deposited. A patterning step removes the PMOS metal from the NMOS

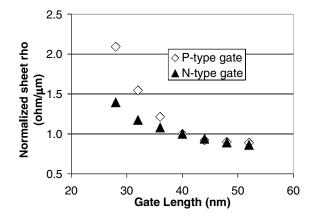

area. The NMOS workfunction metal is deposited, and the gate trenches are filled with Al for low gate resistance. By using novel gap-fill techniques, robust gate resistance is enabled to sub-30nm gate lengths (Figure 3). A metal polish step is used to remove the excess metal and planarize the gate trenches. The flow then continues with the contact and interconnect processing steps.

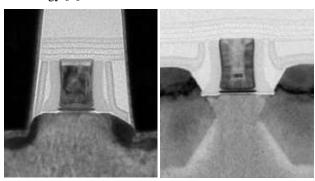

Figure 3: Gate sheet rho versus gate length showing scalability of gate fill process

Figure 4 shows a TEM of the high-k/metal gate NMOS and PMOS transistors with the embedded SiGe S/D strain layer on the PMOS and Ni salicide. The strained silicon techniques that Intel first introduced at the 90nm and 65nm nodes were further enhanced in this generation. The Ge concentration of the embedded SiGe S/D was increased to 30% from the previous generations of 23% in Intel's 65nm technology [6] and 17% in the 90nm technology [7].

Figure 4: TEMs of high-k+metal gate NMOS and PMOS transistors

# DESIGN RULES AND 193NM DRY PATTERNING

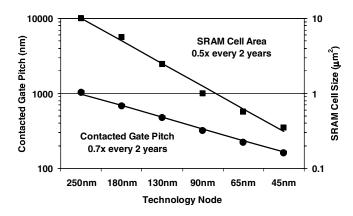

Contacted gate pitch is a key measure of front-end density, and the scaling to 160nm maintains the 0.7x scaling trend (Figure 5). This is the most aggressive contacted gate pitch reported to date for a 45nm high-performance logic

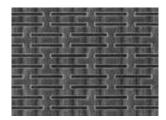

technology. The contact process has also been modified, with trench contacts replacing conventional contacts for lower series resistance. Trench-contact-based local routing improves layout density, especially for cross-coupled inverter pairs that are very common in microprocessor SRAM and register file arrays. Tight pitches and trench contacts allow SRAM cell size to be scaled to  $0.346 \mu m^2$  (Figure 6).

Figure 5: Contacted gate pitch and SRAM cell size scaling trend for Intel's technology nodes

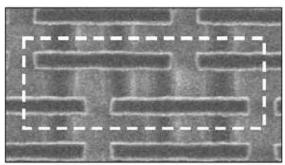

Figure 6: Diffusion and poly layers for 0.346 μm<sup>2</sup> 6-T SRAM cell

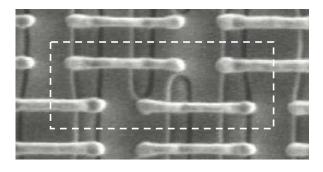

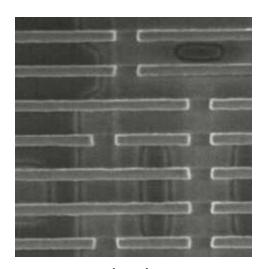

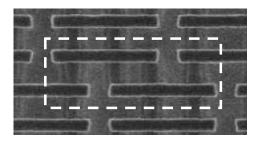

In order to enable these tight pitches by use of low-cost 0.92NA 193nm dry patterning, innovative processes were developed to produce robust patterning. This is demonstrated by the fidelity of the poly lines in Figure 6. The gate patterning process uses a double patterning scheme. Initially the gate stack is deposited including the polysilicon and hardmask deposition. The first lithography step patterns a series of parallel, continuous lines. Only discrete pitches are allowed, with the smallest at 160nm, to assist in the patterning. A second masking step is then used to define the cuts in the lines. The two-step process enables abrupt poly endcap regions, devoid of rounding that allows for tight contact-to-gate design rules (Figure 7). There are no additional masking steps from this process, since the 65nm generation also used two reticles for poly patterning.

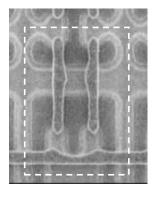

Figure 7: Top-down SEM post-poly-patterning process showing 160nm poly pitch with minimum gate length lines. Note the square poly ends, devoid of rounding.

The contact patterning process uses a similar pitch restriction to facilitate lithography. Trench diffusion contacts run parallel to the gates with discrete pitches, while trench gate contacts run orthogonal to the gates. Use of trench contacts has the added benefits of lowering the contact resistance by >50% and allowing their use as a local interconnect, which improves SRAM/logic density by up to 10%.

#### TRANSISTOR RESULTS

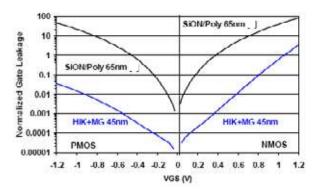

The introduction of the high-k gate dielectric delivered a dramatic gate leakage reduction relative to 65nm transistors of >25X for NMOS and 1000X for PMOS (Figure 8).

Figure 8: Gate leakage reduction of 25-1000x with use of high-k+metal gate relative to 65nm technology

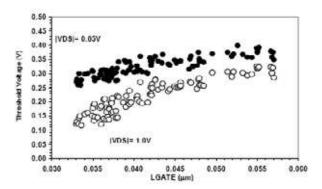

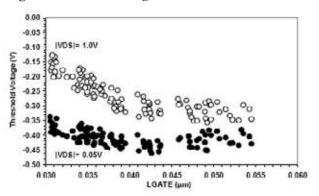

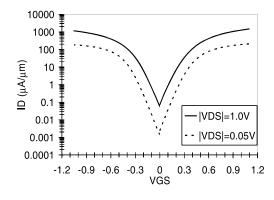

The high-k+metal gate transistors exhibit excellent short channel characteristics due to the combination of Tox scaling and the optimal workfunction metal gates (Figures 9 and 10). The excellent gate control is also illustrated in the well-behaved subthreshold characteristics (Figure 11).

Figure 9: NMOS Vt vs. Lg shows excellent SCE and DIBL

Figure 10: PMOS Vt vs. Lg shows excellent SCE and DIBL

Figure 11: Subthreshold Id-Vgs for both NMOS and PMOS transistors

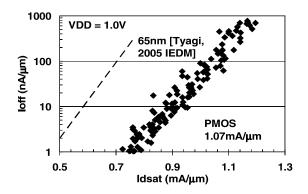

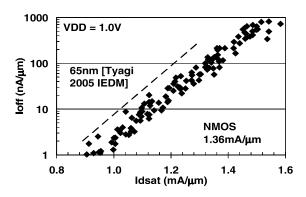

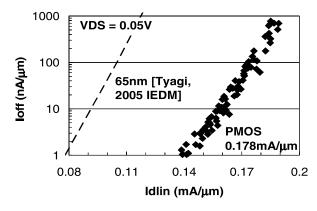

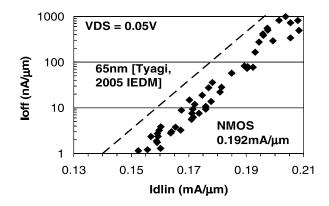

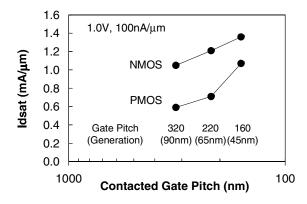

PMOS performance is improved by using high-k+metal gate as well as by the enhancements to the embedded SiGe processing. The PMOS drive current (Figure 12) of 1.07 mA/μm is a marked 51% improvement over 65nm [8]. NMOS drive current (Figure 13) is 1.36mA/μm, 12% better than the previous-generation, 65nm transistors. The average drive current improvement versus 65nm is 32% at the same voltage and Ioff, despite scaled transistor pitch. The linear drive currents show similar enhancements with PMOS (Figure 14) at 0.178mA/μm and NMOS (Figure 15) at 0.192mA/μm. These drive currents are benchmarked at 1.0V, a low 100nA/μm Ioff and at 160nm

contacted gate pitch. Both the saturated and the linear drive currents represent the best drive currents reported to date for a 45nm technology at low Ioff. Figure 16 shows the transistor performance vs. gate pitch for this generation illustrating that both density and performance are improved with this transistor flow.

Figure 12: PMOS Idsat of 1.07mA/μm at 100nA/μm Ioff and Vdd =1.0V

Figure 13: NMOS Idsat of 1.36mA/μm at 100nA/μm Ioff and Vdd =1.0V

Figure 14: PMOS Idlin of 0.178mA/μm at 100nA/μm Ioff and Vds=0.05V

Figure 15: NMOS Idlin of 0.192mA/μm at 100nA/μm Ioff and Vds=0.05V

Figure 16: Performance vs. gate pitch for 90, 65, and 45nm generations

# STRESS ENHANCEMENT IN A METAL GATE FLOW

Since its introduction at the 90nm node, strain has become a central performance enhancement element for the standard CMOS flow. The most commonly used techniques for implementing strain in the transistors include embedded SiGe in the PMOS S/D, stress memorization for the NMOS, and a nitride stress-capping layer for NMOS and PMOS devices (Table 2).

Table 2: Comparison of stress enhancement methods for 65nm and 45nm nodes. New features are highlighted in bold.

| 65nm Method                                           | 45nm Method                                          |

|-------------------------------------------------------|------------------------------------------------------|

| <u>PMOS</u>                                           | PMOS                                                 |

| Embedded SiGe S/D                                     | Embedded SiGe S/D with higher %Ge                    |

|                                                       | Poly Gate Removal<br>Enhancement                     |

| NMOS                                                  | NMOS                                                 |

| Tensile Nitride Cap                                   | Tensile Trench Contacts                              |

| Gate Stress Memorization +<br>S/D Stress Memorization | Metal Gate Stress (MGS) +<br>S/D Stress Memorization |

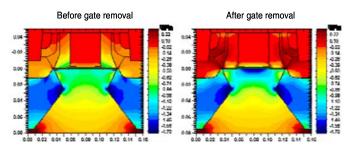

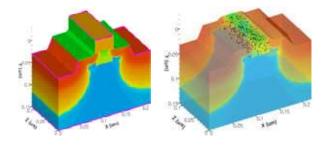

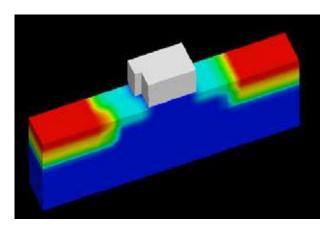

A key benefit of using a gate-last flow comes from removing the poly gate from the transistor after the stress-enhancement techniques are in place. It has been shown that the stress benefit from the embedded S/D SiGe process is enhanced through this removal of the poly gate, since the poly gate acts as a buffer counteracting the effect of the embedded S/D SiGe [9]. This benefit can be illustrated in simulation with an estimated 50% increase in lateral compressive stress by removal of the polysilicon gate (Figure 17). The combined impact of the increased Ge fraction in the embedded S/D and the strain enhancement from the gate-last process allow for a 1.5x higher hole mobility compared to 65nm, despite the scaling of the transistor pitch from 220nm to 160nm.

Figure 17: Stress contours in the PMOS transistor before and after the removal of the polysilicon dummy gate. Stress in the channel is shown to increase 50% from 0.8GPa to >1.2 GPa.

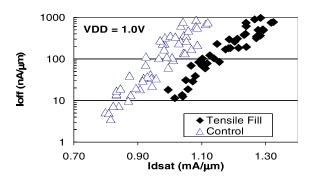

For the NMOS device, two methods of stress enhancement have been employed in this technology. First, the loss of the nitride stress layer benefit, due to scaling the pitch from the 65nm technology node, has been overcome by the introduction of trench contacts and by tailoring the contact fill material to induce a tensile stress in the channel. The NMOS response to tensile (control) vs. compressive contact fill materials is shown in Figure 18. The stress impact of the trench contact fill material on the PMOS device is mitigated by use of the raised S/D inherent in the embedded SiGe S/D process.

Figure 18: Ion-Ioff benefit of tensile contact fill showing a 10% NMOS Idsat benefit. Contact resistance is matched for the two fill materials.

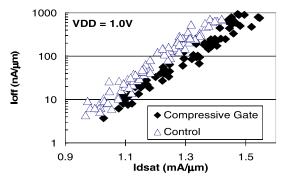

For NMOS stress memorization, there are two primary methods commonly used, one is memorization of stress in the (S/D) of the device and the other is memorization in the poly gate [10]. The metal gate-last flow is compatible with the S/D method while the poly gate component would be compromised. To compensate for this, the poly gate component is replaced by Metal Gate Stress (MGS). i.e., modifying the metal-gate fill material to directly induce stress in the channel [11]. By introducing a gate fill material with a compressive stress, the performance of the NMOS device is enhanced and adds to the contact fill technique (Figure 19). By use of a dual-metal process with PMOS first, the stress of the NMOS gate is decoupled from the PMOS gate through optimization of the PMOS gate stack to buffer the stress.

Figure 19: Ion-Ioff benefit of compressive gate stress showing a 6% NMOS Idsat gain. Tensile contact fill is used on both sets of data.

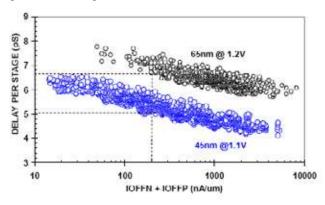

#### RING OSCILLATORS

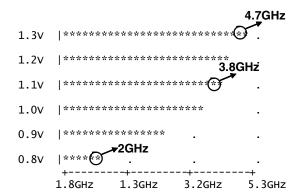

The transistor performance gains are reflected in the ring oscillator performance data. Gate delay data from ring oscillators with a fanout of 2 is benchmarked at  $100 \text{nA}/\mu\text{m}$  Ioff each for NMOS and PMOS, at 1.2 V for 65nm and a lower 1.1 V for 45nm. The ring oscillators use the minimum contacted gate pitch (220nm and 160nm) for

each technology. Despite the scaling of both voltage and gate pitch, FO=2 gate delay is reduced from 6.65pS (65nm) to 5.1pS (45nm), for a gain of 23% (Figure 20). Table 3 breaks out the RO gains between NMOS/PMOS Idsat, Idlin, and the gate and junction capacitances, illustrating the marked impact of the PMOS performance gains on the ring oscillators.

Figure 20: Ring oscillator delay vs. leakage for fanout=2. Comparison of delay for 65nm vs. 45nm is at 1.2 and 1.1V, respectively.

Table 3: Breakdown of RO gains vs. 65nm results. The voltage scaling term accounts for the reduction in VDD from 1.2V (65nm) to 1.1V (45nm).

| Component       | Benefit<br>(%) |

|-----------------|----------------|

| PMOS Idsat      | +13            |

| PMOS Idlin      | +18            |

| NMOS Idsat      | +3             |

| NMOS Idlin      | +2             |

| Cjunction       | +2             |

| Cgate/Cov       | -8             |

| Voltage Scaling | -7             |

| Total           | +23            |

#### **CONCLUSION**

High-k+metal gate transistors have been integrated into a manufacturable 45nm process for the first time. Selection of the metal-gate flow (high-k first, metal-gate last) was made to maximize the benefit from the strained silicon steps. Novel stress techniques were also developed to replace the stress methods that are compromised due to scaling and the metal gate flow. The scaling of the transistor density was achieved through development of new poly and contact patterning schemes The resultant transistors provide record drive current at low leakage and

at tight contacted gate pitch achieving both performance and density benefits. This is demonstrated in the ring oscillators with a 23% gate delay reduction compared to 65nm at the same Ioff and 10% lower VDD.

#### ACKNOWLEDGMENTS

We gratefully acknowledge the collaborative efforts of our colleagues in the Portland Technology Development Group, the Technology Computer Aided Design Group, and in the Corporate Quality and Reliability Group.

#### REFERENCES

- [1] K. Mistry, et al., "A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pb-free Packaging." *IEDM Technical Digest*, 2007, pp. 247–250.

- [2] V. Misra, G. Lucovsky, & G. Parsons, "Issues in High-k Gate Stack Interfaces." *MRS Bull., Vol.* 27, *No.* 3, 2001, pp. 212–216.

- [3] C. Hobbs et al., "Fermi Level Pinning at the Poly-Si/Metal Oxide Interface." *Symposium on VLSI Technology Digest*, 2003, pp. 9–10.

- [4] G. Ribes et al., "Review on High-k Dielectrics Reliability." *IEEE Transactions on Device and Materials Reliability, Vol. 5, No. 1*, 2005, pp. 5–19.

- [5] R. Kotlyar et al., "Inversion Mobility and Gate Leakage in High-k/Metal Gate MOSFETs." *IEDM Technical Digest*, 2004, page 391.

- [6] P. Bai et al., "A 65nm Logic Technology Featuring 35nm Gate Lengths, Enhanced Channel Strain, 8 Cu Interconnect Layers, Low-k ILD and 0.57 um2 SRAM Cell." *IEDM Technical Digest*, 2004, pp. 657–660.

- [7] T. Ghani et al., "A 90nm high-volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors." *IEDM Technical Digest*, 2003, pp. 978–980.

- [8] S. Tyagi, et al., "An advanced low power, high performance, strained channel 65nm technology." *IEDM Technical Digest*, 2005, pp. 1070–1072.

- [9] J. Wang, et al., "Novel Channel-Stress Enhancement Technology with eSiGe S/D and Recessed Channel on Damascene Gate Process." Symposium on VLSI Technology Digest, 2007, pp. 46–47.

- [10] A. Wei, et al., "Multiple Stress Memorization in Advanced SOI CMOS Technologies." *Symposium on VLSI Technology Digest*, 2007, pp. 216–217.

[11] C. Kang, et al., "A Novel Electrode-Induced Strain Engineering for High Performance SOI FinFET utilizing Si (110) Channel for Both N and PMOSFETs." *IEDM Technical Digest*, 2006, pp. 885–888.

#### **AUTHORS' BIOGRAPHIES**

Chris Auth joined Intel in 1997 after completing his Ph.D. degree in Electrical Engineering from Stanford University. He initially developed the NOR flash cell for Intel's 0.18µm node. After joining Portland Technology Development in 2000, he developed the industry's first use of strain for transistor enhancement at the 90nm and 65nm nodes. At the 45nm node, he led the process development and introduction of the industry-first, high-k/metal-gate process. He has received two IAAs, holds five US Patents, and has authored/co-authored 18 publications. His e-mail is chris.auth at intel.com.

Mark Buehler received his B.S. degree in Chemical Engineering from the University of California at Berkeley. He then completed his M.S. and Ph.D. in Chemical Engineering at the University of Washington. In 1995, he joined the Portland Technology Department of Intel Corporation. He has worked in both metal and oxide CMP process development since Intel's 0.25μm technology node. He is currently working on metal CMP for Intel's 32nm and 22nm nodes. His e-mail is mark.buehler at intel.com.

Annalisa Cappellani is a Senior Integration Engineer in the Portland Technology Development Department. She joined Intel in 2001 after receiving a Ph.D. degree from the University of Newcastle (UK). She conducted all her Ph.D. work on Poly/metal gate for advanced RF CMOS and DRAM in Germany at Siemens AG research labs (Munich) and at Infineon AG development fab (Dresden). As a member of PTD group at Intel she has been responsible first for the introduction of NiSi in the 90nm and then of the Metal Gate integration in 45nm logic technology. Annalisa is currently working on the pathfinding for the 22nm logic technology node. Her email is annalisa.cappellani at intel.com.

**Chi-hing Choi** joined Intel in 1991 after completing a Ph.D. degree in Materials Science and Engineering at Northwestern University. He has worked on developing metal gate deposition technologies since 2003. His e-mail is Chi-hing.Choi at intel.com.

Gary Ding joined Intel in 1994 after completing his Ph.D. degree in Materials Science and Engineering at Cornell University. He has worked on metal interconnect, salicide, electroplating, and planarization projects. He is currently a planarization group leader in Portland Technology

Development responsible for front end planarization. His e-mail is gary.ding at intel.com.

Weimin Han joined Intel in 1991 after completing a Ph.D. degree in Physics at Oregon State University. He is a Diffusion Group Leader in Intel's Logic Technology Development organization and worked on diffusion process development since Intel's 0.8µm process technology. He is currently responsible for developing an advanced ALD/CVD batch deposition process for the 32/25nm CMOS node. His e-mail is Weimin.c.Han at intel.com.

**Subhash M. Joshi** joined Intel in 2000 after completing a Ph.D. degree in Materials Science at Duke University. He worked on integrating low-k dielectrics with flip-chip packaging and improving C4 bump reliability on Intel's 90nm technology, together with early development of the lead-free bump and redistribution layer modules. Since 2004, he has worked on front-end process integration, including development of shallow trench isolation, dual metal gate, and trench contact modules for Intel's 45nm technology. His e-mail is subhash.m.joshi at intel.com.

**Brian McIntyre** is an Etch Group Leader in Intel's Logic Technology Development organization. He joined Intel in 1994 and has worked on etch process development since Intel's 0.35μm process technology. He is currently responsible for developing patterning processes for the 22nm CMOS node. He received his Ph.D. degree from the University of California, Berkeley in 1994. His e-mail is brian.mcintyre at intel.com.

Matt Prince joined Intel in 1988 after graduating from Clarkson University. He has developed CMP processes, consumables, and equipment for Intel's 0.8µm to 45nm technology nodes. He has developed STI, ILD, W, Cu, and poly CMP processes for Intel's logic technologies.

**Pushkar Ranade** joined Intel in 2003 after graduating with a Ph.D. degree from the University of California, Berkeley. At Berkeley, his research was in the area of sub-70nm CMOS transistor design and involved the integration of novel gate stack materials and ultra-shallow junctions. Since joining Intel, he has worked on transistor integration and development of Intel's 65nm and 45nm technology nodes, and he is currently working on the 22nm technology node. He has authored or co-authored over 35 technical publications and holds 4 U.S. patents. His e-mail is pushkar.ranade at intel.com.

**Justin Sandford** joined Intel in 1994 after graduating from Arizona State University. He has worked on the front-end process integration of Intel's silicon process technology beginning at the 0.25μm node. Justin is currently working on the development of Intel's 22nm Logic Technology. His e-mail address is Justin.S.Sandford at intel.com.

Christopher Thomas joined Intel in 1997 after completing his Ph.D. degree in Physics from Northwestern University. He supported thin film technology development for the 0.18µm, 90nm, and 45nm nodes. He holds nine US patents. He is currently the High-k Deposition Group Leader, and for the past five years has been responsible for developing the gate oxide deposition process. His e-mail is christopher.d.thomas at intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Intel's trademarks may be used publicly with permission only from Intel. Fair use of Intel's trademarks in advertising and promotion of Intel products requires proper acknowledgement.

\*Other names and brands may be claimed as the property of others.

Microsoft, Windows, and the Windows logo are trademarks, or registered trademarks of Microsoft Corporation in the United States and/or other countries.

Bluetooth is a trademark owned by its proprietor and used by Intel Corporation under license.

Intel Corporation uses the Palm OS® Ready mark under license from Palm, Inc.

LEED - Leadership in Energy & Environmental Design (LEED®)

Copyright © 2008 Intel Corporation. All rights reserved.

This publication was downloaded from http://www.intel.com.

Additional legal notices at:

http://www.intel.com/sites/corporate/tradmarx.htm.

## Process and Electrical Results for the On-die Interconnect Stack for Intel's 45nm Process Generation

Peter Moon, Technology Manufacturing Group, Intel Corporation Vinay Chikarmane, Technology Manufacturing Group, Intel Corporation Kevin Fischer, Technology Manufacturing Group, Intel Corporation Rohit Grover, Technology Manufacturing Group, Intel Corporation Tarek A. Ibrahim, Technology Manufacturing Group, Intel Corporation Doug Ingerly, Technology Manufacturing Group, Intel Corporation Kevin J. Lee, Technology Manufacturing Group, Intel Corporation Chris Litteken, Technology Manufacturing Group, Intel Corporation Tony Mule, Technology Manufacturing Group, Intel Corporation Sarah Williams, Technology Manufacturing Group, Intel Corporation

Index words: 45nm, process technology, copper

#### **ABSTRACT**

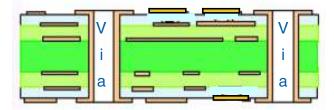

This paper introduces the issues associated with on-die interconnects and describes how they are addressed on Intel's 45nm high-performance, logic process technology. The 45nm process generation uses carbon-doped oxide low-k dielectric and aggressive scaling of the silicon-carbide-nitride (SiCN) etchstop film to achieve a 10% average capacitance reduction at the MT1-MT8 layers, relative to the previous 65nm generation. A thick MT9 layer is added to provide a low resistance path for power routing. MT1-MT8 interconnect RC performance benchmarking and the process and reliability concerns associated with the MT9 redistribution layer are discussed. The combined MT1-MT9 interconnect stack provides high performance and high reliability and enables a completely lead-free (Pb-free) product.

#### INTRODUCTION

The density and performance of the on-die interconnect stack must continue to improve with each process generation to support increasingly powerful and compact microprocessors. At the same time, process costs must be strictly controlled. The on-die interconnect stack for Intel's 45nm process generation extends the dual damascene processing scheme used on previous generations and adds several innovations for increased density and performance [1].

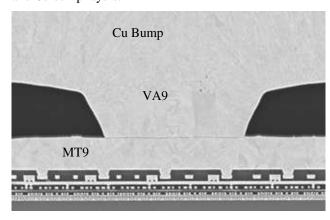

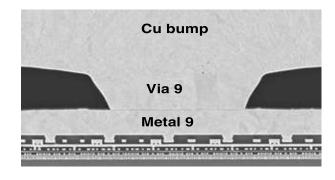

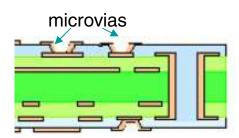

A new, low-cost and low-resistance Metal-9 layer (MT9) is formed on top of the conventional interconnect stack to support improved power distribution between the C4 bumps and the other metal layers. This MT9 redistribution layer is formed by copper plate-up between sacrificial photoresist lines in a similar fashion to C4 bump formation. The MT9 layer is covered by a silicon nitride passivation layer, a polymer dielectric, and finally, the copper C4 bumps.

The Metal-1 to Metal-3 (MT1–MT3) layers use 193nm dry lithography with 160nm pitch to achieve high-density wiring with lower process cost than immersion lithography. These metal layers also achieve low capacitance due to aggressive scaling of the SiCN etchstop film along with use of carbon doped oxide (CDO) low-k dielectric. The median RC performance for the MT2 layer is 0.20fF/um capacitance and 3.3ohm/um resistance at 160um pitch, as measured on the high-volume manufacturing process with electromigration performance that is consistent with the requirements of high-performance microprocessors.

Overall, the on-die interconnect stack for the 45nm process generation delivers 2X higher area density, 10% lower average capacitance, improved power distribution, and a completely Pb-free product.

#### **Process Discussion**

The on-die MT1-MT7 interconnects are formed by dual damascene patterning with highly manufacturable low-k

CDO dielectrics. The lower layer metal pitches are 160nm, while upper layer metal pitches increase progressively to optimize density and performance as shown in Table 1 and Figure 1. MT8 is also formed by dual damascene patterning, but it uses PECVD SiO<sub>2</sub> as the dielectric film, and the MT8 layer is covered with a thick PECVD silicon nitride film.

Table 1: Layer material, pitch, thickness and aspect ratio

| Layer   | Dielectric<br>Material | Pitch<br>(nm) | Thick (nm) | Aspect<br>Ratio |

|---------|------------------------|---------------|------------|-----------------|

| Metal 1 | Low k                  | 160           | 144        | 1.8             |

| Metal 2 | Low k                  | 160           | 144        | 1.8             |

| Metal 3 | Low k                  | 160           | 144        | 1.8             |

| Metal 4 | Low k                  | 240           | 216        | 1.8             |

| Metal 5 | Low k                  | 280           | 252        | 1.8             |

| Metal 6 | Low k                  | 360           | 324        | 1.8             |

| Metal 7 | Low k                  | 560           | 504        | 1.8             |

| Metal 8 | SiO <sub>2</sub>       | 810           | 720        | 1.8             |

| Metal 9 | Polymer                | 30.5μm        | 7µm        | 0.4             |

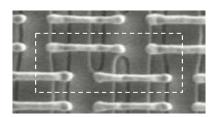

Figure 1: SEM image of interconnect stack up to MT8

The MT9 redistribution layer is formed using a plate-up process. It begins by depositing a blanket Barrier/Seed (Ti/Cu) layer over the entire wafer. The MT9 line/space pattern is created using a thick photoresist followed by standard Cu electroplating to form the MT9 lines. The resist is then stripped and the Barrier/Seed between MT9 lines is removed. The finished MT9 wires are capped with a 400nm PECVD silicon nitride film for improved isolation.

The MT9 layer is covered with 16um of a spin-on polymer dielectric that is patterned by standard lithography techniques and cured in a furnace. From this point onwards the processing is very similar to that used to form the Cu bumps utilized in the 65nm process [2, 3].

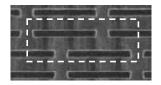

Figure 2 shows a cross-section view of the MT9, VA9, and Cu bump layers.

Figure 2: SEM image detailing the MT9 and VA9 layers

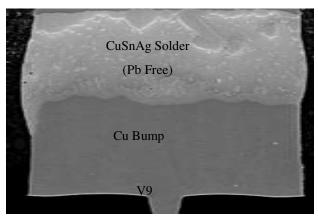

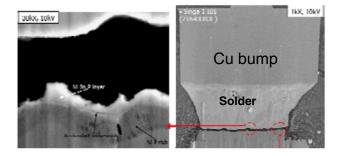

After Cu bump formation, the wafers are tested, diced into individual die, and assembled into packaged units. The electrical connection between die and package uses a Pbfree solder as shown in Figure 3. Details of this process are described elsewhere [4].

Figure 3: SEM image showing a Bump post chip attach

#### RESULTS

The 45nm process delivers reduced capacitance relative to the previous 65nm process generation through a combination of techniques. The newer process replaces  $SiO_2$  dielectric with low-k CDO dielectrics at MT1, MT6, and MT7 for a >20% capacitance improvement at those layers as shown in Figure 4. Also, at the lower metal layers, the SiCN etch stop layer is aggressively scaled for an additional 5% capacitance reduction. Overall, the newer process achieves a 10% average capacitance improvement while re-using the robust CDO dielectric film and capital equipment from the previous process generation.

# 65nm process to Intel 45nm process 120% 100% 80% 60% 40% 20%

Capacitance scaling (fixed length) from Intel

Figure 4: Capacitance comparison between the 45nm process and 65nm process

MT1 MT2 MT3 MT4 MT5 MT6 MT7 MT8

Metal layer

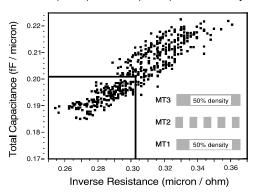

It is important to accurately benchmark interconnect RC performance. Interconnect capacitance and resistance are measured for minimum pitch lines with 50% dense, minimum-pitch metal patterns directly above and below the measured feature. Total capacitance is the sum of line-line capacitance and layer-layer capacitance as indicated in Figure 5.

$C_{TOTAL} = 2 \times C_{LINE-LINE} + 2 \times C_{LAYER-LAYER}$

Figure 5: Components of capacitance measurement

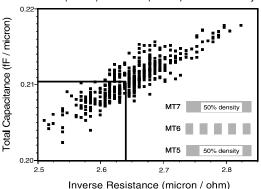

Measured capacitance and resistance values for the 45nm process are shown in Figures 6 and 7 at the MT2 and MT6 layers, respectively. The MT2 layer delivers median values of 0.20 fF/um total capacitance and 3.3 ohm/um resistance at 160nm pitch. Resistance at lower metal layers includes a 10% resistance penalty to enable high current density without electromigration failures for high-performance logic products. The MT6 process delivers median values of 0.21 fF/um total capacitance and 0.38 ohm/um resistance at 360nm pitch.

MT2 R and C values measured at 160nm pitch with MT1 (below) and MT3 (above) at 50% density

Figure 6: R and C values for MT2 at 160nm pitch

MT6 R and C values measured at 360nm pitch with MT5 (below) and MT7 (above) at 50% density

Figure 7: R and C values for MT6 at 360nm pitch

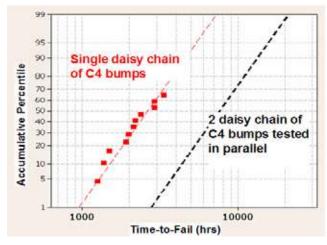

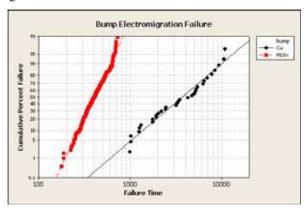

The thick MT9 lines allow for neighboring bumps to be connected by a low-resistance path that enables current redistribution upon initial electromigration (EM) damage at individual bump/solder joints. The large cross-section area of MT9 and its excellent electromigration resistance achieves redundancy of neighboring bumps without concern for electromigration in MT9 itself. Figure 8 shows an electromigration Time-to-Failure comparison between a single daisy chain of C4 bumps vs. two daisy chains of bumps tested in parallel, connected through MT9 with twice the amount of current; and both tested under accelerated conditions of higher temperature and higher current. As the plot indicates, MT9 redundant layout increases bump EM performance by at least 1.65X. Due to long testing periods, the stress ended without any redundant links failing. These data show that MT9 delivered the desired bump EM improvement.

Figure 8: EM fail rate for redundant Cu bumps

Figure 9 shows a Confocal Scanning Acoustic Microscope (CSAM) image of a product unit (full stack) taken after packaging with Sn-Ag-Cu solder. Areas of cracking or interface delamination will show up as white or black spots apart form the contrast variation of the underlying pattern. As seen in Figure 9, no contrast areas are observed, which shows that the unit is free of cracking or interface delamination. These results have been demonstrated on thousands of units and across the expected process variations.

Figure 9: CSAM image of a production unit post packaging

It is critical that this thick MT9 layer also be reliable in addition to achieving electrical benefits. Figure 10 shows a CSAM of the MT9/VA9 layer after 25 hours of HAST stress; the image is clean of any delamination or cracking.

Figure 10: CSAM image of a production unit after 25 hours of HAST

#### DISCUSSION

Interconnect design is a compromise between density, RC performance, and cost: narrow wires deliver high-density but relatively poor RC performance, while wide wires have better RC performance but reduced density. Extra metal layers can improve either density or RC performance, but they also add process cost. High-performance logic products are designed with fine pitch wires at the lower layers where density is critical, and with wide/thick wires at the upper layers where RC performance is critical.

Intel's 45nm interconnect process uses a unique solution to the problem of interaction between density, RC performance, and cost, by adding a low-cost, very-low-resistance layer to improve the power distribution network at the upper metal layers. The reduced requirement for power distribution in the MT6, MT7, and MT8 layers and the move to low-k dielectric at MT6 and MT7 enables these layers to allocate more chip area to signal wires, resulting in improved RC performance, without adding process cost.

The lower metal layers use 160nm pitch with dry 193nm lithography to achieve high density with acceptable RC performance and relatively low process cost. The tungsten-filled local interconnect layer beneath MT1 helps to achieve high density. The re-use of robust dielectric materials with optimized thickness improves RC performance at the lower metal layers while maintaining high reliability and controlling process cost.

The new process exceeds the reliability requirements for high-volume manufacturing. The 45nm process with its seven layers of low-k dielectrics has significant intrinsic margins to film cracking and/or interface delamination even with the increased stress of a Pb-free process. The MT9 redistribution layer has excellent EM performance

on its own and enables redundancy between Cu bumps, which effectively improves their EM resistance as well. The complete interconnect stack is capable of withstanding temperature shock, HAST, and PreCon stresses, all of which exceed end-of-life goals [5, 6, 7].

#### CONCLUSION

The on-die interconnect stack for Intel's 45nm process generation delivers a 2X higher area density, a 10% lower average capacitance, and improved power distribution relative to the previous process generation. The new process also enables Intel's first completely Pb-free microprocessor products.

#### **ACKNOWLEDGMENTS**

We gratefully acknowledge the Portland Technology Development Group and the TD Quality and Reliability Engineering organizations for their contributions to this work.

#### REFERENCES

- [1] K. Mistry et al., "A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning and 100% Pb-free Packaging." *IEDM Technology Digest*, 2007, pps. 247–250.

- [2] P. Bai et al., "A 65nm Logic Technology Featuring 35nm Gate Lengths, Enhanced Channel Strain, 8 Cu Interconnect Layers, Low-K ILD, and .57um SRAM Cell." *IEDM Technology Digest*, 2004, pps. 657–666.

- [3] A. Yeoh et al., "Copper Die Bumps (first level Interconnect) and Low-K Dielectric in 65nm High Volume Manufacturing." In *ECTC Proceedings*, 2006.

- [4] M. Renavikar et al., "Materials Technology for Environmentally Green Micro-electronic Packaging." *Intel Technology Journal, Volume 12, Issue 1*, 2008.

- [5] "Temperature Cycling." *JESD22-A104-C*, May 2005.

- [6] "Accelerated Moisture Resistance—unbiased HAST." *JESD22-A118*, December 2000.

- [7] "Highly Accelerated Temperature and Humidity Stress (HAST)." *JESD22-A110-B*, February 1999.

#### **AUTHORS' BIOGRAPHIES**

**Peter Moon** joined Intel in 1988 after completing his Ph.D. degree in Materials Science at MIT. He has worked on process integration for Intel's 0.8um, 0.35um, 130nm,

and 45nm silicon process technologies including Intel's first use of shallow trench isolation (0.35um), copper interconnects (130nm), and Pb-free microprocessor products (45nm). Peter is currently leading the development of Intel's interconnect process for the 22nm process generation. His e-mail is peter.moon at intel.com.

Vinay Chikarmane completed his B.Tech. degree in Chemical Engineering from IIT, Bombay and his Ph.D. degree in Materials Science from the University of Texas at Austin. He is currently a Principal Engineer in PTD, leads Copper Interconnect Development at the 32nm node, and is the Engineering Group Leader in the Thin Films area. He previously led Copper Interconnect Development at the 45nm, 65nm, and 90nm nodes, and he worked on engineering development of Intel's first Copper Technology (130nm) and the last two Aluminum Interconnect Technology nodes. His e-mail is vinay.b.chikarmane at intel.com.

**Kevin Fischer** is a Senior Individual Contributor in PTD. He received his Ph.D. degree in Electrical Engineering from the University of Wisconsin at Madison. He has worked at Intel for seven years in process integration. Beginning on the 90nm process technology, he has worked on four different generations of back-end technology and is currently working on back-end process development for Intel's 22nm technology. His e-mail is kevin.j.fischer at intel.com.

Rohit Grover completed his B. Tech. degree in Engineering Physics from IIT Bombay in 1997, and he received M.S. and Ph.D. degrees in Electrical and Computer Engineering from the University of Maryland, College Park in 1999 and 2004, respectively. Since 2003, he has been working at Intel as a Senior Process Integration Engineer in the Far Back-end Group of Portland Technology Development. Rohit's team works on enabling lead-free, first-layer interconnects, managing packaging-induced low-k ILD stresses, and first-layer interconnect materials that are compatible with next-generation microprocessor architectures. His e-mail is rohit.grover at intel.com.

**Doug Ingerly** joined Intel in 2000. He holds a Ph.D. degree in Material Science and Engineering from the University of Wisconsin, Madison and a B.S. degree in Ceramic Engineering from the University of Missouri, Rolla. He has worked on process integration for Intel's 130nm and 65nm interconnect processes and led the far backend integration for the 45nm process. Currently, he is working on Intel's 22nm interconnect process. His e-mail is doug.b.ingerly at intel.com.

**Tarek A. Ibrahim** joined Intel Corporation in 2004 after completing his Ph.D. degree in Electrical Engineering at the University of Maryland, College Park. He is a member

of the Portland Technology Development integration group and worked on the interconnect process integration for the 45nm node. He is currently leading the focus team responsible for the interconnect patterning process of the 22nm process generation. His e-mail is tarek.a.ibrahim at intel.com.

Kevin J. Lee is a Principal Engineer in Intel's Portland Technology Development Group, specializing in far backend silicon processing. He was the technical lead for the thick MT9 redistribution layer process development. Prior to that he was Intel's Pb-free Bump Program Director, conducted Intel's initial copper damascene electroplating research and PbSn bump electroplating module development, and developed the buffer coat processes for Intel's 0.8um, 0.6um, and 0.35um technologies. He earned a B.A. degree from Hamline University in 1986 and a Ph.D. degree from the University of Illinois at Urbana-Champaign in 1991, both in Chemistry. His e-mail is kevin.j.lee at intel.com.

Chris Litteken joined Intel's Logic Technology Development organization in 2004 after completing his Ph.D. degree in Material Science from Stanford University. His research interests include the development of fracture mechanics methodologies to improve cracking/adhesion within thin-film structures. As a Senior Quality and Reliability Engineer, he develops predictive models for the thermo-mechanical reliability of 22nm, 45nm, and 65nm microprocessors and chipsets. His e-mail is christopher.s.litteken at intel.com.

**Tony Mule** is a Senior Process Integration Engineer in the PTD BE Integration group. He received his M.S./Ph.D. degrees in Electrical Engineering from the Georgia Institute of Technology in 2004. Upon joining Intel, he has focused primarily on low-k dielectric patterning development for both the 45nm and 22nm technology generations. His e-mail is tony.v.mule at intel.com.

**Sarah Williams** is an etch group leader in Intel's Logic Technology Development organization. She joined Intel in 2000 after completing her Ph.D. in Physical Chemistry at the University of Wisconsin-Madison. She is currently working on the development of interconnect processes for the 32nm logic technology. Her e-mail is Sarah.A.Williams at intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, IPLink, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside,

skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Intel's trademarks may be used publicly with permission only from Intel. Fair use of Intel's trademarks in advertising and promotion of Intel products requires proper acknowledgement.

\*Other names and brands may be claimed as the property of others.

Microsoft, Windows, and the Windows logo are trademarks, or registered trademarks of Microsoft Corporation in the United States and/or other countries.

Bluetooth is a trademark owned by its proprietor and used by Intel Corporation under license.

Intel Corporation uses the Palm OS® Ready mark under license from Palm. Inc.

LEED - Leadership in Energy & Environmental Design (LEED®)

Copyright © 2008 Intel Corporation. All rights reserved.

This publication was downloaded from http://www.intel.com.

Additional legal notices at: http://www.intel.com/sites/corporate/tradmarx.htm.

# Managing Process Variation in Intel's 45nm CMOS Technology

Kelin Kuhn, Technology and Manufacturing Group, Intel Corporation

Chris Kenyon, Technology and Manufacturing Group, Intel Corporation

Avner Kornfeld, Technology and Manufacturing Group, Intel Corporation

Mark Liu, Technology and Manufacturing Group, Intel Corporation

Atul Maheshwari, Technology and Manufacturing Group, Intel Corporation

Wei-kai Shih, Technology and Manufacturing Group, Intel Corporation

Sam Sivakumar, Technology and Manufacturing Group, Intel Corporation

Greg Taylor, Technology and Manufacturing Group, Intel Corporation

Peter VanDerVoorn, Technology and Manufacturing Group, Intel Corporation

Keith Zawadzki, Technology and Manufacturing Group, Intel Corporation

Index words: 45nm, process variation, DFM

#### **ABSTRACT**

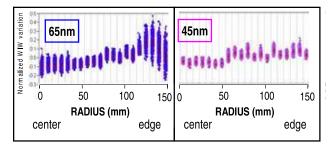

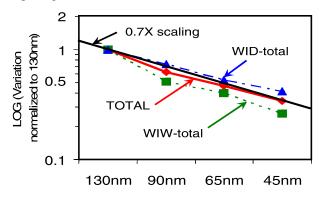

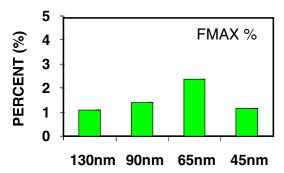

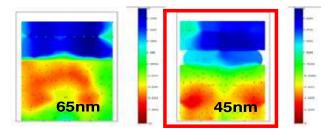

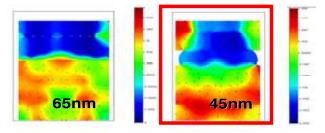

The key message of this paper is that process variation is not an insurmountable barrier to Moore's Law, but is simply another challenge to be overcome. This message is illustrated with data from the 45nm process generation where process variation is shown to be at least equivalent to (and in many cases better than) process variation in the 65nm- and 90nm-process generations.

We begin this paper with an introduction and historical overview of process variation. Although there has been a trend in recent years to convey process variation as a new challenge associated with advanced CMOS technologies, process variation has been a continuing theme throughout the history of semiconductor process engineering.

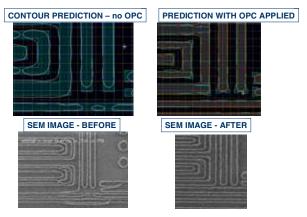

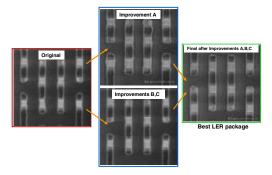

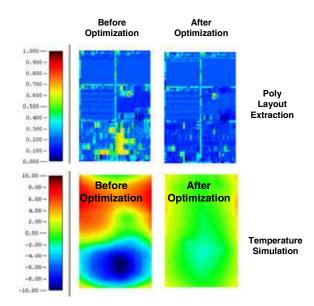

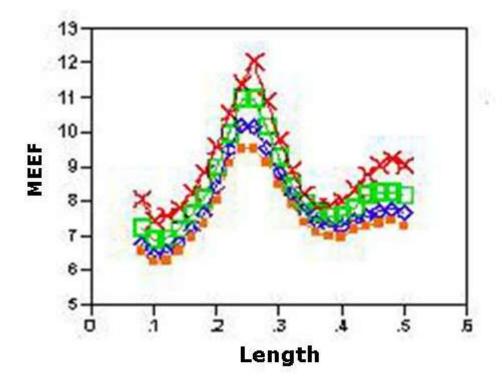

We continue with a review of critical sources of variation specific to the 45nm generation, including highly random effects (random dopant fluctuation, line-edge and linewidth roughness), variation associated with the gate dielectric (oxide thickness, fixed charge, defects and traps), patterning proximity effects (classical, and those based on optical proximity correction (OPC)), variation associated with polish (shallow-trench isolation, gate, and interconnect), variation associated with strain (wafer-level biaxial, high-stress capping layers, and embedded silicongermanium (SiGe)), and variation associated with implants and anneals (implant tool-based, implant profile, rapid-thermal anneal, and implant variation associated with poly-grain boundaries).

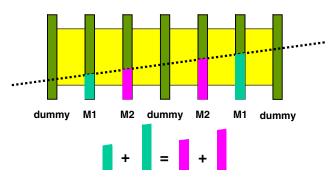

We then explore the variety of process, design, and layout techniques used in the 45nm generation to mitigate the impact of variation. Pure process mitigation techniques include targeting key transistor properties to reduce random dopant fluctuation, reducing traps at the high-k metal-gate (HiK+MG) interface to reduce random charge variation, improving patterning techniques to reduce lineedge roughness and endcap variation, and improving polishing technologies to reduce systematic cross-wafer variation. Combination design-process techniques include optimizing topology, using OPC to reduce random and systematic variation, and adding dummy features to reduce systematic variation. Pure design techniques include chopping techniques to compensate for random variation and common-centroid layout techniques to compensate for systematic variation.

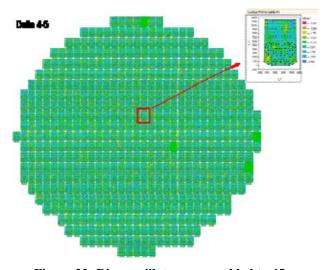

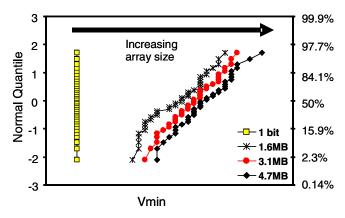

We move on to illustrate the success of these mitigation techniques by reviewing detailed data characterizing variation in the 45nm generation. Three different types of measurements are presented to illustrate various variation mechanisms. The first is in-fab measurement of variation, used to characterize gate dimensional variation for the 45nm versus 65nm and 90nm generations. The second is low-frequency electrical measurement of matched transistor pairs, used to extract random variation for 45nm versus 65nm transistors. The third is measurements of product ring oscillators, used to determine both systematic and random within-wafer and within-die variation for 45nm versus 65nm products.

Finally, we reinforce the key message that variation does not pose an insurmountable barrier to Moore's law, but is simply another challenge to be overcome.

# INTRODUCTION AND HISTORICAL OVERVIEW

Moore's-Law-driven technology scaling has improved VLSI performance by five orders of magnitude in the last four decades. As advanced technologies continue the pursuit of Moore's Law, a variety of challenges will need to be overcome. One of these challenges is management of process variation [1, 2].

Although there has been a trend in the CMOS literature in recent years to convey process variation as a new challenge associated with advanced CMOS technologies, that viewpoint does not effectively capture the history of process variation. Process variation has always been a critical aspect of semiconductor fabrication.

The first discussion of random variation in semiconductor devices was Shockley's 1961 analysis of random fluctuations in junction breakdown [3]. Shockley's concepts of random variation were extended to MOS devices by Keyes [4] in 1975 when he modeled the effect of random fluctuations in the number of impurity atoms in the depletion layer of a field-effect transistor (FET). Systematic variation in MOS devices was first addressed formally in 1974 by Schemmert and Zimmer [5] when they computed the sensitivity of ion-implanted MOS threshold voltages as a function of the implantation energy and the oxide thickness. A more extensive analysis of threshold voltage sensitivity using a closed-forum numerical simulation was presented by Yokoyama et al. in 1980 [6] with a Monte Carlo approach developed by Alvarez in the same year [7]. Interconnect variation has also received significant attention over the years, with Lin et al. presenting a detailed treatment in 1998 [8] that was expanded by many authors in the early 2000s [37, 40–43].

While the continued decrease in the ratio of feature sizes to fundamental dimensions (such as atomic dimensions and light wavelengths) means that management of variation will play a significant role in future technology scaling, the evidence shows that process variation has been a continuing theme throughout semiconductor history.

# CRITICAL SOURCES OF VARIATION IN THE 45NM GENERATION

45nm technology is subject to a number of variation effects that are well documented in the literature [9–63]. Examples include highly random effects (random dopant fluctuation (RDF) [9–17], line-edge and line-width roughness, line-edge and line-width roughness (LER) and

(LWR), respectively [18–21]), variations in the gate dielectric (oxide thickness variations [22–26], fixed charge [27], and defects and traps [28–34]), patterning proximity effects (classical, and those associated with OPC [35]), variation associated with polish (shallow trench isolation (STI) [36, 40], gate [37–38], and interconnect [39,42-44]), variation associated with strain (wafer-level biaxial 46–49, 57], high-stress capping layers [50–52], and embedded silicon-germanium (SiGe) [53–56]), and variation associated with implants and anneals (tool-based [58], pocket implants [59–60], rapid-thermal anneal RTA [61] and variation associated with poly grains [62–63]).

#### **Random Dopant Fluctuation (RDF)**

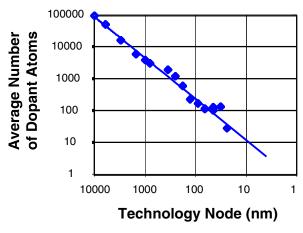

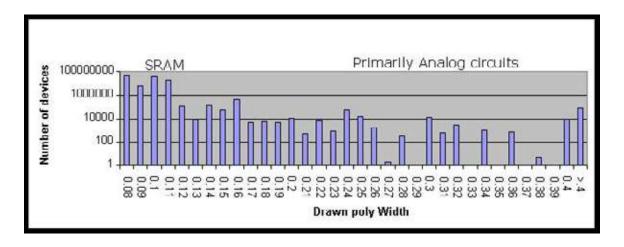

MOS threshold voltage variation due to random fluctuations in the number and location of dopant atoms is an increasingly significant effect in sub-micron CMOS technologies (see Figure 1 and [9–17]). As the number of dopant atoms in the channel decreases with scaled dimensions, the impact of the variation associated with the atoms increases. Figure 2 illustrates the decreasing average number of dopant atoms in the channel as a function of the technology node. Note the change from the 1µm technology node (with many thousands of dopant atoms in the channel) to the 32nm technology node (with less than 100 atoms in the channel).

Figure 1: Random dopant fluctuations (RDF) are an important effect in sub-micron CMOS technologies

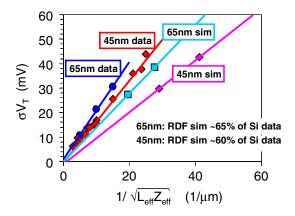

RDF is assumed to be the major contributor to device mismatch of identical adjacent devices and is frequently represented by Stolk's formulation (Equation 1)

$$\sigma V_{Tran} = \left(\frac{\sqrt[4]{4q^3}\varepsilon_{si}\phi_B}{2}\right) \cdot \frac{T_{ox}}{\varepsilon_{ox}} \cdot \left(\frac{\sqrt[4]{N}}{\sqrt{Weff \cdot Leff}}\right) = \frac{1}{\sqrt{2}} \left(\frac{c_2}{\sqrt{Weff \cdot Leff}}\right) \quad (1)$$

illustrating that matching improves with decreases in channel doping (N) and gate oxide thickness (Tox), and it degrades when device area decreases [12].

Figure 2: Average number of dopant atoms in the channel as a function of technology node

While Equation (1) assumes that the only contribution to random variation between two adjacent matched devices is random dopant fluctuation, in practice it is known that additional effects also contribute to the measured variation [14]. Identifying the magnitude and root cause for these additional effects is important in facilitating the development of mitigation techniques. Many groups have attempted to estimate the size of these additional effects by comparing measured data to simulation [15–16]. As an example, we reported the results of such a study [17] where we compared simulation results to 65nm silicon data and showed that simulated RDF is  $\sim$ 65% of the total NMOS  $\sigma V_T$ . Similar results were obtained when we compared 45nm simulation results to data where the simulated RDF is  $\sim$ 60% of the total PMOS  $\sigma V_T$ .

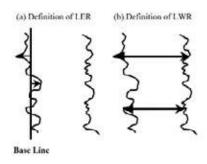

# Line-edge and Line-width Roughness (LER and LWR)

While random fluctuations in patterned lines occur in both the front-end and the back-end of the process, the primary concern with LER/LWR is variations in poly-gate patterning (see Figures 3 and 4). For poly-gate patterning, LER and LWR are associated with increases in the subthreshold current [18, 19] as well as degradation in the threshold voltage ( $V_T$ ) characteristics [20, 21].

Figure 3: LER/LWR definitions [19]

Diaz et al. [18] quantified the impact of LER on transistor performance by comparing devices from a 130nm technology (80nm nominal gate lengths and 17Å oxide) that were patterned with a 193nm binary solution (9.3nm LER) and 248nm alternating phase shift mask (APSM) solution (6.5nm LER). LER reduction from 9.3nm to 6.5nm translated into measured improvement of 1.5X for a nominal device. For the subnominal 70nm device, a 2X improvement was observed.

In a similar experiment, Kim et al. [19] evaluated the impact of LER and LWR on device performance using a set of 80nm node single nMOS transistors from lowdevices power **SRAM** fabricated with various combinations of gate length, gate width, LWR, and LER. The amount of LER and LWR was controlled by applying different resist materials, defocus, and overetch time. Their experimental data showed that LER effects began when the gate length was less than 85nm. They observed a four-order of magnitude increase in the standard deviation of the subthreshold current for the smallest gate lengths in the study.

Fukutome et al. [20] were able to use scanning tunneling microscopy (STM) to directly assess the impact of LER on the carrier profiles of source-drain extensions in submicron MOSFETs. They observed that the roughness of extension edges induced by gate LER depended on the implanted dose, halos (pockets), and various coimplantations. They showed an improvement of 4nm in  $V_T$  roll-off with a decrease in the average LER, and they confirmed that co-implants induced a degradation of 5mV in the standard deviation of  $V_T$ .

Asenov et al. [21] studied the combined effect of LER and random discrete dopants on current fluctuations. They were able to demonstrate that the two sources of fluctuations act in a statistically independent manner when taken into account simultaneously in the simulations. They also showed that the LER-induced current fluctuations have a much stronger channel length dependence and, as devices are scaled to shorter dimensions, LER is expected to supplant RDFs as the dominant variation source.

Figure 4: LER/LWR of poly gates has been modeled by a number of researchers [18–21]

#### **Variations in the Gate Dielectric**

The high-*k* metal-gate (HiK+MG) devices used in the 45nm generation are subject to a number of variation effects in the gate dielectric [22–34]. These include variations in oxide thickness, fixed charge, and interface traps. These physical changes in the dielectric result in parametric variations in drive current, gate tunneling current, or threshold voltage.

#### **Oxide Thickness**