Volume 09

Issue 01 P

Published, February 17, 2005

ISSN 1535-864X

DOI: 10.1535/itj.0901

# Intel® Technology Journal

# Second-Generation Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology

The second-generation platform built on Intel<sup>®</sup> Centrino<sup>™</sup> mobile technology continues to drive new capabilities. This issue of Intel Technology Journal (Volume 9, Issue 1) describes new features, interfaces, and performance that enable new usages for mobile computing.

# Inside you'll find the following articles:

Second-Generation Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology Platform Low-Power Audio and Storage Input/Output Technologies for the Second-Generation Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology Platform

Intel<sup>®</sup> 915GMS Chipset: In Mobile Platforms, Smaller is Better Performance and Power Consumption for Mobile Platform Components Under Common Usage Models

The Emergence of PCI Express\* in the Next Generation of Mobile Platforms

Interface Material Selection and a Thermal Management Technique in Second-Generation Platforms Built on Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology

High-Performance Graphics and TV Output Comes to the Second-Generation Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology Platform Next-Generation PC Platform Built on Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology New Usage Models

More information, including current and past issues of Intel Technology Journal, can be found at: http://developer.intel.com/technology/itj/index.htm Issue 01 Publi

Published, February 17, 2005

ISSN 1535-864X

DOI: 10.1535/itj.0901

# Intel® Technology Journal

Second-Generation Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology

# **Articles**

| Preface                                                                                                                                                            | iii |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Technical Reviewers                                                                                                                                                | V   |

| Second-Generation Intel® Centrino <sup>™</sup> Mobile Technology Platform                                                                                          | 1   |

| Intel® 915GMS Chipset: In Mobile Platforms, Smaller is Better                                                                                                      | 11  |

| The Emergence of PCI Express* in the Next Generation of Mobile Platforms                                                                                           | 21  |

| High-Performance Graphics and TV Output Comes to the Second-Generation Intel <sup>®</sup> Centrino <sup>™</sup> Mobile Technology Platform                         | 35  |

| Low-Power Audio and Storage Input/Output Technologies for the Second-Generation Intel <sup>®</sup> Centrino <sup>™</sup> Mobile Technology Platform                | 49  |

| Performance and Power Consumption for Mobile Platform Components<br>Under Common Usage Models                                                                      | 61  |

| Interface Material Selection and a Thermal Management Technique in Second-Generation Platforms Built on Intel <sup>®</sup> Centrino <sup>™</sup> Mobile Technology | 75  |

| Next-Generation PC Platform Built on Intel <sup>®</sup> Centrino <sup>™</sup> Mobile Technology<br>New Usage Models                                                | 87  |

#### THIS PAGE INTENTIONALLY LEFT BLANK

# Preface

# Second-Generation Intel<sup>®</sup> Centrino<sup>TM</sup> Mobile Technology by Lin Chao Publisher, *Intel Technology Journal*

As we enter the ninth year of publication of the Intel Technology Journal, we bring to our readers an updated web layout and easier navigation for a better reader experience. We continue to provide pdf files for each paper and a combined pdf for the entire issue. For the first time, we are using Digital Object identifiers (DOIs), content identifiers, for web documents similar to ISSN numbers for serial print publications. DOIs provide persistent tagging of online content, addressing actual content rather than location.

This issue of Intel Technology Journal (Volume 9, Issue 1) focuses on the second-generation platform built on Intel<sup>®</sup> Centrino<sup>™</sup> mobile technology. For many users, a laptop is their primary computer and a large part of their daily experience. This includes mobility usage models that fall into three main categories as defined by Intel: Mobile Digital Office, Mobile On-the-Go, and mobile entertainment.

Mobile Digital Office connects the IT enterprise to a wirelessly connected mobile notebook, an alwaysavailable virtual office with a primary focus of manageability and security. For example, malicious bufferoverflow attacks pose a significant security threat; the Pentium<sup>®</sup> M processor supports the XD (execute disable) bit that prevents buffer-overflow virus attacks. Another aspect of digital office is being able to connect wirelessly as easily as with a cell phone.

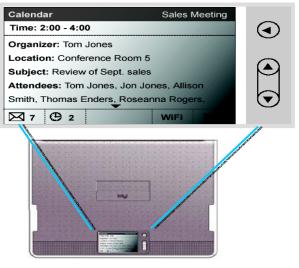

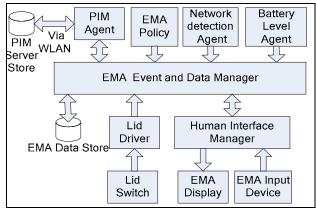

Mobile On-the-Go is mobility in or out of the office or home with emphasis on productivity, entertainment, and communication. Highly mobile users prefer flexible thin and light mobile systems with optimized battery life. Extended Mobile Access (EMA) technology offers a better thin and light experience with a small screen in the lid of the notebook similar to some cellular telephone models. Even with the notebook lid closed, the EMA display will show new e-mail messages, up-to-date calendars, or daily task lists. EMA technology reduces notebook power and consumption and saves battery life by turning off the main LCD.

Mobile Entertainment is optimized for entertainment–viewing movies, watching TV, sharing and editing photos, and playing games anywhere in the home. The Intel<sup>®</sup> 915 Express Chipset has a TV output feature, which is important for merging the personal computer and the television into a single platform.

The eight papers in this issue of Intel Technology Journal (Volume 9, Issue 1) examine the newest technologies for second-generation platforms built on Intel<sup>®</sup> Centrino<sup>TM</sup> mobile technology. The introductory paper provides an overview of the platform including the new Intel<sup>®</sup> Pentium<sup>®</sup> M processors, the Mobile Intel<sup>®</sup> 915 Express Chipset family (formerly codenamed Alviso), and Intel<sup>®</sup> PRO/Wireless 2915ABG or 2200BG wireless LAN components.

<sup>&</sup>lt;sup>TM</sup> Centrino is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>&</sup>lt;sup>®</sup> Pentium is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

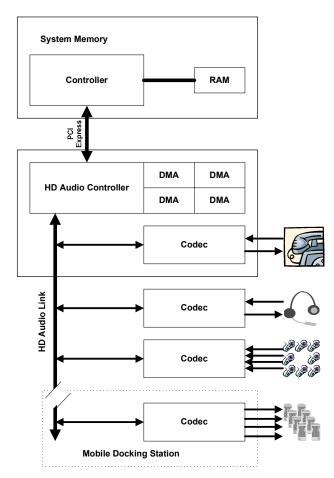

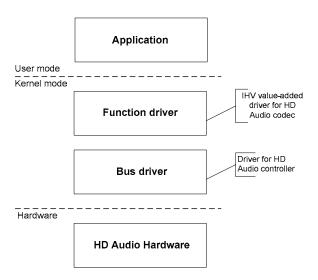

The next four papers in this Journal look at the new features and capabilities in the platform system. The second explores the electrical packaging, manufacturing, and motherboard routing issues associated with enabling thinner, lighter laptop designs. The third looks at PCI Express<sup>\*</sup>, a high-speed bit serial bus for I/O, graphics, and networking interconnections. The paper focuses on PCI Express architecture, power management, and mobile applications such as graphics, networking, and form factors including the ExpressCard<sup>\*</sup> module and future form factors such as the PCI Express Wireless Card and the PCI Express Mini Card. The fourth paper considers two major enhancements to Intel's graphics memory controller hubs in the Intel<sup>®</sup> 915 Express Chipset family. First, it discusses the microarchitecture of the 3D pipeline and the steps taken to optimize it for peak performance. Secondly, the TV output feature–which is important for merging PCs and TVs into a single platform–is described. The fifth paper focuses on two key Input/Output (I/O) technologies provided by the chipset: integrated audio and the interface to the storage device (hard drive). First it examines the architectural features of Intel<sup>®</sup> High Definition (HD) Audio. Next it discusses the architectural benefits of Serial AT Attachment (SATA) which will replace Parallel AT Attachment as the interface for hard drives.

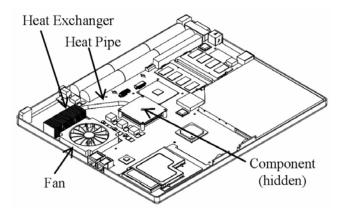

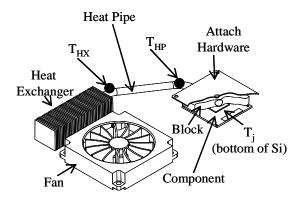

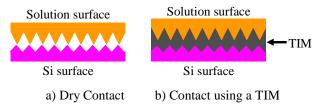

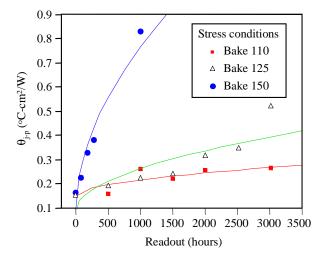

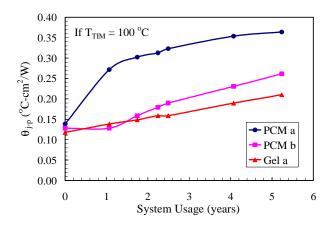

The next section is on power and thermal management. The sixth paper takes a look at performance and power consumption under common use models. In this paper we discuss some of these new features and the impact they have on platform performance and power as observed while executing industry benchmarks. The seventh examines thermal interface material (TIM) selection and improving the platform component performance/power efficiency and platform cooling capability when given finite heat budgets. By using better material for component packages, component cooling is improved.

The last paper focuses on future and current new usages for laptops. Here we explore new capabilities of the platform, and the interfaces and the wireless ecosystem used to enable new usage models: Extended Mobile Access (EMA), Voice over Internet Protocol (VoIP), Simplified Network Selection (SNS), and One Bill Roaming (OBR).

These papers reveal the exciting new mobile technologies and supporting standards already here or coming soon to our next laptop-technologies and standards that complement our multi-tasking, on-the-go computing lifestyle.

<sup>\*</sup> Other names and brands may be claimed as the property of others.

<sup>&</sup>lt;sup>®</sup> Intel is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

# **Technical Reviewers**

Ketan Bhat, Mobility Group Bala Cadambi, Digital Enterprise Group Chia-Pin Chiu, Technology and Manufacturing Group Les Cline, Mobility Group Peter Doyle, Mobility Group Terry Fletcher, Mobility Group Bill Huffman, Mobility Group Jon Inouye, Mobility Group Bob Jacobs, Mobility Group Mark Jamieson, Mobility Group Rob Kubick, Mobility Group Animesh Mishra, Mobility Group Ramin Neshati, Digital Enterprise Group Himanshu Pokharna, Mobility Group Ed Pole, Mobility Group Krishnan Rajamani, Mobility Group Vijay Rao, Mobility Group Jeff Reilly, Digital Enterprise Group Bill Sadler, Mobility Group Allen Sampson, Corporate Technology Group Eric Samson, Mobility Group Brad Saunders, Mobility Group Nirav Shah, Mobility Group Tom Shewchuk, Mobility Group Sanjaya Tayal, Digital Enterprise Group Jim Trethewey, Mobility Group Murali Veeramoney, Mobility Group Feng (Frank) Yang, Mobility Group

#### THIS PAGE INTENTIONALLY LEFT BLANK

# Second-Generation Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology Platform

Shreekant (Ticky) Thakkar, Mobility Group, Intel Corporation

Index words: CPU, GMCH, ICH, DDR2, WLAN, Audio, Power, Performance, Mobile, Notebook, Laptop, Centrino, Florence, Sonoma, Dothan, Alviso

# ABSTRACT

In this paper, we provide an overview of the secondgeneration Intel<sup>®</sup> Centrino<sup>™</sup> mobile technology platform. This represents a major revision of several new I/O and memory interfaces: Peripheral Component Interconnect (PCI) Express<sup>\*</sup> (PCIe), Serial Advanced Technology Attachment (SATA), Intel<sup>®</sup> High Definition Audio (Intel<sup>®</sup> HD Audio), and Double Data Rate (DDR2), which all enable a range of computing and media capabilities. The second-generation Pentium<sup>®</sup> M processor, the i915 Graphics and Memory Controller Hub (GMCH), the 82801FM I/O Controller Hub (ICH) and the Intel® PRO/Wireless 2915 Network Interface Controller (NIC) with higher performance, new capabilities and interfaces enable exciting new usages: Mobile Digital Office. Mobile On-the-Go, and Mobile Entertainment. Intel has demonstrated these usages through innovative concepts based on the Intel Centrino mobile technology platform and is actively enabling our Original Equipment Manufacturers (OEMs) and Original Design Manufacturers (ODMs) to bring these to market. Intel has driven power reductions on both the platform and its silicon while still delivering new features and capabilities.

#### INTRODUCTION

The mobile Personal Computer (PC) market segment has entered a period of rapid innovation driven by an accelerated demand for mobile devices and advances in mobile technologies that enable new mobile usage models. With the introduction of the first-generation Centrino mobile technology platform in 2003, the wireless LAN (WLAN) attached rate has climbed from under 20% to over 65% in 2004. According to industry analysts, IDC, more than 95% of all notebook PCs are expected to have integrated WLAN capability by 2006. This will complete the notebook transition from a portable to a wireless device.

Also, IDC expects that by the end of 2005, there will be over 150,000 WLAN hotspots around the world, nearly a 300% increase from 2003. Hotspot growth enables users to access critical data needed to make decisions, stay informed, and communicate while on-the-go. This growth in WLAN hotspots is expected to help drive a tenfold increase in the number of frequent WLAN hotspot users from less than 1 million in 2002 to over 10 million in 2004, and expanding to over 30 million by 2006.

Users view the notebook as the preferred mobile device to access wireless messaging content. Over the past few years computer mobility is part of many lifestyles: businesses, students, and home users have clearly recognized the flexibility and productivity benefits of having notebooks with wireless connectivity. Enterprise IT managers have been moving wireless deployments from prototype to production resources and enabling more notebooks with wireless access. According to industry analyst, Gartner (Dec. 2003), Mobile PC Notebook CAGR is 17% for 2002-2007.

Intel introduces the second-generation platform built on Intel Centrino mobile technology (previously codenamed Sonoma) in 2005 to continue driving growth in mobility through its vision. This platform represents a new building block with new interfaces, features, and performance that enable exciting new usages for second-generation mobile form factors. We briefly discuss technologies, features, and usage models in this paper.

<sup>&</sup>lt;sup>®</sup> Intel is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>&</sup>lt;sup>TM</sup> Centrino is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>\*</sup> Other brands and names are the property of their respective owners.

<sup>&</sup>lt;sup>®</sup> Pentium is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

#### Figure 1: The second-generation platform built on Intel Centrino mobile technology

Intel's mobility vision revolves around the four vectors of mobility that drive mobile PC capabilities: breakthrough mobile performance, integrated Wireless LAN (WLAN) capability, great battery life, and thinner, lighter designs. Newer capabilities will continue to emerge to build on the foundation of these vectors and provide future users with an advanced and compelling mobile computing experience for the wireless communications environment and anywhere, anytime computing.

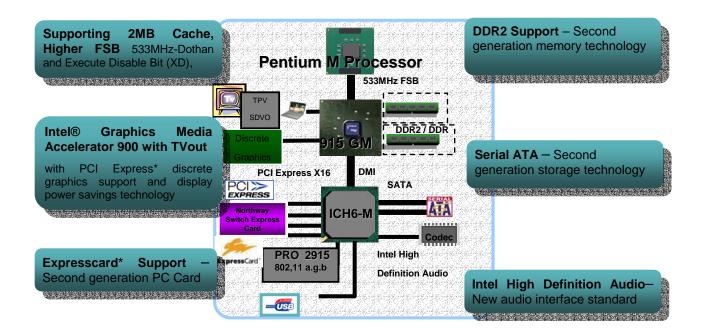

# **NEW PLATFORM**

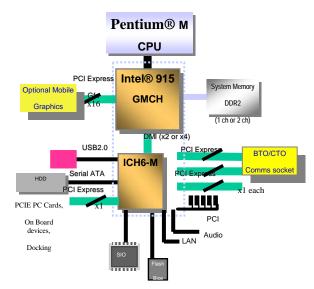

The second-generation platform built on Intel Centrino mobile technology (Figure 1) continues to excel on the four vectors of mobility. It comprises the Intel Pentium M processor, the i915 Graphics and Memory Controller Hub (GMCH), the IO Controller Hub (ICH) 6-M, and the Intel PRO/Wireless 2915 a/b/g Network Interface Controller (NIC). It introduces several new technologies that make it a new building block for this decade: mobile PCI Express (PCIe) and ExpressCard<sup>\*</sup> technology, Serial Advanced Technology Attachment (SATA) interface, PCIe External Graphics (PEG) interface, Intel High Definition (HD) Audio, and Double Data Rate (DDR2) memory. This new platform delivers both on CPU and graphics performance through scaling in core and bus frequencies as well as with microarchitecture enhancements including doubling processor cache size. The graphics performance improves by 2x over the previousgeneration platform. GMCH enables an enriched media experience through incorporation of Intel HD Audio and higher-speed interfaces.

Various platform power-savings techniques are used in all Intel silicon to reduce the power consumption of the platform while still providing the new features that demand higher power. Intel has also been working with the Industry to drive lower power displays, reducing power from over 4.5 W for 14" XGA LCD to under 3 W. The display vendors have shipped over 4M such units in the past year. Thus, battery life on the secondgeneration platform built on Intel Centrino mobile technology stays the same as the previous generation with integrated graphics, even though graphics performance has been doubled in the second-generation platform.

Wireless connectivity is enhanced with industry-standard WLAN security support (such as WPA2 and Cisco<sup>\*</sup> Compatible Extensions v.3), a new user interface for

<sup>\*</sup> Other brands and names are the property of their respective owners.

<sup>\*</sup> Other brands and names are the property of their respective owners.

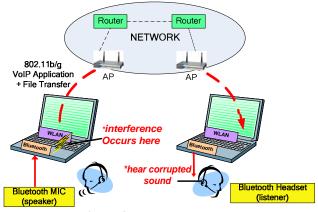

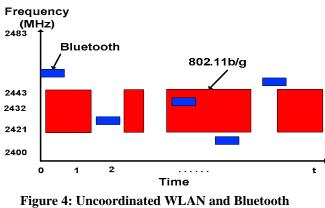

ease of connectivity, and support of a wireless coexistence solution that mitigates interference with wireless Bluetooth<sup>1</sup> human interface devices (HIDs).

Smaller mobile form factors (mini and subnotebooks) are now enabled through the introduction of new smaller chipset packages.

# **NEW INTERFACES**

PCIe introduces a scalable, point-to-point, powermanaged, serial interface. Full isochronous data transfer support is provided to guarantee minimum service latency and bandwidth requirements. This mode is advantageous for isochronous or time-sensitive applications, such as streaming video, where it is more important to display frames in a timely fashion than it is to display every frame. The Mobile PCIe Mini Card and ExpressCard interfaces enable a new level of interconnect performance on mobile platforms upgrading the I/O bandwidth from a half-duplex 133 MB/s to a full-duplex 250 MB/s. The PCIe Mini Card replaces the Mini PCI card, typically used on the mobile motherboard for build-to-order optional functions. The ExpressCard module is a new add-in card that replaces the CardBus PC Card. Both of these new cards provide not only PCIe bus connectivity but also USB 2.0 connectivity through the same connector. The PCIe Mini Card (30 mm x 51 mm) is about half the size of the Mini PCI (61 mm x 51 mm) card, thus two PCIe Mini Cards can fit in the space for one Mini PCI card. The ExpressCard module comes in two sizes: One is 40% the size of the PC Card for small mobile small factors, and the other is 80% the size of the PC Card for larger mobility notebooks. The ExpressCard technology will also appear on desktops.

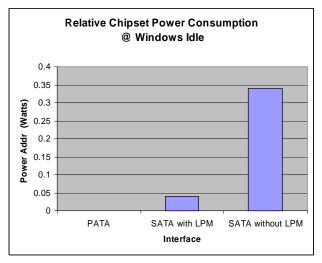

SATA is the evolution of the Parallel ATA (PATA) bus for connecting mass storage (hard and optical drives) on mobile platforms initially upgrading the transfer rate from 133 MB/s to 150 MB/s with ability to scale to 300 MB/s and 600 MB/s in future. SATA is also friendly to mobile form factors since it needs a much smaller connector than PATA. Also, both PCIe and SATA were designed from the ground up to be better power managed than their predecessors. Because of higher transfer rates they consume higher power during transfers. However, overall they will use less power since the work (transfer) is done quicker than it was done with previousgeneration interfaces. From a power-management perspective, it is best to get work done quickly in mobile platforms and then power down the link versus taking a longer time using less power.

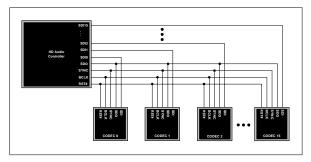

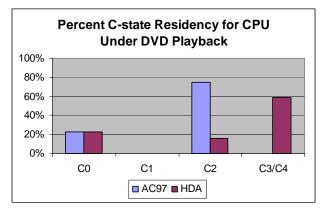

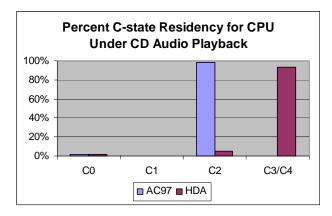

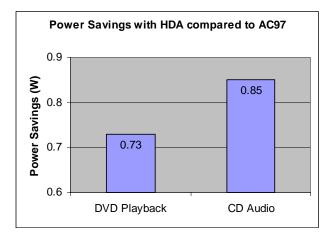

Finally, the second-generation platform built on Intel Centrino mobile technology introduces Intel HD Audio which delivers significant improvements over AC'97 previous-generation integrated audio and sound cards. Intel HD Audio hardware is capable of delivering the support and sound quality for up to eight channels at 192 kHz/32-bit quality, while the AC'97 specification can only support six channels at 48 kHz/20-bit. This new platform can support three external codecs with isochronous data transfers. In addition, Intel HD Audio is architected to prevent the occasional glitches or pops that other audio solutions can have by providing dedicated system bandwidth for critical audio functions. Intel HD audio offers considerable power savings (over 700 mW) for media-oriented workloads such as DVD and CD audio playback because it supports power management by allowing the processor to run in lower power states. Additionally, Intel HD Audio enables Dolby 5.1/7.1 surround sound audio out capability, which can be used with an SPDIF optical interface for component audio amplifiers.

To support PCIe, SATA, and Intel HD Audio, a newer cross-chip interconnect, Direct Media Interface (DMI), between the GMCH and the ICH, was developed. This upgraded the cross-chip transfer rate from 266 MB/s to 2 GB/s The DMI enables concurrent traffic and isochronous data transfer capabilities.

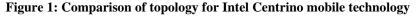

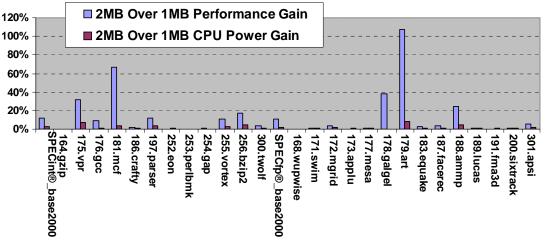

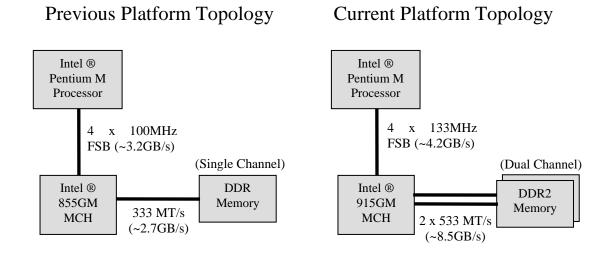

Platforms based on this new mobile technology support next-generation memory technology by implementing the DDR2 specification, an evolutionary technology that extends first-generation DDR (supported on the first Centrino mobile technology platforms). The new mobile technology platforms (i.e., GMCH) also introduce a second memory channel to system memory, effectively doubling the total available memory bandwidth especially for graphics' workloads. With dual-channel DDR2 memory support, these systems have increased peak bandwidth and lower per-SO-DIMM power consumption over first-generation Intel Centrino mobile technology platforms. The DDR2 specification allows increased clock rates over DDR while operating at 1.8 V vs. 2.5 V on earlier-generation technology. These platforms also support a peak bandwidth of 4.3 GB/s, a 60% increase over first-generation Intel Centrino mobile technology platforms, having a peak bandwidth of 2.7 GB/s (DDR 333 MHz). Together with the second channel, overall bandwidth of memory sub sub-systems will be around 8.5 GB/s.

<sup>&</sup>lt;sup>1</sup> Bluetooth is a trademark owned by its proprietor and used by Intel under license.

# **NEW COMPONENTS**

Intel's next-generation Pentium M (codename Dothan) processor implemented using Intel's 90nm technology has a number of new features. These include the L2 cache that has been doubled to 2 MB and at the same time optimized for reduced power. The Front-Side Bus (FSB) has been increased from 400 MHz to 533 MHz, and the available CPU frequencies have also been increased. Microarchitecture implementation has been optimized for performance and the Execute Disable Bit (XD) has been added to harden against buffer overflow virus attacks.

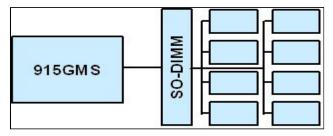

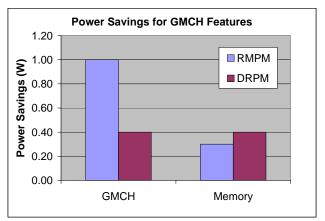

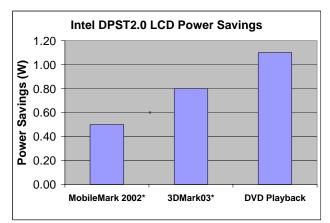

The i915 (codename Alviso) GMCH is the integrated GMCH for the second-generation platform built on Intel Centrino mobile technology delivering over 2x improvement in graphics performance over the previous 855GM controller. The i915 supports several newer and faster interfaces such as a 533 MHz FSB, two DDR2 Memory Channels, PEG (PCIe 16x) and a DMI link to ICH6-M. The integrated graphics controller includes support for Pixel Shader 2.0 and Microsoft Windows\* DX9 Graphics API, integrated TVout, and improved power and performance techniques such as Display Power Savings Technique 2 (DPST2), Intel Dual Frequency Graphics (IDFG), and Frame Buffer Compression (FBC) as well as techniques to increase processor C3/4 residency, thus decreasing average power consumption. There is also use of a virtual thermal sensor to help manage thermal throttling and shutdown. GMCH comes in two packages (Intel 915GM and Intel 915GMS) supporting full and reduced functionality to accommodate different form factors.

The Intel 82801FM ICH (ICH6-M) comprises newer interfaces: PCIe, SATA with an Advanced Host Controller Interface (AHCI), and Intel HD Audio devices to connect current and the next generation of high-performance and lower-power peripherals. In addition to these new interfaces, ICH6-M provides support for USB 1.1/2.0 as on the previous-generation ICH4-M, but it adds two additional ports. The ICH6-M also provides the interface for the Intel PRO/Wireless 2915ABG wireless module and ExpressCard devices. The latter removes the need for an additional PCMCIA controller, thus saving cost while providing higher performance and form-factor-friendly connectivity.

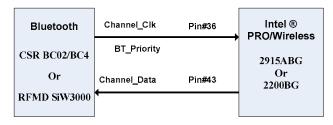

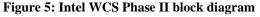

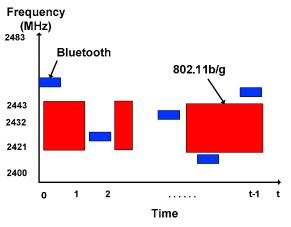

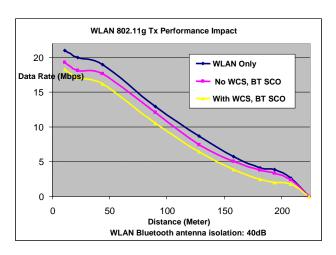

Finally, WLAN communication is provided by the Intel PRO/Wireless 2915ABG NIC. It supports 802.11a,

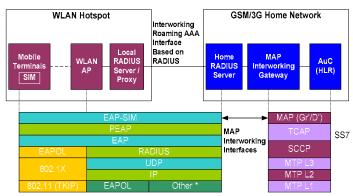

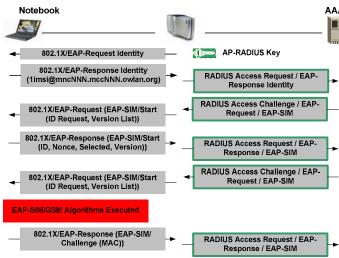

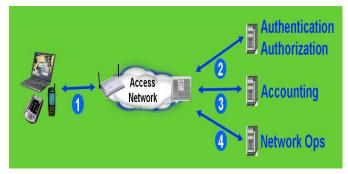

802.11b, and 802.11g with the Intel Wireless Coexistence System (WCS) II that mitigates wireless interference with wireless Bluetooth devices, for e.g., headsets. This solution also supports industry-standard wireless security features including WPA2 and Cisco Compatible Extensions v3. The Intel PRO/Wireless 2915 NIC also supports the EAP-SIM protocol that allows SIM credentials to be accessed from the WWAN GSM/GPRS add-in card or add-in USB SIM reader for use in WLAN authentication and billing. This would enable carriers with the qualified WWAN add-in cards or USB SIM Reader to provide One-Bill Roaming (OBR) capability for WLAN hotspots and WWAN usage.

The increased convenience of on-demand connectivity will result in a new set of requirements to address users' needs to maintain the value of being connected while they are in transit or while the notebook lid is closed. To address these needs, Intel introduces Extended Mobile Access (EMA) capability, which enables the notebook to become a more useful tool to the user all day long.

In 2005, EMA features will include a small external display (Figure 1), similar to what has been available on some new cell phones, that provides the user with quick access to calendar, contact, and e-mail information, as well as alerts, reminders, and network availability and connection status. Running in a low-power state, the mobile notebook will provide critical information without unnecessary drain on the battery. We believe this capability will become a standard one especially with the introduction of support for auxiliary displays in the next generation of the PC client operating system.

#### **NEW USAGES**

The second-generation platform built on Intel Centrino mobile technology enables new mobile usages with the above technologies and features. We divide these usages into three key categories: Mobile Digital Office, Mobile On-the-Go, and Mobile Entertainment (Figures 2a, b, c).

<sup>\*</sup> Other brands and names are the property of their respective owners.

Figure 2(a): Mobile Digital Office

Figure 2(b): Mobile On-the-Go

Figure 2(c): Mobile Entertainment

#### **Mobile Digital Office**

This usage is the evolution of the enterprise portable computer to a wirelessly connected mobile notebook. Our vision for this notebook is that it be an always-available virtual office with the following four pillars of the Digital Office:

- Embedded IT-making manageability and security transparent.

- Pervasive Connectivity–making wireless connectivity as easy as with a cell phone.

- Instant Teamwork–making collaboration spontaneous.

- Information Assistant-ready to relieve users from mundane tasks by anticipating their needs.

The second-generation platform built on Intel Centrino mobile technology takes a first step towards making this

vision a reality by driving delivery on the key pillars of the Digital Office. The Pentium M processor supports the XD bit that prevents buffer overflow type virus attacks. The Intel PRO/Wireless 2915 NIC supports all security standards and offers OBR capability to make connectivity easier between WLAN hotspots and WWAN (GSM/GPRS) through the use of SIM credentials. The second-generation platform also delivers the next iteration of the Intel Stable Image Platform Program (single set of drivers) for facilitating better manageability by reducing client environment complexity, which consequently reduces total cost of ownership.

With rapid adoption of Voice-Over-IP (VoIP), the mobile PC is the platform of choice for providing access to the office phone while at home or on the road, and for voice and video conferencing. Intel HD Audio provides a better way of attaching array microphones to the platform, thus delivering a great audio experience for collaboration through VoIP calls, rivaling the \$200 price tag of a

discrete microphone array used in high-end conference rooms. The CPU performance of the next-generation Pentium M processor is used for echo cancellation, ambient noise reduction, and optimization of codecs. Intel Wireless Coexistence System II in the Intel PRO/Wireless 2915ABG NIC mitigates interference resulting from overlapping harmonics of WLAN and Bluetooth radios operating in the same frequency spectrum. This enables the use of Bluetooth headsets for VoIP calls and for listening to music.

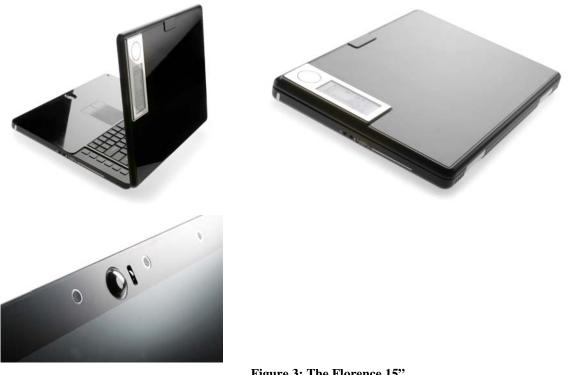

In order to inspire and demonstrate these usage models, Intel showcased the Florence Concept Family based on our new platform in the Spring of 2004 at the Intel Developers Forum. The first concept is the Florence 15" (Figure 3), and it delivers the promise of Digital Office as described with array microphones and camera for a great collaboration experience, a 15"-wide screen with a 16:9 aspect ratio for a great viewing experience, a finger print sensor for easier log in, and an EMA module for access to information on the go. This notebook also has an ExpressCard slot, a DVI connector, and a Smartcard slot for industry-standard smartcards. The system is based on the Intel Centrino mobile technology platform with a standard-voltage Pentium M processor, a 915 chipset, and an Intel PRO/Wireless 2915 NIC.

Intel is actively enabling ODMs and OEMS to make these Digital Office features part of their enterprise notebook offering starting in 2005.

#### **Mobile On-the-Go**

This usage is optimized for mobility in or out of the office or home, for productivity, entertainment, and communication. Highly mobile users prefer flexible thin and light mobile systems with optimized battery life. Flexibility allows the system to be used as a tablet or as a notebook either convertible or detachable. The system can be used to do all the work done on a Digital Office notebook while on the move. These systems can also acquire and view content such as photos, TV programs, music, or movies on a home network for consumption outside the home.

The second member of the Florence concept family is the 12" On-the-Go concept (Figure 4). This enables users to use it as a detachable tablet or as a laptop. It features array microphones, camera, finger print sensors, EMA display, and Bluetooth connectivity just like the Digital Office concept. Both the tablet and base with keyboard have lithium polymer battery packs for maximum battery life. The system also features a lower-power Low Temperature Poly Silicon (LTPS) display to enable lower average power, further enhancing the battery life of the platform. This concept is built on the Intel Centrino mobile technology platform and uses the ultra-low-voltage Pentium M processor, the 915 chipset, and Intel PRO/Wireless 2915 NIC, and it is passively cooled. It uses a 1.8 in. hard and optical drive.

Several OEMS, since the introduction of these concepts, have produced these kinds of detachable tablet/notebook systems.

Figure 3: The Florence 15"

Figure 4: The Florence 12"

#### **Mobile Entertainment**

This usage is optimized for entertainment: viewing movies, watching TV, sharing and editing photos, and playing games anywhere in the home. The Mobile Entertainment PC provides a consumer electronics experience with added PC functionality in a portable, allin-one form factor allowing the user to bring the PC and entertainment experience to more communal areas of the home, such as the kitchen or living room. The mobile entertainment PC is also a rich communications platform allowing users to make voice or video calls and create a "virtual gathering" with friends and family far away. This platform represents the convergence of computing, communications, and entertainment.

Figure 5: The Florence 17"

The final member of the 2004 Businessweek/IDA Gold award-winning Florence concept family is a 17" Mobile Entertainment PC (Figure 5). This innovative design turns a PC into a Digital Home Consumer Device. Its main usage is entertainment and communications, but when needed is also a high-performance wireless portable computer. The industrial design of this system reflects this usage; it looks like a 17" LCD TV screen with a stand, but hidden behind the stand are a wireless Bluetooth keyboard, remote control, and VoIP handset. These peripherals can be detached from the base and moved 6-10 feet away for viewing. The system is based on the second-generation Intel Centrino mobile technology platform with a standard-voltage Pentium M processor, a 915 chipset, and the Intel PRO/Wireless 2915 NIC. It delivers a HDTV-quality video experience and a good gaming experience with 915 graphics performance. Additionally, it incorporates array microphones and a camera, just like the two other members of the Florence family, to deliver a great virtual gathering experience with family and friends. The latter is now possible with broadband services delivered to a large percentage of homes. The Florence 17" screen is also a wireless TV (without a tuner) that receives TV broadcast over Intel PRO/Wireless 2915 NIC from a wireless TV receiver connected to a cable or satellite source. Such devices are now sold by Sony and Sharp to work with wireless TVs operating over IEEE 802.11a/b/g WLAN. The Florence family also uses Intel HD Audio to provide Dolby 5.1/7.1

surround sound audio with an SPDIF optical interface that can be interfaced with a component audio amplifier.

Intel is enabling these kinds of consumer systems for introduction in 2005. We expect this trend to continue with larger screen sizes. Our vision is to see every TV integrated with Intel Centrino mobile technology to provide a rich entertainment, communication, and computing experience.

# CONCLUSION

The second-generation platform built on Intel Centrino mobile technology excels on the four vectors of mobility delivering more performance through microarchitecture feature enhancements, 90nm process technology, and new interfaces while keeping the battery life of the platform the same as that of previous-generation technologies. These new interfaces, performance, and capabilities unleash exciting Mobile Digital Office, Mobile On-the-Go, and Mobile Entertainment usage models. Intel demonstrated these usage models through innovative concept platforms and are continuing to enable our OEMs and ODMs to include these capabilities in the next generation of mobile platforms.

# ACKNOWLEDGMENTS

We acknowledge all the members of the secondgeneration Centrino mobile technology platform and the Mobile Concept team for their dedication in making this platform happen. And special thanks to Tom Shewchuk for his dedication and help in guiding the development of this issue of Intel Technology Journal. And an additional acknowledgment to Judith C. Anthony for coordinating a seamless issue.

# **AUTHOR'S BIOGRAPHY**

Dr. Shreekant (Ticky) Thakkar is the director of mobile technology and is the Mobile visionary in Intel's Mobility Group. He has over 26 years of experience in various development and planning positions at Intel and Sequent (now part of IBM). Dr. Thakkar was a key driver in establishing the direction for mobile notebook PCs to transition from portable to wireless computing with Intel's Centrino mobile technology. Recently, he drove the convergence of computing, communications, and entertainment in the Mobility Group's Florence Concept Platform. Dr. Thakkar also created the Mobile Platform Architecture team within the Mobility Group. Prior to the Mobility Group, he was the general manager of a new business unit, Persona, which delivered smart proactive services over wired and wireless devices. At Intel, he also led the team that developed the Pentium Pro MP (Intel<sup>®</sup>

Xeon<sup>™</sup> processor) as well as teams that developed Multimedia/Graphics Media (SSE) extensions to the Pentium III and 4 processors. Among Dr. Thakkar's many accomplishments was bringing the Pentium Pro MP (Intel Xeon) processor to market in record time, 11 months from first silicon to production. He has led the development of security functionality in Intel's processors and chipsets and fills the roadmap planning role for Intel's microprocessor family. Prior to Intel, Dr. Thakkar pioneered the development of Shared Memory Multiprocessors and Databases on these systems at Sequent Computer Systems

Dr. Thakkar holds a Ph.D. degree, an M.S. degree in Computer Science/Engineering from the University of Manchester (England), and a B.S. degree in Computer Science/Statistics from the University of London. He holds or has pending applications for over 50 patents. Dr. Thakkar has published numerous articles and edited special editions of IEEE journals. His e-mail is ticky.thakker at intel.com.

Copyright © Intel Corporation 2005. This publication was downloaded from <u>http://www.intel.com/</u>.

Legal notices at <a href="http://www.intel.com/sites/corporate/tradmarx.htm">http://www.intel.com/sites/corporate/tradmarx.htm</a>.

<sup>&</sup>lt;sup>TM</sup> Xeon is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

# Intel<sup>®</sup> 915GMS Chipset: In Mobile Platforms, Smaller is Better

David W. Browning, Mobility Group, Intel Corporation Vinay Kumar C., Mobility Group, Intel Corporation Praveen G., Mobility Group, Intel Corporation Ananth V. Gopal, Digital Enterprise Group, Intel Corporation Tom Shewchuk, Mobility Group, Intel Corporation Suresh V. Subramanyam, Mobility Group, Intel Corporation

Index words: Intel 915GMS chipset, package, manufacturing, motherboard, routing

# ABSTRACT

The Intel<sup>®</sup> Centrino<sup>™</sup> mobile technology is based on four basic vectors of mobility: breakthrough mobile performance, integrated Wireless LAN (WLAN) capability, great battery life, and thinner, lighter designs. Historically, Intel's focus has been on increasing performance and, to a lesser extent, on improving power consumption. Intel Centrino mobile technology sharpens this focus and also allows Intel to increase the feature set of the platform to include wireless solutions. In this paper, however, we focus on the mostly overlooked promise of the fourth vector of mobility: thinner, lighter designs.

The packaging, manufacturing, and motherboard routing issues associated with enabling thinner lighter designs are explored in detail. We discuss the package electrical and motherboard breakout challenges, exploring the ideas and concepts used to ensure that reducing the package size will allow for high-volume manufacturing requirements. Finally, we discuss how Intel enables unique form factors through the support of specialized motherboard routing techniques. All of these solutions allow Intel Centrino mobile technology to provide a very convincing answer to the challenge of innovating compelling form factors.

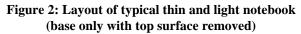

# INTRODUCTION

The Intel Centrino mobile technology was specifically developed for on-the-go computing, with a focus on the four vectors of mobility: breakthrough mobile performance, integrated Wireless LAN (WLAN) capability, great battery life, and thinner, lighter designs. When Centrino mobile technology platforms were introduced in March of 2003, notebooks became much smaller (X and Y) and much thinner (Z) compared to previous notebooks based on the Intel Pentium<sup>®</sup> 4 processor. This reduction was primarily due to the significantly lower Thermal Design Power (TDP) of the processor and the Graphics and Memory Controller Hub (GMCH) components compared to previous platforms.

However, even smaller form factors could not be developed as the size of the processor and GMCH components was still quite large; in fact these components were the largest two components on a mobile motherboard. For example, the Intel 855GM GMCH package was 37.5 mm square, even though the silicon die size was only 9 mm square. This was due to the very large number of pins on the package together with the board assembly technology required to get all these signals routed onto the motherboard.

As Intel started to develop the next-generation mobile PC platform built on Intel Centrino mobile technology, the GMCH package size actually grew by 7% to 37.5 mm x 40 mm. This growth was primarily due to the addition of a second channel of Double Data Rate (DDR2) system

<sup>&</sup>lt;sup>®</sup> Intel is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>&</sup>lt;sup>TM</sup> Centrino is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>&</sup>lt;sup>®</sup> Pentium is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

memory, that was required for the highest performance mobile notebooks. In order to continue to drive the thinner, lighter designs vector of mobility, Intel wanted to develop a significantly smaller GMCH package, specifically designed for the smallest (X and Y) and thinnest (Z) systems. Thus the idea of the Intel 915GMS chipset was born.

This paper explains the steps Intel took to design this new product. We first explain how the number of signal and power pins was reduced on this product, and how the package ball pitch was optimized while maintaining effective board routing. Second, we address the manufacturing concerns that result from a significantly smaller package. The result of our work was the creation of a 27 mm square Intel 915GMS package, a 51% size reduction from the standard Intel 915 package.

Third, we explain additional board-routing guidelines that were developed to allow mobile Original Equipment Manufacturers (OEMs) to further compress their motherboard layout. It is hard to know what new form factors will result from this, but OEMs are very creative when it comes to smaller and sleeker notebooks. We end with some ideas on what new usage models might result from this work, and we discuss future challenges for the continued push toward compelling form factors.

# INTEL 915GMS BREAKOUT ROUTING CHALLENGES AND SOLUTIONS

The standard Intel 915 chipset was developed in a 37.5 mm x 40 mm package. Many techniques were used to reduce the size of the Intel 915GMS package while still meeting the needs of the small form factor market.

# **Interface Removal**

One of the easiest ways to reduce the size of a package is to remove unnecessary features. A detailed investigation of the small form factor market led to an understanding of what subset of features of the Intel 915 chipset were needed. As seen in Table 1, ~300 pins were removed on four key Intel 915GMS interfaces.

| Interface       | 915GM | 915GMS | # Removed |

|-----------------|-------|--------|-----------|

| PCIe to Ext.GFX | 142   | 32     | 110       |

| DDR to Memory   | 383   | 227    | 156       |

| DMI to ICH      | 35    | 18     | 17        |

| LVDS to Panel   | 41    | 25     | 16        |

Table 1: Pin-reduction summary

During this analysis we found that the small form factor segment does not typically have room to accommodate an external graphics controller and therefore is primarily designed for internal graphics. Since the Intel 915 chipset family supports both internal and external graphics configurations, external graphics support was removed from the Intel 915GMS product in order to eliminate the majority of the Peripheral Component Interconnect (PCI) Express<sup>\*</sup> interface and its associated signal pins. This allowed us to remove 50 signal pins and 60 ground pins.

Another thing we found was that most of the small form factor systems only require a single channel of memory support due to their reduced performance needs. Since the Intel 915 chipset family supports both dual-channel and single-channel system memory, one of the two channels was removed to save ~120 signal pins. This also allowed approximately 30 power pins to be removed since fewer power pins were needed to support a single-channel memory configuration.

In addition to the reduced memory performance requirements, it was found that the small form factor systems also have reduced I/O performance requirements. The Intel 915 chipset family supports both a 4-lane Direct Media Interface (DMI) and a 2-lane DMI between the GMCH and the I/O Controller Hub (ICH). The reduced I/O performance requirement of the small form factor segment allowed us to alter the DMI bus for this chipset to only support a 2-lane configuration, and we thus were able to remove 17 more pins.

Finally, we found that most of the small form factor LCDs selected by OEMs and Original Design Manufacturers (ODMs) utilize a single channel of Low Voltage Differential Signaling (LVDS). This finding allowed the design team to remove one of the LVDS channels when developing the Intel 915GMS chipset to save another 16 pins.

The removal of these pins associated with the unnecessary interfaces allowed for a major reduction in package size, resulting in a 31 mm x 31 mm package. We then moved on to investigate making pin pitch changes to the pinout in order to shrink the package size even further.

# Parquet Package Technique

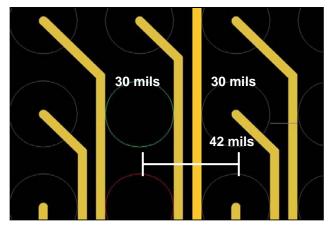

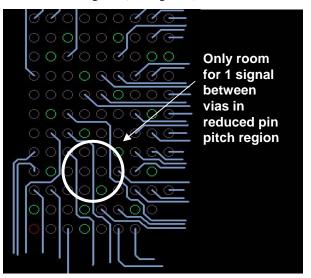

The standard Intel 915 chipset product utilizes a uniform grid pin pitch of 42 mils. This pin pitch was selected to allow two traces to route between the via field in the breakout region, assuming a via antipad diameter of 30 mils (a via size typically used in mobile high-volume manufacturing). After the vias' antipad area is accounted for there is only 12 mils of remaining room for trace routing. As illustrated in Figure 1, utilizing a standard

<sup>\*</sup> Other brands and names are the property of their respective owners.

stripline trace width of 4 mils allows for two traces to fit between the vias with 4 mils of space between them (hereafter referred to as 4:4 routing).

Figure 1: Breakout region routing dictated by via size

As can be seen, the minimum allowable pin pitch is directly related to the via size that is assumed for the platform. For the majority of mobile designs the standard via uses an antipad size of 30 mils so the resulting pin pitch is 42 mils (to allow for two tracks of 4:4 routing). However, the analysis of the small form factor market segment showed an inclination to utilize slightly more expensive motherboard technologies. This analysis showed that a 28 mil antipad was acceptable in this market and would allow for some pin compression. Therefore, the Intel 915GMS pin pitch was reduced from 42 mils to 40 mils (assuming a via with a 28 mil antipad).

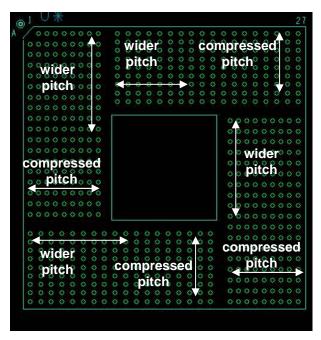

Upon closer inspection of the breakout routing of the standard Intel 915 chipset package, it was determined that the perpendicular (or "transverse") routing channels were not being utilized. In effect, all of the signals were breaking out in a radial fashion away from the center of the package. This observation led to the idea of reducing the perpendicular pin pitch to something smaller than 40 mils to "compress" the package even further. In order to achieve an equal amount of compression along all four package sides, the parquet technique was developed.

The parquet package technique is composed of four periphery sections and a center region. Each of the periphery sections utilizes a wider pin pitch in the direction along the package edge, and they utilize a reduced pin pitch in the direction towards the package center (see Figure 2). The result is a 40 x 32 mil parquet pin pitch.

Figure 2: Parquet package illustration

The parquet package routing technique is not without challenges of its own. In particular, since one of the pin pitches is reduced to 32 mils, there is only enough room to route one signal in a perpendicular fashion to the typical breakout direction. This in itself presents no problem, because as the signal density increases so can the complexity of trying to find a breakout routing solution for each of the signals (see Figure 3).

**Figure 3: Transverse parquet routing**

# **Corridor Routing**

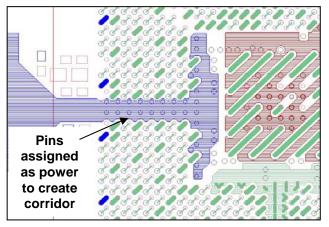

An additional benefit of the parquet package technique is that it provides natural "gaps" or "corridors" where two different parquet periphery sections meet. These corridors have a wider pin pitch and therefore can be used to route more signals, or to provide a wider gap for power delivery (see gaps between periphery sections in Figure 2).

In addition to the natural corridors, the Intel 915GMS pinmap creates some artificial corridors with power pin assignments. The pinmap assigns power pins in corridor shapes from the edge of the package towards the center region. These "power corridors" have power delivery benefits since they allow a wider copper flood on the surface layer to connect to the package and therefore can accommodate higher currents and provide a lower DC-power loss routing path for power delivery (see Figure 4).

Figure 4: Power corridor on top-surface layer

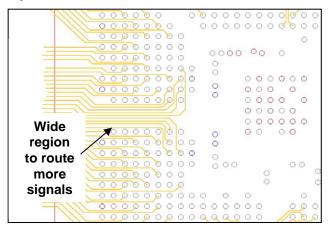

Another benefit of the corridors is that they allow higher signal density breakout on the inner stripline layers due to that region being absent of vias. Without a via being associated with every package pin, these corridors can be seen on internal routing layers as a wide unused region through which many signals can be routed. This allows for greater signal density within a smaller package size (see Figure 5).

Figure 5: Signal routing under power corridor

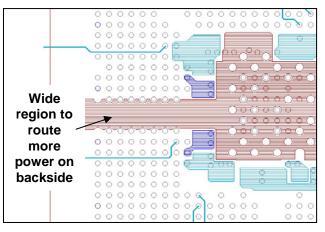

The final benefit of power corridors is that the same advantage seen on internal layers is seen on the backside surface layer. Just like the wide open regions on the internal layers, the backside surface layer is open and can be used to deliver wide copper floods for additional power delivery (see Figure 6).

Figure 6: Power routing under power corridor

Together with interface removal, the parquet package technique, and corridor routing, the size of the Intel 915GMS package was reduced to  $27 \times 27$  mm, a 51% area reduction from the original 37.5 x 40 mm package size of the standard Intel 915 chipset.

# PACKAGE SUBSTRATE LAYOUT AND PACKAGE TECHNOLOGY CHALLENGES

The challenges faced by the package development team in delivering the Intel 915GMS package included pushing key assembly technology parameters.

# Package Size and Layer Stack-up

The package development team was given the task of delivering the smallest package possible for the given product feature-set yet still meeting the electrical requirements.

Using a 6-layer package substrate, similar to the standard Intel 915 chipset package, would have resulted in a package size of at least 35 mm. Moving to an 8-layer package substrate would enable the bulk of the signals, mainly front-side bus (FSB) and DDR2, to be routed as striplines, and this would reduce the size of the package. As mentioned earlier, there were a couple of package sizes that were considered during the feasibility analysis phase.

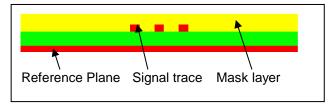

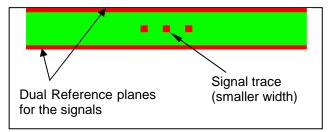

Refer to Figure 7 and Figure 8 for definitions of microstrip and stripline routing.

Figure 7: Microstrip signal routing

Figure 8: Stripline signal routing

The Intel 915 chipset used a 6-layer package substrate with all the signals routed on the surface layer as microstrip. Stripline routing with smaller trace width and spacing, when compared to microstrip routing, allowed us to achieve more routes per unit area, while maintaining the electrical integrity. Utilizing a 26  $\mu$ m trace width for stripline results in a 50-ohms impedance as compared to a 55-ohm impedance which is found on the Intel 915 chipset. We decided to proceed with a 26  $\mu$ m trace width for FSB and DDR2. The 5-ohms mismatch was deemed a non issue for FSB speeds @ 400/533 MHz. With DDR2 motherboard routing optimal at 40-ohms, the 50-ohms on the Intel 915GMS package was seen as an advantage over the 55-ohms on the standard Intel 915 chipset package.

# Sub 1.0 mm Ball Pitch

One of the two package options required a minimum ball pitch of 0.8128 mm (32 mils) that was falling out of the Intel certified flip chip package technology envelope. Limited experimental reliability data was available on sub 1.0 mm ball pitch. The initial experimental data collected for the shock and vibrations test, for sub 1.0 mm ball pitch, showed that the solder joint reliability was a manageable risk. The product development team decided to continue working on the sub 1.0 mm pitch package design.

The package substrate design was intercepted, just before the design completion, to enlarge the ball grid array (BGA) pad size, an increase that was recommended based on the initial experimental results. For the subsequent shock and vibration experiments, Design of Experiments (DOEs) were planned with refined mobile shock tests and increased pad size on the substrate. Engineers from the Intel Technology and Manufacturing groups and the Mobile Chipset Products group worked closely to define a new experimental set-up including the Shock-Test Board design and the revised Shock-Test Spec. Interaction with key customers to understand the system-level designs and their capability for shock and vibration formed part of the DOEs' planning process. The data collected using the Intel 915GMS chipset Thermo-Mechanical Test Vehicle (TMTV) showed that the overall shock and vibration risk level of the Intel 915GMS package was manageable, and so the technology was certified.

# Keep-Out Zone (KOZ) Reduction

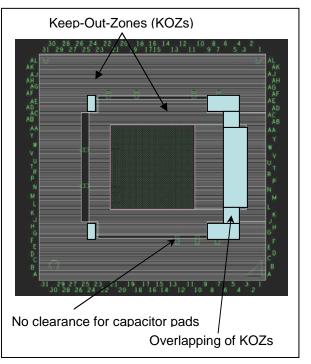

Certain areas on the top surface of the package must be clear of any interferences: the die, decoupling capacitors, and underfill material. These are called Keep-Out Zones (KOZs) and are needed for handling of the package during the package assembly and testing processes.

Figure 9 shows the KOZs surrounding the die and the package periphery. The zones shown were defined as per the Intel Package Design specifications. As you can see, there is an overlap of KOZs at various locations. The overlapping of the KOZs violated the design specification and does not accommodate any on-package capacitors.

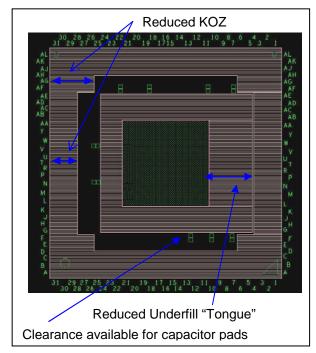

Experiments in the assembly and test areas were initiated to determine how to reduce the KOZs. The experiments yielded positive results. The Edge exclusion zone was reduced by over 25% of the specification and the Corner exclusion zone was reduced by 35%.

Figure 9: KOZs overlapping (before modifying the Intel Package Design spec)

Figure 10 shows the modified KOZs, which allowed the design to accommodate the on-package capacitors.

#### Figure 10: KOZs after modification of Intel Package Design spec

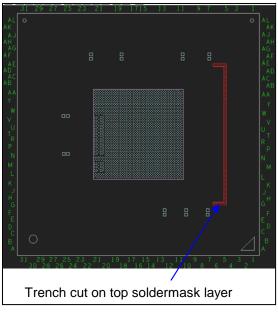

Also, the assembly line experiments showed that we could reduce the Underfill Tongue-width by 17%, which was needed to avoid overlap with the already "reduced" edge exclusion zone. A "trench" was cut on the top solder mask layer that further enabled us to reduce the tongue width. Since the routing on the east side was stripline, the trench was implemented without any signal traces passing across the trench. Figure 11 shows the trench design.

Figure 11: Location of the trench

# MOTHERBOARD ROUTING IMPROVEMENTS

Along with providing an optimized chipset for small formfactor platforms, Intel has also put effort into developing guidelines to help in reducing the motherboard size and in reducing the effort required to design a small form-factor platform.

In the following sections, we discuss these guidelines and their benefits. The guidelines are optimized for two important areas: system memory and FSB.

# System Memory Guidelines

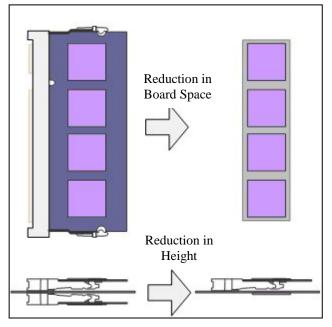

With the Intel 915GMS chipset, Intel provided guidelines for implementing on-board memory that helps to reduce the size of the board. In a notebook design, there are many benefits if one can design the memory on the board rather than utilizing Small Outline Dual Inline Memory Modules (SO-DIMMs). By going for on-board memory, along with a reduction in the board size, a reduction in height can also be achieved.

Typically, the notebooks that are available in the market have two SO-DIMM slots. The product is sold with one SO-DIMM pre-installed; if consumers wish to increase the memory, they can buy an additional SO-DIMM and upgrade their notebooks. With Intel 915GMS platforms, designers can take advantage of the new on-board memory guidelines to change the pre-installed memory from SO-DIMM to on-board memory. Also, with products where a memory upgrade by the end user is not feasible, on-board memory can supply the total memory requirements of the platform. Figure 12 illustrates the benefits achieved, with respect to board size and height, when designed with one SO-DIMM and on-board memory as compared to two SO-DIMMs. Benefits would even be greater if only on-board memory is supported.

Figure 12: Benefits of on-board memory

Intel provides guidelines for various configurations with SO-DIMM and on-board memory. With these configurations, one can design the platform that can support up to 2 GB of memory. Table 2 lists these configurations and the maximum memory possible when 1 Gbit memory devices are used.

| Configuration<br>(in space-saving order) | Max Memory (with<br>1 Gbit Technology) |

|------------------------------------------|----------------------------------------|

| 1 rank (4 devices) on-board              | 512 MB                                 |

| 2 ranks (8 devices) on-board             | 1 GB                                   |

| 1 SO-DIMM                                | 1 GB                                   |

| 1 SO-DIMM & 1 rank on-board              | 1.5 GB                                 |

| 1 SO-DIMM & 2 ranks on-board             | 2 GB                                   |

| 2 SO-DIMMs                               | 2 GB                                   |

| Table | 2: | Various  | configurations |

|-------|----|----------|----------------|

| Lable |    | , alloub | comigarations  |

A configuration of four SDRAM components, where all four components are on the same side in one row, is the simplest configuration to route and yields the best signal integrity as well as timing budgets. When designing with eight SDRAM components, it is recommended to have four components on the top and four on the bottom of the board. This configuration is easier to route and has better signal integrity than designs where all of the eight components are on the same side: these may necessitate the use of more than 8-layer boards in order to route all of the memory signals.

For the configurations with on-board memory, the recommendations are for the SO-DIMM to be placed closest to the Intel 915GMS and the on-board memory SDRAM devices to be placed farthest away from the Intel 915GMS. Figure 13 shows the topology for one SO-DIMM and eight devices on the board.

Figure 13: Simplified topology with eight memory devices

# **Front-Side Bus Guidelines**

Intel 915GMS supports a 400 MT/s FSB to connect to low-voltage and ultra-low-voltage processors based on Intel Pentium M 90nm technology. The FSB guidelines were optimized to ease the routing on small form-factor platforms. With these optimized guidelines, the minimum routing length of the FSB signals can be as low as 0.1" as compared to 0.5" for earlier platforms. This provides the possibility of placing the processor and the Intel 915GMS very close to each other. Also, the minimum signal-tosignal spacing of the FSB interface can be as low as 1:1 (4 mil trace and 4 mil space) as compared to 1:2 (4 mil trace and 8 mil space) of earlier platforms. The reduced spacing requirement makes routing of FSB signals more flexible and also allows for denser routing of the signals. This leads to a reduction in the required routing space on the board.

# **INTEL 915GMS USAGE MODELS**

Up to this point we have focused our discussion on what was done to reduce the size of the Intel 915GMS chipset. This reduced size delivers on the Intel Centrino brand promise of enabling unique form factors. However, what exactly will these products look like? How can this technology be used?

There are many vertical segments that might be interested in smaller and lighter form factors: health care, research, entertainment, and education, for example. These designs could be in the form of Tablet PCs, extremely thin-andlight notebooks, or something radically new. Only time will tell what creative OEMs will do with these platforms, based on the Intel 915GMS platforms.

In the field of health care, for example, people move around a lot such as in hospitals where doctors and nurses need to gather information from many patients. Most of this information today is not digitized. Smaller tablet designs could provide the right combination of features to push digitization into this field and make this usage model real.

Similar to the health care profession, researchers in all disciplines require mobility in order to collect information in the field. For these individuals, smaller and lighter notebooks would provide greater ease of data collection. Notebooks, based on the Centrino mobile technology, also provide the ability to wirelessly upload these data to laboratories for analysis and storage.

OEMs targeting consumers who purchase mobile PCs to enjoy entertainment have many opportunities to take advantage of smaller form factors. The reduced size of the Intel 915GMS could be coupled with designed-in features like small wide-aspect ratio LCDs, and the capability to instantly wake-up the platform into a DVD-playback mode. This effort could result in a smaller entertainment focused mobile platform.

As notebook computers get smaller and lighter, their use in education by students will also increase. For example, students currently carry most of their text books to and from school. By making use of Intel's smaller and lighter notebooks, students would have less heavy books to carry; something that would also make it easier for younger students where the weight of books is often an issue.

As the market for personal computers expands so will the demanded usages from customers. The examples listed above are only a few of the areas where the Intel 915GMS chipset can provide for further development of the uniqueness that mobility provides.

# **Future Challenges**

The Intel 915GMS chipset improves upon the form-factor promise of the Intel Centrino mobile technology brand. However, there are areas where future improvements could be made in order to allow form factors to become even smaller. The underlying design challenge is to reduce the size of the platform, while still providing performance and great battery life.

First and foremost, the techniques used on the Intel 915GMS product need to be utilized on other components on the platform, including the Intel Pentium M processor, ICH, and wireless solutions. Ball pitch and board routing technologies can be pushed to even further reduce

package sizes. And additional integration of other platform components, removal of resistors and capacitors, and voltage plane reduction will all help to even further reduce the size of systems based on Intel Centrino mobile technology.

Advancement in some of these areas will be required to continue to push the vector of thinner, lighter designs, and some are being considered by Intel for use in future generations of small form-factor designs.

# SUMMARY AND CONCLUSION

Together with signal and power-pin reduction, optimized package ball pitch, and resolution of manufacturing concerns, Intel was able to develop the Intel 915GMS product with a 27 mm square package, a 51% reduction from the standard Intel 915 package.

The excitement from the customer base is clear: there are more than a dozen Intel 915GMS platforms in development, all ready to launch in the March 2005 through September 2005 timeframe. Customers will be able to take advantage of this small package, and use the routing guidelines to further reduce the board area of their products. Intel expects that this will enable smaller and sleeker form factors, and potentially new usage models. And as the interest of platforms based on Intel Centrino mobile technology continues to grow, it is clear that the Intel 915GMS is just the first of many products focused on smaller and sleeker form factors.

# ACKNOWLEDGMENTS

The authors acknowledge all of the Intel teams who worked together to develop the Intel 915GMS chipset. This list includes, but is not limited to, the Product Development Team, the Package Development Team, the Second Level Interconnect Team, the Future Platform Enabling Team, the Signal Integrity Analysis Team, the Power Delivery Team, the Assembly/Test/Development Team, the Manufacturing Team, the Board Development Team, the Post-Silicon Validation Team, and the Applications Engineering Team.

# **AUTHORS' BIOGRAPHIES**

**David W. Browning** is a senior design engineer in the Mobile Product Group at Intel Corporation with a focus on advanced mobile platform architecture. He has been working for Intel for more than six years. David has a B.S. degree in Electrical Engineering from the University of Washington. His e-mail is david.w.browning at intel.com

**Vinay Kumar C.** is a platform application engineer and was in charge of the platform design guide document. He also provided technical support on Intel 915 to mobile customers. He has a B.E. degree in Electronics and

Communication from India. After a job at Force Computers as a board designer he joined Intel in 2003. His e-mail is vinay.k.c at intel.com.

**Praveen G.** is a platform application engineer and was in charge of the chipset datasheet. He also provided technical support on the Intel 915 chipset to mobile customers. He has a B.E. degree in Electronics and Communication from India. After a job at Force Computers as a board designer he joined Intel in 2003. His e-mail is praveen.g at intel.com.

**Ananth V. Gopal** is a software platform application engineer and provided technical support on the Intel 915 chipset to mobile customers. He has a B.E. degree in Computer Science and Engineering from India. He joined Intel in 2003. His e-mail is ananth.v.gopal at intel.com.

**Tom Shewchuk** was the Intel 915 chipset program manager and currently is managing Intel's next-generation mobile chipsets. He has B.S.E.E, M.S.E.E, and M.B.A. degrees, all from the University of Illinois at Urbana-Champaign. After jobs at Honeywell and Ford Microelectronics, he joined Intel in 1991, spending his first five years working on microprocessors, and the past nine years working on integrated graphics chipsets. His e-mail is tom.j.shewchuk at intel.com.

**Suresh V. Subramanyam** is the package design manager with Intel, India, supporting mobile chipsets. He has a B.S.M.E. degree from India and an M.S. degree in Materials Science & Engineering from Singapore. He joined Intel in 2003 after spending six years with HP/Agilent, Singapore. He started his career with Bharat Electronics, Bangalore, India, in 1988. His e-mail is suresh.v.subramanyam at intel.com.

Copyright © Intel Corporation 2005. This publication was downloaded from <u>http://www.intel.com/</u>.

Legal notices at <a href="http://www.intel.com/sites/corporate/tradmarx.htm">http://www.intel.com/sites/corporate/tradmarx.htm</a>.

#### THIS PAGE INTENTIONALLY LEFT BLANK

# The Emergence of PCI Express<sup>\*</sup> in the Next Generation of Mobile Platforms

Mohammad Kolbehdari, Digital Enterprise Group, Intel Corporation David Harriman, Digital Enterprise Group, Intel Corporation Altug Koker, Mobility Group, Intel Corporation Seh Kwa, Mobility Group, Intel Corporation Brad Saunders, Mobility Group, Intel Corporation

Index words: PCI Express\* architecture, ExpressCard\*, mini-card, GMCH, ICH, SIOM, DLLP, TLP, PHY, power management (PM), reliability, high-end graphics, PC built on Intel<sup>®</sup> Centrino<sup>TM</sup> mobile technology

# ABSTRACT

The PCI Express\* architecture, both as a unified foundation of I/O, graphics, and networking interconnections, and as a preeminent building block on chip-to-chip, board-to-board, and system-to-system, is widely adopted by multiple market segments in the computing and communication industries. PCI Express architecture is a state-of-the-art serial interconnect technology that keeps pace with recent advances in processor and memory subsystems. From its initial release at 0.8 V, 2.5 GHz, the PCI Express technology has evolved to the general-purpose interconnect of choice for a wide range of applications, including graphics, storage, networking, etc. The PCI Express architecture retains the familiar PCI software and configuration interfaces for seamless migration and adoption in desktop and mobile PC platforms, enterprise servers and workstations, and, increasingly, a wide range of communication and embedded systems.

The PCI Express technology addresses requirements from multiple market segments in the computing and communication industries, and it supports chip-to-chip, board-to-board, and adapter solutions at an equivalent or lower cost than existing PCI designs. Currently, PCI Express architecture supports a 2.5 GT/s signaling rate that yields 500 MB/s bandwidth per lane and a maximum bandwidth of 16 GB/s in a 32-lane configuration. Consistent with the expected cadence of I/O performance progression, the next generation of the PCI Express interconnect will support a signaling rate of 5 GT/s, doubling the performance of the existing links.

The PCI Express interconnect provides numerous architectural improvements over existing I/O technologies. It defines a native hot-plug scheme, enables aggressive power management, provides advanced Reliability, Availability, and Serviceability (RAS) and Quality of Service (QoS) features, and simplifies PCB layouts. In this paper, we discuss the unique, universal capabilities and values of PCI Express technology emerging in the next generation of mobile platforms. We focus on PCI Express architecture, power management, and mobile applications such as graphics, networking, and form factors including the ExpressCard\* module as well as future form factors such as the PCI Express Wireless Card and the PCI Express Mini Card. Finally, we cover the next generation of mobile PC platforms built on the Intel® Centrino<sup>™</sup> mobile technology.

#### **INTRODUCTION**

The PCI Express technology has emerged as the platform I/O solution of choice in the computing and communications industries. Some significant features of the PCI Express technology are also geared towards the next generation of mobile platform designs especially the Active State Power Management (ASPM) capability that enables aggressive power management within the link

<sup>\*</sup> Other brands and names are the property of their respective owners.

<sup>&</sup>lt;sup>®</sup> Intel is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>&</sup>lt;sup>TM</sup> Centrino is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

layer as defined in the PCI Express Base specification. Support for ASPM varies by form factor; however, all mobile electromechanical specifications require ASPM support by PCI Express applications. In this paper, we focus on PCI Express applications, PCI Express architecture and protocols, as well as PCI Express form factors for next-generation mobile platforms and high performance, such as ExpressCard module defined by the Personal Computer Memory Card International Association (PCMCIA) industry group and the PCI Express Mini Card defined by the PCI Special Interest Group (PCI-SIG).

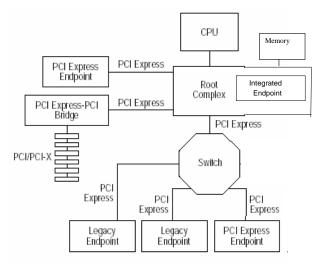

Additionally, the next-generation Intel Centrino mobile technology platform contains a variant of the Intel 915 Express as its "root complex." This chipset is comprised of a PCI Express x16 link optimized for high-performance graphics applications chipsets, the Graphics Memory Controller Hub (GMCH), and the I/O Controller Hub (ICH), which provide four PCI Express x1 links for general-purpose I/O applications. These latter links can be used to implement a combination of PCI Express Mini Card sockets, slots for ExpressCard modules, and other PCI Express devices on the system board that enable communications, storage, or other peripheral applications. If additional ports are necessary to implement a higherend platform, OEMs may add a PCI Express switch to the ICH to increase I/O fanout. To facilitate a smooth, gradual transition for legacy devices, the conventional, multi-drop PCI bus continues to be supported via the ICH.

# PCI EXPRESS ARCHITECTURE

#### **Architectural Overview**

The PCI Express architecture uses familiar software and configuration interfaces, the conventional PCI bus architecture, by providing a new high-performance physical interface and numerous new and enhanced capabilities that are built into a framework that retains software compatibility with the existing conventional PCI infrastructure. The enhanced capability is new and different from the legacy, parallel PCI bus architecture and supports scalable link widths in 1-, 2-, 4-, 8-, 16- and 32-lane configurations.

PCI Express power management is built on the PCI Power Management (PCI-PM) software architecture defined for conventional PCI. Additional PCI Express specific powermanagement capabilities are defined that further extend power manageability by allowing direct hardware control of power states with entry and exit latencies that are low enough to be effectively invisible to software.

PCI Express supports a native hot-plug architecture. Hotplug support requirements vary by form factor and are documented in the various PCI Express electromechanical specifications. The hot-plug "Toolkit" is defined in the PCI Express base specification to ensure a consistent, common interface for system software to correctly manage hot-plug operations.

PCI Express architecture supports numerous Reliability, Availability, and Serviceability (RAS) features such as error detection and reporting that can be detected using an End-to-end Cyclic Redundancy Check (ECRC) and a Cyclic Redundancy Check (CRC). Erroneous packets are corrected, and the reporting and logging of error conditions is considerably expanded. Mechanisms such as traffic service differentiation, including architecturally defined mechanisms for system control of arbitration, are also provided.

Support for multiple form factors was considered from the outset of the architecture definition. In addition to a card form factor (similar to the existing mainstream PCI cards/slots), there are other form factors defined such as the PCI Express Mini Card, also similar to the existing conventional Mini PCI form factor for notebooks, the ExpressCard standard, meant to replace the CardBus PC Card<sup>\*</sup> form factor, a wireless card form factor designed to fit in the lid of notebook computers, an enterprise-class hot-plug module commonly called a Server I/O Module (SIOM), and several mezzanine cards and blade modules. Additional form factors are being defined.

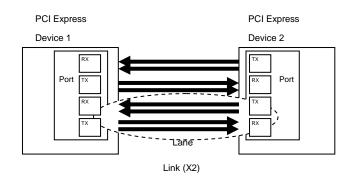

Figure 1: PCI Express architecture system

Figure 1 shows an example of the PCI Express architecture system. There are six types of PCI Express devices. Endpoints include devices such as network and disk interfaces, and they are categorized as either PCI Express Native endpoints or Legacy endpoints. The

<sup>\*</sup> Other brands and names are the property of their respective owners.

Legacy endpoint category is intended for existing designs that have been migrated to PCI Express, and it allows legacy behaviors such as use of I/O space and locked transactions. PCI Express endpoints are not permitted to require the use of I/O space at runtime and must not use locked transactions. By distinguishing these categories, it is possible for a system designer to restrict or eliminate legacy behaviors that have negative impacts on system performance and robustness. PCI Express/PCI Bridges allow older PCI devices to be connected to PCI Expressbased systems. Since PCI Express is a point-to-point interconnect, switches are used to increase connectivity. The Root Complex (RC), which includes the Graphics Memory Controller Hub (GMCH) and the I/O Controller Hub (ICH), is at the top of a PCI Express hierarchy, and it connects PCI Express to the CPU and main memory.

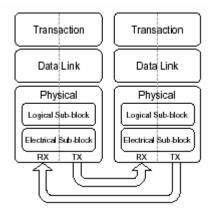

Figure 2: PCI Express link and layered architecture

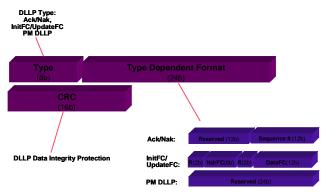

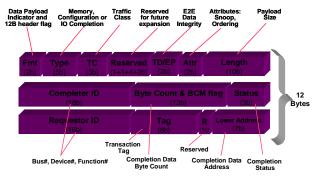

Figure 2 shows two components connected by PCI Express and highlights the layered structure of the PCI Express interface at the upper component. It should be noted that the layering structure shown represents the way PCI Express is described, but is not an implementation requirement. The Physical Layer (PHY) initialized the link between the two components on a link, and it manages low-level aspects of data transfer and power management. The Data Link Layer (DLL) provides reliable data transfer service to the Transaction Layer (TL) and also a lower overhead communication mechanism for link management of flow control and power. Data packets generated and consumed by the DLL are called Data Link Layer Packets (DLLPs). The TL generates and consumes data packets used to implement load/store data transfer mechanisms and also manages the flow control of those packets between the two components on a link. Data packets generated and consumed by the TL are called Transaction Layer Packets (TLPs).

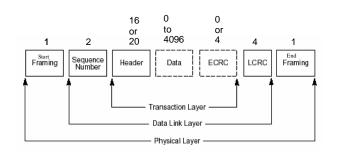

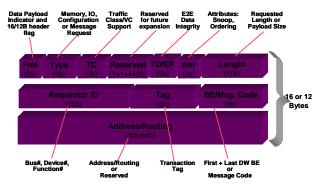

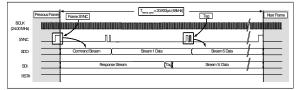

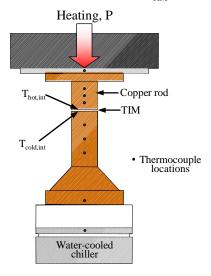

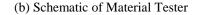

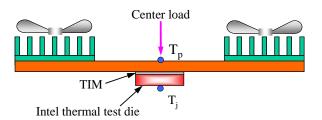

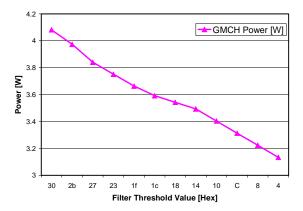

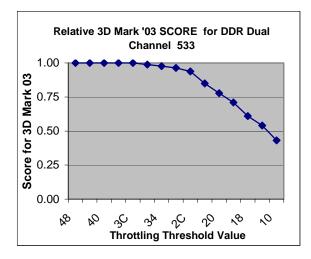

#### Figure 3: Representation of a Transaction Layer Packet as transmitted over a link