Issue 02

# Intel® Technology Journal

## **Optical Technologies and Applications**

This issue of Intel Technology Journal discusses Intel's work on optical interconnects; commercial optical transceiver products that combine leading-edge packaging and assembly technologies with advanced electronics; and collaborative research with academia focusing on bringing optical closer to and around the microprocessor.

Inside you'll find the following papers:

Optical Technologies for Enterprise Networks Optical Interconnect System Integration for Ultra-Short-Reach Applications

**On-Chip Optical Interconnects**

10 Gb/s Optical Transceivers: Fundamentals and Emerging Technologies

Automated Optical Packaging Technology for 10 Gb/s Transceivers and its Application to a Low-Cost Full C-Band Tunable Transmitter **Silicon Photonics**

Indium Phosphide-Based Optoelectronic Wavelength Conversion for High-Speed Optical Networks

More information, including current and past issues of Intel Technology Journal, can be found at: http://developer.intel.com/technology/itj/index.htm Volume 08

Issue 02

## Intel® Technology Journal

## Optical Technologies and Applications

## Articles

| Preface                                                                                                                              | iii |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Foreword                                                                                                                             | v   |

| Technical Reviewers                                                                                                                  | vii |

| Optical Technologies for Enterprise Networks                                                                                         | 73  |

| 10 Gb/s Optical Transceivers:<br>Fundamentals and Emerging Technologies                                                              | 83  |

| Automated Optical Packaging Technology for 10 Gb/s Transceivers<br>and its Application to a Low-Cost Full C-Band Tunable Transmitter | 101 |

| Optical Interconnect System Integration for Ultra-Short-Reach Applications                                                           | 115 |

| On-Chip Optical Interconnects                                                                                                        | 129 |

| Silicon Photonics                                                                                                                    | 143 |

| Indium Phosphide-Based Optoelectronic Wavelength Conversion<br>for High-Speed Optical Networks                                       | 161 |

#### THIS PAGE INTENTIONALLY LEFT BLANK

## Preface

By Lin Chao Publisher, Intel Technology Journal

Optical (light-based) devices are typically used by telecom companies and long-haul fiber-optic networks for high-bandwidth communications. Optical devices direct information coded in light, or photons, the basic unit of energy associated with light. The goal for today's computing and communications networks is to deliver more data faster, so the ability to process information at the speed of light—the fastest possible speed known today at 300 million meters per second—clearly has its advantages.

Electrons flow through silicon, the common building material for today's integrated circuits. But photons can travel farther and faster. Optical devices are typically made not on silicon, but on exotic materials from the column III and column V family of elements in the periodical table, such as indium phosphide and gallium arsenide. And these III-V materials have limitations due to difficulty of manufacturing and associated higher costs.

Intel is interested in applying Intel's volume manufacturing expertise and Moore's Law to optical communications. This Intel Technology Journal (Volume 8, Issue 2) examines Intel's and collaborative academia work on optical transceivers, interconnects, and optical research.

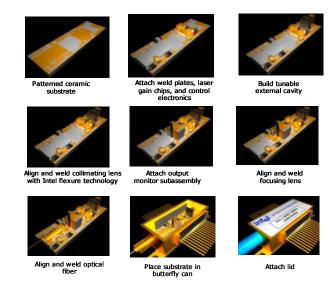

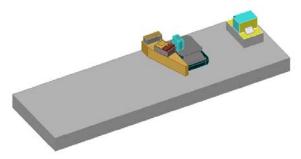

The first paper examines the fundamentals of optical interconnect technologies, their potential to replace copper-based interconnects inside and around servers, PCs, and the devices that connect to them. The second paper details a common 10 Gb/s optical transceiver architecture, tradeoffs in designing a wavelength tunable DWDM transceiver, and technology for electronic dispersion compensation. The third paper describes the planar automated package and how it can be adapted to the practical manufacturing of tunable transmitters.

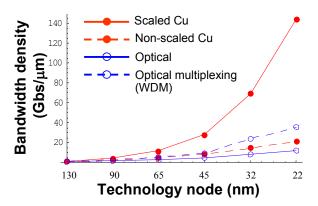

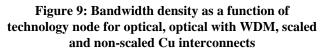

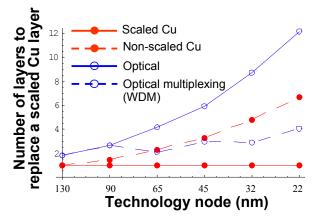

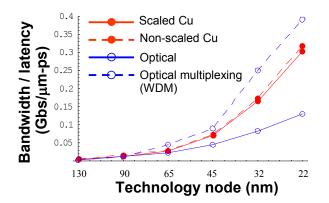

The next two papers discuss optical interconnects. Optical interconnects could be a viable solution to the predicted bandwidth limitations for copper interconnects on integrated circuits both in Ultra-Short-Reach (<10m) applications and on chip. On-chip optical interconnects can offer decreased interconnect delays and provide higher bandwidth, with lower power consumption and resistance to EMI.

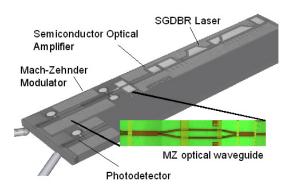

The last two papers examine research underway in silicon photonics and monolithically integrated wavelength converters (WCs) made on Indium Phosphide. Silicon photonics uses silicon-based materials for the generation, guidance, control, and detection of light. The Silicon Photonics paper looks at Intel's approach to opto-electronic integration, silicon photonics, and opto-electronic integration platforms. The final paper discusses research—undertaken jointly with the University of California at Santa Barbara and Stanford University—into novel approaches for monolithically integrating Wavelength Converters (WCs) in Indium Phosphide.

These papers reveal the excitement underway as Intel and the industry research how to harness the speed of light into computers and communications that we use every day.

### Foreword

#### A New Era in Optical Communications By Mario Paniccia Director Photonics Technology Lab, Intel Corporation

The thirst for information and the need to "always be connected" is spawning a new era of communications. This new era will drive the need for higher bandwidth technologies in order to keep pace with increasing processor performance, driven by Moore's Law. Today, computing is often limited less by microprocessor performance than by the rate at which data can be transmitted between the processor to the outside world. As the demand for higher bandwidth continues to steadily grow, an increasing number of optical technologies are replacing copper-based interconnects to meet the needed higher bandwidth performance requirements. These optical-based technologies are not only important for the traditional long-haul telecommunications market, but are becoming increasingly more important for the connections inside and around servers, PCs and the devices that connect to them. Optical offers many advantages besides pure bandwidth; these include reduction in EMI (Electro-Magnetic Interference), reduced signal cross talk, lower weight and improved security.

Over the past decade, optical communication technologies have migrated steadily from long-haul backbones to the network edge, invading Metropolitan Area Networks (MANs) and campus-level Local Area Networks (LANs). A key inflection point will come when optical technologies are used to interconnect within and around enterprise networks and access points. One of the most important consequences of this migration has been the need to develop more efficient and lower cost optical technologies and solutions. The future of optical networks rests on the ability to bring optical communications technologies from the MAN, LAN, into the data centers, to the curb, to the home and if possible, maybe someday directly to the microprocessor. However, the cost of these optical technologies is still relatively high compared with electrical or copper-based interconnects. The transition of optical to the mass market may only happen if one can bring data-com economics, high-volume manufacturing and assembly to the optical world.

Optical systems have become, to a large extent, more strongly linked with electronics. Moore's Law and new 90 nm fabrication technologies are enabling new electronic capabilities that add more intelligence and/or increased performance to optical systems. In addition, improved manufacturing and

packaging technologies are reducing assembly cost and producing new form factors that a few years ago were not possible. All these point to the possibility that "data-com" economical optical communication technologies may become a reality in the not-too-distant future.

In this issue of Intel Technology Journal, we discuss various optical activities within Intel, ranging from today's commercial optical transceiver products that combine leading-edge packaging and assembly technologies with advanced electronics to some much longer range research activities focused on bringing optical closer to and around the microprocessor. These optical activities could someday revolutionize the optical communications industry and bring the benefits of optical to the mass market and most importantly to the end user.

### **Technical Reviewers**

Bennett, Jeff, Intel Communications Group Dietrich, Casper, Intel Communications Group Dunning, Dave, Corporate Technology Group Epitaux, Marc, Intel Communications Group Finot, Marc, Intel Communications Group Hanberg, Jesper, Intel Communications Group Hutchinson, John, Technology and Manufacturing Group Karnik, Tanay, Corporate Technology Group Kikidis, John, Intel Communications Group Kirkpatrick, Peter, Intel Communications Group Kozlovsky, William J., Intel Communications Group Liu, Hai-Fang, Corporate Technology Group Nikonov, Dmitri, Technology and Manufacturing Group Paniccia, Mario, Corporate Technology Group Rao, Valluri, Technology and Manufacturing Group Vandentop, Gilroy, Technology and Manufacturing Group Webb, Clair, Technology and Manufacturing Group Williams, David, Technology and Manufacturing Group

#### THIS PAGE INTENTIONALLY LEFT BLANK

## Optical Technologies for Enterprise Networks

Pierre Herve, Intel Communications Group, Intel Corporation Shlomo Ovadia, Intel Communications Group, Intel Corporation

Index words: optical interconnects, 10 Gb/s transceivers, packaging, enterprise networks

#### ABSTRACT

Optical networking technologies have been over the last two decades reshaping the entire telecom infrastructure networks around the world. As network bandwidth requirements increase, optical communication and networking technologies have been moving from their telecom origin into the enterprise. For example, today in data centers, all storage area networking is based on fiber interconnects with speeds ranging form 1 Gb/s to 10 Gb/s. As the transmission bandwidth requirements increase and the costs of the emerging optical technologies become more economical, the adoption and acceptance of these optical interconnects within enterprise networks will increase. This paper, which provides the framework for the different optical interconnect technologies in this special optical issue of the Intel Technology Journal, is organized as follows. First, a brief overview of the fiber optics interconnects technology evolution and its current application within the enterprise, is presented. Second, various interconnect evolution paths, such as, board-to-board, chip-to-chip, and on-chip interconnects, are discussed.

#### INTRODUCTION

The birth of optical communications occurred in the 1970's with two key technology breakthroughs. The first was the invention of the semiconductor laser in 1962 [1]. The laser generates a tightly focused beam of light at a single pure wavelength, a spot small enough to be connected to fiber optics. The second breakthrough happened in September 1970, when a glass fiber with an attenuation of less than 20 dB/km was developed [2, 3]. In the 1960's, glass-clad fibers had an attenuation of about 1 dB/m, which was sufficient for medical imaging applications, but was too high for telecommunications. With the development of optical fibers with an attenuation of 20 dB/km, the threshold to make fiber optics a viable technology for telecommunications was crossed. In 1977, AT&T installed the first optical fiber cables in Chicago [3]. The first field deployments of fiber

communication systems used Multimode Fibers (MMFs) with lasers operating in the 850 nm wavelength band. These systems could transmit several kilometers with optical losses in the range of 2 to 3 dB/km. A second generation of lasers operating at 1310 nm enabled transmission in the "second window" of the optical fiber where the optical loss is about 0.5 dB/km in a Single-Mode-Fiber (SMF). In the 1980's, the telecom carriers started replacing all their MMFs operating at 850 nm. Another wavelength window around 1550 nm was developed where a standard SMF has its minimum optical loss of about 0.22 dB/km. The development of fiberbased telecommunication systems in the 1990's focused on increasing their transmission capacity. This was done first by increasing the signal modulation speed from 155 Mb/s to 622 Mb/s, to 2.5 Gps, and finally to 10 Gb/s, today's modulation speed. The total available bandwidth of standard optical fibers is enormous; it is about 20 THz. Since it is impossible for a single-wavelength laser to utilize this enormous bandwidth, multiple singlewavelength laser transmitters are typically multiplexed and transmitted on a single fiber. This scheme, which was developed in the mid 1990's, is called Wavelength-Division-Multiplexing (WDM) [4]. Dense WDM (DWDM) optical communication systems with more than 60 wavelengths, where each wavelength carries 40 Gb/s data, have been demonstrated [5]. Thus, the demonstrated total transmission capacity of an SMF is more than 2.5 Tb/s.

Today, MMFs operating at 850 nm are primarily used for short distances in the enterprise as the least expensive method. An SMF at the 1310 nm wavelength band is primarily used for medium distances ranging from 2 km to 40 km. For long-haul telecommunications, WDM systems operating in the 1550 nm wavelength band windows are deployed. From 850 nm to long wavelength and WDM, higher performance is being offered, but each one comes with a higher price tag. Nowadays, all the telecom infrastructure is fiber-based with the exception of the famous last miles to homes, which is still based on coaxial cables and copper-twisted pairs. Inside enterprise networks, fiber has been deployed since the early 1980's initially with supercomputers, and later in Local Area Networks (LANs) as well as more recently in Storage Area Networks (SANs). With continuously increasing demands for high-speed data, optical fibers and interconnects will continue to play an increasing role within the enterprise network.

In this paper, we first discuss the fundamentals of optical components for communication such as optical fibers, laser transmitters, and receivers. Second, we review the optical packaging trends for optical modules and optical transceivers. Then, after a review of the various optical interconnect topologies in the enterprise, we discuss their applications and cost trends. We then move on to discuss the next-generation optical interconnects dividing them into four main categories: box-to-box, board-to-board, chip-to-chip, and on-chip interconnects. Finally, the evolution of optical interconnects and technical challenges in enterprise networks are discussed.

## THE FUNDAMENTALS OF OPTICAL COMPONENTS

A basic optical communication link consists of three key building blocks: optical fiber, light sources, and light detectors. We discuss each one in turn.

#### **Optical Fibers**

In 1966, Charles Kao and George Hockmam predicted that purified glass loss could be reduced to below 20 dB per kilometer, and they set up a world-wide race to beat this prediction. In September 1970, Robert Maurer, Donald Keck, and Peter Schultz of Corning succeeded in developing a glass fiber with attenuation less than 20 dB/km: this was the necessary threshold to make fiber optics a viable transmission technology. The silica-based optical fiber structure consists of a cladding layer with a lower refractive index than the fiber core it surrounds. This refractive index difference causes a total internal reflection, which guides the propagating light through the fiber core. There are many types of optical fibers with different size cores and cladding. Some optical fibers are not even glass-based such as Plastic Optical Fibers (POFs). which are made for short-distance communication. For telecommunications, the fiber is glass based with two main categories: SMF and MMF. SMFs typically have a core diameter of about 9 µm while MMFs typically have a core diameter ranging from 50 to 62.5 µm. Optical fibers have two primary types of impairment, optical attenuation and dispersion. The fiber optical attenuation, which is mainly caused by absorption and the intrinsic Rayleigh scattering, is a wavelengthdependent

loss with optical losses as low as 0.2 dB/km around 1550 nm for conventional SMF (i.e., SMF-28<sup>\*</sup>) [6].

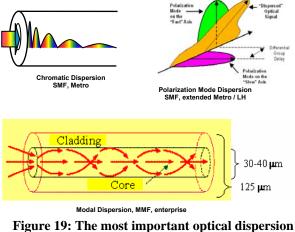

The optical fiber is a dispersive waveguide. The dispersion results in Inter Symbol Interference (ISI) at the receiver. There are three primary types of fiber dispersions: modal dispersion, chromatic dispersion, and polarization-mode dispersion. The fiber modal dispersion depends on both the fiber core diameter and transmitted wavelengths. For a single-mode transmission, the step-index fiber core diameter (D) must satisfy the following condition [2]:

$$D < \left[\frac{2.405 \cdot \lambda}{\pi}\right] \cdot \left(n_1^2 - n_2^2\right)^{-1/2}$$

where  $\lambda$  is the transmitted wavelength and  $n_1$  and  $n_2$  are the refractive indices of fiber core and cladding layer, respectively. Consequently, for a single-mode operation at 850 nm wavelength, the fiber must have a core diameter of 5 µm. Since a conventional SMF has typically a core diameter of 9 µm, single-mode operation can be only supported for wavelengths in the 1310 nm wavelength band or longer.

The fiber chromatic dispersion is due to the wavelengthdependent refractive index with a zero-dispersion wavelength occurring at 1310 nm in conventional SMF [6]. At 1550 nm, the fiber dispersion is about 17 ps/nm/km for SMF-28. When short duration optical pulses are launched into the fiber, they tend to broaden since different wavelengths propagate at different group velocities, due to the spectral width of the emitter. Optical transmission systems operating at rates of 10 Gb/s or higher and distances above 40 km are sensitive to this phenomenon. There are other types of SMFs such as Dispersion Shifted Fibers (DSFs) where the zero dispersion occurs at 1550 nm.

Polarization-Mode Dispersion (PMD) is caused by small amounts of asymmetry and stress in the fiber core due to the manufacturing process and environmental changes such as temperature and strains. This fiber core asymmetry and stress leads to a polarization-dependent index of refraction and propagation constant, thus limiting the transmission distance of high speed ( $\geq 10$  Gb/s) over SMF in optical communication systems. Standard SMF has a PMD value of less than 0.1 ps/ $\sqrt{km}$  [6]. Special SMFs were developed to address this issue.

<sup>\*</sup> All other trademarks are the property of their respective owners.

Optical fiber is never bare. The fiber is coated with a thin primary coating by the fiber manufacturer; then a cable manufacturer, not necessarily the fiber manufacturer, cables the fiber. There is a wide variety of cable construction. Simplex cable has a single fiber in the center while duplex cables contain two fibers. Composite cable incorporates both single-mode and multimode fiber. Hybrid cables incorporate mixed optical fiber and copper cable. In the enterprise, the MMF is housed in a cable with an orange colored jacket, and the SMF is housed in a yellow jacket cable.

#### **Light Sources**

The light source is often the most costly element of an optical communication system. It has the following key characteristics: (a) peak wavelength, at which the source emits most of its optical power, (b) spectral width, (c) output power, (d) threshold current, (e) light vs. current linearity, (f) and a spectral emission pattern. These characteristics are key to system performance.

There are two types of light sources in widespread use: the Laser Diode (LD) and the Light Emitting Diode (LEDs). All light emitters that convert electrical current into light are semiconductor based. They operate with the principle of the p-n semiconductor junction found in transistors. Historically, the first achievement of laser action in GaAs p-n junction was reported in 1962 by three groups [1-4]. Both LEDs and LDs use the same key materials: Gallium Aluminum Arsenide (GaAIAs) for short-wavelength devices and Indium Gallium Arsenide Phosphide (InGaAsP) for long-wavelength devices.

Semiconductor laser diode structures can be divided into the so-called edge-emitters, such as Fabry Perot (FP) and Distributed Feedback (DFB) lasers and vertical-emitters, such as Vertical Surface Emitting Lasers (VCSELs). When edge-emitters are used in optical fiber communication systems, they incorporate a rear facet photodiode to provide a means to monitor the laser output, as this output varies with temperature.

In today's optical networks, binary digital modulation is typically used, namely on (i.e., light on) and off (no light) to transmit data. These semiconductor laser devices generate output light intensity which is proportional to the current applied to them, therefore making them suitable for modulation to transmit data. Speed and linearity are therefore two important characteristics.

Modulation schemes can be divided into two main categories, namely, a direct and an external modulation. In a direct modulation scheme, modulation of the input current to the semiconductor laser directly modulates its output optical signal since the output optical power is proportional to the drive current. In an external modulation scheme, the semiconductor laser is operating in a Continuous-Wave (CW) mode at a fixed operating point. An electrical drive signal is applied to an optical modulator, which is external to the laser. Consequently, the applied drive signal modulates the laser output light on and off without affecting the laser operation.

One important feature of the laser diode is its frequency chirp. The frequency of the output laser light changes dynamically in response to the changes in the modulation current. A typical DFB has a frequency chirp of about 100-MHz/mA. This spread of the wavelength interacts with the fiber dispersion. As previously mentioned, as the data rate is increased, this interaction limits the transmission distance of optical transmission systems due to the additional ISI generated at the receiver [1–4].

Optical back-reflection is one of key issues when coupling the output light from a laser source to a fiber. The optical back-reflection disturbs the standing wave in the laser cavity, increasing its noise floor, and thus making the laser unstable. One practical way to reduce the phenomenon of back-reflection is to place an isolator between the laser cavity and the fiber, which adds a significant additional cost to the laser [1, 4]. Temperature also affects the peak wavelength of the laser; threshold current also increases with temperature as slope efficiency decreases. For DWDM applications, which require very precise operating wavelengths, most of the current laser diode designs need to be cooled to within  $\pm 0.3$  °C.

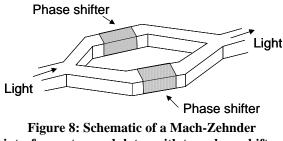

As previously explained, the direct modulation of a laser diode has several limitations, including limited propagation distance due to the interaction between the laser frequency chirp and fiber dispersion. This is not an issue for enterprise networks which are short distance, but could be a serious limiting factor for telecommunications applications. To overcome this limitation, the laser diode is operated in a CW mode, and output light is externally modulated by an optical modulator. Intensity modulators can be divided into two main groups: Mach-Zehnder Interferometer (MZI) and Electro-Absorption (EA) modulators. In an MZI modulator, a single input waveguide is split into two optical waveguides by a 3 dB Y junction and then recombined by a second 3 dB Y junction into a single output. A Radio Frequency (RF) signal, which is applied to a pair of electrodes constructed along the waveguides, modulates the propagating optical beam. The modulator key parameters are its modulation bandwidth, linearity, and the required drive signal voltage for  $\pi$  phase shift. MZI modulators based on LiNbO<sub>3</sub> are high-performance modulators with a large form-factor (about 2.5 inches) that are not suitable for optical integration [4, 7]. EA modulators are based on a voltageinduced shift of the semiconductor bandgap so that the modulator becomes absorbing for the lasing wavelength. The advantages of an EA modulator is its low driving voltage, high-speed operation, and suitability for optical integration with InP-based laser diodes [8].

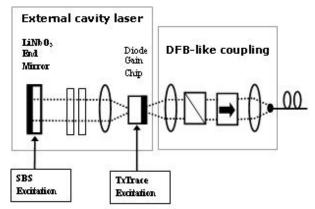

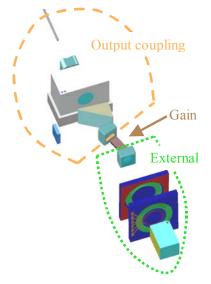

A tunable laser is a new type of laser where its main lasing longitudinal mode can be tuned over a wide range of wavelengths such as the C band (1510–1540 nm) of an Erbium-Doped Fiber Amplifier (EDFA), which is commonly used for DWDM systems [1–4]. The use of tunable lasers is driven by the potential cost savings in DWDM transport networks since a significantly reduced inventory of fixed-wavelength lasers could be maintained for a robust network operation. The technical challenges are to provide both broad wavelength tunability and excellent wavelength accuracy over the laser life. A broadly tunable External Cavity Laser (ECL) employing micromachined, thermally tuned silicon etalons has been designed to achieve these goals.

#### **Light Detectors**

Light detectors convert an optical signal to an electrical signal. The most common light detector is a photodiode. It operates on the principle of the p-n junction. There are two main categories of photodetectors: a p-i-n (positive, intrinsic, negative) photodiode and an Avalanche Photodiode (APD), which are typically made of InGaAs or germanium. The key parameters for photodiodes are (a) capacitance, (b) response time, (c) linearity, (d) noise, and (e) responsivity. The theoretical responsivity is 1.05 A/W at a wavelength of 1310 nm. Commercial photodiodes have responsivity around 0.8 to 0.9 A/W at the same wavelength [1-4]. The dark photo-current is a small current that flows through the photo-detector even though no light is present because of the intrinsic resistance of the photo-detector and the applied reverse voltage. It is temperature sensitive and contributes to noise. Since the output electrical current of a photodiode is typically in the range of  $\mu A$ , a Transimpedance Amplifier (TIA) is needed to amplify the electric current to a few mA [2-4].

APDs provide much more gain than the pin photodiodes, but they are much more expensive and require a high voltage power to supply their operation [2]. APDs are also more temperature sensitive than pin photodiodes.

#### PACKAGING: PACKAGING: OPTICAL SUB-ASSEMBLY (OSA) AND OPTICAL TRANSCEIVERS

As previously described, laser diodes and photodiodes are semiconductor devices. To enable the reliable operation of these devices, an optical package is required. In general, there are many discrete optical and electronic components, which are based on different technologies that must be optically aligned and integrated within the optical package. Optical packaging of laser diodes and photodiodes is the primary cost driver. These packages are sometimes called Optical Sub-Assemblies (OSAs). The Transmitter OSA package is called a TOSA and the Receiver OSA package is called a ROSA.

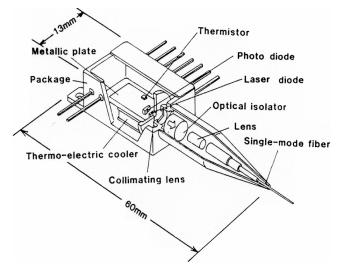

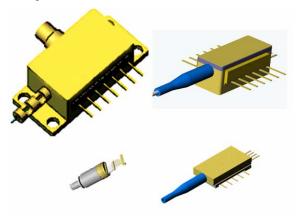

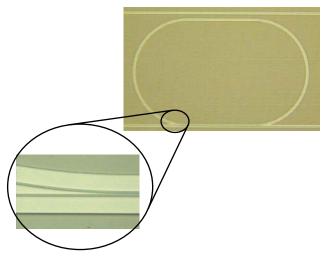

Figure 1 shows, for example, a three-dimensional schematic view of a DFB laser diode mounted on a Thermo-Electric Cooler (TEC) inside a hermetically sealed 14-pin butterfly package with an SMF pigtail [9]. Most of the telecom-grade laser diodes are available in the so-called TO can or butterfly packages. The standard butterfly package is a stable and high-performance package, but it has a relatively large form-factor and it is costly to manufacture. These packages are typically used for applications where cooling is required using a TEC [4].

#### Figure 1: Three-dimensional view of a DFB laser diode configuration with single-mode fiber pigtail (after Ref. [8] (© 1990 IEEE))

The TEC requires a large amount of power to regulate the temperature of a laser inside the package. This type of optical packaging was used for the early 10 Gb/s modules. More recently, tunable 10 Gb/s lasers are using a similar butterfly optical package. The butterfly package design uses a coaxial interface for passing broadband data into the package, which requires the use of a coaxial interface to the host Printed Circuit Board (PCB). Although coaxial cables and connectors have been reduced in size, they still consume valuable real estate in the optical transceiver.

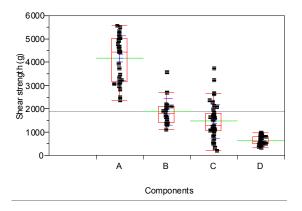

The evolution of optical module packages is toward smaller footprint packages. If relatively easy for receivers, the trend toward smaller packages is particularly challenging for laser transmitter modules due to the power and thermal dissipation constraints. Figure 2 shows the evolution of 10 Gb/s optical module packaging technology. To operate with high-performance, uncooled designs must be implemented with more advanced control systems that can adjust the laser and driver parameters over temperature. The smaller packages utilize a coplanar approach to the broadband interface, which more closely resembles a surface-mount component and enables much smaller RF interfaces.

TO-can-based designs, which have been used extensively in lower data rate telecom and datacom systems up to 2 Gb/s as well as CD players and other high-volume consumer applications, are now maturing to support highperformance 10 Gb/s optical links. Leveraging the fact that these packages are already produced in high volume will further reduce the cost of the 10 Gb/s optical modules in optical transceiver designs.

#### Figure 2: Trends in 10 Gb/s optical transmitter packaging technology. To decrease size and power dissipation, the trends are from cooled to uncooled packages, from coaxial to planar RF interfaces, and from pigtailed to pluggable optical interfaces.

The current TOSA/ROSA package form factors are trending toward smaller packages, and it will not end at the 10 Gb/s TO-can implementation. These TOSA/ROSA form factors are still too large and too expensive to compete in the market segment where today copper interconnects dominate. Leadframe-type packages could be an attractive choice for high-speed optical modules since similar packages are already in use in the semiconductor industry [10]. Using insert molded or prethermoplastic housing, different molded optical components can be passively aligned in a fully automated manufacturing process. For example, integrated modules with VCSEL and photodiodes in leadframe packages have been developed for the automobile industry, but are limited today in the 20 Mb/s bit rate. Additional research and development is needed to define the packaging specifications for optoelectronic modules based on size and cost.

#### **Optical Transceivers**

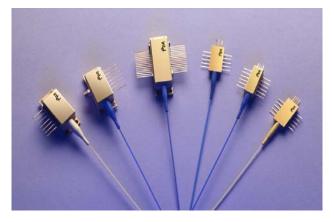

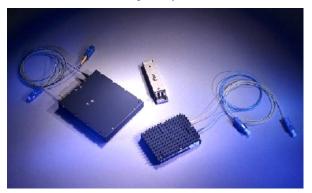

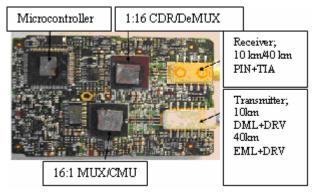

For telecommunication applications. the optical transmitter and receiver modules are usually packaged into a single package called an optical transceiver. Figure 3 shows an example of different transceivers and Figure 4 shows an example of the printed circuit board of a transceiver. There are several form factors for this optical transceiver depending on their operating speed and applications. The industry worked on a Multi-Source Agreement (MSA) document to define the properties of the optical transceivers in terms of their mechanical, optical, and electrical specifications. Optical transponders operating at 10 Gb/s, based on MSA, have been in the market since circa 2000, beginning with the 300-pin MSA, followed by XENPAK, XPAK, X2, and XFP. Table 1 summarizes the key MSA specifications for the different form-factor 10 Gb/s optical transceivers and their release dates.

## Which are the Most Popular Form-Factor Transceivers in the Enterprise?

For the 1/2/4 Gb/s transceivers, the Small Form-Factors (SFFs) and the small Form-Factor Pluggables (SFPs) are the most recently developed and the ones that are finding new sockets into systems. It should be noted, however, that the older GBIC form factors for 1 Gb/s Ethernet (GbE), despite no new development, is still shipping in large volumes due to the large installed base of this design. The SFF transceiver is used in a Network Interface Card (NIC) for the LAN or in the Host Bus Adaptor (HBA) in SANs. The SFP transceiver is typically used for enterprise switches such as Ethernet or Fiber-Channel (FC) switches. In these high-capacity switches, switching is done by electrical ICs while the optical transceivers provide optical-to-electrical electrical (O-E) or electrical-to-optical (E-O) conversion.

#### Figure 3: Next-generation 10 Gb/s enterprise optical transceivers: (from left) XFP, XPAK/X2, XENPAK. These modules are electrically hot-pluggable and optically pluggable.

In general, not all the switches' ports are populated with transceivers when they are shipped to customers. The customer has the option to buy these transceiver modules as the demand for ports increases. It also gives the customer the choice of optics: MMF or SMF. Therefore, these modules have been designed to be pluggable.

The choice between the different 10 Gb/s form-factor optical transceiver packages is guided by reach, cost, and thermal and size constraints and requirements.

## Table 1: Summary of different form-factor 10 Gb/s optical transceiver packages

| MSA               | XENPAK               | XPAK/X2                                | XFP                |  |

|-------------------|----------------------|----------------------------------------|--------------------|--|

| MSA Date          | March<br>2002        | March<br>2003                          | April<br>2003      |  |

| Application       | Enterprise<br>switch | Enterprise<br>switch<br>NIC<br>Storage | Telecom<br>Datacom |  |

| Electrical        | 4 bit                | 4 bit                                  | 1 bit              |  |

| Interface         | XAUI                 | XAUI                                   | XFI                |  |

| Optical interface | SC<br>pluggable      | SC or LC pluggable                     | LC<br>pluggable    |  |

| Dimension         | 4.8x1.4x0.<br>7      | 2.7x1.4x0.<br>4                        |                    |  |

| Max Power         | 11W                  | 5W                                     | 3W                 |  |

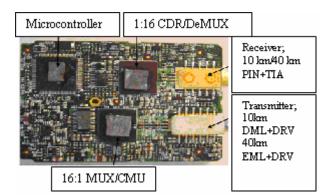

#### Figure 4: Intel<sup>®</sup> TXN13220 FR-4 printed circuit board showing optical modules, Mux/DeMux, and microprocessor

## OPTICAL TECHNOLOGY TRENDS IN THE ENTERPRISE

Enterprise network topology can be divided into four main categories: horizontal cabling, vertical cabling, data center interconnects, and campus backbone. Table 2 shows the use of various technologies in each of these topologies based on distance and speed. Within a data center, the LAN, which is based on the Ethernet protocol, is based mostly on copper interconnects operating at speeds of up to 1 Gb/s for all distances below 100 m. Some MMFs at 850 nm are also used at speeds of up to 10 Gb/s. However, within a SAN, which is based on the Fiber Channel (FC) protocol, only MMFs at 850 nm are used for transmission rates ranging form 1 Gb/s to 10 Gb/s. Optical interconnects based on SMFs at 1310 nm are typically used within a campus-size network with transmission distances up to 10 km and rates of up to 10 Gb/s. All the optical interconnects used in enterprise networks today are box-to-box connections typically between a server to a switch connection and a switch to a switch connection. The most popular optical modules are SSF and SFP form-factor modules operating at speeds of up to 4 Gb/s, while the 1 Gb/s GBIC for LAN is still shipping in volume. For the 10 Gb/s modules, the XENPAK is the most commonly used today within enterprise networks. However, the new optical module designs are trending towards smaller form-factor modules such as XPAK and XFP.

| Segment        | Distance | Speed                                               | Technology                      |

|----------------|----------|-----------------------------------------------------|---------------------------------|

| Horizontal     | 100 m    | 10/100/1000 Mb/s                                    | Copper                          |

| Vertical       | 300 m    | 10/100 Mb/s<br>1/10 Gb/s                            | Copper<br>MMF                   |

| Data<br>center | 100 m    | 10/100Mb/s<br>1Gb/s-10Gb/s<br>LAN<br>1/2/4 Gb/s SAN | Copper<br>Copper/MM<br>F<br>MMF |

| Campus         | 2-10 km  | 1- 10 Gb/s                                          | SMF                             |

Table 2: Used technology in each of the enterprise network topologies

In today's enterprise networks, copper-based interconnects dominate the box-to-box connections due to their cost advantage over comparable optical interconnects. For example, in the 1 Gb/s LAN (i.e., Ethernet-based) market, Dell'Oro in January 2004 was forecasting the shipment volume to grow from about a total of 13 million switch ports in 2003 to 158 million ports in 2008 [11]. Out of the total number of switch

ports, the number of 1 Gb/s copper-based interconnects is expected to grow from about 7 million in 2003 to about 141 million in 2008. This anticipated growth of copperbased interconnects is driven by the deployment of 1 Gb/s to the desktop. The average selling price of copper-based switch ports is \$181 in 2003. For the lowest cost segment of the copper-based 1 Gb/s switch port market, the average selling price is forecasted to decline from about \$59 to \$9 over the same period. In comparison, out of the total number of switch ports, the 1 Gb/s optical interconnects market is expected to grow from about 6 million ports in 2003 to 17 million ports in 2008 with the average selling price about \$416 in 2003 [11]. The market for the SAN, which is based on the FC protocol standard, is planned to transition from optical interconnects operating at 2 Gb/s to 4 Gb/s during the 2005-2006 period. The forecasted volume for the FC-based switch ports is expected to grow from 1.8 million of 2 Gb/s ports in 2003 to 6.4 million of 4 Gb/s ports in 2007, according to the IDC forecast published in August 2003 [12]. Over the past year, the average selling price of optical 10 GbE switch ports has been dropping from about \$30K to about \$10K per port today. The average selling price of these 10 GbE switch ports must be below \$3K per port for a wide deployment within enterprise networks.

#### NEXT-GENERATION OPTICAL INTERCONNECTS

In general, interconnects can be divided into four main categories: box-to-box, board-to-board, chip-to-chip, and on-chip interconnects. Today, optical interconnections in the enterprise are mostly used for the box-to-box interconnects. The optical transceivers are either plugged into high-capacity Ethernet or FC-based switches, or placed on a NIC/HBA, which are implemented into servers. Will optical interconnects move into the other categories? A brief overview of each optical interconnect category is provided in the next subsections.

#### **Board-to-Board Interconnects**

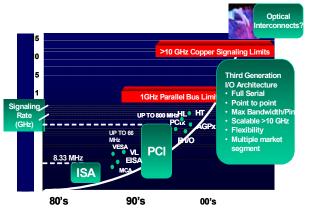

The move of the communications industry, both telecom and datacom toward a Modular Communication Platform (MCP) favors the deployment of bladed architecture. Functions that were traditionally housed in a standalone box, such as between servers and switches, have started to be implemented into a board-level form-factor, which is called a blade, and they plug into a common chassis. Therefore, interconnect opportunities at the board level are becoming more important. As the transmission speed increases, copper-based interconnects are facing technical challenges in terms of speed, reach, EMI, and routing.

Backplanes are potential applications for optical interconnects. These are point-to-point or point-to-

multipoint high-speed interconnects with typical lengths of under 1m. The key advantages of optical backplane interconnects are low-crosstalk among the optical signals, and their large bandwidth. However, most of today's optical backplanes are more like patch panels rather than replacements for backplanes. Many different optical technologies have been demonstrated including polymer waveguides integrated on Si, planar light wave circuit interconnects, and fiber ribbon arrays integrated with VCSELs and photodiodes. However, none of these optical technologies today have displaced copper interconnects outside of some niche applications. The transition to optical backplanes might be induced by the accumulating technical challenges of electrical interconnects. However to be widely adopted, optical interconnects must be able to advance toward a smaller form-factor with a lower power consumption at a lower cost. Meeting these requirements is critical to the technology evolution of optical interconnects from boxto-box to board-to-board to chip-to-chip. Several new technical breakthroughs will need to occur in order to meet these challenging requirements.

#### **Chip-to-Chip Interconnects**

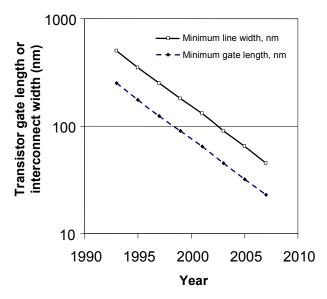

Extrapolation of Moore's law shows that microprocessors are expected to be clocked at about 10 GHz by the end of the decade [13, 14]. Consequently, it is becoming extremely difficult to route enough bandwidth through a PCB or a module using the existing electrical wires. It has been shown that frequency-dependent loss for copper traces on FR4 circuit boards rapidly rises above 1 GHz, reducing the Signal-to-Noise Ratio (SNR) and introducing timing errors. In addition, the resultant highfrequency crosstalk among the different copper traces limits the wiring density on the circuit board. High-speed short-distance (L < 10 cm) chip-to-chip optical interconnects have several advantages over copper interconnects. Optical interconnects are low-loss interconnects with a large transmission bandwidth. Another key advantage is their inherent immunity to Electro-Magnetic Interference (EMI). The density of copper traces on FR4 boards is constrained by these EMI and electrical crosstalk problems. Over the last 20 years, many different optical technologies were demonstrated to overcome the electrical bottleneck [14, 15]. However, their relative high costs due to implementation complexity and use of exotic materials made them unsuitable for high-volume manufacturing and thus prevented the adoption of these technologies.

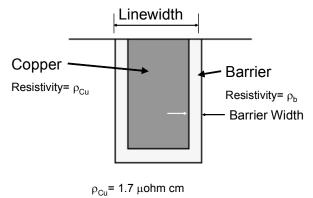

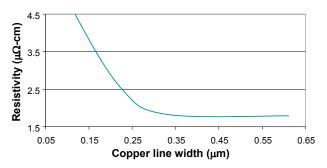

#### **On-Chip Interconnects**

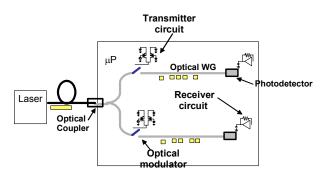

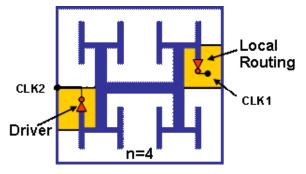

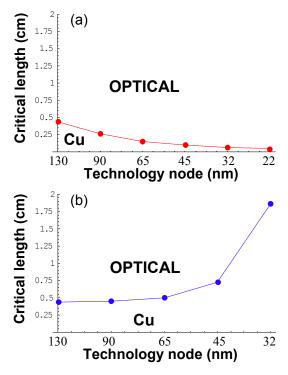

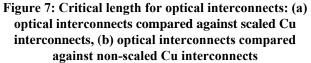

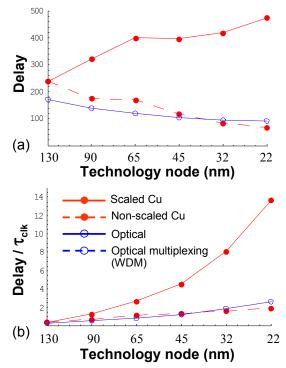

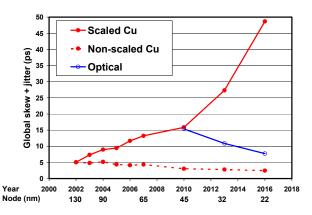

The design of on-chip electrical interconnects is becoming increasingly difficult given the continuous growth in the complexity of integrated circuits operating at multi-GHz. Can on-chip optical interconnects potentially solve these issues? On-chip point-to-point and point-to-multipoint optical interconnects with typical lengths under 1 cm are potentially attractive because of the following reasons: (a) they decrease the existing electrical interconnect delays, (b) provide a higher bandwidth to keep pace with the speed of transistors, (c) reduce electrical power consumption, and (d) minimize sensitivity to EMI. The potential primary application of on-chip optical interconnects in microprocessors, for example, are in high-speed signaling and clock distribution. For on-chip signal distribution, four key benchmark parameters are typically used: signal delay normalized by clock cycle, available bandwidth per unit area or bandwidth density, bandwidth density/delay ratio, and cost. For on-chip clock distribution, the critical parameters are timing, skew, and jitter. The primary challenges for implementing these optical interconnects is the integration of multiple VCSEL and photodiode arrays with their corresponding drivers and TIAs, and on-chip light coupling into optical waveguide arrays over the entire chip. Currently, such optoelectronic integration is not only in its early stages of development, but it is also very expensive relative to copper-based interconnects with limited or no performance advantages. In order to take advantage of on-chip optical interconnects, today's microprocessor architecture might need to evolve from a single superscalar chip to a mesh of optically interconnected processors with their associated memories. The WDM scheme could be used, for example, to send multiple wavelengths in the same optical waveguide to significantly increase the overall communication bandwidth.

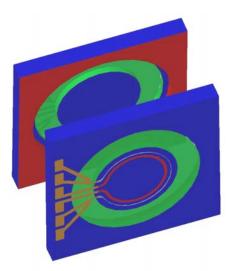

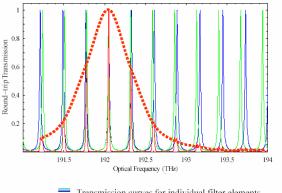

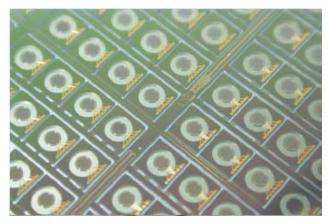

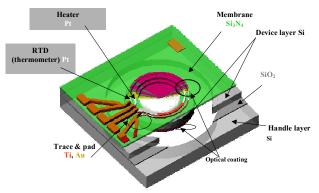

#### **Silicon-Based Optical Interconnects**

In order to enable the chip-to-chip or on-chip optical interconnects, silicon-based optical components should be developed. As previously noted, optical components such as tunable WDM filters, photodiodes, optical waveguides, and electronic components such as laser drivers and TIA circuits are all based on different materials and technologies precluding them from an optoelectronic monolithic integration. The attractiveness of silicon-based optical interconnects is the potential integration with integrated circuits CMOS for high-volume manufacturing. The first prototype of such silicon-based optical components includes thermally tunable WDM Bragg filters, high-speed optical MZI modulators and a Si/Ge high-speed photodiode [16].

A narrow-band Bragg grating filter has been made in silicon waveguides with alternating polycrystalline/crystalline layers. The Bragg grating reflects only the wavelengths that satisfies the Bragg condition [1-4]

$$\lambda_{\rm B} = 2n \cdot \Lambda / m$$

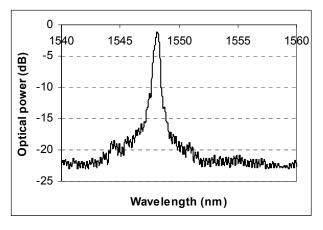

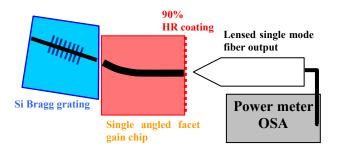

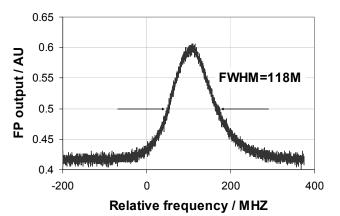

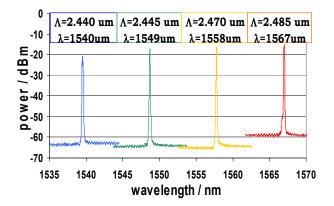

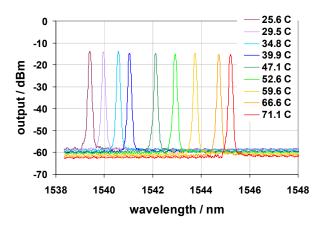

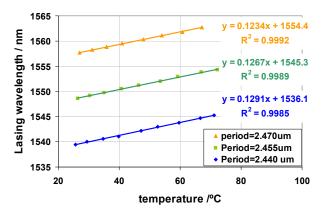

where n = 3.46 in the effective refractive index of the silicon waveguide,  $\Lambda = 2.445 \mu m$  is the Bragg grating pitch, and m = 11 is the Bragg grating order. Using the strong thermo-optics effect in silicon, these Bragg grating filters can be made tunable [17]. Such WDM Bragg grating filters with a 3-dB bandwidth of 100 GHz and 200 GHz, insertion loss of about 4 dB and tunability over 12 nm for 100 °C temperature variation were demonstrated. These tunable Bragg filters can be used as channel filters in a low-cost WDM communication system.

Silicon-on-Insulator (SOI) optical modulators based on current injection had a modulation bandwidth of only 20 MHz. Consequently, these devices were not suitable for today's high-speed communication networks.

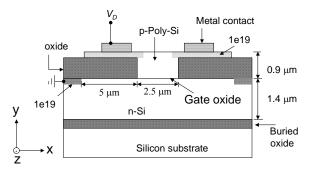

Recently, an MZI silicon optical modulator with a modulation bandwidth of 2.5 GHz around 1550 nm was demonstrated [18]. The high-speed operation was achieved by using a novel phase shifter design based on a Metal-Oxide-Semiconductor (MOS) capacitor embedded in a passive silicon waveguide with doped and undoped polysilicon regions in MZI configuration. The accumulated charges in the MOS capacitor induce fast refractive index changes in the silicon waveguide due to the free carrier plasma dispersion effect [19]. The 1.5 cm long silicon MZI modulator had an extinction ratio of more than 16 dB with an applied peak-to-peak voltage of about 7.7 volts.

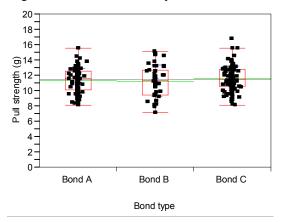

Figure 5: Future vision of hybrid optical integration of a four-channel WDM optical transceiver with silicon photonic components and conventional CMOS drivers

However, the demonstrated modulator had a total of 12 dB insertion loss, which can potentially be reduced to about 4–5 dB if the polysilicon is replaced with a singlecrystal silicon and tapered waveguides are used to efficiently couple the light in and out of the modulator through a diabatic transformation of the optical mode. The development of tapered waveguide technology for this high-index contrast optical system is one of the key challenges to developing a hybrid integration of these devices.

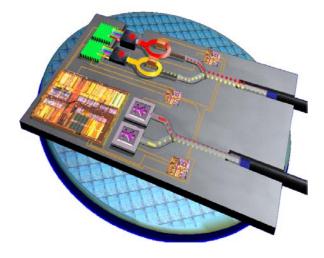

Such SOI-based modulators and Bragg filters can lead to an integrated optical transceiver module on a single die, combining multiple wavelength sources, modulators, and WDM multiplexer/de-multiplexers with the corresponding drive electronics. This concept is illustrated through an artist vision in Figure 5 which shows a hybrid integration of a four-channel WDM optical transceiver with silicon photonic components such as modulators, filters, and multiplexer/de-multiplexers and conventional CMOS-based drivers on the same silicon die.

## TECHNICAL CHALLENGES AND CONCLUSION

The costs of high-speed optical interconnects has been reduced by more than an order of magnitude while their performance has been significantly improved over the last five years. Tremendous progress has been made in the development of cost-effective packaging technologies for optical modules operating at transmission rates up to 10 Gb/s. Four different MSA form-factor packages for 10 Gb/s optical transceivers in enterprise networks, namely, XENPAK, XPAK, X2, and XFP have been created, trending toward smaller form factors. In the meantime, the SFF and SFP, which are the smallest form-factor modules on the market, are trending to higher speed capabilities from 1/2 Gb/s today toward 4 Gb/s. In today's enterprise networks, the optical transceivers are used for box-to-box connections. The optical transceivers are either plugged into high-capacity Ethernet or FC-based switches, or placed on a NIC/HBA, which are plugged into servers. In terms of volume shipped, copper-based interconnects dominate the box-to-box connections due to their cost advantage over comparable optical interconnects until at least 2008. However, the number of either Ethernet-based or FC-based server-to-switch and switch-to-switch optical interconnects is expected to grow in the coming years.

To be widely adopted, optical interconnects must be able to advance toward a smaller form-factor with a lower power consumption at a lower cost. Meeting these requirements is critical to the technology evolution of optical interconnects from box-to-box to board-to-board, to chip-to-chip. Several new technology breakthroughs will need to occur in order to meet these challenging requirements.

#### ACKNOWLEDGMENTS

The authors would like to thank Dr. Mario Paniccia for technical discussions and support. Pierre would like to acknowledge Pete Kirkpatrick, Marc Epitaux, Eric Zbinden, Mark Finot, Marc Verdiell, and Jeff Bennett for their technical support.

#### REFERENCES

- Agrawal, G. P., and Dutta, N. K., *Long-Wavelength* Semiconductor Lasers, Van Nostrand Reinhold, New York, 1986.

- [2] Agrawal, G. P., Fiber-Optic Communication Systems, John Wiley & Sons, New York, 1997.

- [3] Goff, R., *Fiber Optics Reference Guide*, Focal Press, Third Edition, 2002.

- [4] Ovadia, S., Broadband Cable TV Access Networks: From Technologies to Applications, Prentice Hall PTR, Upper Saddle River, NJ, 2001.

- [5] Suzuki, M., and Otani, T., "High-Speed (40–160 Gb/s) WDM Transmission in Terrestrial Networks," 2003 OFC Technical Digest, pp. 741–742, paper FN1.

- [6] Corning SMF-28<sup>™</sup> Optical Fiber Product Information (2002).

- [7] Wooten, E. L., "A Review of Lithium Niobate Modulators for Fiber-Optic Communications Systems," *IEEE Journal on Selected Topics in Quantum Electronics* 6, pp. 69–82, 2000.

- [8] Ido, T. et al., "Ultra-High-Speed Multiple-Quantum-Well Electro-Absorption Optical Modulators with Integrated Waveguides," *IEEE Journal of Lightwave Technology* 14, pp. 2026–2034, 1996.

- [9] Takemoto, A., Watanabe, H., Nakajima, Y., Sakakibara, Y., Kakimoto, S., Yamashita, J., Hatta, T., and Miyake, Y., "Distributed Feedback Laser Diode and Module for CATV Systems," *IEEE Journal of Selected Areas in Communications* 8, 1359–1364, 1990.

- [10] Longford, A., and Radloff, B., "The Use of Pre-Molded Leadframe Cavity Package Technologies in Photonic and RF Applications," 27<sup>th</sup> Annual IEEE/SEMICON conference proceedings, 348–352, July 17–18 (2002).

- [11] Dell'Oro Group Ethernet Switch 5-Year Forecast, January 2004.

- [12] IDC Worldwide Fibre Channel Hub and Switch Forecast and Analysis, 2003-2007 Aug. 2003, Doc #29882 Study

- [13] Huang, D., Sze T., Landin A., Lytel R., Davidson, H. L., "Optical Interconnects: Out of the Box Forever?," *IEEE J. of Selected Topics in Quantum Electronics* 9, 614–623, 2003.

- [14] Collet, J. H., Caignet, F., and Litaize, D.,

"Performance Constraints for Onchip Optical Interconnects," *IEEE Journal of Selected Topics in Quantum Electronics* 9, 425–432, 2003.

- [15] Goodman, J. W., Leonberger, F. J., Kung, S.-Y., and Athale, R. A., "Optical Interconnects for VLSI Systems," *Proceedings of IEEE* 72, 850–866, 1984.

- [16] Colace, L., Masini, G., and Assanto, G., "Ge-on-Si Approaches to the Detection of near-Infrared Light," *IEEE Journal of Quantum Electronics* 35, 1843–1852 (1999).

- [17] Soref, R. A., "Silicon-based Optoelectronics," *Proceedings of IEEE* 81, 1687–1706, 1993.

- [18] Liu, A., Jones, R., Liao L., Samara-Rubio D., Rubin, D., Choen O., Nicolaescu R., and Paniccia M., "High-Speed Silicon Optical Modulator Based on a Metal-Oxide-Semiconductor Capacitor," *Nature* 427, 615–618, 2004.

- [19] Soref, R. A., and Bennett, B. R., "Electro optical effects in Silicon," *IEEE Journal of Quantum Electronics* 23, 123-129, 1987.

#### **AUTHORS' BIOGRAPHIES**

**Pierre Herve** is currently director of Enterprise Strategic Planning at Intel in the Communication Infrastructure Group. He has been with Intel since 1996 and has held various marketing positions including director of optical strategy, wireless senior marketing manager, and CATV product manager. Before joining Intel, Pierre managed an online services provider based in Northern California for five years. He graduated with a M.S. degree in Telecommunications from the Institut National des Telecommunications in 1988. His email is pierre.m.herve at intel.com.

**Shlomo Ovadia** received a Ph.D. degree in Optical Sciences from the Optical Sciences Center, University of Arizona in 1984. After two years as a postdoctoral fellow at the University of Maryland, Shlomo held various technical positions at IBM, Bellcore, and General Instruments. In 2000, Shlomo joined Intel in San Jose, California, as principal architect in CTG, where he was leading the effort on the architecture, design, and development of optical burst switching in enterprise networks. Currently at Intel Communication Group, Shlomo is responsible for WiMAX interoperability and certification for IEEE 802.16d/e wireless modems. He is the author of a recently published book titled *Broadband Cable TV Access Networks: From Technologies to Applications* (Prentice Hall, 2001). He is a Senior Member of IEEE/LEOS/COMSOC with more than 70 technical publications and conference presentations. He is the holder of 35 patents, and his personal biography is included in the Millennium edition of Who's Who in Science and Engineering (2000/2001). His email is shlomo.ovadia at intel.com.

Copyright © Intel Corporation 2004. This publication was downloaded from <u>http://developer.intel.com/</u>.

#### Legal notices at

http://www.intel.com/sites/corporate/tradmarx.htm.

## 10 Gb/s Optical Transceivers: Fundamentals and Emerging Technologies

Peter Kirkpatrick, Intel Communications Group, Intel Corporation Wei-chiao Fang, Intel Communications Group, Intel Corporation Henrik Johansen, Intel Communications Group, Intel Corporation Benny Christensen, Intel Communications Group, Intel Corporation Jesper Hanberg, Intel Communications Group, Intel Corporation Martin Lobel, Intel Communications Group, Intel Corporation Tom Mader, Intel Communications Group, Intel Corporation Song Shang, Intel Communications Group, Intel Corporation Craig Schulz, Intel Communications Group, Intel Corporation Doug Sprock, Intel Communications Group, Intel Corporation Marc Verdiell, Intel Communications Group, Intel Corporation

Index words: fiber optics, optical transceiver, 10 Gb/s, Dense Wavelength Division Multiplexing (DWDM), tunable laser, Electronic Dispersion Compensation (EDC)

#### ABSTRACT

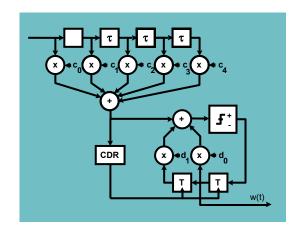

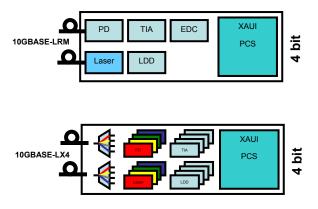

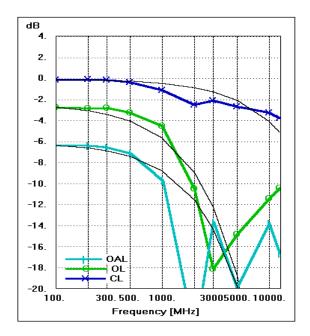

Continued demand for higher bandwidth in data networks along with an industry need for standardized network components has driven the need for 10 Gb/s optical transceivers into the long haul, metro core, and enterprise/storage environments. In response to this demand, the functionality and performance of these modules have increased significantly, while the size, cost, and power consumption have been dramatically reduced. While each transceiver application has unique systemlevel requirements, performance criteria, and cost sensitivities, the structure of each transceiver is much the same. This paper presents a discussion of the basic transceiver architecture including analog and digital electronic ICs and process choices, optical components and packaging, and control, monitoring, and interface circuitry. With each component, the critical performance criteria and cost-reduction opportunities are highlighted. More detail is presented on a full C-band wavelength tunable long-haul optical transceiver for Dense Wavelength Division Multiplexed (DWDM) systems, including the DWDM system requirements and design issues that arise in amplified, high-power, multi-channel links. The functionality and performance of a tunable 10 Gb/s transceiver are explored in more depth with a focus on transmitter and receiver front-end design. Finally, an application of Electronic Dispersion Compensation

(EDC) is presented, and we show how it can be used to compensate for fiber limitations to enable extended 10 Gb/s links over modal bandwidth limited legacy multimode fiber in enterprise systems.

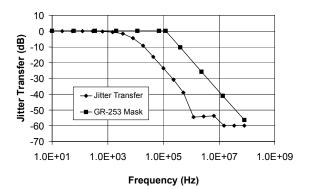

Figure 1: 10 Gb/s optical transceivers for DWDM line side and metro client-side interfaces. Pictured from the left are the 300-pin, XFP, and small form factor 300-pin MSA modules.

#### INTRODUCTION

Optical transceivers operating at line rates of 10 Gb/s have matured rapidly over the last few years and are currently available in a wide variety of form factors, each addressing a range of link parameters and protocols. These form factors are the result of Multi-Source Agreements (MSAs) that define common mechanical dimensions and electrical interfaces. The first MSA was the 300-pin MSA in 2000, followed by XENPAK, X2/XPAK, and XFP. Each of the transceivers defined by the MSAs have unique advantages that fit the needs of various systems, supporting different protocols, fiber reaches, and power dissipation levels. Figures 1 and 2 show 10 Gb/s transceivers for client-side telecom and enterprise interfaces, respectively. As the underlying technologies have matured, the optical and electrical performance of these modules has been significantly improved, while the power dissipation and cost have been reduced dramatically.

Figure 2: 10 Gb/s optical transceivers for enterprise interfaces. Pictured from the left are the XFP, X2/XPAK, and XENPAK MSAs.

In the architecture section of this paper, the basic architecture of all 10 Gb/s transceivers is presented, highlighting the functionality and critical performance parameters of each functional block. Design considerations such as IC process and optical packaging technologies are also discussed.

In the DWDM section, details on the design challenges and performance of a 10 Gb/s full C-band wavelength tunable optical transceiver are presented. Issues that arise in amplified, high-power, multi-channel links are discussed in terms of design choices and performance criteria.

Finally, the fundamentals of Electronic Dispersion Compensation (EDC) are presented, which uses adaptive electrical filtering techniques to compensate for limitations incurred during fiber propagation. The application of EDC to the problem of extending 10 Gb/s links using 1310 nm directly modulated lasers over lowbandwidth Multi-Mode Fiber (MMF) is explored in more detail.

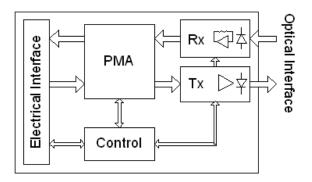

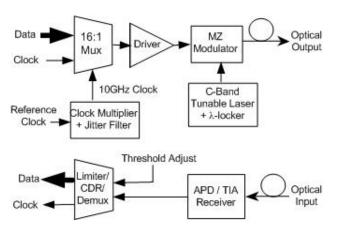

#### **10 GB/S TRANSCEIVER ARCHITECTURE**

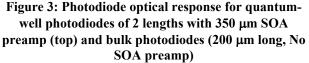

The basic architecture and interconnection between components in a 10 Gb/s optical transceiver are shown in Figure 3. This basic architecture holds for all of the 10 Gb/s transceiver Multi-Source Agreements (MSAs), independent of form factor, electrical interface, or fiber reach. Figure 4 shows the actual printed circuit board from a small form factor 300-pin MSA transceiver.

#### **Electrical Interface**

The electrical interface provides input/output data transfer to the host card, various clocking channels, control and monitoring channels, as well as DC power and ground connections. This interface can take the form of a socket that plugs perpendicularly into the plane of the host board, as in the 300-pin MSA [1], or it can take the form of a board-edge connection that mates to a socket in the plane of the host board. The latter is the case for XENPAK [2], X2/XPAK [3,4], and XFP [5], which provide front-panel pluggability at the host system level. Along with this benefit comes the added requirement of hot-pluggability and inrush current management.

The width of the data bus varies between the different MSAs. The first to emerge was the XSBI (based on SFI-4) interface of the 300-pin MSA, with 16-bit differential buses for input and output data [6]. Each I/O channel transmits or receives data at 1/16 the line rate (e.g., 622.080 Mb/s with a SONET line rate of 9.953 Gb/s). The XAUI interface on XENPAK and X2/XPAK provides a 4-bit differential bus. In this interface, each channel operates at 3.125 Gb/s, for a total bandwidth of 12.5 Gb/s. Multiple encoding/decoding steps on the XAUI signals result in the Ethernet line rate of 10.3125 Gb/s, which we discuss further in the Physical Medium Attachment (PMA) section. Finally, for XFP, the XFI interface provides a 1-bit differential signal at the line rate, providing a truly protocol-independent interface for 10 Gb/s communication.

Clocking schemes vary between the different interfaces. The clocking used in SFI-4 systems can vary, but generally a synchronous clock (1/16 or 1/64 of the line rate) is provided with the input data, and a reference clock is provided to keep the receiver Clock and Data Recovery (CDR) within locking range of the input data rate. The clock recovered by the receiver CDR is provided along with the output data. In XAUI and XFP transceivers, the host board simply provides a reference clock to keep the CDRs in the module within locking range of the data rate.

The electrical interface also provides DC connections to the host board DC power supplies. Care must be taken to minimize power dissipation given the different voltage and current levels available in various system designs.

#### **Control System**

The control systems in modern 10 Gb/s transceivers are generally implemented using a microcontroller. This device performs many functions that previously had been implemented using analog hardware. The controller sets control parameters for the Physical Medium Attachment (PMA), transmitter, and receiver, which may vary over time and temperature or when the host system changes the link configuration (i.e., loopback modes). The controller also provides a two-wire interface such as I<sup>2</sup>C so the host board can set control parameters and read the status registers where monitor values are stored.

#### **Physical Medium Attachment**

The core electrical functionality of a 10 Gb/s transceiver is contained in the PMA device. Transceivers at lower data rates generally do not include this functionality, because maintaining robust signal integrity is not as difficult at lower speeds. PMA devices take the form of clock multiplier/multiplexer (MUX/CMU) and clock and data recovery/demultiplexer (CDR/DeMUX) in the 300pin modules. The MUX/CMU interleaves the 16-channel

data bus into a serialized data stream at the line rate, clocked by a multiplied version of the input clock. This data stream is used to modulate the optical transmitter. CDR/DeMUX provides the complementary The functionality on the receive side. For the two types of PMA, there are a wide range of features and performance parameters that are critical to system-level quality. Here, we focus on the basic functionality and jitter characteristics. The PMA output waveform quality has a large impact on optical transmit eye quality, and PMA sensitivity has a large impact on optical receive The system-level impacts of these sensitivity. characteristics are covered in the optical device section below.

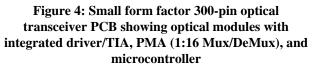

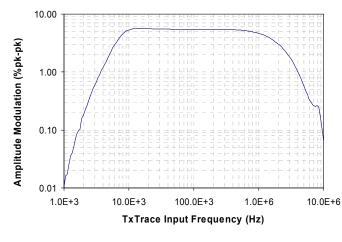

#### Figure 5: Jitter tolerance performance of a typical 300-pin small form factor 40 km transceiver. Note the stepped mask indicating the specification limit.

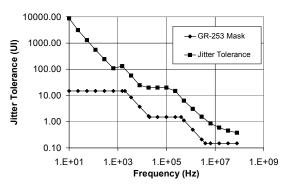

In SONET systems [7], jitter performance is critical to maintaining error-free performance over links involving several network elements [8]. There are three jitter parameters of interest in these systems: transmitter jitter generation, receiver jitter tolerance, and receive-totransmit jitter transfer. For all SONET network elements, the jitter generation must have significant margin on the specification limit of 100 mUIpp (UI denotes a unit interval, or one bit period), ideally 50 mUIpp. For a receiver, robust jitter tolerance is critical to performance of the network. This is the amount of sinusoidal jitter that causes a 1 dB penalty in the sensitivity of the receiver. Figure 5 shows the worst-case jitter tolerance performance of the 300-pin small form factor transceiver along with the specification mask. When a transceiver is used as a simple repeater, the jitter transfer characteristic is also important to network reliability. This is the amount of jitter transmitted at a specific frequency given a specified level of jitter into the transceiver. The worstcase jitter transfer performance of a 300-pin small form factor transceiver is shown in Figure 6. The peaking is less than 0.1 dB at low frequencies, and at higher frequencies the transfer rolls off to stay below the specification limit.

#### Figure 6: Jitter transfer performance of a typical 300pin small form factor 40 km transceiver. The specification limit is indicated on the plot.

Although Ethernet standards do not specifically define jitter parameters, the jitter generation and tolerance of these devices are still critical in Ethernet systems [9]. Jitter generation has an impact on the Transmitter and Dispersion Penalty (TDP), where the transmission performance over a fiber link of a device under test is compared with a reference transmitter. Any degradations due to waveform imperfections or jitter generation add to this penalty. Jitter tolerance has an impact in the Stressed Receive Sensitivity (SRS) test, where receiver sensitivity is measured with an eye that contains stress from sinusoidal jitter, as well as filtering and vertical sinusoidal closure. The TDP and SRS performance of a 40 km XENPAK transceiver is shown in Table 1. As 300-pin modules are often used in Ethernet systems, the TDP and SRS performance of the 40 km 300-pin small form factor module is shown for comparison.

Table 1: 10 Gb/s Ethernet 40 km (10GBASE-L) optical transceiver performance

| Spe | CIFICATION | 300-ріл 40 км XENPA |        | К 40 км     |        |

|-----|------------|---------------------|--------|-------------|--------|

|     |            | Performance         | Margin | Performance | Margin |

| SRS | <-11.3 dBm | -15.1 dBm           | 3.8 dB | -15.4 dBm   | 4.2 dB |

| TDP | < 3  dB    | 0.6 dB              | 2.4 dB | 1.1 dB      | 1.9 dB |

Data is worst-case performance over temperature (-5..70°C) and power supply variation ( $\pm 10\%$ ).

The XAUI PMA used in Ethernet and Fiber Channel systems also has MUX/CMU and CDR/DeMUX functionality for the 4-lane interface. The definition of the XAUI interface provides the additional benefits of individual CDRs on each lane as well as several bits of deskew functionality to provide robustness to layout and routing issues. The architecture also defines encoding and decoding overhead to the interface, to provide error detection, link status, and DC balance. On the 4-lane side,

each lane operates at a line rate of 3.125 Gb/s, for an aggregate bit rate of 12.5 Gb/s. The 8B/10B coding on this interface provides DC balance at a 25% overhead, for an actual datarate of 10 Gb/s. The signal is then scrambled, and 64B/66B coding is used to add link status, line/block coding, and scrambler synchronization on the optical interface, bringing the serial line rate to 10.3125 Gb/s.

For XFP transceivers, the PMA consists of simple CDRs for both the transmit and receive paths. As these modules work in both SONET and Ethernet systems, all of the performance parameters above apply. They must provide robust SONET jitter performance as well as TDP and SRS. This is particularly difficult in SONET systems as the output of an XFP transmitter must meet the 100 mUIpp jitter generation spec, while the chip providing the data signal to the XFP unit is allowed to have 50 mUIpp of jitter.

#### **Optical Devices and Physical Medium Dependent ICs**

Depending on the reach requirements of a fiber link, different optical transmit and receive devices are required. Although there are alternative devices and technologies emerging, devices that are technically established and available in the market are discussed here.

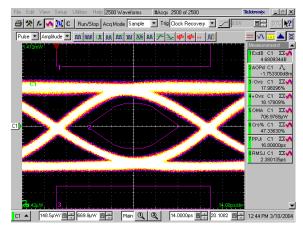

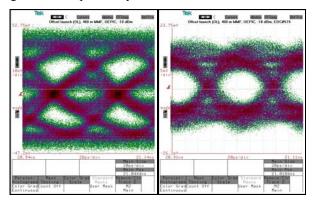

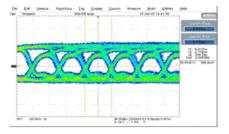

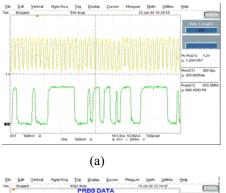

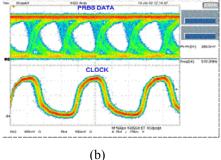

Figure 7: 850 nm multimode VCSEL optical eye diagram at 10 Gb/s from an XFP module

For Very Short Reach (VSR) applications in the enterprise space, such as within-building or withincampus LAN and SAN connections where multimode fiber (MMF; 50 or 62.5  $\mu$ m core diameter) is present, 850 nm GaAs/AlGaAs Vertical Cavity Surface Emitting Laser (VCSEL) transmitters and GaAs pin photodetector-based receivers are sufficient for 10 Gb/s on links of 25 to 300 m, depending on fiber quality. The low drive current and high efficiency of a VCSEL enable a transceiver with very low power dissipation. As the drive current and voltages are low, generally less than 20 mApp, a low-power CMOS driver can be used for direct modulation of the VCSEL current. The bias current and driver swing may be controlled over temperature to compensate for changes in the characteristics of the device in uncooled operations. As these devices are only used in Ethernet links, they are generally operated at lower extinction ratios (> 3.5 dB). A typical 850 nm VCSEL transmit eye diagram is shown in Figure 7.

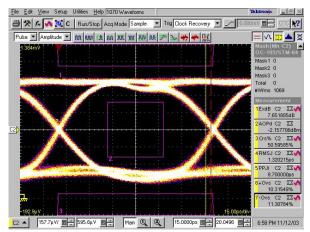

Figure 8: 1310 nm directly modulated DFB optical eye diagram at 10 Gb/s from small form factor 300-pin 10 km module

For Longer Reach (LR) links (7-20 km), a single-mode fiber (SMF; 9  $\mu$ m core diameter) is required, along with an InP-based single-mode Distributed Feedback Laser (DFB) operating at 1310 nm. This wavelength is chosen to match an operating region in the fiber that has close to zero chromatic dispersion (an impairment which otherwise causes pulses to expand during propagation). To satisfy SONET extinction ratio specifications (> 6 dB), a DFB has higher current swing requirements than a VCSEL, which drives the need for higher current GaAs or SiGe drivers, lower impedance (25  $\Omega$ ) interfaces, and alternative modulation schemes to save power, improve yields, and lower cost. Care must be taken to compensate for temperature variations in uncooled formats. A typical 1310 nm, 10 km DFB eye diagram is shown in Figure 8.

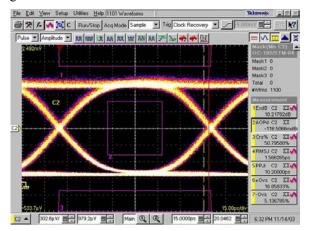

For metro area network access, Extended Reach (ER) links (40-80 km) may be used over SMF. These links are traditionally addressed by using externally modulated lasers, or EMLs, at 1550 nm. These devices, which monolithically combine a DFB laser with an Electro-Absorption Modulator (EAM) on an InP substrate, can be tuned to operate with low chirp (change of wavelength under modulation) to enable extended propagation in the low attenuation but higher dispersion 1550 nm window. These devices are generally modulated with GaAs or SiGe drivers to provide ample voltage swing and offset to achieve high extinction ratios (> 9 dB) and high-quality eye diagrams. EMLs are operated in controlled temperature environments to ensure performance, the cost

of which is increased power dissipation from the Thermo-Electric Cooling (TEC) element and control circuit. A typical 1550 nm, 40 km EML eye diagram is shown in Figure 9.

Figure 9: Small form factor 300-pin 40 km module 1550 nm optical eye diagram at 10 Gb/s

This type of eye quality must be achieved without sacrificing dispersion penalty performance, or difference between back-to-back sensitivity and post-dispersion sensitivity. High-quality 40-80 km transmit modules have low-dispersion penalty (< 1 dB).

#### **Optical Receivers**

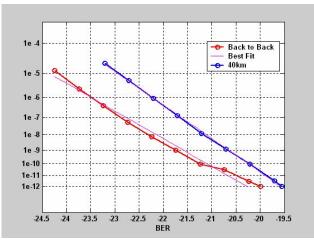

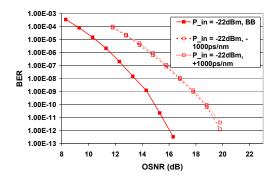

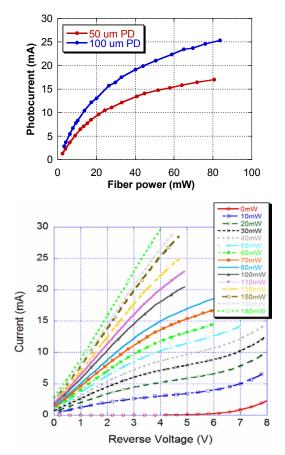

Receivers for 10 Gb/s links are based on two types of optoelectronic devices, InP or GaAs PIN (Positive-Intrinsic-Negative doped structure) photodiodes or InP Avalanche Photodiodes (APD) that convert light into electrical current. The fundamental performance criteria for a receiver is its optical sensitivity, which is the optical power required to maintain a link Bit Error Rate (BER) of 10<sup>-12</sup>. A typical sensitivity curve is shown in Figure 10.

#### Figure 10: Sensitivity curves from a typical 300-pin small form factor transceiver. The BER is plotted in error function space to yield a straight line.

At these data rates, receivers integrate Transimpedance Amplifiers (TIA) to convert the photocurrent into a voltage swing that can be provided to a decision circuit such as a CDR. The shorter reach links above, from 300 m at 850 nm up to 40 km at 1550 nm, all use pin-based receivers. Unamplified links at 80 km use the additional gain of an APD to meet more stringent sensitivity requirements. Generally, a Limiting Amplifier (LIA) is integrated into the TIA to provide high gain and high sensitivity. There are cases, discussed later, where high gain is traded for linearity. Depending on the noise and gain requirements set by the sensitivity level of a particular link, TIAs can be designed in GaAs, SiGe, or CMOS processes.

Figure 11: Optical module packaging options. Upper left shows a standard cooled "butterfly" can with coaxial RF interface. Upper and lower right show cooled and uncooled modules, respectively, with coplanar RF interface. Lower left shows uncooled TO can with coplanar RF interface.

#### **Optics Packaging**

Depending on the performance, cooling, and board interface requirements of a particular transceiver design, several different optical packaging technologies are employed, as shown in Figure 11. Traditionally, due to the difficult problem of achieving stable high optical coupling in a reliable manner, "butterfly" style packages have been used. Although they are large and costly, these packages provide a stable, hermetic environment for transmitters, TECs, and receivers, along with a coaxial RF interface to ensure high-quality signal integrity. Smaller, lower cost cooled packages with coplanar RF interfaces have been developed to enable smaller form factor transceivers without sacrificing performance. Uncooled designs are also smaller and cost a lot less; although, their use is limited to devices that can operate over a wide temperature range such as receiver circuitry and uncooled transmitters. Finally, coaxial TO-can-style optics with either coplanar ceramic or glass feedthrough RF interfaces are emerging to provide a very low-cost package that still provides adequate signal integrity for 10 Gb/s operation. While miniaturizing and reducing the cost of these optical modules, it is important to maintain performance and the standards of reliability that have been met by modules qualified to the Telcordia requirements in GR-468 [10]. It is critical that new optical packaging technologies increase vields and the quality of performance and reliability while decreasing the cost of the components, simplifying their manufacture, and reducing testing.

With the basic architecture of the 10 Gb/s optical transceivers presented here, optical communication system vendors have a wide array of transceivers available to meet the specific needs of individual system designs. Depending on the requirements of a particular system design, various form factors, fiber reaches, and performance levels are available in standardized modules.

Two emerging technologies that are influencing 10 Gb/s transceiver design are discussed in the following sections. The first, a wavelength tunable transceiver, enables next-generation DWDM systems. The second, EDC, can compensate for signal degradations due to fiber limitations.

#### **DWDM DESIGN CHALLENGES**

#### Introduction

The recent downturn in the telecom market has forced telecommunications carriers to put enormous pressure on equipment providers to reduce system costs in the core backbone, where DWDM transport systems are typically employed. As a result, equipment providers are beginning to outsource their line-side optics to transceiver vendors. Cost pressures will continue to push standardized

transceiver-based solutions into next-generation products as the DWDM market continues to grow. However, standardizing DWDM line-side optics is very difficult given the very stringent and proprietary requirements specific to each system provider. Here, we present the technologies employed in a 10 Gb/s DWDM transceiver to guarantee robust transmission.

DWDM transport systems are made possible by one key invention, the Erbium-Doped Fiber Amplifier (EDFA). An EDFA boosts the optical power without the need for an electrical regeneration, and thus it manages the link losses between network nodes. It simultaneously amplifies any optical channel within its gain-bandwidth, and this is why optical transport system designers densely pack channels together. Telecommunications carriers can install EDFAs at repeater sites between each fiber span, usually every 20-80 km. The benefits of EDFAs include the ability to add and drop channels at intermediate nodes while allowing pass-through of other channels and the flexibility to add dispersion compensators at each repeater site to minimize transmission penalties. With these technologies, 10 Gb/s long-haul systems have extended their reach well past 1000 km, and 10 Gb/s metropolitan systems have surpassed 300 km in ring circumference.

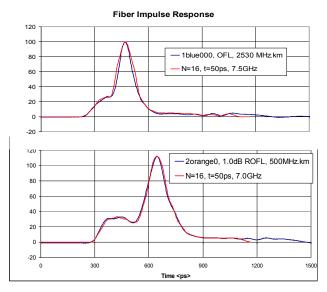

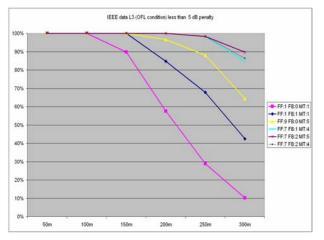

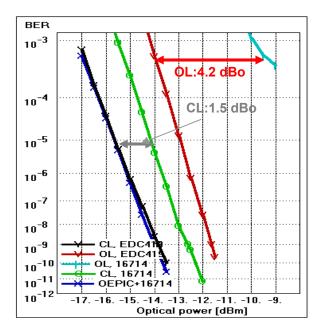

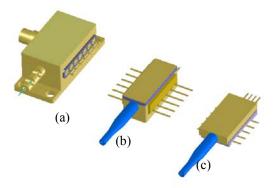

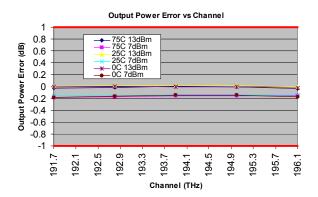

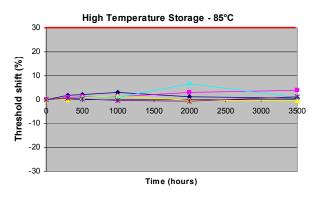

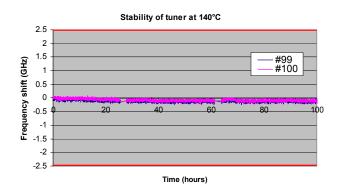

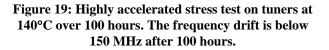

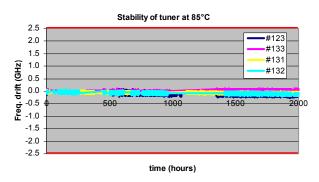

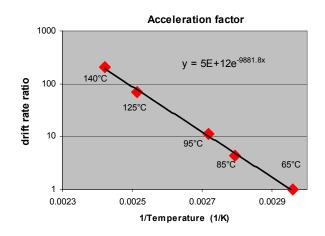

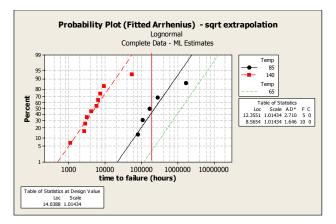

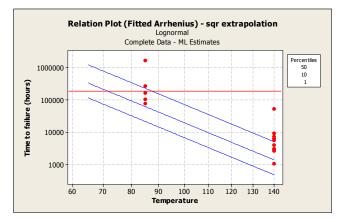

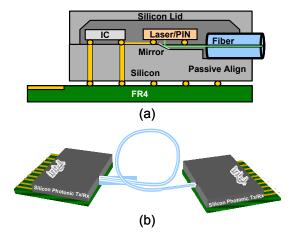

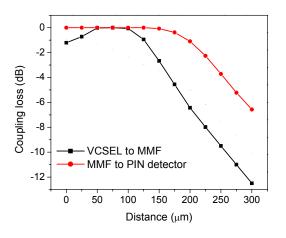

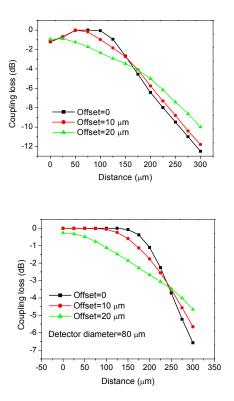

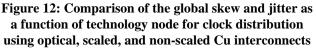

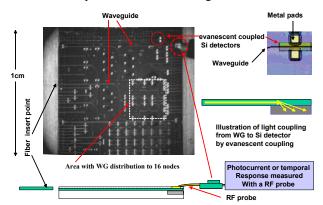

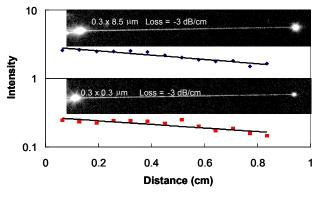

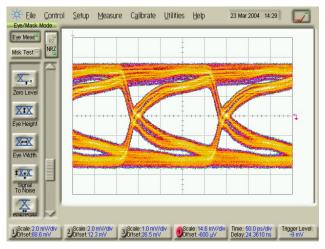

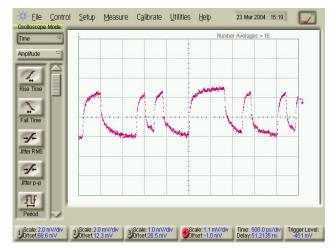

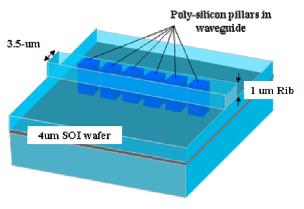

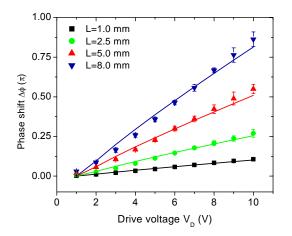

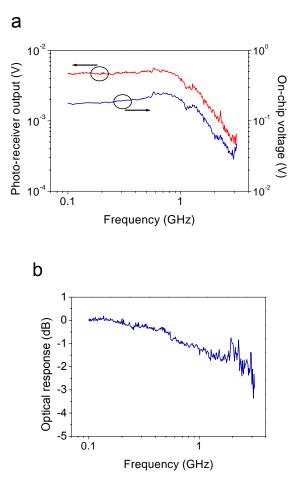

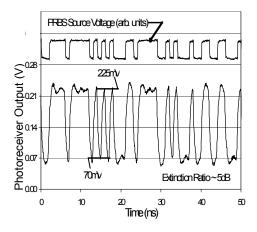

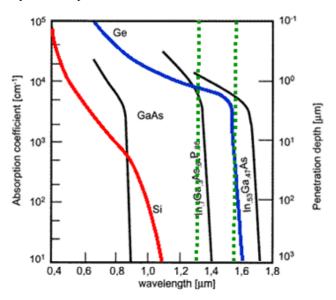

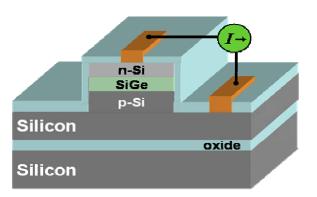

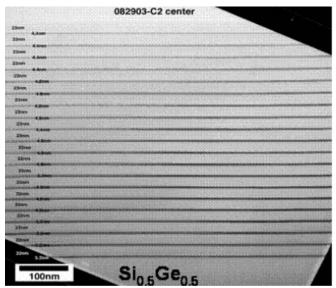

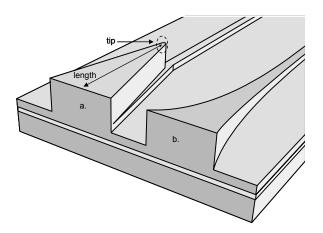

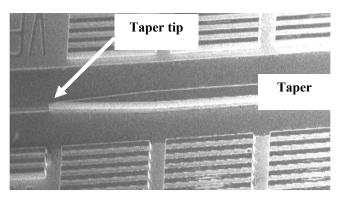

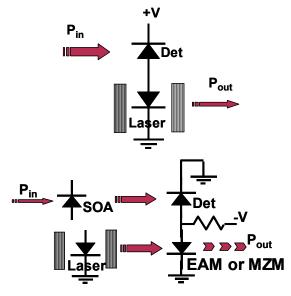

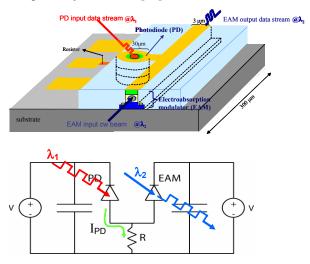

Figure 12: Functional block diagram of a DWDM transceiver