# Intel® Technology Journal

Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology

Mobile PC Platforms Enabled with Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology

# Mobile PC Platforms Enabled with Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology

Gordon Chinn, Mobile Platforms Group, Intel Corporation Sanjiv Desai, Mobile Platforms Group, Intel Corporation Eric DiStefano, Mobile Platforms Group, Intel Corporation Krishnan Ravichandran, Mobile Platforms Group, Intel Corporation Shreekant (Ticky) Thakkar, Mobile Platforms Group, Intel Corporation

Index words: Bluetooth<sup>TM</sup>, Intel<sup>®</sup> Centrino<sup>TM</sup> mobile technology, Intel<sup>®</sup> WCS, WLAN, battery, coexistence, electronic cooling, notebook, power, validation, wireless

## ABSTRACT

Mobile PC platforms enabled with Intel<sup>®</sup> Centrino<sup>TM</sup> mobile technology incorporate innovative technologies to significantly increase the mobility of notebook PCs. In this paper, we describe the following innovations:

- How to reduce interference between wireless communication technologies using the Intel<sup>®</sup> Wireless Coexistence System (Intel<sup>®</sup> WCS).

- Two techniques for significantly extending average platform battery life.

- Simple thermal solutions for thinner and lighter form factors.

Finally, we outline a comprehensive platform-level validation process that helps deliver a stable platform with Intel quality.

#### **INTRODUCTION**

Platforms enabled with Intel Centrino mobile technology incorporate innovative technologies to significantly increase the mobility of notebook PCs. This paper describes innovations in reducing interference between wireless communication technologies, extending average platform battery life, and in driving a thermal solution for thinner and lighter form factors. When multiple wireless technologies such as Bluetooth<sup>\*</sup> Wireless LAN, and Wireless WAN are embedded in the same mobile system, the risk of interference between these radio frequency (RF) technologies greatly increases because of their close proximity to each other. In this paper we discuss general technical RF challenges for mobile platforms and describe innovative techniques used on platforms enabled with Intel Centrino mobile technology. These techniques mitigate interference by using the Intel Wireless Coexistence System (Intel WCS).

We also discuss new and advanced platform powermanagement features for improved battery life. Two new techniques are described: asynchronous voltage regulator (VR) control with a power status indicator (PSI), and multiphase Intel<sup>®</sup> Mobile Voltage Positioning (IMVP).

Platforms enabled with Intel Centrino mobile technology also incorporate state-of-the-art techniques to enable compact, lightweight thermal solutions in smaller form factor systems. The design includes an efficient remote heat exchanger, an air flow set aside for system cooling, and system venting, that together cool the processor and the system as a whole, using only a single fan. The latest interface materials, heat pipe technology, and fans provide the required performance in a small package.

Finally, Intel validation best-known methods (BKMs) are applied to ensure that these platforms deliver optimum

<sup>&</sup>lt;sup>®</sup> Intel and Intel Centrino are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>\*</sup> Other names and brands are the property of their respective owners

<sup>&</sup>lt;sup>®</sup> Intel is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

system performance with multiple wireless technologies operating concurrently within the enterprise as well as when connected to hotspots outside the enterprise.

#### WIRELESS TECHNOLOGIES

Platforms enabled with Intel Centrino mobile technology incorporate innovative radio frequency (RF) technologies to significantly increase the mobility of notebook PCs. These technologies include Wireless Personal Area Networking (WPAN), e.g., Bluetooth; Wireless Local Area Networking (WLAN), e.g., 802.11a and 802.11b; and Wireless Wide Area Networking (WWAN), e.g., General Radio Packet Service (GPRS). Integrating greatly multiple wireless technologies enhances connectivity to the enterprise Intranet and the Internet, as well as to peripherals such as PDAs, printers, and headsets.

#### **Radio Frequency Challenges in Mobile** Notebook PCs

When incorporating RF technologies into a digital computing environment such as a notebook PC, traditional system designers are faced with new challenges previously relegated to RF engineers. Antennas must be added for each frequency band. Since notebook PCs generally consist of many metallic components such as framing structures, hard drives, displays, antenna radiation patterns can be greatly distorted. This distortion can potentially cause significant RF performance variations, as the notebook PC's physical orientation is varied relative to the location of the intended communicating device such as an access point (AP), a peripheral such as a printer, and even another notebook PC.

These RF technologies consist of very sensitive receivers and potentially high-power transmitters. When multiple RF technologies are embedded (co-existent) in the same notebook PC, the risk of interference between these technologies is greatly increased as the transmitters of one radio can couple with the sensitive receivers of another radio, even if they operate in different frequency bands. Technologies such as Bluetooth and 802.11b have even greater interference risks since they both operate in the same 2.4GHz frequency band. Antenna isolation techniques mitigate some of these interference issues, but with multiple antennas and decreasing form factor sizes, optimal placement of antennas is not always possible. New interference-mitigating technologies are then required. For example, Intel Centrino mobile technology includes the Intel Wireless Coexistence System (Intel WCS), which significantly mitigates the interference between 802.11b and Bluetooth technologies.

## Intel Wireless Coexistence System

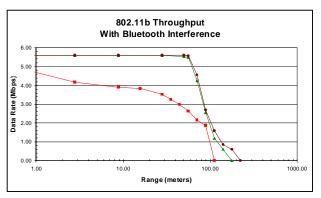

While antenna isolation provides some interference mitigation between 802.11b and Bluetooth radios, performance is still impacted to some degree. For example, 802.11b data throughput is degraded by Bluetooth interference, even with 40dB of antenna isolation, as shown by the lower curve in Figure 1. The upper curve shows the ideal throughput when no Bluetooth interference is present.

Figure 1: 802.11b throughput with Bluetooth interference

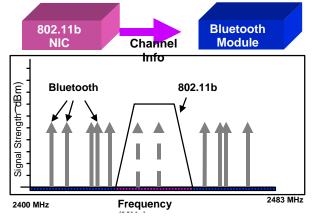

To further mitigate interference between Bluetooth and 802.11b, Intel WCS was developed as one of the Intel Centrino-enabling technologies. Intel WCS consists of a combination of antenna isolation techniques, a channel exchange (Figure 2), and priority signaling between an Intel PRO/Wireless Network Connection 802.11 solution and a third-party Bluetooth module. Phase 1 of Intel WCS has been implemented: it mitigates Bluetooth interference and restores 802.11b data throughput nearly completely as shown by the chart in Figure 1.

Figure 2: Intel WCS Channel Exchange

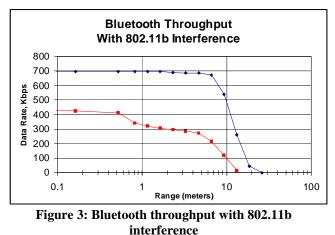

Intel WCS is designed to complement the Adaptive Frequency Hopping (AFH) interference mitigation algorithm being developed by the Bluetooth Special Interest Group (SIG). AFH will mitigate the impact of 802.11b on Bluetooth data throughput, but only between AFH-compliant Bluetooth devices as shown in Figure 3.

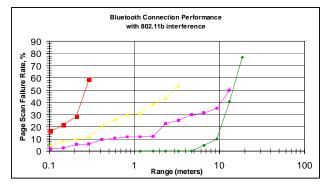

Phase 2 of Intel WCS will add Bluetooth priority signaling from the Bluetooth module to the Intel PRO/Wireless network connection, resulting in a

restoration of connection reliability for both AFH and non-AFH (legacy) Bluetooth devices as shown in Figure 4.

Figure 4: Bluetooth connection performance

#### **Bluetooth Enabling**

Multiple third-party Bluetooth silicon and module vendors have been enabled to be compatible with Intel WCS, including <u>SiliconWave</u> and <u>Cambridge Silicon Radio</u>. Extensive verification and validation testing has been completed with these silicon vendors, providing prevalidated system solutions to the customer.

In summary, integrating multiple RF technologies into mobile notebook PCs provides new challenges to systems designers, including antenna gain uniformity and interference mitigation. Intel WCS, an Intel Centrino mobile technology, provides powerful interference mitigation between 802.11b and Bluetooth and enhances AFH.

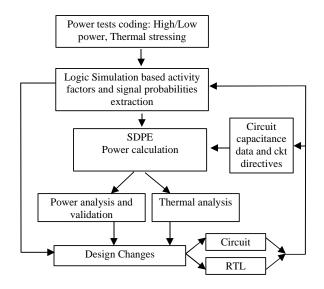

#### EXTENDED BATTERY LIFE TECHNIQUES

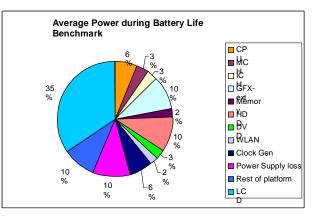

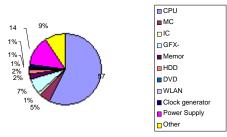

The battery life of a mobile PC is a function of the power consumed by each of its components and the capacity of the battery. Figure 5 shows the breakdown of the power consumption of a typical notebook while running the battery life benchmark Ziff-Davis BL4.01.

Figure 5: Platform average power distribution

As can be seen, some of the largest power consumers are the display (LCD), power supply, hard disk drive (HDD) and graphics. It is also noteworthy that the CPU is one of the lowest consumers of battery life power (only consumes 6%) due to the advanced power-management built into the processor (Intel SpeedStep<sup>®</sup> technology, QuickStart, Deep Sleep, etc.) To learn more about processor power management, please see "Intel<sup>®</sup> Pentium<sup>®</sup> M Processor Power Estimation, Budgeting, Optimization, and Validation" in this issue of the *Intel Technology Journal*.

On Intel Centrino mobile technology, Intel developed and enabled the following *techniques* to reduce the power consumption of some of these subsystems and to help increase the battery life:

- Asynchronous Voltage Regulator (VR) Control with Power Status Indicator #

- Multiphase Intel Mobile Voltage Positioning (IMVP) technology

# Asynchronous Voltage Regulator Control with PSI#

The fully power-optimized CPU represents a very complicated load to the voltage regulator (VR). This is because its current draw can range from a few mAs to several tens of Amperes, depending on the workload put on the processor. The transitions from low to high currents can also occur rapidly (in ms). This makes it difficult for the VR designer to maintain high-power conversion efficiency in the full operating range. Typically, the efficiency is maximized at the highest end of the current range. However, the power-conversion efficiency of the VR drops off quickly toward the low-power condition. This is because the standby or quiescent (zero output loading) power of the VR is approximately 0.2-0.5W, which is comparable to the low-power CPU load, causing the efficiency to be <50%.

In a battery life benchmark, such as the ZDBL4.01, the processor spends >80% of the time in the low-current state (C3). Therefore, it is very important to maximize the power-conversion efficiency of the VR during the C3 state to extend the battery life of the notebook. The Asynchronous VR control with PSI# is a method used to increase the efficiency of the VR during the C3 state, without affecting the efficiency during the high-power state.

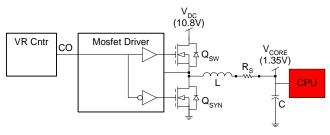

A VR is used to convert an unregulated high input voltage, either the AC/DC adapter or battery, to a suitable regulated DC voltage rail to power the core of the CPU. In this particular application, the regulated voltage is  $1.35V \pm 7.5\%$ , including VR DC error, noise, and transient response error, etc. A switching voltage regulator is used to produce high-power conversion efficiency. Due to the high current demand of the CPU, this VR operates in a continuous synchronous topology.

Figure 6: Synchronous VR

Referring to Figure 6, a VR is used to regulate the battery voltage (8.1-12.6V, 10.8V nominally) down to 1.35V for the CPU core rail. A VR controller monitors the output voltage,  $V_{CORE}$ , and compares it to an internal 1.35V reference.

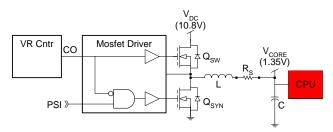

Figure 7: Non-synchronous VR with CPU power status indicator

Referring to Figure 7, the logic driving the gate of  $Q_{SYN}$  is gated, in addition to CO, by a Power Status Indicator (PSI). PSI, when LO, keeps the gate of  $Q_{SYN}$  low regardless of CO level. When PSI is HI, the Mosfet driver drives the gate of  $Q_{SYN}$  normally. In this application, the STP\_CPU# signal can be used in place of a PSI.

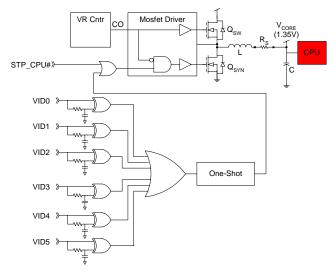

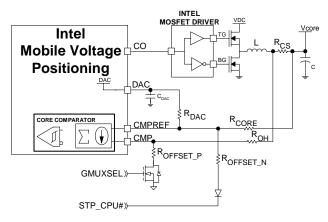

The Geyserville-III transition (Performance Optimized Mode to Battery Optimized Mode) also requires additional modifications due to the voltage differences between the two modes. Figure 8 shows the final circuitry that is used in Intel Centrino mobile technology.

Figure 8: STP\_CPU# override with VID code

#### **Optimized Intel Mobile Voltage Positioning**

A CPU enabled with Intel SpeedStep technology operates at a different CPU core frequency. For example, when operating with an AC adapter plugged into the notebook, battery life is not an issue, as power is always available (although power consumption can limit performance as the internal temperature may rise.) The CPU is placed into a Performance-Optimized Mode (POM), where the core frequency is high (i.e., 1GHz). When operating from the battery as the input power source, the CPU is placed into the Battery-Optimized Mode (BOM) where the core frequency is dropped to a lower value (i.e., 600MHz) to reduce power consumption. The CPU power demand for POM is higher than that of BOM. More importantly, the current demand for POM is much higher than for BOM. This means the output-decoupling requirement for POM is much worse than that for BOM. The CPU voltage tolerance is  $\pm$  7.5% for both POM and BOM because the Intel Mobile Voltage Positioning (IMVP) load line remains constant for both POM and BOM. Therefore, when switched to BOM, using the GMUXSEL signal

(with low indicating that the CPU is in BOM and high indicating POM), the output voltage can be "shifted" down to reduce power consumption.

#### Intel Mobile Voltage Positioning Design Implementation

Figure 9 shows positive offset voltage is controlled by  $R_{OFFSET-P}$ . A small-signal mosfet switch is added in series with this resistor and ground. During POM, GMUXSEL is high connecting  $R_{OFFSET-P}$  to ground, providing a positive offset voltage. During BOM, GMUXSEL is low turning off the mosfet, removing the positive offset voltage.

During DeepSleep state, a negative offset voltage is applied through  $R_{OFFSET-N}$  and pulled down with the STP\_CPU# signal.

**Figure 9: IMVP implementation**

#### RESULTS

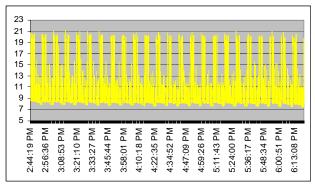

The techniques were implemented on two IBM T20 notebooks with 600 MHz Pentium<sup>®</sup> III processors. All data, unless mentioned otherwise, are averaged power numbers measured during the entire battery discharge (~3-4 hours duration) during a Ziff-Davis Battery Life benchmark, ZDBL4.01.

To establish accurate improvement (if any), a baseline measurement is first established. Two complete ZDBL runs were performed on a new T20 notebook platform with the same battery pack charged overnight each time. An average runtime was calculated along with an average platform/battery power measurement.

#### **CPU Intel Mobile Voltage Positioning Feature Results**

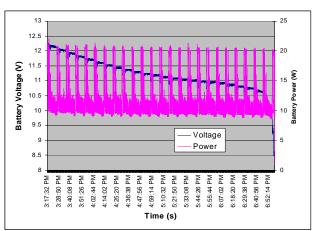

Figure 10 shows a battery from a charged status, 12.0V, down to a discharged status, ~8.5V. The average power over the entire ZDBL run of 3 hours, 40 minutes is 11.77W.

Figure 10: Discharge battery voltage/power profilebaseline

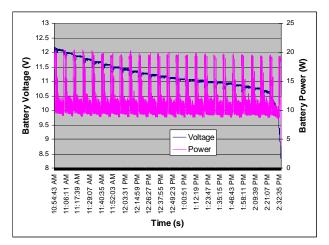

# Figure 11: Discharge battery power profile with CPU IMVP VR

Measurements after CPU Intel Mobile Voltage Positioning Modification show the average power over the entire ZDBL run is 11.49W. This is a 280mW power reduction in the CPU during the ZDBL run (see Figure 11).

<sup>&</sup>lt;sup>®</sup> Pentium III is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

## Non-Synchronous Voltage Regulator with PSI# Results

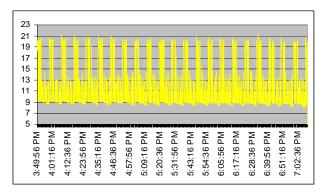

Figure 12 shows the battery discharge power over the entire 3 hour, 15 minute ZDBL run of the IBM T20 notebook used for this study.

Figure 12: Discharge battery power profile-baseline

The average power over the entire ZDBL run of 3 hours, 19 minutes, is 10.94W.

With the non-synchronous VR with PSI# (STP\_CPU#) implemented, the discharge profile is as shown in Figure 13:

Figure 13: Discharge battery power profile with STP\_CPU# VR

The average power over the entire ZDBL run of 3 hours, 36 minutes, is 10.36W. This is a 580mW power reduction in the CPU VR.

In summary, as demonstrated in the above experiments, the two features implemented on the IBM T20 can result in over 1W of power savings during the battery life benchmark (ZDBL4.01) run. While the benefits may vary with different OEM systems, the expectation is that these will save power and improve the life of the battery.

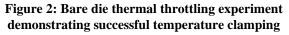

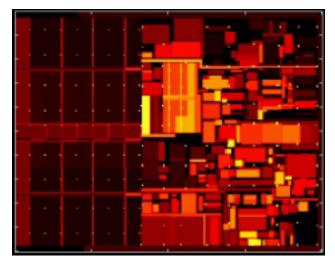

## THERMAL DESIGN

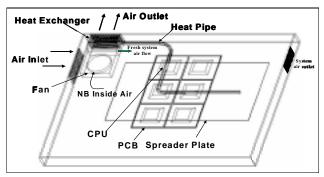

The Intel Centrino mobile technology platform can be cooled using a simple, compact, light-weight solution. The approach, though simple, is fundamentally important to successful design. In this section, we discuss a strawman set of requirements, the overall cooling approach, cooling performance expectations, and the resulting cooling solution design.

For the purposes of this discussion, we define a set of strawman requirements comprising the system form-factor, a platform power scenario, and a set of boundary conditions. We assume a system thickness of 25 mm (total base and display) with a footprint of 320x260 mm, which accommodates a 15" display. This thin form-factor allows for approximately a 13 mm inside height below the keyboard, for a solution design. We further assume a power scenario in which the processor may be at 24.5W, and all the other components may be at 18.5W, for a total of 43W in the base of the system (see Figure 14).

Platform Power (High Power Application)

Figure 14: Platform TDP power

Finally, important boundary conditions are the maximum temperature difference allowed between the component and the user ambient  $\Delta T_{j-a}$ . For the CPU, we assume 65°C. Additionally, any given system design must consider chassis surface temperatures as well as acoustic limits on fan noise, for ergonomic constraints.

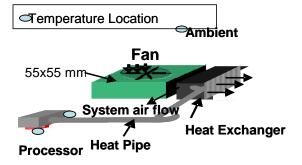

The overall thermal solution approach is illustrated in Figure 15:

Figure 15: Notebook layout illustration

It includes the now conventional remote heat exchanger approach for component cooling, but with fresh air flow capability set aside to provide cool air to the system. The fresh air flow is important to cool components and especially to keep skin temperatures cool. The passive cooling limit (i.e., dissipation by radiation and natural convection from the base of the system) is approximately 18W, allowing for a chassis skin temperature of roughly 15°C above ambient as is observed in typical system designs; close to the non-processor power assumed above.

The overall cooling performance expectations are identified using the equation below:

$$\theta_{j-a} = \frac{\Delta T_{j-a} - T_{system}}{P_{CPU}}$$

where  $P_{CPU}$  is the power we need to cool and  $\Delta T_{j-a}$  is as discussed above.  $T_{system}$  represents the net impact of the power of the rest of the platform on the component, in this case the processor and the thermal solution. The value of  $T_{system}$  is dependent upon system design and is best approximated prior to design by using system simulations. Assuming 10°C for the strawman scenario discussed above, the required performance  $\theta_{i-a}$  is 2.25°C/W.

Figure 16 illustrates schematically the remote heat exchanger cooling solution and important locations of temperatures. The overall performance  $\theta_{j-a}$  is further approximated by the equation below:

$$\theta_{j-a} \approx \theta_{j-hp} + \theta_{hp-a}$$

where  $\theta_{j-hp}$  is the thermal resistance from the component junction to the heat pipe and  $\theta_{hp-a}$  is the remaining resistance from the heat pipe to the ambient temperature through the heat exchanger.  $\theta_{j-hp}$  includes resistance of conduction through silicon, the interface material and contact resistances, and the resistance of the evaporator (region over the heat source) of the heat pipe. With new thermal interface materials, suitable thermal attach and heat pipe design, a performance of approximately 0.45 Ccm2/W can be achieved on a reference die. For performance verification, direct communication with respective suppliers is recommended. All components of  $\theta_{i-hp}$  are affected by the source they are cooling and are considered in  $\theta_{j\text{-}hp}.$  Although the Intel  $^{\circledast}$  Pentium  $^{\circledast}$  M processor uses 0.13 micron process technology, the design is optimized to mitigate the effects of a smaller source,

and the effective  $\theta_{j-hp}$  translates to approximately 0.9°C/W.

Prototypes from fan and heat exchange suppliers indicate that 1.1°C/W can be achieved for  $\theta_{hp-a}$ . However, the  $\theta_{hp-a}$ value must be de-rated to allow for fresh air to be set aside for system cooling. Although the passive limits are close to those accommodated by the maximum passive limits, spreading is not perfect, and an allowance must be made for system constraints on effective passive dissipation. We assume 15%  $\theta_{hp-a}$  performance set aside to complement system cooling. It is important to note that the air flow is provided directly from the exhaust of the fan and flows underneath the motherboard to best protect skin temperature. Two very important features of the system design provide short and direct air flow paths into the fan and out of the heat exchanger and adequate system air outlet vents, respectively.

Figure 16 shows a design rendition of the solution. The weight and volume of prototypes are approximately 55g and 4.3cm<sup>3</sup>, respectively, approximately one-third the weight and size of solutions for higher-power processors.

In summary, the thermal solution for Intel Centrino mobile technology platforms is compact and lightweight, utilizing only a single fan to cool the processor and the system.

#### PLATFORM-LEVEL VALIDATION

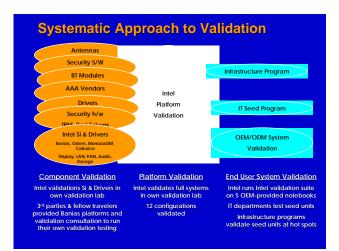

This section outlines the comprehensive platform-level validation process that helped deliver a stable platform with Intel quality. Intel validation BKMs were applied to ensure that a mobile platform with Intel Centrino mobile technology delivered optimum system performance with multiple wireless technologies operating concurrently within the enterprise as well as when connected to hotspots outside the enterprise.

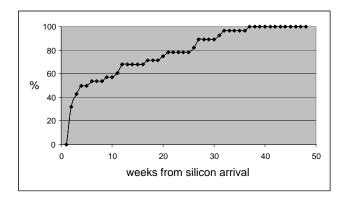

The goal for the platform with Intel Centrino mobile technology was extended validation of all platform components to maximize reliability and interoperability.

<sup>&</sup>lt;sup>®</sup> Pentium M is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

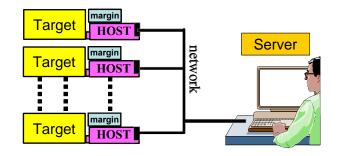

This validation was primarily divided into the following three categories (see Figure 17):

- 1. Validation of Intel and Third-Party Vendor (TPV) Intel Centrino mobile technology-enabled platform components.

- 2. Validation of Intel Centrino mobile technologyenabled platforms on customer reference boards.

- 3. End-User system validation.

Figure 17: Systematic approach to validation

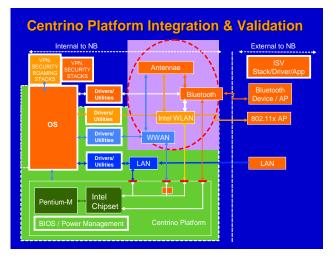

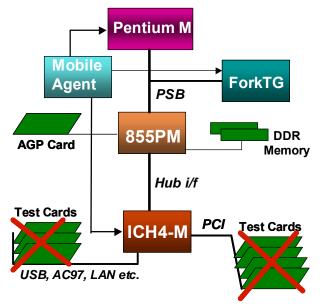

Figure 18 shows Intel and TPV delivered components on a platform with Intel Centrino mobile technology. Each Intel component underwent thorough comprehensive system and compatibility validation using Intel validation BKMs traditionally used on processors and chipsets. To ensure high-quality validation of TPV components, Intel worked with TPVs to define comprehensive test plans for validation of their components using Intel validation BKMs.

# Figure 18: Intel Centrino technology platform integration and validation

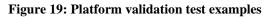

The focus of platform-level validation was the integration of Intel Centrino mobile technology components on an Intel Customer Reference Board platform and the performance of comprehensive compatibility and interoperability validation under mobile-specific stress test conditions as well as under typical usage-model scenarios. Figure 19 shows some examples of platform validation tests.

| Test Category                                                 | Test Examples                                                                                                                                                                                                                           |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pentium-M Processor and<br>System Power Management<br>Testing | -Verify C3 and C4 State transitions occur with<br>the wireless device and its software<br>-Suspend and resume system from 51, 53, and<br>S4 states many times and verify the Wireless<br>Device and its software is in consistent state |

| Multiple Wireless Integration<br>Testing                      | Perform the Banias Processor and System<br>Power States testing with all the wireless<br>elements present in the system                                                                                                                 |

| Stress Testing                                                | Verify wireless device and its software is in<br>consistent state while running CPU and<br>network intensive applications like DVD<br>playback, and Packet Blaster                                                                      |

The third type of validation was platform-level validation using Intel Centrino mobile technology-based OEM systems. The focus was testing in a real end-user environment. For example, multiple Intel Centrino mobile technology-based systems with multiple platform configurations were tested for compatibility with industry- standard Wireless LAN (WLAN) access points at various hotspots.

#### **Intel Wireless Verification Program**

As part of establishing Intel Centrino mobile technology as the premier Wireless LAN notebook PC client, Intel worked with many leading companies to accelerate the deployment of 802.11 wireless communication capabilities in private and public spaces. The overall goal is to help reduce the two major Wi-Fi adoption barriers: availability and awareness. The program works with traditional and emerging Wi-Fi providers and key location owners to achieve the following:

- 1. Deploy Wi-Fi in locations relevant to the business traveler, such as airports, hotels, and franchise chains.

- 2. Verify Intel Centrino mobile technology in the installed infrastructure.

3. Raise the awareness of the availability of the service in these locations by directed co-marketing programs and a signage program.

## CONCLUSION

Platforms enabled with Intel Centrino mobile technology incorporate innovative technologies to significantly increase the mobility of notebook PCs. We described the following innovations:

- Details are given on how to reduce interference between wireless communication technologies. The Intel Wireless Coexistence System is demonstrated to basically recover all WLAN performance under Bluetooth interference.

- Two new, advanced platform power-management features for improved battery life are described in this paper: Asynchronous VR control with PSI, and multiphase IMVP. These features implemented on an IBM T20 can result in over 1W of power savings during the battery life benchmark (ZDBL4.01) run. While the benefits may vary with different OEM systems, the expectation is that these will save power and improve battery life

- By coupling state-of-the-art thermal techniques with the advanced platform power-management features for lower power consumption, the thermal solution for a typical platform with Intel Centrino mobile technology was demonstrated to be compact and lightweight, utilizing only a single fan to cool the processor and the system.

Finally, the Intel Centrino mobile technology platform is extensively tested and tuned for components of Intel Centrino mobile technology to optimally work together in order to maximize reliability and interoperability and to deliver on all four mobility vectors. Intel Centrino mobile technology continues to undergo extensive security validation with industry-standard security and leading third-party security solutions. Intel is continuing to conduct comprehensive infrastructure verification with the wireless LAN infrastructure ecosystem and public wireless LAN service providers.

## ACKNOWLEDGMENTS

The authors thank the following individuals for their contributions: Al Bettner for antenna development and enabling; Marlon Cardenas and Je-Young Chang for driving thermal solution development; Camille Chen for driving WLAN coexistence integration and validation; Randy Durrant for Intel WCS systems design and Bluetooth enabling; Eddie Lin for driving Bluetooth coexistence integration and validation; Don Nguyen for developing the detailed white papers on each of these initiatives, which provided much of the data that is incorporated into this paper; and Francis Truntzer for codeveloping and driving wireless platform validation strategy.

## REFERENCES

For more information on Extended Battery Life Program, please access the following Web site: http://developer.intel.com/design/mobile/battery.htm

#### **AUTHORS' BIOGRAPHIES**

**Gordon Chinn** is the Radio Frequency (RF) Systems Architecture manager in Intel's Mobile Platforms Group (MPG) and is responsible for enabling mobile platform PCs with multiple, concurrent, embedded radio technologies. He has over 30 years of experience in various RF communications development positions in the commercial and aerospace industry. Gordon holds a B.S. and M.S. degree in Electrical Engineering and Computer Science from the University of California at Berkeley. His e-mail is gordon.chinn@intel.com.

**Sanjiv Desai** is the Mobile Systems and Wireless Architecture manager in Intel's Mobile Platforms Group (MPG). He is responsible for the definition and architecture of mobile platforms at Intel. He has over 20 years of industry experience in various CPU, Chipset, and System design and development positions at Intel, National Semiconductor, and American Microsystems Inc. (Gould). Sanjiv holds an M.Sc. degree in Electrical Engineering from North Carolina A&T State University (USA) and a B.Sc. degree in Electrical Engineering from M.S. University (India). His e-mail address is sanjiv.c.desai@intel.com.

**Eric DiStefano** is the manager of the Thermal Tools and Technology team in the Mobile Platforms Group. He has been with Intel defining thermal solutions for mobile processors and platforms for five years. Prior to Intel, he worked in the aerospace industry for 15 years developing advanced space propulsion, propellant feed systems, and cooling of various systems including avionics. His e-mail is <u>eric.distefano@intel.com</u>.

Krishnan Ravichandran has a B.S.E.E. degree from IIT Madras, India and an M.S.E.E. degree from Carnegie Mellon University. He joined Intel in 1988 after completing his M.S. degree and has spent his entire career in the Mobile Group, performing a variety of roles (circuit design, chipset lead, CPU Design Manager, Program Manager, Platform Architecture and more recently Extended Battery Life Manager). His e-mail is krishnan.ravichandran@intel.com.

**Shreekant (Ticky) Thakkar** is the co-director of Mobile Platform Architecture in Intel's Mobile Platforms Group (MPG). He has over 24 years of experience in various development and planning positions at Intel and Sequent (now part of IBM). Ticky established direction for mobile notebook PCs to transition from portable to wireless computing–making the notebooks deliver the best wireless Internet experience. Ticky holds Ph.D. and M.S. degrees in Computer Science/Engineering from the University of Manchester (England) and a B.S. degree in Computer Science/Statistics from the University of Manchester. His e-mail is <u>ticky.thakkar@intel.com</u>.

Copyright © Intel Corporation 2003. This publication was downloaded from <u>http://developer.intel.com/</u>.

#### Legal notices at

http://www.intel.com/sites/corporate/tradmarx.htm.

For further information visit: developer.intel.com/technology/itj/index.htm

Copyright © 2003, Intel Corporation. All rights reserved. Intel is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries. For a complete listing of trademark information visiti: www.intel.com/sites/corporate/tradmarx.htm

# Intel® Technology Journal

Intel<sup>®</sup> Centrino<sup>™</sup> Mobile Technology

The Intel<sup>®</sup> Pentium<sup>®</sup> M Processor: Microarchitecture and Performance

# The Intel<sup>®</sup> Pentium<sup>®</sup> M Processor: Microarchitecture and Performance

Simcha Gochman, Mobile Platforms Group, Intel Corporation Ronny Ronen, Microprocessor Research Labs, Intel Corporation Ittai Anati, Mobile Platforms Group, Intel Corporation Ariel Berkovits, Mobile Platforms Group, Intel Corporation Tsvika Kurts, Mobile Platforms Group, Intel Corporation Alon Naveh, Mobile Platforms Group, Intel Corporation Ali Saeed, Mobile Platforms Group, Intel Corporation Zeev Sperber, Mobile Platforms Group, Intel Corporation Robert C. Valentine, Mobile Platforms Group, Intel Corporation

Index words: Pentium<sup>®</sup> M processor, microarchitecture, power-aware design, branch prediction, instruction fusion, processor bus, SpeedStep<sup>®</sup> technology

#### ABSTRACT

The Intel<sup>®</sup> Pentium<sup>®</sup> M processor is a key component of Intel<sup>®</sup> Centrino<sup>™</sup> mobile technology platform. It is Intel's first microprocessor designed specifically for mobility. It provides outstanding mobile performance<sup>1</sup> and its dynamic power management enables energy saving for longer battery life.

Designing a mobile processor calls for different power/ performance tradeoffs than designing a traditional highperformance processor. In this paper we explain the design philosophy that was adopted by the Intel Pentium M processor's architects to achieve best performance at given power and thermal constraints.

We present an overview of the Intel Pentium M processor's major advanced power-aware performance features including the innovative branch predictor, the dedicated stack manager, the micro-operation fusion, and the Intel Pentium M processor bus.

We next describe the Pentium M processor's Enhanced Intel SpeedStep<sup>®</sup> technology that allows significant reduction in energy consumption without compromising performance.

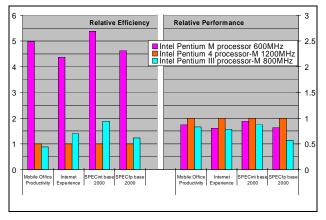

We conclude with demonstrating the superior performance and power-awareness of the Pentium M processor by comparing it with other mobile processors on a variety of known industry benchmarks.

#### **INTRODUCTION**

The distinction between *Mobile* and *Desktop* computing segments is not new. There are several vectors in which these segments differ, two of which are relevant to our discussion: power dissipation and battery life [1].

• *Power, Power Density, and Thermal.* The overall dissipated power, as well as the power dissipated by the chip per unit area, are important factors. Power generates heat. In order to keep transistors within their allowed operating temperature range, the generated heat has to be dissipated from its source in a cost-effective manner. These constraints limit the processor's *peak power* consumption. Peak power consumption limits apply both to desktops and mobile computers. However, the mobile computer's

<sup>&</sup>lt;sup>®</sup>Intel Pentium M is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>&</sup>lt;sup>®</sup>Intel Centrino is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>&</sup>lt;sup>1</sup> System performance, battery life and functionality will vary depending on your specific hardware and software configurations.

<sup>&</sup>lt;sup>®</sup>SpeedStep is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

smaller form-factor and lighter weight decrease the mobile processor's power budget<sup>2</sup>.

• *Battery Life.* Batteries are designed to support a certain Watts x Hours<sup>3</sup>. The higher the average power is, the shorter the time that a battery can operate. This constraint limits the processor's *average power* consumption, which is a crucial factor for mobile computers but less relevant for desktop computers.

Until not so long ago, the size of the mobile market was significantly smaller than that of the desktop market, causing mobile PC designers to retrofit processors designed to address the desktop market. Desktop processors were designed to achieve the highest performance possible for all user profiles with little consideration of power consumption. Meeting the more restrictive peak and average power constraints of mobile PCs involved a compromise. New processors were adapted to the mobile market by either operating them at a lower voltage and frequency, hence compromising performance, or by delaying the implementation of their mobile version to the next-generation process technology, hence losing time-to-market.

The increased demand for mobile PCs, combined with the growing gap between desktop and mobile peak and average power budgets, made it impractical to continue the trend of using desktop processors for the mobile market. Mobile users expect to have close-to-desktop performance even with the more restricted power and thermal environment. Addressing this need called for a processor designed with the mobile environment in mind. This is where the Intel Pentium M processor comes in.

The Pentium M processor is Intel's new flagship poweraware microprocessor. Upon introduction (in March 2003) its highest performing version ran at 1.6 GHz  $@1.47V^4$ , its Low Voltage version ran at 1.1 GHz @1.18V, and its Ultra Low Voltage version ran at 900 MHz @1.0V. It follows a new design approach with the goal of delivering breakthrough performance at a lower power budget as well as minimizing the processor's average power for extending battery life. The Intel Pentium M processor includes several new innovative features that enable it to meet its design goals.

This new processor has 77 million transistors implemented on Intel's  $0.13\mu$  CMOS process, with six levels of copper interconnect. Its die size is 84 mm<sup>2</sup> and its peak power consumption is 24.5 watts at 1.6 GHz. Its 3.2 GB/second processor bus helps to provide the high data bandwidths needed for today's and tomorrow's demanding applications. It fully implements the IA32 instruction set architecture [2], including Streaming SIMD Extension (SSE) and Streaming SIMD Extension 2 (SSE2) targeted for multimedia, content creation, scientific, and engineering applications.

We begin with an overview of the Intel Pentium M processor design philosophy. Then we examine in depth the major innovative power-aware and energy-aware features of this processor. We conclude by comparing the performance and power-awareness of the Pentium M processor with those of other mobile processors.

## POWER-AWARENESS PHILOSOPHY AND STRATEGY

Design tradeoffs for the mobile market are rather complicated and involve several challenges:

- Optimizing the design for maximum performance and extended battery life. The challenge lies in how to balance between these conflicting goals.

- Trading performance for power. Performance features-whether increasing instruction-level parallelism (ILP) or speeding up frequency-usually increase power consumption. Power-saving features usually decrease performance. The challenge lies in figuring out how much power one can afford to lose in order to implement a performance feature.

Setting a clear direction for tradeoffs between higher performance and longer battery life and between performance and power was essential for converging the definition of the Intel Pentium M processor.

## Higher Performance vs. Longer Battery Life

Early in the design it was realized that the average power consumption for typical usage of the Intel Pentium M processor is only a small portion of the whole platform power consumption–less than 10%. This low average power is mainly due to the ability of the processor to enter lower power states in idle periods and to the Enhanced Intel SpeedStep technology, which significantly reduces power in periods of low processor activity. The majority of the power in the platform is

<sup>&</sup>lt;sup>2</sup> Currently (2003), typical desktop processor peak power consumption is about 100W. Typical mobile processor peak power is about 30W.

<sup>&</sup>lt;sup>3</sup> Currently (2003), typical battery capacity is 24-72WxH. A typical Pentium M platform uses 48WxH batteries. A typical platform's power is 13W, of which the processor consumes about 1W on average. Smaller platforms use 24WxH to save weight.

<sup>&</sup>lt;sup>4</sup> 1.47V is the highest operating voltage of the  $0.13\mu$  CMOS process on which the processor is implemented.

consumed by other components: the LCD, the hard disk, the memory system, networking components, etc. Under these circumstances, it was clear that the potential gain in system battery life by further reducing the processor's average power would be small<sup>5</sup>. With that in mind, we decided to optimize the design for the highest performance within power and thermal constraints, when the processor is active, and to focus on battery life when it is idle.

It should be noted that the above may change in the future. We expect high-performing processors' average power to grow due to more complex processor logic and higher static power and new demanding workloads. We expect platforms to become smaller, simpler, and more efficient hence consuming less power. Therefore, the portion of the processor's average power as part of the overall platform power consumption will increase.

#### **Trading Performance For Power**

The tradeoffs are different if we optimize for higher performance or for longer battery life. For higher performing mobile processors (and in fact, now, in all high-performing processors) the criterion is "Maximizing performance at given thermal constraints." For longer battery life the criterion is "Minimizing energy per task." Below, we explain what each criterion actually means.

# Maximizing Performance at Given Thermal Constraints

The processor's thermal map depends on the power consumption, the local power density at various points on the die, the cooling mechanism, and more. At the early stages of the Intel Pentium M processor's microarchitecture definition, when thermal information was not available, we replaced the criterion "Maximizing performance at given thermal constraints" with: "Maximizing performance at a given power envelope" <sup>6</sup>.

According to this criterion, a microarchitectural feature that gains performance or saves power should be better than simply using voltage/frequency scaling. For a given working point of core voltage  $V_0$  and Frequency  $F_0$  the power consumption of a processor is given by

$$Power_0 = \alpha * C_0 * V_0^2 * F_0$$

where  $\alpha$  is the activity factor,  $Power_0$  is the power consumption and  $C_0$  is the effective capacitance for a given design. The frequency is usually approximated as being linearly proportional with the operating voltage, namely

$$F_0 \cong K_{\rm f} * V_0$$

where  $K_{\rm f}$  is the proportion constant. This leads to the cubic dependency of power on the operating voltage

$$Power_{\max} = \alpha * C_0 * V_0^3 * K_f$$

The performance at this operating condition is given by

$$Perf_0 \cong IPC_0 * F_0$$

where  $IPC_0$  indicates the Instruction Per Cycle in Frequency  $F_0^{7}$ .

It can be derived from the above formulae (see also [3]) that by increasing the voltage by 1%, for example, one can increase performance by 1% through increased frequency. This would result in a power increase of approximately 3%. Thus, an alternate microarchitectural feature that gains less than 1% in performance for a power increase of 3% or more should be rejected upfront. In general, a microarchitectural feature can be regarded as power-aware, if the % ratio between the power increase and the performance gain is less than 3.

#### **Minimizing Energy Per Task**

Energy consumption in general is a sum of two components: active energy and idle energy. Minimizing the idle energy consumption is relatively straightforward and does not involve conflicting design tradeoffs: the processor enters a deep-sleep power state, stops the clocks, and lowers the operating voltage to the minimum allowed to sustain the internal state. Optimizing active energy is more complex. A very slow execution consumes less power for a longer period of time, while heavy parallelism reduces the active time but increases the active power.

or

$$Energy_{active} = Power_{active} + Iume_{active}$$

$$Energy_{active} \cong Power_{active} / Perf_{active}$$

This implies that in order to improve overall battery life, the % performance benefit must be greater than the additional power consumed.

<sup>&</sup>lt;sup>5</sup> In the ideal case where the 10% power is totally eliminated, battery life would be extended by only 11%. <sup>6</sup> The Intel Pentium M processor's design assumed

power envelopes from 7W for passively cooled boxes up to 24W for Thin and Light platforms.

<sup>&</sup>lt;sup>7</sup> For the sake of this discussion, we assume performance scales linearly with frequency. In reality, mainly due to off-chips accesses (memory and I/O), performance does not scale with frequency.

During the definition of the Intel Pentium M processor we tended to use the stricter criterion in each case:

- Performance improvement features were usually included if they *"minimized energy per task,"* that is, they save energy. Features that pass this criterion improve performance and extend battery life-the ultimate win/win situation. Faster execution also implies longer idle time, allowing active units to be shut off, thus saving even more energy.

- Power-saving features may reduce Instructions Per Cycle (IPC) resulting in a performance loss. Such power-saving features were usually included only when they "maximized performance at given thermal constraints," that is, the performance loss was smaller than would have been achieved by just using voltage and frequency scaling. In practice, by applying this criterion, a tradeoff can be made between saved power and increased frequency, thus squeezing more performance at the peak allowed power.

- Performance-improvement features that met the "maximize performance at given thermal constraints" criterion, but failed the "minimizing energy per task" one, were carefully judged and in many cases included. Such features do increase performance but consume more energy. This loss is negligible, since, as mentioned above, the processor's average power as a portion of the overall system average power is relatively small. In fact, the faster execution results in a longer idle time, potentially allowing additional energy savings.

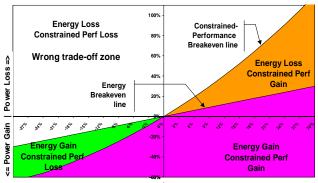

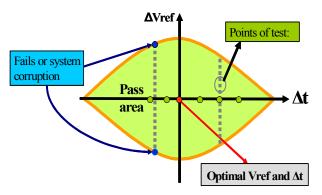

- Figure 1 illustrates the design tradeoffs from a performance feature viewpoint. The magenta area (in the lower right side) indicates a clear win–improving both performance at the power envelope and battery life. The orange area (resides in the upper right side) indicates a tradeoff where constrained performance is preferred over lower battery life. The green area (resides in the lower left side) indicates a tradeoff where improved battery life is preferred over constrained performance. The white area (in the upper left side) is a clear "drop."

<= Performance loss | Performance gain =>

Figure 1: Performance/power tradeoff zones

Now that the tradeoffs are known, we examine the strategies we used to identify power-aware features. Power-awareness means attacking power and energy consumption at all levels:

- Reducing number of instructions per task.

- Reducing number of micro-ops per instruction.

- Reducing number of transistor switches per micro-op.

- Reducing the amount of energy per transistor switch.

#### **Reducing the Number of Instructions Per Task**

From an architectural point of view the number of instructions per task is fixed. However, from a microarchitectural point of view, this is true only for the number of retired instructions. With branch prediction, there are many speculated instructions running within the processor that are not retired. A better branch predictor decreases the number of the speculated instructions, thus practically reducing the number of overall processed instructions. Indeed, the extra logic involved in a better branch predictor does consume power, but the gain in the reduced number of instructions exceeds that extra cost.

#### **Reducing the Number of Micro-ops Per Instruction**

Out-of-order implementations of the IA32 Instruction Set Architecture (ISA) break macro-instructions into a sequence of one or more simple operations, called micro-operations, or *micro-ops* [4]. Handling and executing each micro-op consumes power. Eliminating micro-ops from the micro-op stream or combining several micro-ops together reduces the overall power. The Intel Pentium M processor micro-ops fusion and dedicated stack engine do exactly that. Here, as well, the gain in reduced micro-ops exceeds the cost of the extra logic involved.

# Reducing the Number of Transistor Switches Per Micro-op

This is more straightforward and intuitive. High performance processors run at a high frequency and

provide a high degree of instruction-level parallelism– switching a lot of transistors on the way. There is a clear gain in doing the same operation with a smaller number of switches. In some cases, this is simple and involves only local optimizations such as accessing only the portion of a register or a cache line that is actually needed. In other cases, it calls for a global optimization to decide whether a unit will not be used for the next cycle, and thus can be shut off. Occasionally, such power saving may involve a performance loss.

# Reducing the Amount of Energy Per Transistor Switch

Energy per switch depends on the transistor size and type, and on the operating voltage. Smaller transistors and lower operating voltages reduce energy per switch [5]. The effect of microarchitecture here is rather limited. Transistor size and type are tuned so that they meet the timing constraints without wasting unnecessary power. The Enhanced Intel SpeedStep technology reduces the operating voltage at low activity periods, thus reducing the energy per transistor switch. Microarchitecture can help reduce energy per switch by optimizing the amount of interconnect in the processor.

Each strategy affects performance, power, and energy in a different way. In most cases, features that fall under one of these strategies save energy per task. However, performance-improving features are likely to result in increased power consumption, e.g., better branch prediction reduces energy, but also reduces stalls, thus increasing power. This may look bad, but, in fact, it is not. Higher performance at lower energy can be traded for lower power by slowing down the processor either by using voltage/frequency scaling or microarchitectural throttling.

#### Static Power

The power consumed by a processor consists of active power (used to switch transistors) and static power (leakage of transistors under voltage). In this paper we focus mainly on active power reduction, but it is worth mentioning how the Intel Pentium M processor also reduces static power consumption.

The static power is roughly a function of the number of transistors, their type, the operating voltage, and the die temperature. The Pentium M processor reduces static power by several means:

• *Low-leakage devices*. The processor's 1MB power managed L2 cache, which contains roughly two-thirds of the transistors in the processor, is built with low-leaking transistors. Low-leaking transistors are somewhat slower, thus slightly increasing the cache

access latency, but the significant power saved justifies the small performance loss.

• *Enhanced Intel SpeedStep technology*. This advanced technology significantly reduces the processor voltage (and temperature), hence leakage power, when processor activity is low.

#### **POWER-AWARE FEATURES**

The following sections describe several of the Intel Pentium M processor's power-aware features. These features cover all the above-mentioned strategies:

- Reducing the number of instructions per task: advanced branch prediction.

- Reducing the number of micro-ops per instruction: micro-ops fusion and dedicated stack engine.

- Reducing the number of transistor switches per micro-op: the Intel Pentium M processor bus and various lower-level optimizations.

- Reducing the amount of energy per transistor switch: Intel SpeedStep technology.

## **ADVANCED BRANCH PREDICTION**

For high-frequency pipelined microprocessors, branch prediction continues to be one of the biggest ticket items for gaining performance. In the Intel Pentium M processor, the benefits are actually twofold: the decrease in speculative code gains performance and reduces the energy spent per instruction retired.

The advanced branch prediction in the Pentium M processor is based on the Intel Pentium<sup>®</sup> 4 processor's [6] branch predictor. On top of that, two additional predictors to capture special program flows, were added: a Loop Detector and an Indirect Branch Predictor.

Figure 2: The Loop Detector logic

<sup>&</sup>lt;sup>®</sup>Pentium 4 is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

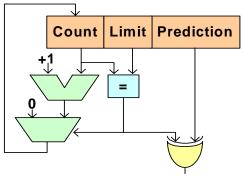

The Loop Detector (Figure 2) analyzes branches to see if they have loop behavior. Loop behavior is defined as moving in one direction (taken or not-taken) a fixed number of times interspersed with a single movement in the opposite direction. When such a branch is detected, a set of counters are allocated in the predictor such that the behavior of the program can be predicted completely accurately for larger iteration counts than typically captured by global or local history predictors.

The Indirect Branch Predictor solves the problematic data-dependent indirect branches. Indirect branches are heavily used in object-oriented code (C++, Java), hence they became a growing source of branch mispredictions. While most indirect branches have a single target at run time, some, such as a case statement in a byte-code interpreter, may have many targets. These targets are chosen in a data-dependent manner.

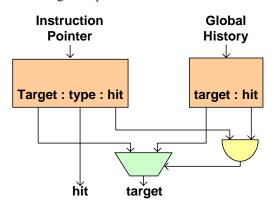

The Indirect Branch Predictor (Figure 3) chooses targets based on a global control flow history, much the same way a global branch predictor chooses the direction of conditional branches using global control flow history. As can be seen in the figure, it is an adjunct to the normal target prediction device. Targets are always allocated in the Instruction Pointer tagged table along with the type of branch. When a misprediction occurs due to a mispredicted target on an indirect branch, the Indirect Branch Predictor allocates a new entry corresponding to the global history leading to this instance of the indirect branch. This construction allows monotonic indirect branches to predict correctly from the IP-based Target array, and data-dependent indirect branches to allocate as many targets as they may need for different global history patterns, which correlate with the different targets. Entries in the Indirect Branch Predictor are tagged with the hit and type information in the IP-based target array to prevent "false positives" from the Indirect Branch Predictor to lead to new sources of target mispredictions.

**Figure 3: The Indirect Branch Predictor logic**

The Intel Pentium M processor branch predictor misprediction rate is 20% lower than that of previous generation designs, resulting in as much as 7% in real performance. Approximately 30% of this benefit comes from the combination of the Loop Detector and Indirect Branch Predictor. The Loop Predictor captures a common program behavior and benefits many applications regardless of compilation techniques. The Indirect Target Predictor shows its gains more in specific applications where indirect branches are used to select data-dependent targets. In such applications, when the compilers use calculated branches rather than if-trees made from conditional branches, performance gains can be a few percentage points.

#### **MICRO-OPS FUSION**

Out-of-order implementations of the IA32 Instruction Set Architecture (ISA) break macro-instructions into a sequence of one or more simple operations, called micro-operations, or *micro-ops*. A conventional microop consists of a single operation operating on two sources. The Instruction Decoder breaks a macroinstruction into multiple micro-ops whenever the macroinstruction operates on more than two sources or when the nature of the operation requires a sequence of unrelated operations. There are quite a few cases of macro-instructions that break into several micro-ops, two of which are store operations and load-and-op (readmodify) operations.

Macro-instructions that store data in memory are decoded as two independent micro-ops. The first operation–*store-address*–calculates the address of the store, while the second operation–*store-data*–stores the data into the Store Data buffer<sup>8</sup>. The separation between the store-data and the store-address operations is important for memory disambiguation. Breaking the store operation into two micro-ops allows the store-address operation to dispatch earlier, even before the stored data are known, enabling resolution of address conflicts and opening the memory pipeline for other loads.

A typical load-and-op macro-instruction consists of two micro-ops: the first operation reads the operand from an address in memory, and the second operation calculates the result based on the data read from memory and the register operand. A load-and-op macro-instruction may have up to three register operands, so it must be implemented by two micro-ops. The atomic operations

<sup>&</sup>lt;sup>8</sup> The actual write to memory is done when the store retires. Only then are the data in the respective Store Data buffers written into the specified address.

are inherently serial, and the second operation cannot start until the first operation completes.

Splitting the macro-instruction into multiple micro-ops also has its toll:

- The increased number of micro-ops creates pressure on resources with limited bandwidth (rename, retire) or limited capacity (Reorder-Buffer, Reservation-Station). This pressure eventually results in performance loss.

- Splitting a macro-instruction into more than one micro-op is a complex operation that requires a significantly more capable decoder. Due to its complexity, most implementations opt to have only one complex decoder; all other decoders are left to handle macro-instructions that break only into a single micro-op.

- Delivering more micro-ops through the system increases the energy required to complete a given instruction sequence.

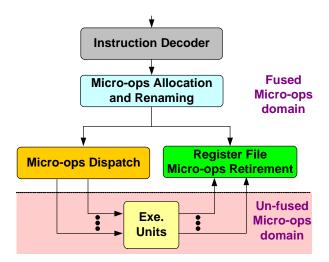

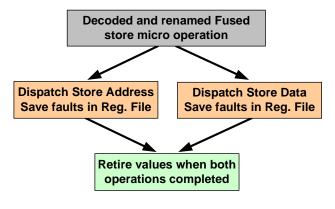

The Pentium M processor features the micro-ops fusion mechanism to reduce this performance and energy cost while maintaining the benefit of the out-of-order execution. With micro-ops fusion, the Instruction Decoder *fuses* two micro-ops into one micro-op and keeps them united throughout most parts of the out-of-order core of the processor–at allocation, dispatch, and retirement. To maintain their non-fused behavior benefits, the micro-ops are executed as non-fused operations at the execution level. This provides an effectively wider instruction decoder, allocation, and retirement. Figure 4 describes the different domains in which the micro-op is fused and unfused.

**Figure 4: Micro-ops fusion domains**

The macro-instruction is decoded into a single fused micro-op by the Instruction Decoder. The fused microop is allocated, renamed, and then issued into a single entry in the Reorder-Buffer and the Reservation-Station. To support fused micro-ops, each reservation-Station entry can accommodate up to three source operands. When dispatching to the execution units, the Dispatcher controls the separate execution of each portion of the fused micro-op according to the readiness of its sources. In a sense, the Dispatcher treats each portion as if it occupied the whole entry for itself. The Execution of each operation is performed in the same way as a nonfused micro-op with only minor changes made to the execution units.

The fused store operation is depicted in Figure 5.

**Figure 5: Fused store flow**

The two micro-ops making up the fused store micro-op can be issued to their relevant execution units in parallel. The dispatch of the store-address operation to the address-generation unit is performed when its sources (the base and index registers) are ready. The dispatch of the store-data operation to the store data buffer unit can occur independently when its source operand is available. The retirement of the fused store can occur only after both operations complete.

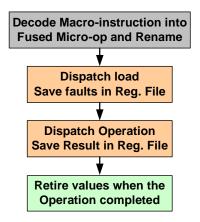

The fused load-and-op operation is depicted in Figure 6.

Figure 6: Fused load-and-op flow

The two micro-ops making up the fused load-and-op micro-op are issued serially to the relevant execution units. The dispatch of the load operation is performed when its sources (the base and index registers) are ready. The dispatch of the "op" portion of the load-and-op operation to the execution unit can occur only after the load completes and the other operand is ready. The retirement of the fused load-and-op micro-op can occur only after both operations complete.

We have found that the fused micro-ops mechanism reduces the number of micro-ops handled by the out-oforder logic by more than 10%. The reduced number of micro-ops increases performance by effectively widening the issue, rename, and retire pipeline. The biggest boost is obtained during a burst of memory operations, where micro-op fusion allows all decoders, rather than the one complex decoder, to process incoming instructions. This practically widens the processor decode, allocation, and retirement bandwidth by a factor of three.

The typical performance increase of the micro-op fusion is 5% for integer code and 9% for Floating Point (FP) code. The store fusion contributes most of the performance increase for integer code. The two types of fused micro-ops contribute about equally to the performance increase of FP code.

Delivering less micro-ops through the processor decreases the energy required to complete a given instruction sequence since the same task is accomplished by processing fewer micro-ops. The gain in power consumption is higher than the loss, due to the additional logic required to implement the micro-ops fusion mechanism.

## **DEDICATED STACK ENGINE**

The IA32 Instruction Set Architecture (ISA) features instructions for hardware-assisted stack management that

are typically used to implement a combined parameter and control-flow stack used in high-level programming languages. The ISA provides PUSH, POP, CALL, and RET, which have the obvious parameter stack and control-flow stack behaviors. The ISA dedicates the hardware Stack Pointer register (ESP) as the machine stack pointer, and this register is modified as a side effect of each of these instructions. Sequences of such instructions are quite common, for instance, PUSHing a set of operands and then using a CALL instruction is the standard mechanism for making a Procedure or Function Call.

In traditional out-of-order implementations of the IA32 ISA, these side-effect operations were performed by sending with each stack-related macro-instruction an additional micro-op to update the ESP register. This micro-op adds or subtracts an immediate value to the ESP register.

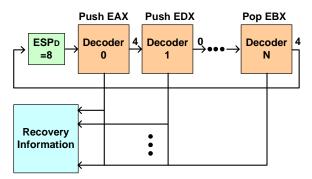

The Intel Pentium M processor chose to implement the ESP "side-effect" behavior in a more efficient way, using dedicated logic near the superscalar decoders. The idea is to represent the programmer's view of ESP  $(ESP_P)$  at any given point in time by some historic ESP living in the out-of-order execution core  $(ESP_O)$  added to a delta  $(ESP_D)$  that is maintained in the front end (see also [7]):

$$ESP_P := ESP_O + ESP_D$$

When, for example, a sequence of PUSHes and POPs is encountered in the instruction stream, the dedicated Stack Hardware executes the ESP side-effects in the decoders and updates the ESP<sub>D</sub> register. Referring to Figure 7, we can see a superscalar implementation for N+1 decoders passing the accumulated delta value across the decoders and updating the delta register with the result, after the instructions are decoded. The hardware also patches the in-flight ESP<sub>D</sub> value into the address syllable of each of the stack referencing microops (patch HW not shown for clarity) so that the address generation unit (AGU) can calculate the proper memory location referenced by ESP<sub>P</sub>. This provides the following benefits:

- Dependencies on ESP are removed since the ESP<sub>o</sub> value used for scheduling in the out-of-order machine is not changed during the sequence of stack operations. This allows more parallelism opportunities to be realized in the out-of-order execution.

- ESP<sub>D</sub> updates are done using a small specialized dedicated adder, thus freeing the general execution units to work on other micro-ops. This allows a higher degree of superscalarity for these instructions

without the cost associated with going to a higher degree of superscalarity for all integer operations. Additionally, since the ESP updating micro-ops have been eliminated, the ALUs are free to be utilized by more complex operations that would have been blocked by the ESP updates, increasing execution bandwidth.

• Updating the delta register in the front end eliminates the ESP updates micro-ops from the out-of-order machine. Thus, power saving is realized since the large adders are not used for small operations, and the eliminated micro-ops do not toggle bits throughout the machine.

Figure 7: The dedicated stack engine logic

There are two complications with the Dedicated Stack Engine. Since it lives in the front of the pipeline, all its calculations are speculative. In order to recover a precise state at any point in the machine's life, the value of  $ESP_0$  and  $ESP_D$  must be able to be recovered for all instructions in the machine.  $ESP_0$  is maintained by the out-of-order core as any other general-purpose register. The Intel Pentium M processor adds an additional table (also shown in Figure 7) that saves the  $ESP_D$  value and a code relating to the effect on the  $ESP_D$  register for every instruction in the machine. This allows the value of  $ESP_P$  to be recovered for all instructions either pre- or post-execution. This allows for handling of either Faults or Traps as defined in IA32.

The second complication occurs when the architectural value of ESP is needed inside the out-of-order machine, for instance, "*XOR ESP,3*" or, more commonly, when ESP is used in an address syllable. In this case, the decode logic automatically inserts a micro-op that carries out the ESP<sub>P</sub> calculation. The ESP<sub>D</sub> register can be cleared since the architectural value is now coherent. A sync is not generated when the ESP<sub>D</sub> register is zero, so continued usage of ESP as a general-purpose register will have no ill effects.

The Dedicated Stack Engine ESP typically eliminates 5% of the micro-ops from an IA32 program compared to a processor not including this feature, even when

including the ESP synchronization micro-ops. Clearly this makes the out-of-order machine look virtually larger and frees execution bandwidth. However, the major performance gain is to increase the front-end bandwidth on these common instruction sequences to the full width of the superscalar decoders. These 5% of eliminated micro-ops result in a similar decrease in energy per instruction–in line with the Pentium M processor's power-awareness direction.

## THE INTEL PENTIUM M PROCESSOR BUS

The Intel Pentium M processor bus was designed to provide a desktop-like performance while consuming significantly less power. Power saving is achieved by the combination of protocol and circuit methods that are unique to the Pentium M processor bus.

The processor bus supports 100 MHz bus clocks with a data rate of 400M transfers per second. It is a latched bus with an in-order queue of 8-pipelined transactions. Designed for mobile systems, the bus is optimized for a uni-processor environment. For example, it allows us to reduce the number of pins to save power:

- There are only 32 address bits that cover 4GB of physical address space.

- The bus does not support dual-processors, since the mobile systems' power budget cannot support dual processors anyway.

The Pentium M processor bus saves power aggressively when idle; it carefully controls its input buffer's senseamplifiers that sample the activity on the bus. When the bus is idle, all sense amplifiers are disabled and do not consume any power. When the bus is active and address and data are driven on the bus, the input buffers are enabled in advance to ensure all information is captured with no delay.

The bus features many innovative mechanisms to reduce power while maintaining performance. Several of them are described below.

**DPWR#:** Data Bus Power Control. This is a special signal driven by the 855PM chipset whenever data are transferred to the processor. DPWR# is used to dynamically enable the processor's 64-bit data bus input sense amplifiers and their related controls (~80 signals) only when data are transferred to the bus.

**BPRI Control**: This is a method to achieve the DPWR# functionality for the address bus. BPRI# is asserted whenever the 855PM chipset attempts to drive the bus. It is used to dynamically enable the 32-bit address bus

input sense amplifiers and their related controls (~40 signals) only when a transaction is issued to the bus.

Low Vtt: The Intel Pentium M processor's I/O buffers work at a low voltage of 1.05V (Vtt). The low Vtt is an essential element to reduce the bus power. However, operating at low Vtt introduces a new set of problems because the I/O buffer is working at the low linear point, which affects the buffer's characteristics. The bus includes a special Resistor Compensation (RCOMP) method to adjust the buffer strength dynamically during run time. It accommodates the impacts of temperature, voltage drift, and bus topology. Thus, at any thermal and power state the Pentium M processor bus has full impedance termination. It has split power planes that allow setting the I/O operating voltage to a fixed value of 1.05V even though the core may be operating at a higher Enhanced Intel SpeedStep technology operating point.

**PSI:** Power Status Indicator. The Pentium M processor bus provides a signal to reduce the overall platform power (not just the processor power!). This signal is driven by the processor to control the current consumption of the Voltage Regulator (VR) when the processor operates at a low power state.

## LOWER-LEVEL POWER OPTIMIZATIONS

This section describes several lower-level mechanisms that demonstrate the power awareness of the Intel Pentium M processor.

A simple, yet effective method that was pursued in order to reduce power was to identify idle logic and shut it off. This was done locally and globally.

Locally, the design was thoroughly reviewed for any inefficiency during idle states. The goal was to gate the clocks as much as possible. Ideally, the clocks should be shut off for each pipe stage separately. However, if such a naive approach is used, the added complexity may sometimes outweigh the gain. In these cases the logic is shut off for the entire unit only at the end of the operation, resulting in a smaller power saving.

Globally, idle time identification is done at a higher microarchitectural level, when the unit alone cannot identify the idle period. For example, the first stage of a unit is always kept awake in order to respond to incoming messages. So, the goal was to create a few central controllers that can microarchitecturally identify or predict idle periods and instruct the units to reduce power (either by shutting off their clocks or by disabling parts of their logic). Also, the prediction logic should allow operations to resume seamlessly with no performance penalty.

One example for such a power predictor is the "Allocate stall" predictor. Whenever the Reorder-Buffer is full, the Allocator stalls the pipeline. However, the Allocator cannot tell if the Reorder-Buffer will remain full on the next cycle. It therefore needs to re-evaluate the stall condition every cycle. It turns out that in many cases when the Reorder-Buffer is full, it stays so for very long periods. Therefore the power penalty in this case is high. A specialized logic was defined to collect information from the Reorder-Buffer and other units in order to predict the nature of the next cycle. This logic instructs the Allocator to hold on to the stall condition and shut off its clocks.

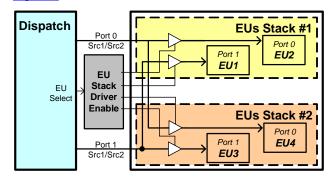

Another type of a microarchitectural power feature identifies the logic that is necessary for a specific operation and activates only that part of the processor. Here are two examples for an implementation of such a power feature.

In a conventional processor, all the units of a specific execution port electrically share the same source bus wires. However, power can be saved if instead of driving the sources to all the execution units (EUs), only the wires that belong to the target EU are driven. Therefore, the Pentium M processor execution units were divided into a few segments (stacks), and a special logic was created in order to control the flow of data to every stack according to its actual destination (see Figure 8).

Figure 8: Execution units stacking

A generic processor operates on several different data types with different widths. In an IA32 processor there are integer operations, operating on 32 bits, multimedia operations, operating on 64 bits or 128 bits, and floatingpoint operations, operating on 80 bits. The most common instructions are integer instructions that access only a limited set of registers and use only 32-bit data values. Toggling a wider bus and reading from a bigger register file consumes more power than is actually required. The Intel Pentium M processor saves power by identifying integer operations in advance and activating only the appropriate hardware (see Figure 9). The savings include the narrower buses to and from the EU during dispatch and writeback, and also other elements in the renaming logic that are not accessed while an integer operation is executing. This effectively transforms the processor into a 32-bit machine that utilizes only resources needed for integer operations while operating on integer data types.

| Rename                       |                               | Dispatch         |                                   |                                    | EUs          |                                   |

|------------------------------|-------------------------------|------------------|-----------------------------------|------------------------------------|--------------|-----------------------------------|

| FP/XMM<br>Register<br>Rename | Integer<br>Register<br>Rename | Control<br>Array | Upper<br>Data<br>Array<br>[85:32] | Integer<br>Data<br>Array<br>[31:0] | WB<br>[85:0] | Data<br>[31:0]<br>Data<br>[85:32] |

|                              |                               | 1                |                                   |                                    | Source       | Write                             |

| Enable 1                     |                               | Integer          |                                   |                                    | [85:0]       | Enable                            |

| if non<br>Integer            |                               |                  |                                   |                                    |              | if non<br>Integer                 |

Figure 9: Early identification of EU width

#### ENHANCED INTEL SPEEDSTEP TECHNOLOGY

High-performance processors tend to have high power consumption during execution. This is a simple derivative of the active power equation

$$Power = \alpha * C * V^2 * F$$

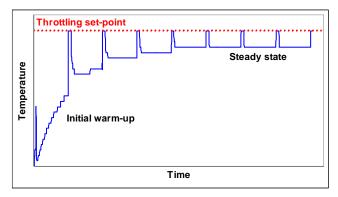

where V is the core voltage, F is the operating frequency, and  $\alpha$  is the activity factor. However, proven mobile usage models, indicate that typical usage is bursty in nature, requiring high performance only for short bursts of time. Average power reduction can be achieved by switching voltage and frequency to a lower operating point, when demand is low. The efficiency of the solution depends on the ability to execute this operationpoint switch frequently and efficiently, to track demand.

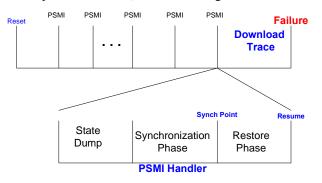

Previous generations of Intel mobile processors implemented the Intel basic SpeedStep technology [8]. It switches both voltage and frequency between two distinct states: Lowest Frequency Mode (LFM) and Highest Frequency Mode (HFM) by using the platform C3-idle state. While achieving low-power operation during LFM, the basic SpeedStep architecture does not fully address demand-based switching needs. The long system unavailability time during transitions limits the switching frequency due to interaction with streaming devices such as Audio Codec '97 (AC '97) and the Universal Serial Bus (USB). Additionally, having only two fixed operating points limits operating point optimization according to the load. The Intel Pentium M processor introduces a multi-point Enhanced Intel SpeedStep technology optimized for demand-based switching.

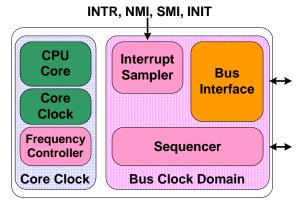

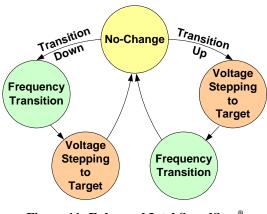

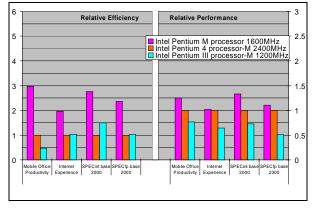

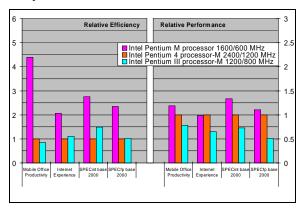

The Enhanced Intel SpeedStep technology attempts to address the following challenges: