Volume 06

Issue 02

Published, May 16, 2002

**ISSN 1535766X**

# Intel® Technology Journal

### Semiconductor Technology and Manufacturing

This issue of the Intel Technology Journal describes Intel's state-of-the-art logic and flash-memory technologies and how some of the key technology elements will evolve in the near future.

| Inside y | you'll find the | following | papers: |

|----------|-----------------|-----------|---------|

|----------|-----------------|-----------|---------|

130nm Logic Technology Featuring 60nm Transistors, Low-K Dielectrics and Cu Interconnects

Integration of Mixed-Signal Elements into a High-Performance Digital CMOS Process

Process Development and Manufacturing of High-Performance Microprocessors on 300mm Wafers

ETOX<sup>™</sup> Flash Memory Technology: Scaling and Integration Challenges Transistor Elements for 30nm Physical Gate Length and Beyond

> The Intel Lithography Roadmap

**Emerging Directions for Packaging Technologies**

More information, including current and past issues of Intel Technology Journal, can be found at: http://developer.intel.com/technology/itj/index.htm Volume 06

Issue 02

Published, May 16, 2002

**ISSN 1535766X**

# 21010 101010110

## Intel<sup>®</sup> Technology Journal Semiconductor Technology and Manufacturing

### Articles

| Preface                                                                                      | 3  |

|----------------------------------------------------------------------------------------------|----|

| Foreword                                                                                     | 4  |

| 130nm Logic Technology Featuring 60nm Transistors,<br>Low-K Dielectrics and Cu Interconnects | 5  |

| Process Development and Manufacturing of High-Performance<br>Microprocessors on 300mm Wafers | 14 |

| ETOX™ Flash Memory Technology: Scaling and Integration Challenges                            | 23 |

| Integration of Mixed-Signal Elements into a<br>High-Performance Digital CMOS Process         | 31 |

| Transistor Elements for 30nm Physical Gate Length and Beyond                                 | 42 |

| The Intel Lithography Roadmap                                                                | 55 |

| Emerging Directions for Packaging Technologies                                               | 62 |

### Preface

Since the invention of the integrated circuit some forty years ago, engineers and researchers around the world have worked on how to put more speed, performance and value onto smaller chips of silicon. By the end of this decade (2010) we at Intel want to reach the goal of 10 billion transistors on a single chip. This is a big challenge. Today we continue to break barriers to reach this goal. This issue (Q2, 2002, Vol. 6 Issue 2) of the *Intel Technology Journal* gives a detailed look into the exciting advances in the areas of transistor architecture, interconnects, dielectrics, lithography, and packaging.

This past year there have been many recent fundamental breakthroughs, particularly in five areas. Here we summarize some of those breakthroughs.

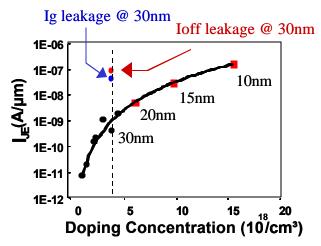

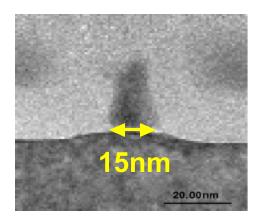

**Transistor size**: Intel's research labs have recently shown the world's smallest transistor, with a gate length of 15nm. We continue to build smaller and smaller transistors that are faster and faster. We've reduced the size from 70 nanometer to 30 nanometer to 20 nanometer, and now to 15 nanometer gates.

**Manufacturing process**: A new manufacturing process called 130 nanometer process technology (a nanometer is a billionth of a meter) allows Intel today to manufacture chips with circuitry so small it would take almost 1,000 of these "wires" placed side-by-side to equal the width of a human hair. This new 130-nanometer process has 60nm gate-length transistors and six layers of copper interconnect. This process is producing microprocessors today with millions of transistors and running at multi-gigahertz clock speeds.

**Wafer size**: Wafers, which are round polished disks made of silicon, provide the base on which chips are manufactured. Use a bigger wafer and you can reduce manufacturing costs. Intel has begun using a 300 millimeter (about 12 inches) diameter silicon wafer size, up from the previous wafer size of 200mm (about 8 inches). 300 millimeter is the size of a medium pizza in the United States, up from the previous size of a small pizza!

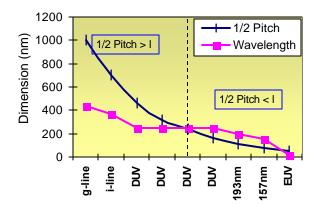

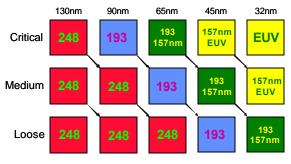

**Lithography**: Lithography is the technology used to 'print' intricate patterns that define circuits on silicon wafers. With our extreme ultraviolet (EUV) program, we've made a fundamental breakthrough in the area of lithography. EUV lithography is the technology that allows printing of lines smaller than 50nm. A few years ago, we realized that the light spectrums we were using were no longer scalable. We needed the shorter wavelengths of extreme ultraviolet beams. But rather than magnifying the beam through a glass lens as before, we now use mirrors. About five years ago we launched the industry consortium for EUV, and this year we demonstrated the first EUV using mirroring techniques.

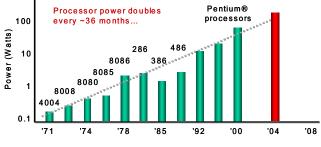

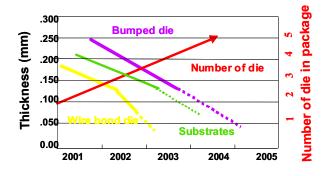

**Packaging**: A silicon chip is useless without its package. The package delivers the power the chip needs and transfers all the information into and out of the chip. BBUL ("Bumpless Build-Up Layer") packaging is a new microprocessor packaging technology that has been developed by Intel. It is called bumpless because, unlike today's packages, it does not use tiny solder bumps to attach the silicon die to the package wires. Instead of having the die on top, the die is embedded in the package. It has build-up layers because the package is "grown" (built up) around the silicon die rather than being manufactured separately and bonded to it. This package is smaller, improves package inductance characteristics, and is better for multi-chip packaging.

The seven papers in this Q2, 2002, issue of Intel Technology Journal discuss the details on fundamental advancements of silicon process and manufacturing, including improvements in current technologies of 130nm logic technology, manufacturing using 300mm wafers, flash memory, digital CMOS integrated with analog RF signal elements, and next-generation advancement underway in lithography, transistor structure, and packaging technologies.

### Foreword

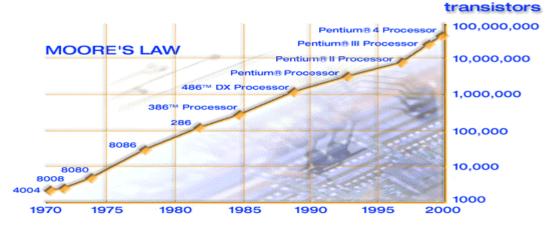

The semiconductor industry has made phenomenal progress since Robert Noyce invented the integrated circuit over 40 years ago. The fundamental driver has been the continued shrinking of feature sizes, allowing the exponential growth in device count that tracks the well-known <u>Moore's Law</u> first formulated by Intel co-founder Gordon Moore. Shrinking feature sizes allow more transistors to be packed onto a piece of silicon, with each one running at higher speeds. This combination translates into more computing capabilities, ultimately delivering better value to the end user. This exponential trend has driven the amazing computing and communications revolution that is profoundly changing our world. By most measures, the industry has progressed further than anyone imagined even as recently as 10 years ago.

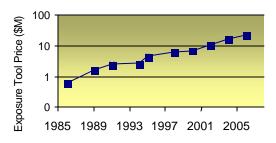

Making these increasingly dense and varied integrated circuits requires progress in many disciplines. New transistor materials and structures are required in order to meet new performance, speed and power objectives. New types of interconnect are required to speed signal transmission between devices. Lithography–the process of printing the intricate patterns on silicon–must break new barriers as feature sizes become ever smaller. Packaging also must become much more sophisticated to meet ever more stringent thermal management, power delivery, interconnect density and integration requirements. And all of these goals must be achieved in a cost-effective manner amenable to high-volume manufacturing.

Intel has been at the forefront of our industry since our founding in 1968, and today holds a leadership position with high-performance microprocessors, dense flash memories, and the ability to manufacture these very complex products in high volume. This issue of the Intel Technology Journal describes Intel's state-of-the-art logic and flash-memory technologies and how some of the key technology elements will evolve in the near future.

### 130nm Logic Technology Featuring 60nm Transistors, Low-K Dielectrics, and Cu Interconnects

Scott Thompson, Technology and Manufacturing Group, Intel Corporation Mohsen Alavi, Technology and Manufacturing Group, Intel Corporation Makarem Hussein, Technology and Manufacturing Group, Intel Corporation Pauline Jacob, Technology and Manufacturing Group, Intel Corporation Chris Kenyon, Technology and Manufacturing Group, Intel Corporation Peter Moon, Technology and Manufacturing Group, Intel Corporation Matthew Prince, Technology and Manufacturing Group, Intel Corporation Sam Sivakumar, Technology and Manufacturing Group, Intel Corporation Matthew Prince, Technology and Manufacturing Group, Intel Corporation Matthew Prince, Technology and Manufacturing Group, Intel Corporation Mark Bohr, Technology and Manufacturing Group, Intel Corporation

Index words: CMOS transistor, logic technology, copper interconnects

#### ABSTRACT

Transistor gate dimensions have been reduced 200X during the past 30 years (from 10mm in the 1970s to a present-day size of 0.06mm). The transistor and feature size scaling have enabled microprocessor performance to increase exponentially with transistor density and microprocessor clock frequency doubling every two years. In this paper we describe Intel's latest 130nm CMOS logic technology used to make high-performance microprocessors >3GHz.

#### **INTRODUCTION**

For more than 30 years, MOS device technologies have been improving at a dramatic rate [1-6]. A large part of the success of the MOS transistor is due to the fact that it can be scaled to increasingly smaller dimensions, which results in higher performance. The ability to consistently improve performance while decreasing power consumption has made CMOS architecture the dominant technology for integrated circuits. The scaling of the CMOS transistor has been the primary factor driving improvements in microprocessor performance. Transistor delay times have decreased by more than 30% per technology generation resulting in a doubling of microprocessor performance every two years. Recently, chip performance has also come to be limited by back-end

RC delay if low-resistance metal lines or low dielectric constant interlayer dielectrics are not used.

In this paper we describe Intel's 130nm logic technology that features 60nm gate length and 1.5nm gate-oxide transistors for high-performance and low-k interdielectrics with six layers of Cu interconnects. We first discuss transistor scaling. Next, we present data from our 130nm technology on 60nm transistors and copper interconnects with low-k Fluorinated SiO<sub>2</sub>. We conclude with static random access memory (SRAM) and microprocessor performance data.

#### TRANSISTOR SCALING OVERVIEW

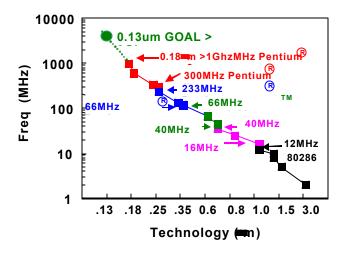

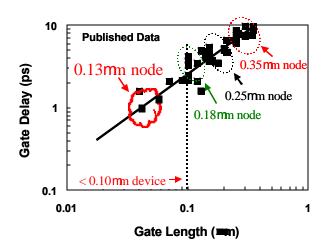

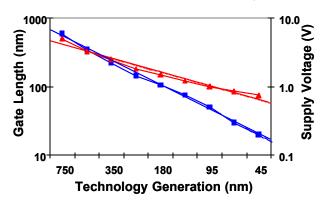

Transistor scaling has been the key driving force behind the rapid increase in microprocessor clock frequency. Figure 1 shows the scaling trend of clock frequency. The technology target for the 130nm node was to produce microprocessors at >3GHz.

### Figure 1: Microprocessor clock frequency vs. technology generation

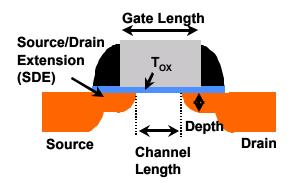

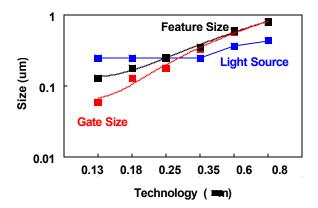

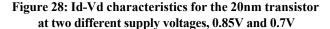

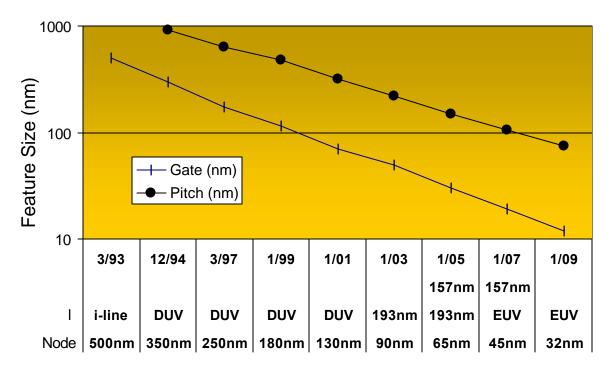

Two primary factors set the transistor speed and hence microprocessor clock frequency for a given design: transistor channel length and gate-oxide thickness (Figure 2). To reach the >3GHz goal, circuit simulations show that 60nm gate length and 1.5nm gate-oxide thickness are required for the 130nm technology node. The 60nm transistor requires a significant acceleration of the transistor feature size relative to the technology and light source.

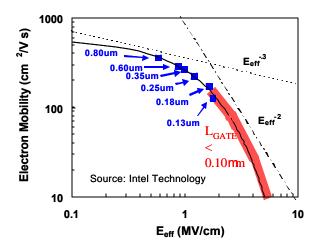

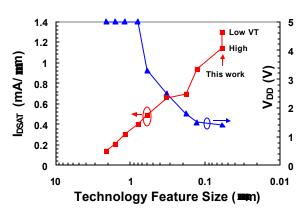

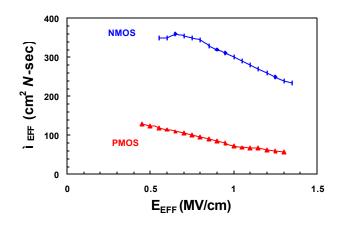

Figure 3 shows the trends of these key feature sizes versus technology generation. The 130nm technology node was designed for the fabrication of Intel<sup>o</sup> Pentium<sup>®</sup> 4 microprocessors in high-volume manufacturing. Once the Pentium 4 chip architecture is set, the transistor speed required for 3GHz operation can be determined. To obtain a clock frequency of >3GHz, it was determined that a 1.3mA/mm transistor saturation drive current would be needed. This value of drive current is significantly higher than the value in our 180nm technology ( $\sim 1.0 \text{mA}/\text{mm}$ ). 60nm transistors with 1.5nm physical oxide thickness will allow for CV/I close to 1ps (Figure 4) and saturation drive current of 1.3mA/mm (Figure 6). This drive current is the highest to date in high-volume production. Key to obtaining the high drive current is high channel mobility. The channel mobility decreases at higher effective oxide fields for the smaller feature size technology. The electron mobility is shown in Figure 5. The electron mobility is on the universal mobility curve even though the physical thickness of the oxide is only 1.5nm.

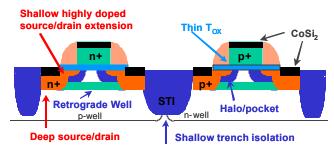

Figure 2: Cross-section drawing of a CMOS transistor

Figure 3: Technology feature size, wavelength light source, and transistor gate size vs. technology node

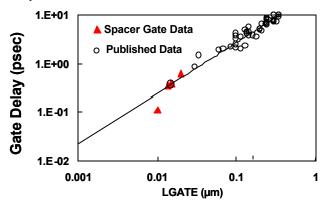

Figure 4: CV/I gate delay vs. transistor gate length

<sup>&</sup>lt;sup>o</sup>Intel and Pentium are registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Figure 5: Electron mobility vs. effective vertical electrical field

Figure 6: Transistor saturated drive current vs. technology feature size

#### **Process Flow and Technology Features**

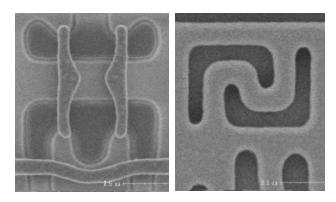

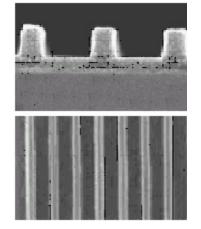

Front-end technology features include shallow trench isolation, retrograde wells, shallow abrupt source/drain extensions, halo implants, deep source/drain, and cobalt salicidation. Figure 7 shows a front-end cross section of the technology. The minimum pitches and thicknesses for the technology layers are summarized in Table 1. The rules enable a 2.0 um<sup>2</sup> 6-T SRAM cell (1.22 x 1.64 um). Figure 8 shows a top-down scanning electron micrograph (SEM) of the polysilicon gate conductor and the Metal 1 connections. The interconnect technology uses dual damascene copper to reduce the resistances of the six layers of interconnects. Fluorinated SiO<sub>2</sub> is used as an inter-level dielectric (k is measured to be 3.6).

Table 1: Layer pitch, thickness (nm) and aspect ratio

| LAYER       | <u>PITCH</u> | THICK | AR  |

|-------------|--------------|-------|-----|

| Isolation   | 345          | 450   | -   |

| Polysilicon | 319          | 160   | -   |

| Metal 1     | 293          | 280   | 1.7 |

| Metal 2,3   | 425          | 360   | 1.7 |

| Metal 4     | 718          | 570   | 1.6 |

| Metal 5     | 1064         | 900   | 1.7 |

| Metal 6     | 1143         | 1200  | 2.1 |

Figure 7: Cross-section drawing of 130nm technology front-end

Figure 8: Top-down SEM of polysilicon gate conductor and Metal 1 connections

#### **TRANSISTOR FEATURES**

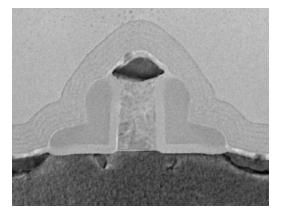

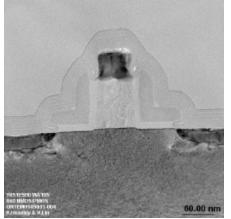

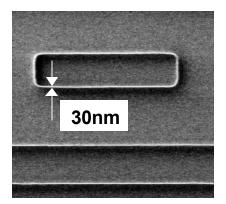

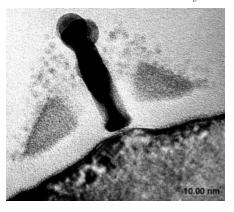

(a) Gate Length Dimension: Figure 9 shows a crosssectional transmission electron micrograph (TEM) for a transistor with a 60nm gate length and straight poly-Si sidewall profile as opposed to the notched poly used in the 180nm node [6]. Straight sidewall gates were chosen at the 130nm node since the source drain extension does not have to diffuse under the notch, thus allowing for shallower junctions to be fabricated. At aggressive gate lengths of 60nm, controlling short channel effects at low-threshold voltage, by using shallow junctions and abrupt halo doping, is key to achieving high linear and saturation drive currents.

Figure 9: TEM cross section of 60nm NMOS

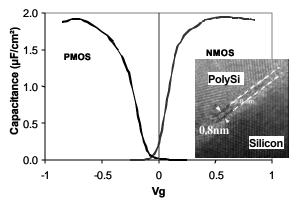

(b) 1.5nm Physical Gate-Oxide: In order to achieve high drive current and minimize short channel effects, a gateoxide process with a 1.5nm physical thickness was developed that meets performance, reliability, and manufacturability criteria (Figure 10). High-electron and hole mobilities are required to achieve high linear drive current, which can be missed in technology optimization, since transistor linear current is not reflected in a simple CV/I metric. Concerns have been raised that in ultra-thin oxides, gate-electrode-to-oxide interface scattering and high fixed charge due to nitridation reduce mobility. The measured mobility dependence on the effective oxide field, shown in Figure 11, demonstrates that high-electron and hole mobilities can be achieved for well-optimized gate oxides with a thickness of 1.5nm.

Figure 10: TEM of 1.5nm physical gate oxide

Figure 11: Mobility vs. effective electric field

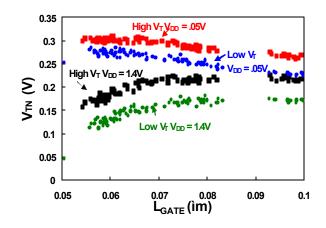

(c) Well-Halo and SD-Extension Engineering: A simple but ineffective way to offer high-saturation drive current at small gate lengths is to use high well-doping to raise the threshold voltage to control short channel effects. This approach offers low CV/I but does not improve product performance, for two reasons. First, the linear drive current will be significantly degraded (saturated drive current is not degraded at a fixed I<sub>OFF</sub> due to high drain-induced barrier lowering (DIBL)). Second, the high well-doping leads to increased threshold voltage variations due to gate length variation (present in the range of +/-10% L<sub>GATE</sub> for a modern technology). In this work we use retrograde wells, and low-energy, high-angle abrupt halo implants with shallow junctions formed by low-diffusion processing to control short channel effects. Figure 12 shows the N-channel threshold voltage versus gate length resulting in a linear threshold voltage of 300 and 270mV at a gate length of 60nm for the high- and lowthreshold devices, respectively. From Figure 12, DIBL for the 60nm NMOS devices is measured to be <100mV/V for high- and bw-threshold devices. Similar results have been achieved for p-channel devices.

Figure 12: V<sub>TN</sub> vs. L<sub>GATE</sub>

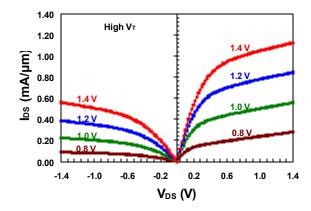

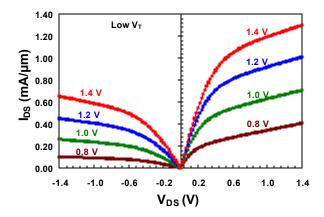

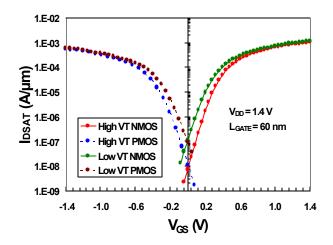

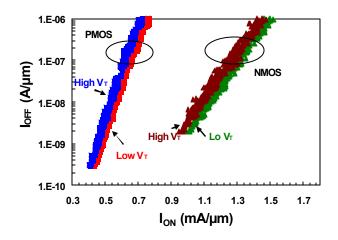

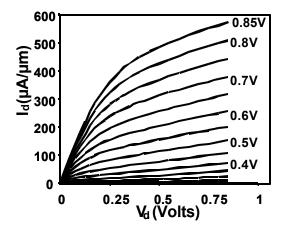

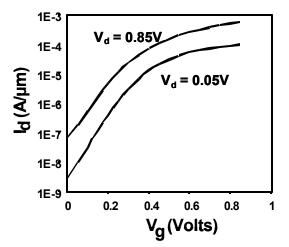

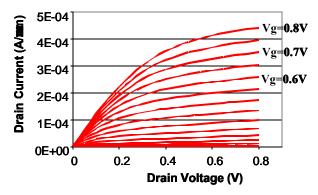

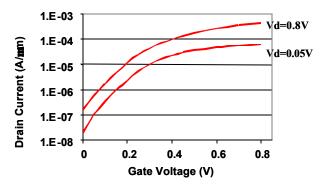

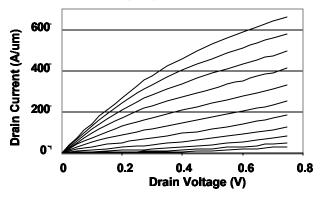

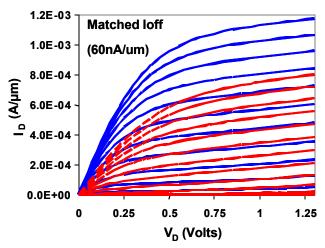

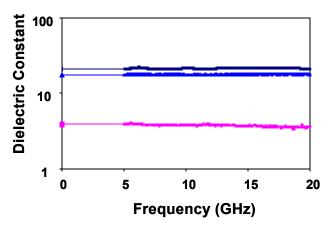

High  $V_T$  saturation drive currents are 1.14mA/um for Nchannel and 0.56mA/um for P-channel devices (Figure 13). Low  $V_T$  drive currents are 1.30mA/um for N-channel and 0.66mA/um for P-channel devices (Figure 14). Subthreshold slopes for both N-channel and P-channel highand low-threshold devices remain well controlled at less than 85mV/decade at  $L_{GATE}$ =60 nm (Figure 15). The  $I_{ON}/I_{OFF}$  ratio remains high for the aggressively scaled power supply voltage of 1.4V (Figure 16). Table 2 shows the transistor  $I_{ON}$  and  $I_{OFF}$  at 0.7 and 1.4 V.

Figure 13: I-V curves for high  $V_T$  device ( $L_{GATE}$ =60nm)

Figure 14: I-V curves for low  $V_T$  device ( $L_{GATE}$ =60nm)

Figure 15: Sub-threshold characteristics

Figure 16: I<sub>ON</sub> Vs I<sub>OFF</sub> (V<sub>DD</sub>=1.4V)

| Table 2 | : I <sub>on</sub> and | I <sub>OFF</sub> at 0.7 | and 1.4V | V <sub>DD</sub> |

|---------|-----------------------|-------------------------|----------|-----------------|

|---------|-----------------------|-------------------------|----------|-----------------|

| DEVICE                 | VDD<br>(V) | I <sub>OFF</sub> (N)<br>(nA/um) | I <sub>on</sub> (N)<br>(mA/um) | I <sub>on</sub> (P)<br>(mA/um) |

|------------------------|------------|---------------------------------|--------------------------------|--------------------------------|

| $\text{Low } V_{\tau}$ | 1.4        | 100                             | 1.30                           | 0.66                           |

| High $V_{\tau}$        | 1.4        | 10                              | 1.14                           | 0.56                           |

| $\text{Low } V_{\tau}$ | 0.7        | 20                              | 0.37                           | 0.19                           |

| High $V_{\tau}$        | 0.7        | 2                               | 0.32                           | 0.16                           |

In a modern microprocessor with six layers of interconnects, transistor loads are comprised of >50% interconnect capacitance. To obtain high product performance it is necessary to provide transistors with more than low CV/I; you also need high saturation and linear drive currents. Figure 6 shows the recent trend of saturation drive currents for Intel's process technologies. This work extends the trend to offer the highest drive current to date of 1.30mA/um for low-threshold N-channel devices.

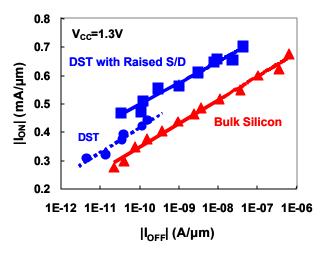

#### INTERCONNECTS

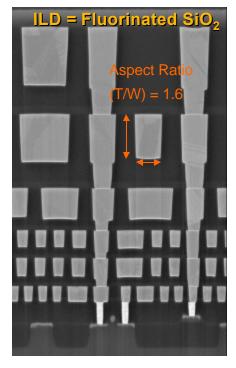

Chip performance is increasingly limited by the RC delay of the interconnect as the transistor delay progressively decreases while the narrower lines and space actually increase the delay associated with interconnects. Using copper interconnects helps reduce this effect. This process technology uses dual damascene copper to reduce the resistances of the interconnects. Fluorinated SiO<sub>2</sub> (FSG) is used as an inter-level dielectric (ILD) to reduce the dielectric constant; the dielectric constant k is measured to be 3.6. Figure 17 is a cross-section Scanning Electron Micrograph (SEM) image showing the dual damascene interconnects.

Figure 17: Cross-section SEM image of a processed wafer

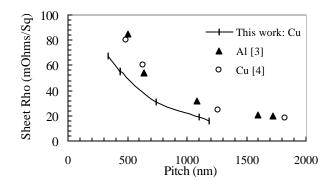

Table 1 lists the metal pitches. The pitch is 350nm at the first metal layer and increases to 1200nm at the top layer. Metal aspect ratios are optimized for minimum RC delay and range from 1.6 to 2. The first metal layer uses a single damascene process, and tungsten plugs are used as contacts to the silicided regions on the silicon and polysilicon. Unlanded contacts are supported by using an Si<sub>3</sub>N<sub>4</sub> layer for a contact etch stop. Copper interconnects are used because of the material's lower resistivity. The advantage is seen in Figure 18, where the sheet resistance is shown as a function of the minimum pitch of each metal layer and compared to earlier results from 180nm technologies using Al [6] and Cu [6]. The present technology exhibits 30% lower sheet resistance at the same metal pitch due to the use of Cu with high aspect ratios. The total line capacitance is 230fF/mm for M1 to M5 and slightly higher for the top layer.

Figure 18: Sheet resistance as a function of layer pitch

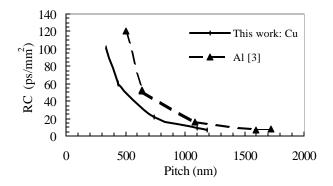

To benchmark the performance of interconnects, Figure 19 shows the RC delay in picoseconds per millimeter of wire. Data for each metal layer are shown as a function of the minimum pitch at that layer. For a given pitch, 50% reduction in RC is achieved by using Cu interconnects and FSG ILD.

Figure 19: RC delay for a wire length of 1mm as a function of layer pitch

#### **Performance Metrics**

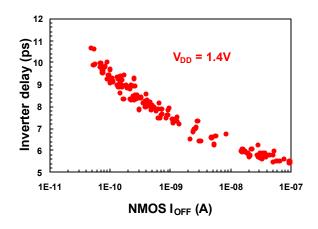

Figure 20 shows measured inverter gate delay versus nchannel off-state leakage for an unloaded ring oscillator (fan out =1) operating at 1.4V at room temperature. PMOS off-state leakage is fixed at 10nA/um for these devices. The delay per stage at 1.4V falls below 6psec when the off-state leakage is about 10nA/um.

Figure 20: Inverter delay (PMOS I<sub>OFF</sub> = 10nA/um)

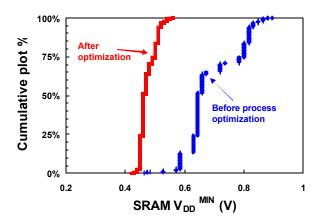

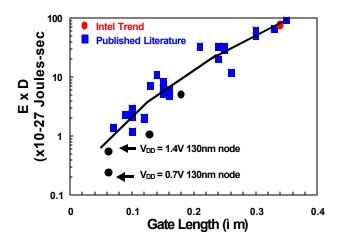

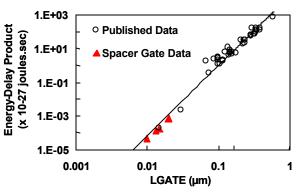

Power consumption is a growing concern for highperformance microprocessors with increasing clock frequency and transistor count. The best way to reduce power is to operate at a low supply voltage. Figure 21 shows that by improving device matching and eliminating defects that cause device mismatches, an 18Mb SRAM fabricated in this technology can operate at voltages of down to 0.5V. A metric, which comprehends both power and speed, is the energy-delay product. Figure 22 shows the estimated NMOS energy-delay product for a large number of published devices and for the devices reported in this paper. As evident from Figure 22, the NMOS energy-delay product is better than the published industry trend.

Figure 21: SRAM operation vs. voltage

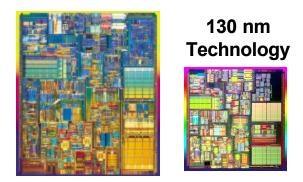

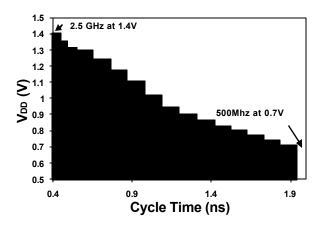

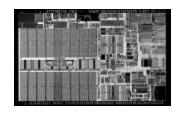

An 18 Mbit CMOS SRAM, Pentium<sup>o</sup> III and Pentium<sup>®</sup> 4 microprocessor were fabricated and used as yield and reliability test vehicles during the process development. Figure 23 shows the die photo of the Pentium 4 in the 0.18 and 0.13um technologies. The SRAM and microprocessor die yields are equivalent or better than past technologies at this point of time relative to ramping in high-volume manufacturing. The performance of the Pentium 4 processor is measured using the maximum clock frequency of operation. Figure 24 shows the schmoo plot for the Pentium 4, i.e., the maximum frequency as a function of voltage. At an operation voltage of 1.4V, the present design version of the Pentium 4 microprocessor has a clock frequency of 2.5GHz.

180 nm Technology

Figure 23: Comparison of 180nm technology to 130nm technology

Figure 24: Fmax schmoo plot for the Pentium<sup>®</sup> 4 processor

#### CONCLUSIONS

A 130nm-generation logic technology has been developed and is in high-volume manufacturing with high-performance transistors that can operate in the range of 0.7 and 1.4 V. The technology performance capabilities are demonstrated with ring oscillator delays of 6 ps/stage and with a Pentium<sup>å</sup> 4 processor operating at 2.5 GHz. The transistors can support microprocessors operating at >3GHz.

#### ACKNOWLEDGMENTS

The authors acknowledge the collaborative efforts of our colleagues in the Portland Technology Development Group, the Technology Computer Aided Design Group, and in the Corporate Quality and Reliability group.

#### REFERENCES

- M. Bohr, S.U. Ahmed, L. Brigham, R. Chau, R. Gasser, R. Green, W. Hargrove, E. Lee, R. Natter, S. Thompson, K. Weldon and S. Yang, *IEDM Technical Digest*, 1994, p. 273.

- [2] M. Bohr, S.S. Ahmed, S.U. Ahmed, M. Bost, T. Ghani, J. Greason, R. Hainsey, C. Jan, P. Packan, S. Sivakumar, S. Thompson, J. Tsai, and S. Yang, *IEDM Technical Digest*, 1996, p. 847.

- [3] S. Thompson, VLSI Symposium Technology Short Course, 1998.

- [4] S. Thompson, P.A. Packan, and M.T. Bohr, VLSI Symposium Digest, 1996, p. 154.

- [5] C.T. Sah, Fundamentals of Solid-State Electronics, 1991, p. 553.

<sup>&</sup>lt;sup>o</sup>Pentium is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

[6] S. Thompson, M. Alavi, R. Arghavani, A. Brand, R. Bigwood, J. Brandenburg, B. Crew, V. Dubin, M. Hussein, P. Jacob, C. Kenyon, E. Lee, B. Mcintyre, Z. Ma, P. Moon, P. Nguyen, M. Prince, R. Schweinfurth, S. Sivakumar, P. Smith, M. Stettler, S.Tyagi, M. Wei, J. Xu, S. Yang and M. Bohr, *IEDM Technical Digest*, 2001, p. 11.6.1-11.6.4.

#### **AUTHORS' BIOGRAPHIES**

**Scott Thompson** joined Intel in 1992 after completing his Ph.D., under Professor C. T. Sah at the University of Florida, on thin gate oxides. He has worked on transistor design and front-end process integration on Intel's 0.35, 0.25, 0.18, and 0.13mm silicon process technology design for the Intel<sup>®</sup> Pentium<sup>®</sup> and the Pentium<sup>®</sup> II microprocessors. Scott is currently managing the development of Intel's 90nm logic technology. His e-mail is <u>scott.thompson@intel.com</u>.

**Mohsen Alavi** joined Intel in 1986 after completing his Ph.D. in Electrical Engineering at Michigan State University on Schottky Barrier Diodes. He has worked on transistor and interconnect development and reliability of many of Intel's logic process technologies starting from the 1um process. More recently, he has been the reliability program manager for 0.13um and subsequently, 90nm logic technology development and is currently manager of LTD Q&R. His e-mail is <u>mohsen.alavi@intel.com</u>

Makarem Hussein is a Principal Engineer with Patterning Area of Portland Technology Development. He graduated from the University of Wisconsin-Madison in 1990 with a Ph.D. degree in Nuclear Engineering and Engineering Physics. He joined Intel in 1992, and since then has been working on developing dry etch processes. His most recent focus has been on the patterning of dielectric substrates for copper interconnect systems. He holds six US patents and has authored/co-authored more than 15 articles in the field of plasma etching and e-mail patterning technology. His is makarem.hussein@intel.com

**Pauline Jacob** joined Intel in 1994 after completing a Ph.D. in Chemical Engineering at the University of Washington. She has worked on diffusion process development since Intel's 0.35um process technology. Pauline is currently the diffusion group leader working on the development of Intel's 90nm gate-oxide module. Her e-mail is pauline.n.jacob@intel.com.

**Chris Kenyon** is a lithography group leader in Intel's Logic Technology Development organization. He joined Intel in 1996 and has worked primarily on Intel's gate patterning process since that time. He is currently responsible for developing the gate patterning process for

the 90nm CMOS node. He received his B.A. degree from Princeton University in 1990 and his Ph.D. degree from Caltech in 1996 in Physical Chemistry. His e-mail is <u>Chris.Kenyon@intel.com</u>

**Peter Moon** joined Intel in 1988 after completing his Ph.D. in Materials Science at the Massachusetts Institute of Technology. He has worked on process integration for Intel's 0.8, 0.35 and 0.13um silicon process technologies for Pentium® microprocessors including Intel's first use of shallow trench isolation (0.35um) and Intel's first use of copper interconnects (0.13um). Peter is currently leading the development of Intel's interconnect process for the 45nm process generation. His e-mail is Peter.Moon@intel.com

**Sam Sivakumar** joined Intel in 1990 after graduating from the University of Illinois. He is a member of the Portland Technology Development lithography group and has worked on patterning process development for a variety of Intel's logic processes. He is currently responsible for lithography development for Intel's 90nm logic process. His e-mail is <u>sam.sivakumar@intel.com</u>.

**Mark T. Bohr** joined Intel in 1978 after receiving an M.S.E.E. degree from the University of Illinois. He has been a member of the Portland Technology Development group since 1978 and has been responsible for process integration and device design on a variety of DRAM, SRAM, and logic technologies, including recent 0.35um and 0.25um logic technologies. He is an Intel Fellow and director of process architecture and integration. He is currently directing development activities on 0.18um and 0.13um logic technologies. His e-mail is mark.bohr@intel.com

**Matthew Prince** joined Intel in 1988 after graduating from Clarkson University in New York. Since 1989 he has developed ILD, W, and Cu CMP technologies. His e-mail address is <u>matthew.j.prince@intel.com.</u>

Copyright © Intel Corporation 2002. This publication was downloaded from <u>http://developer.intel.com/</u>.

Legal notices at http://www.intel.com/sites/corporate/tradmarx.htm

### Process Development and Manufacturing of High-Performance Microprocessors on 300mm Wafers

Sanjay Natarajan, Logic Technology Development, Intel Corporation Melton Bost, Logic Technology Development, Intel Corporation Derek Fisher, Logic Technology Development, Intel Corporation David Krick, Logic Technology Development, Intel Corporation Chris Kenyon, Logic Technology Development, Intel Corporation Chris Kardas, Logic Technology Development, Intel Corporation Chris Parker, Logic Technology Development, Intel Corporation Robert Gasser, Jr., Logic Technology Development, Intel Corporation

Index words: 300mm, Px60, P1260, 0.13mm, 130nm, Copy Exactly!

#### ABSTRACT

Over 35 years ago, Moore's Law established the nature of competition in the semiconductor industry by projecting a 2x transistor density improvement approximately every 18 months. Faced with increasingly challenging process technology issues, industry leaders such as Intel have had to achieve increasingly faster yield improvement and volume production ramps to maintain competitiveness. The Copy Exactly! methodology, which has been used since 1992 to transfer technologies and ramp new factories, has been instrumental in allowing Intel to meet these challenges.

The subject of this paper is the successful extension of Copy Exactly! to Intel's first 300mm process technology, P1260, to achieve rapid yield learning and volume production. P1260 replicates Intel's industry-leading 200mm 0.13mm CMOS process in performance, yield, reliability, and density, with SRAM cell sizes below 2mm<sup>2</sup> [1]. Intel has used the Copy Exactly! methodology for several generations with documented success, and we present perhaps the most compelling evidence to date of its utility: accurate replication of an industry-leading 200mm 0.13mm CMOS process on a 300mm wafer size using a completely new process equipment set.

#### **INTRODUCTION**

#### **Moore's Law**

In 1965, Gordon Moore, then R&D manager at Fairchild Semiconductor and now Chairman Emeritus of Intel Corporation, characterized the rate of progress in the semiconductor industry and arrived at an astounding conclusion: the density of transistors per integrated circuit (IC) had been doubling at regular intervals and would continue to do so indefinitely [2].

The observation, later termed "Moore's Law," has been extremely influential in the semiconductor industry, even to the point of becoming self-fulfilling. Since Moore's Law has accurately predicted past IC growth, it is also viewed as a method for predicting future trends, setting goals for innovation, directing the pace of the technology treadmill, and ultimately defining the nature of industry competition [3].

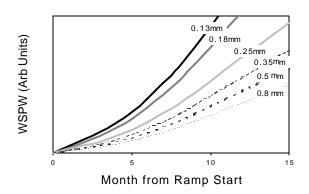

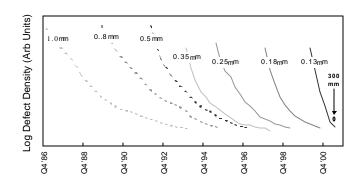

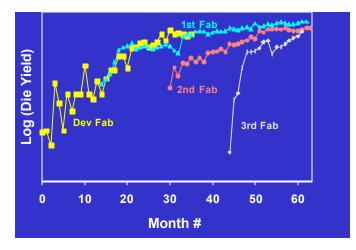

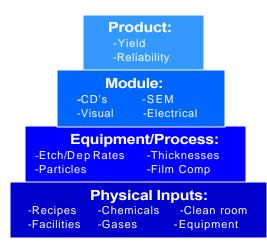

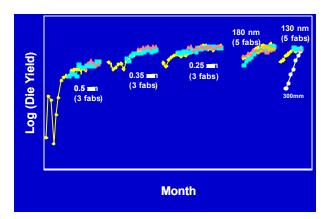

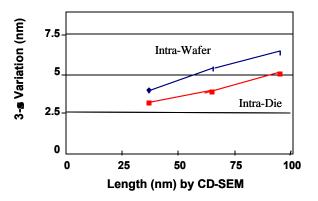

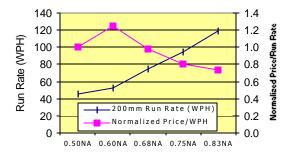

Delivering the regular progress dictated by Moore's Law in the face of increasingly complex process technologies requires steady improvements in the pace of yield learning and volume manufacturing capability. Figures 1 and 2 illustrate this trend for Intel's process technologies. Figure 1 shows the steadily increasing rate of production ramp for each of the last six process generations. Across these six generations, there has been a 4x increase in the ramp rate, measured in wafer starts per week per Fab. In addition, this increase has been achieved across more Fabs each generation. The net result is a greater than 20x increase in normalized die output in early ramp over the past six generations. Figure 2 illustrates the rapid increase in yield-learning trends over the last seven generations. The graph shows defect learning rates (the y-axis is the logarithm of defect density, so lower is better) for Intel technologies from the start of process development through initial production. There are three key points in this data. First, the elapsed time from the start of development to the point of high yield is decreasing with subsequent technology generations. Second, the inflection point, where yield learning slows down, is occurring at higher yields with subsequent generations. Finally, the time between new process introductions is decreasing. The net result is a greater than 5x increase in normalized good die per wafer at the start of production, over the past seven generations.

These continuously increasing ramp rates and everimproving yield-learning rates have been instrumental in maintaining Intel's leadership in the technology race, as defined by Moore's Law. There are three primary methods that enable rapid yield learning and manufacturing ramp. The first is predictive in-line metrology to shorten the cycle time for yield improvement feedback. The second is designing the process for manufacturability and performance, including using advanced process control and developing new materials. The final method is the Copy Exactly! process for transfer and ramp. The first two methods are discussed in detail elsewhere [4]. This paper focuses on Copy Exactly!.

Figure 1: Intel high-volume production ramp rates

Figure 2: Intel defect density trends

#### **COPY EXACTLY!**

Up to Intel's Imm process technology, die yields were becoming increasingly harder to match as processes were transferred from development to manufacturing facilities. During the 1mm process transfer, the first production Fab attempted to copy the development Fab closely while the second and third Fabs instituted changes (intended to be process improvements) during transfer. The results, shown in Figure 3, are striking. The so-called improvements actually resulted in an up to 10x *reduction* in die per wafer compared to the development Fab and first production Fab. This phenomenon led to the development of the Copy Exactly! methodology.

Figure 3: The birth of Copy Exactly!

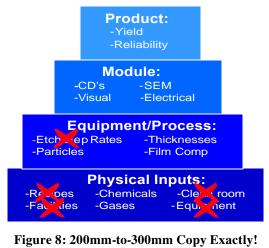

The current Copy Exactly! methodology used at Intel is shown in Figure 4. The key principle behind Copy Exactly! is that Fabs running a given process technology strive to be matched in every respect except where prohibited by hard barriers. Physical inputs, such as chemical sources and purities, facilities, and hookups are all derived from the same specifications. Likewise, equipment configurations and process recipes are matched exactly, and monitors that predict yield, reliability, and performance are all matched to within 1.5s. Once matched, changes are coordinated through cross-Fab joint engineering teams. Audits of equipment configurations and process monitors are routinely done to ensure ongoing matching. High-level tactical and strategic changes are executed in all Fabs under joint engineering and management structures.

Figure 4: Current Copy Exactly! methodology

Figure 5 shows the benefit this methodology has brought since the 0.5mm technology generation. In contrast to the range of die yields observed in the 1mm generation without Copy Exactly!, every generation from the 0.5mm generation to the most recent 0.13mm generation has seen multiple Fabs started with matched die yields.

Figure 5: Die yield matching with Copy Exactly!

#### OVERVIEW OF INTEL'S 0.13mM LOGIC TECHNOLOGY

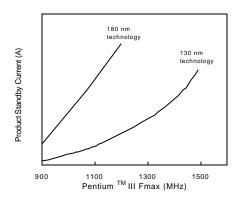

Most recently, Intel led the industry in 2001 with the volume manufacturing ramp of a 0.13mm CMOS technology featuring 70nm dual V<sub>t</sub> transistors, copper and low k (dielectric constant) interconnects and 2mm<sup>2</sup> SRAM cell sizes [1]. Table 1 summarizes the design rules for this process technology. Figures 6 and 7 illustrate Pentium<sup>O</sup> III processor die size and show the relative performance between this technology and the previous 0.18mm process generation. The transition from 0.18mm to 0.13mm process technology yields a greater than 40% increase in product frequency.

Figure 6: Pentium<sup>®</sup> III die on 0.13**m** process

| <u>Layer</u> | Pitch (nm) | Thicknes | ss(nm) Aspect Ratio |  |

|--------------|------------|----------|---------------------|--|

| Isolation    |            | 345      | 450 -               |  |

| Polysilicor  | n 319      | 160      | -                   |  |

| Metal 1      | 293        | 280      | 1.7                 |  |

| Metal 2, 3   | 425        | 360      | 1.7                 |  |

| Metal 4      | 718        | 570      | 1.6                 |  |

| Metal 5      | 1064       | 900      | 1.7                 |  |

| Metal 6      | 1143       | 1200     | 2.1                 |  |

|              |            |          |                     |  |

Table 1: Intel's 0.13mm CMOS design rules

<sup>&</sup>lt;sup>o</sup>Pentium is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

Figure 7: Pentium<sup>®</sup> III performance on 0.13mm and 0.18mm processes

#### **300mm Wafer-Size Conversion**

Intel chose the 0.13mm generation to make the wafer size change from 200mm (8") to 300mm (12"). This wafer size increase is part of an ongoing evolution beginning over 30 years ago with 1" wafers. The key driver for wafer size increase is cost reduction. The larger wafers provide a 2.25x increase in area and, due to the rectangular die size, an even larger increase in die per wafer. Manufacturing costs per wafer scale at less than this rate, so there is an overall reduction in cost per die at the larger wafer size.

The 300mm wafer size also brought a unique challenge. For the first time, the wafer size had grown large enough to pose an ergonomic hazard. A full lot of 300mm wafers weighs 18 lbs., and manual handling of 300mm wafers is prohibited due to ergonomic risks. In contrast, a full lot of 200mm wafers weighs 8 lbs. and is much smaller than a lot of 300mm wafers. 200mm wafer lots are routinely handled manually. The requirement for automated and mechanically-assisted wafer handling posed by the 300mm wafer size translates into longer cycle times for routine Fab tasks and ultimately translated into overall delays during process development.

The principal issue, however, in wafer size conversions is that the equipment set and process recipes must be completely changed to support the larger wafer. 300mm process equipment was selected using a rigorous and data-based approach. Similarity to the existing 200mm toolset was not a major factor during equipment selection: technical capability, cost, extendibility to future technologies, and productivity were. This selection process delivered a highly capable and productive toolset that could be reused for future technologies, but it drove changes away from well-characterized but less productive toolsets that had been operating, in some cases, for many years in Intel Fabs. A state-of-the-art process such as Intel's 0.13mm process has several-hundred process steps using 50-100 unique process tools. For every step, recipes must be rewritten to accommodate the larger wafers, but the higher-level goal is that the 300mm process must be essentially identical to the 200mm process in performance, reliability, and yield. With a completely new toolset and recipes that could not be simply copied or scaled, Intel faced a huge challenge in matching outputs between its 200mm and 300mm technologies. To meet the challenge, the Copy Exactly! process was adapted. This adaptation is described in the next section.

#### **300MM COPY EXACTLY!**

The development of the 300mm 0.13mm process used a modified Copy Exactly! process. Because the equipment was, by definition, different, and facility changes had to be made to accommodate the new equipment and new wafers, many of the physical inputs could not be matched. Figure 8 illustrates this. At the physical input level, recipes, facilities, equipment, and cleanroom were all not matched to 200mm. At the equipment and process level, many characteristics could not be matched because the tools either operated in different regimes from their 200mm equivalents or were based on different operating principles altogether.

However, to achieve matched output at the highest level, matching to 200mm was very extensive in other areas. To a large extent, chemicals and gases were matched, in some cases sharing a common distribution system with 200mm. Recipes were optimized for 300mm based on scaling 200mm recipes wherever possible, matching tool-level outputs to 200mm wherever possible, and always matching critical inputs to tools. "Critical inputs" are defined as those that have an impact on the wafer beyond their intended process step. For example, temperature in a thermal oxidation operation is considered a critical input because, in addition to modulating the film properties (the intended process step), temperature may also have an unintended impact on dopant diffusion and activation.

Critical outputs such as film thickness, profiles, and electrical properties were matched to 200mm within 1.5s. Variability was targeted to be equivalent or better than 200mm. The results of applying this methodology are presented in the next section.

methodology

#### RESULTS

We now review several key metrics of our 300mm 0.13mm process and compare them to the 200mm process. We begin with module-level data, characterizing the matching of specific tools or subsets of the overall process. We then report matching data on transistor and Pentium<sup>6</sup> 4 processor product performance, yield, and reliability. The data shown are a representative sample of all such indicators. In general, all data are matched between 200mm and 300mm to a similar degree. Across the board, the data show excellent matching between the 200mm and 300mm 0.13mm processes.

#### **Module-Level Matching**

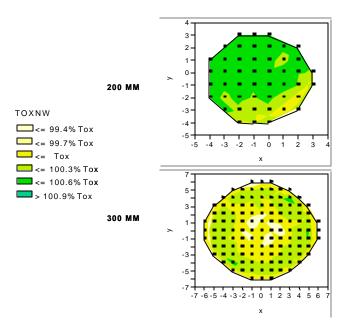

Figure 9 shows within-wafer matching for a representative in-line key monitor. Shown here are 200mm and 300mm wafer maps of gate-oxide thickness. The data show that 300mm wafers have slightly better within-wafer gate-oxide thickness variation than 200mm wafers.

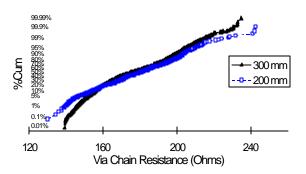

Figure 10 shows cumulative distributions for back-end Via resistances for 200mm and 300mm wafers. Via resistance is an integrated measure of interconnect electrical performance. As the data show, 200mm and 300mm Via resistances are closely matched.

Figure 9: 200mm/300mm within-wafer gate oxide

#### Figure 10: 200mm/300mm Via resistance distribution

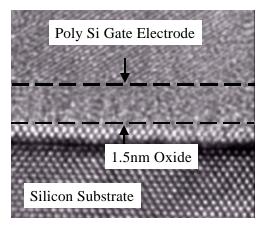

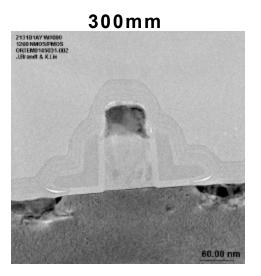

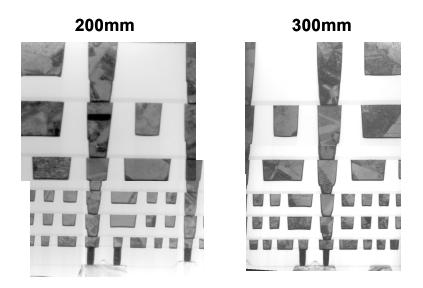

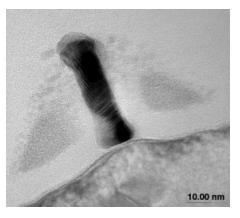

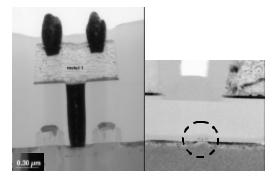

Figures 11(a) and 11(b) show Transmission Electron Microscope (TEM) cross-sections of 200mm and 300mm gate electrodes. These are approximately identical, nonminimum gate-length transistors. Profiles and critical film thicknesses are well matched. Slight differences in the film conformality and interfaces are evident. These are unavoidable differences caused by configuration differences between the 200mm and 300mm tools.

Figure 12 shows a TEM cross-section of the complete 6layer interconnect system. Profiles and thickness are virtually identical between 200mm and 300mm.

<sup>&</sup>lt;sup>o</sup>Pentium is a trademark of Intel Corporation or its subsidiaries in the United States and other countries.

200mm

Figure 11(a): 200mm gate electrode TEMs

Figure 11(b) : 300mm gate electrode TEMs

Figure 12: 200mm/300mm interconnect TEMs

#### **Performance Matching**

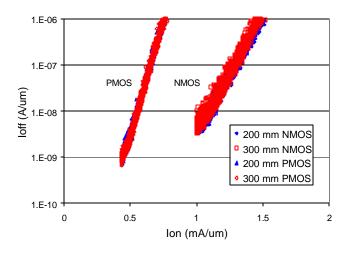

Figure 13 shows a basic transistor matching graph between 200mm and 300mm. Saturated drive current (Idsat) is plotted against off-state leakage (Ioff) for both 200mm and 300mm NMOS and PMOS transistors. The data show that the 200mm and 300mm devices are perfectly matched across a wide range of Ioff.

Figure 13: 200mm/300mm transistor Ion/Ioff

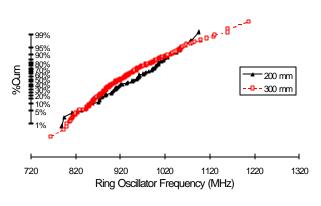

Figure 14 shows a circuit-level matching metric. The graph is a cumulative distribution of ring oscillator test circuit frequencies on 200mm and 300mm wafers. Again, the data indicate that the circuit operating frequencies are perfectly matched.

Figure 14: 200mm/300mm ring oscillator circuit frequency

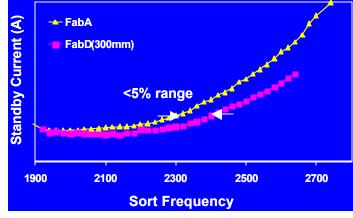

Figure 15: Pentium<sup>®</sup> 4 sort frequency vs. standby current

Finally, Figure 15 shows a normalized performance comparison for the Pentium<sup>®</sup> 4 product. The graph shows sort frequency graphed against product standby current. The 300mm product speed is within 5% of the reference 200mm population, matched to within normal variability.

#### Yield Matching

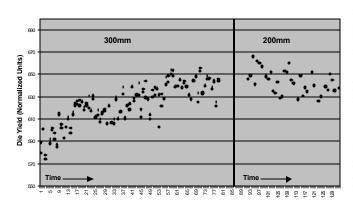

Figure 16 shows normalized die yield for 300mm and 200mm as a function of time. 300mm die yield at the start of development is lower than 200mm, which is shown starting after initial ramp. Rapid yield learning, facilitated by the ability to copy 200mm learning, enabled steadily improving die yields to the point where 200mm and 300mm die yields are matched at the point of the 300mm initial ramp.

#### **Reliability Matching**

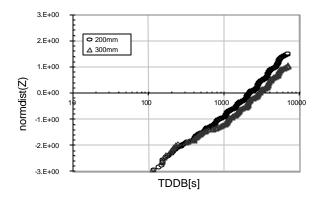

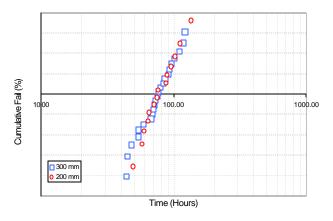

Figure 17 shows a key transistor reliability metric, gateoxide time-to-breakdown. The data are shown as a normalized distribution function of time-dependent dielectric breakdown (TDDB) in seconds. Both 200mm and 300mm are well matched in gate-oxide reliability.

Figure 18 shows a key interconnect reliability metric, electromigration fail rate. The data are shown as a normalized distribution function of time-to-fail. Again, both 200mm and 300mm are well matched.

Figure 16: 200mm/300mm normalize die yield

Figure 17: Gate oxide 200mm/300mm time-to-fail

Figure 18: Electromigration cumulative fail rate

#### CONCLUSION

For over 35 years, Moore's Law has set a rapid pace for progress in the semiconductor industry. With the continuously increasing technical challenges for silicon technology development, increasingly rapid yield learning and volume manufacturing ramp rate have been instrumental in maintaining Intel's technology leadership.

In this paper, we discussed the implementation of Intel's industry-leading 0.13mm logic technology on the 300mm wafer size and associated process equipment. The 0.13mm process has been ramped to volume production in multiple factories and on both 200mm and 300mm production lines at record yields, quality, and ramp rate. Rapid development of Intel's first 300mm wafer-size technology, well matched to the 200mm state-of-the-art process, is a critical milestone for future competitiveness. The adaptation of proven Copy Exactly! methods is the key element that enabled successful conversion to the 300mm wafer size and sets the stage for Intel's continued leadership in the semiconductor industry.

#### ACKNOWLEDGMENTS

The authors thank the many outstanding engineers and technicians in the Logic Technology Development and 300mm OHT organizations who are responsible for developing, ramping, and transferring Intel's P1260 logic technology.

#### REFERENCES

- [1] Tyagi, S., et. al., "A 130nm Generation Logic Technology Featuring 70nm Transistors, Dual Vt Transistors and 6 layers of Cu Interconnects," *IEDM Technical Digest*, December, 2000, pp. 567-570.

- [2] Moore, G.E. "Cramming More Components Onto Integrated Circuits," *Electronics Magazine*, Vol. 8, April, 1965, pp. 114-117.

- [3] Schaller, R.R. "Moore's Law: Past, Present, and Future," *IEEE Spectrum*, Vol. 34, Issue 6, pp. 52-59.

- [4] Gasser, Jr., R.A., "Yield Learning and Volume Manufacturing of High-Performance Logic Technologies on 200mm and 300mm Wafers," *IEDM Technical Digest*, December, 2001, pp. 599-601.

#### **AUTHORS' BIOGRAPHIES**

Sanjay Natarajan is a process integration group leader in Intel's Logic Technology Development organization. He joined Intel in 1993 and has held numerous positions in both factory automation and process integration. He is presently responsible for transistor integration for Intel's 65nm CMOS process technology. Prior to this, he led transistor integration for Intel's first 300mm process technology, a 0.13mm CMOS process matched to Intel's 200mm technology. He received his B.S., M.S., and Ph.D. degrees from Carnegie Mellon University, all in Electrical Engineering. His e-mail is <u>Sanjay.Natarajan@intel.com</u> **Melton Bost** is a process integration group leader in Intel's Logic Technology Development organization. He joined Intel in 1987 and has worked primarily in back- end process integration since that time. He is presently responsible for the P1260 backend process technology. He received his B.S.E. degree from Duke University in 1978, his M.S.E. degree from Stanford University in 1979, both in Materials Science, and his Ph.D. degree from Colorado State University in 1987 in Electrical Engineering. He is the author of numerous technical papers and holds six patents. His e-mail is <u>Melton.Bost@intel.com</u>.

Derek Fisher is the P1260 Yield Group Leader in Intel's Logic Technology Development organization. Since 1994, he has been responsible for Defect Metrology Roadmaps and participated in Fab startup and process transfer activities from P854 to P1260. He joined Intel in Ireland in 1991 and worked on P652 to P852 transfer and yield improvement. Prior to that, he worked in manufacturing development and process roles for National Semiconductor, Philips Research, and Motorola. He graduated from Strathclyde University in 1983. His e-mail is Derek.G.Fisher@intel.com

**David Krick** is the equipment startup coordinator for Intel's Logic Technology Development organization. He joined Intel in 1989 as a process engineer and has held numerous process engineering and management positions. He is currently responsible for coordinating the startup of Intel's newest 300mm technology development facility, D1D. Prior to this, he managed the successful startup of D1C, Intel's first 300mm factory. He holds three patents. Krick received his B.S. degree in Electrical Engineering and his M.S. degree in Engineering Science, both from Pennsylvania State University. His email is David.T.Krick@intel.com

**Chris Kenyon** is a lithography group leader in Intel's Logic Technology Development organization. He joined Intel in 1996 and has worked primarily on Intel's gate patterning process since that time. He is currently responsible for developing the gate patterning process for the 90nm CMOS node. He received his B.A. degree from Princeton University in 1990 and his Ph.D. degree from Caltech in 1996 in Physical Chemistry. His e-mail is <u>Chris.Kenyon@intel.com</u>

**Chris Kardas** is a process engineering group leader in Intel's Logic Technology Development organization. Since joining Intel in 1984, he has worked on a variety of Etch modules where he holds a patent. Most recently he has been working in the area of lithography and is presently responsible for P1260 and P1212 front-end layers. He received his B.S.E.E. degree from the University of Illinois in 1984. His e-mail is <u>Chris.Kardas@Intel.com</u>. **Chris Parker** is a senior process engineer in Intel's Logic Technology Development organization. He joined Intel in 1998 and has worked on front-end oxidation and gate development. He is presently responsible for the development of alternative gate dielectric processes for 300mm P126x technologies. He received his B.S.E.E. degree from Auburn University and M.S. and Ph.D. degrees in Electrical Engineering from North Carolina State University. His e-mail is <u>Chris.PTD.Parker@intel.com</u>

**Robert A. Gasser, Jr.** is Vice President, Technology & Manufacturing Group, and Director, Components Research. He is responsible for research and development of process technologies used to build future Intel logic devices that will be in production five to ten years from now. He joined Intel in 1982 as a Technology Evaluation Engineer. Most recently, Gasser was responsible for the development of Intel's 0.18-micron logic process technology (P858) and 300mm, 130nm logic technology (P1260) and 90nm logic technology (P1262). Gasser received his B.A. degree in Physics from Reed College in 1980. He received his M.S. degree in Materials Science from Stanford University in 1982. Gasser has written numerous technology papers and holds five patents. His e-mail is Bob.Gasser@intel.com.

Copyright © Intel Corporation 2002. This publication was downloaded from <u>http://developer.intel.com/</u>.

Legal notices at http://www.intel.com/sites/corporate/tradmarx.htm

### ETOX<sup>TM</sup> Flash Memory Technology: Scaling and Integration Challenges

Al Fazio, California Technology and Manufacturing, Intel Corp. Stephen Keeney, California Technology and Manufacturing, Intel Corp. Stefan Lai, California Technology and Manufacturing, Intel Corp.

Index words: Flash memory, ETOX<sup>TM</sup>, Intel StrataFlash<sup>®</sup> memory, Moore's Law

#### ABSTRACT

The 0.13mm flash memory technology that started highvolume manufacturing in the first quarter of 2002 is the eighth generation of flash technology since its first conception and development in 1983. The scaling has been accomplished by improved lithography capability as well as many process architecture innovations. In this paper, the key scaling challenges as well as the key innovations are presented. It is projected that the current planar cell structure can be scaled to the 65nm node. More revolutionary innovations, such as 3D structures, may be required for the 45nm node and beyond. To lower cost further, Intel StrataFlash<sup>o</sup> memory technology has been developed, which stores two bits of information in a single physical memory cell. The scaling innovations also allow for the integration of flash memories with highperformance logic for "wireless Internet on a chip" technology. These integration challenges are also discussed.

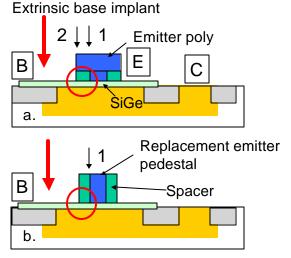

#### **INTRODUCTION**

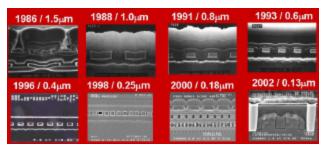

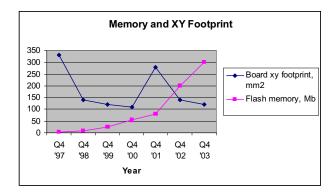

The in-system update and non-volatile capabilities of flash memories have enabled it to become the memory of choice for many emerging markets over time, originally as point of sales system configurations, then as PC BIOS components, and today for cell phones and handheld computing devices [1]. Similar to other memory technologies,  $ETOX^{TM}$  flash memory scaling follows Moore's law. Figure 1 shows SEM cross-sections of the memory cells for eight generations of flash memory technologies. The memory cell size for the first generation based on 1.5mm lithography was 36mm<sup>2</sup>, whereas the cell

size for the latest 0.13 mm lithography is 0.154 mm<sup>2</sup>. This represents an over 230 times cell size reduction over the eight generations. In the same period, the memory density for peak volume has increased one thousand fold from 64Kb to 64Mb.

#### Figure 1: Eight generations of flash technology

Although scaling the flash cell is important to achieve die size reduction or larger memories, the periphery transistors must also be scaled. Scaling the periphery transistors can be achieved by reducing the maximum voltages that need to be supported along with junction engineering and more advanced lithography and etch capabilities. The process architecture innovations and scaling of periphery transistors enables the integration of flash memories with high-performance logic for "wireless Internet on a chip" technology. In this paper we review the key process architecture innovations for scaling, the Intel StrataFlash memory technology and the key innovations required for "wireless Internet on a chip" technology. Table 1 outlines the key innovations for each generation of flash memory.

StrataFlash and ETOX are trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Table 1: Innovations by technology generation

| Technology Node | Key Innovation                                                                                      |

|-----------------|-----------------------------------------------------------------------------------------------------|

| 1.5 <b>m</b> m  | Established Flash                                                                                   |

| 1.0 <b>m</b> m  | Isolation rounding reduction for<br>improved cell gate alignment<br>Cycling reliability established |

| 0.8 <b>m</b> m  | Recessed LOCOS                                                                                      |

| 0.6 <b>m</b> m  | Self Aligned Source<br>Scaled Array Field Oxide                                                     |

| 0.4 <b>m</b> m  | Negative Gate Erase<br>Intel StrataFlash memory                                                     |

| 0.25 <b>m</b> m | Trench Isolation<br>Salicide                                                                        |

| 0.18mm [2]      | Self Aligned floating gate<br>Unlanded Contacts<br>Multiple Periphery Gate Oxides                   |

| 0.13mm [3]      | Channel Erase<br>Dual Trench<br>Dual gate Spacer<br>Wireless Internet on a Chip                     |

#### FLASH CELL SCALING

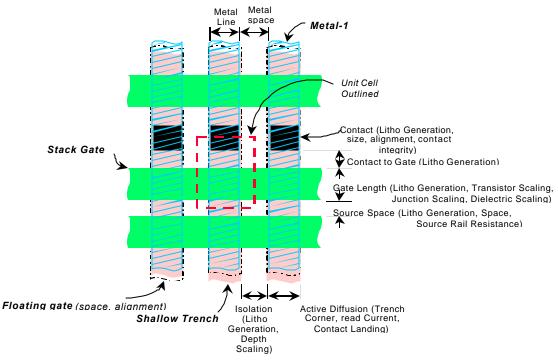

Cell size scaling is achieved by scaling critical area components. Each of the key scaling components is described. Figure 2 illustrates cell layout and scaling constraints. A key enabler to scaling is improved line width and space definition through new lithography at each generation. Architecture innovations, such as a number of self-aligned techniques, provide the bulk of the remaining area reduction.

#### **CELL WIDTH (WORDLINE DIRECTION)**

The cell width is determined by the simultaneous constraints of isolation pitch (isolation and cell active diffusion); floating gate pitch (endcap, space, and alignment); and contacted metal pitch (contact size, contact and metal space, and alignment). Each of these needs to be scaled in order to scale the cell width.

#### **Isolation Pitch**

Two key approaches have been adopted over the last several generations that have enabled continuous pitch scaling. The first is the adoption of a dual isolation scheme where the flash array isolation is decoupled from the periphery isolation so each can be optimized independently. This was first introduced in a local oxidation of a silicon isolation scheme, LOCOS, in the 0.6mm generation. The second key enabler was the introduction of trench isolation at the 0.25mm node, which helped to reduce the active width loss in the device. For the 0.13mm generation, a dual isolation scheme was adopted, now called dual trench, where the array trench was made shallower than the periphery trench for independent optimization. As before with the dual LOCOS scheme, the flash cell can be scaled more aggressively while still meeting the periphery isolation requirements. At each technology node, improved lithography capability is utilized. Additionally, improved gap fill capability of High-Density Plasma (HDP) oxides has been utilized since the 0.18mm technology node.

#### **Floating Gate Pitch**

The correct alignment of the floating gate to the active area is a very important cell size determinant, and it becomes more of a constraint as the isolation pitch is scaled and the floating gate isolation is constrained by the lithography minimum space capability. The 0.18mm technology node introduced a new self-aligned scheme (Figure 3, left half) where the floating gate is self-aligned to the isolation using a chemical mechanical polish process. This has been carried forward to the 0.13mm node as well. This self-aligned scheme removes the registration component of the scaling and also allows a sub-lithographic poly space.

#### **Contacted Metal Pitch**

Each generation takes advantage of the advances in lithography to scale the contact size and metal pitch. However, the contact alignment to the active area became the constraint at the 0.18mm node, and an UnLanded Contact (ULC) scheme was introduced (Figure 3, right half). In this case, a nitride etch stop layer is deposited below the inter-layer-dielectric oxide to prevent the contact etch punching through the isolation and causing a short to the substrate. This allows the contact to land partially in the isolation and reduces the registration constraint. This ULC scheme is continued in the 0.13mm technology.

#### **CELL HEIGHT (BITLINE DIRECTION)**

The cell height is determined by constraints of contact size and contact-to-gate alignment, gate length and drain and source space (source rail width).

Figure 2: Cell layout and scaling constraints

#### **Contact Size**

The key determinants to contact scaling have been the advances in lithography tools, resists, and masks. These have enabled the printing of smaller contacts at every generation. This has been coupled with advances in contact etch chemistry along with the adoption of salicided junctions starting at the 0.25mm generation, eliminating the need for plug implants, required by non-salicided contact processes. The contact plug uses PVD Ti/CVD TiN adhesion layers and blanket tungsten deposition followed by chemical-mechanical polish. The unlanded contact process introduced at 0.18mm (Figure 3, right half) improved registration by allowing a direct contact-to-gate alignment without worrying about alignment to the isolation.

#### **Source Space Scaling**

The primary challenge to scale the source space is to meet the source resistance requirements for each generation. Similar to the contact, the most advanced lithography is used to define the poly space at each generation. A selfaligned source architecture was introduced in the 0.6mm node to eliminate the registration component of the flash cell gate to the diffusion edge, and this continues to be used today. To prevent the source resistance from increasing beyond the maximum requirement, the trench profile and source implants are carefully engineered to manage the trench sidewall resistance without the need for angled implants. The adoption of a dual trench scheme in the 0.13mm generation allowed a much shallower trench to be chosen for the flash array, which made it easier to dope the sidewall, especially at the tighter pitch.

#### **Gate Length Scaling**

Gate length has been scaled at each generation using similar techniques to classical transistor scaling, which include junction and channel doping optimization along with gate oxide scaling. In the case of flash, both the tunnel oxide thickness and the interpoly Oxide-Nitride-Oxide (ONO) thickness are scaled to improve the gate coupling to the channel to allow further channel length scaling. In the 0.13mm generation, the ONO effective electrical thickness is 15nm, and the tunnel oxide thickness is 9nm. Changes to the erase scheme have also aided in channel length scaling by allowing the source junction to be scaled, thereby reducing the source junction underlap. At the 0.4mm generation a negative gate erase scheme was adopted, which reduced the cell source voltage from 12V in the source erase scheme used in earlier generations to  $\sim 5V$  with negative gate erase. At the 0.13mm generation a channel erase scheme was adopted so that the junction could be scaled further as it now no longer needs to support a voltage above the well voltage.

#### **Drain Space Scaling**

Generally the drain space is not limited by lithography, as it is larger than the source space, due to the presence of a contact. The key concerns with drain space scaling are adequate contact-to-gate space, which is reduced with improved registration, Inter-Layer-Dielectric gap fill (a HDP oxide is used at the 0.18mm generation and beyond), and the spacer architecture. In the transition from 0.18mm to 0.13mm, a dual spacer scheme was adopted that allowed the flash array spacer to be independent from the periphery high-voltage transistors. This enabled a narrower spacer in the flash drain region so that gap fill was not an issue.

#### SCALING LIMIT PROJECTION

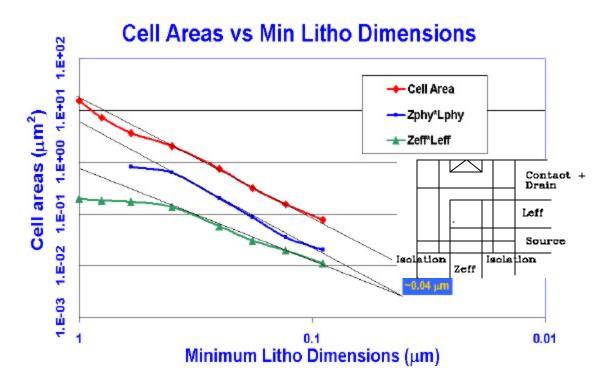

One can extrapolate the scaling trend based on what has been accomplished so far and the result is shown in Figure 4. This extrapolation is based on the fact that the basic planar cell structure is the same for all the generations, and scaling is achieved by reducing specific cell dimensions. The active electrical cell area is Zeff x Leff, which represents the minimum area required for cell functionality. The trend was relatively flat from 1.0mm to 0.40mm nodes, but was scaled aggressively since the 0.25mm generation. Zphy and Lphy represent the active width and gate length dimensions defined lithographically. The difference between Zphy and Zeff is the beak of the isolation process while the difference between Lphy and Leff is the lateral diffusion of the source and drain underneath the gate. Zphy x Lphy is scaling down at a faster rate compared to Zeff x Leff because of the aggressive reduction of beak and source/drain underlap. However, the beak and source/drain underlap cannot go to zero. Thus, the convergence point of the trend represents a projection of a scaling rate limiter of the current planar cell structure. The trend shows convergence at 45nm, which means that this component of scaling is no longer available. A practical limit of scaling of this component is the 65nm node. This also agrees well with analyses based on other considerations. To continue scaling at the same rate, i.e., meeting Moore's Law, more revolutionary ideas will be needed to either scale the Leff and Zeff more aggressively, which is historically difficult due to hot electron programming limitations, or to go to other cell structures that are not planar (3D cell structures).

Figure 4: Cell scaling projection

#### INTEL STRATAFLASH<sup>®</sup> MEMORY

The Intel StrataFlash<sup>o</sup> memory technology represents a cost breakthrough for flash memory devices by enabling the storage of two bits of data in a single flash memory transistor. Cost-per-bit reduction of flash memory devices has been traditionally achieved by aggressive scaling of the memory cell transistor using silicon process-scaling techniques as discussed in the previous sections of this paper. In an attempt to accelerate the rate of cost reduction beyond that achieved by process scaling, a research program was started in 1992 to develop methods for the reliable storage of multiple bits of data in a single flash memory cell. The result of this research was the commercial introduction of the first Intel StrataFlash memory in 1997, utilizing the 0.4mm technology node. The two-bit-per-cell Intel StrataFlash memory technology provides a cost structure equivalent to the next generation of process technology while using the current generation of process technology equipment. Today, the Intel StrataFlash memory technology has become the mainstream flash solution.

### The Multi-Bit Storage Breakthrough: Intel StrataFlash<sup>®</sup> Memory Technology

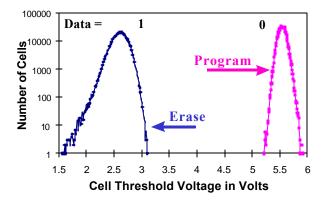

As discussed earlier, the flash memory device is a single transistor that includes an isolated floating gate. The floating gate is capable of storing electrons. The behavior of the transistor is altered depending on the amount of charge stored on the floating gate. Charge is placed on the floating gate through a technique called programming. The programming operation generates hot electrons in the channel region of the memory cell transistor. A fraction of these hot electrons gain enough energy to surmount the 3.2eV barrier of the Si-SiO<sub>2</sub> interface and become trapped on the floating gate. For single-bit-per-cell devices, the transistor either has little charge (<5,000 electrons) on the floating gate and thus stores a "1," or it has a lot of charge (>30,000 electrons) on the floating gate and thus stores a "0." When the memory cell is read, the presence or absence of charge is determined by sensing the change in the behavior of the memory transistor due to the stored charge. The stored charge is manifested as a change in the threshold voltage of the memory cell transistor. Figure 5 illustrates the threshold voltage distributions for a halfmillion cell (1/2Mc) array block. After erasure or programming, the threshold voltage of every memory cell transistor in the 1/2Mc block is measured, and a histogram of the results is presented. Erased cells (data 1) have

threshold voltages less than 3.1v, while programmed cells (data 0) have threshold voltages greater than 5v.

### Figure 5: Single-bit/cell array threshold voltage histogram

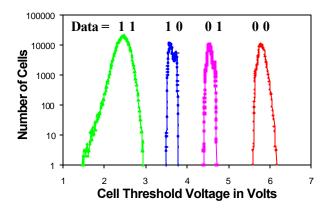

The charge storage ability of the flash memory cell is a key to the storage of multiple bits in a single cell. The flash cell is an analog storage device, not a digital storage device. It stores charge (quantized at a single electron), not bits. By using a controlled programming technique, it is possible to place a precise amount of charge on the floating gate. If charge can be accurately placed to one of four charge states (or ranges), then the cell can be said to store two bits. Each of the four charge states is associated with a two-bit data pattern. Figure 6 illustrates the threshold voltage distributions for a 1/2Mc block for two bits per cell storage. After erasure or precise programming to one of three program states, the threshold of each of the 1/2Mc is measured and plotted as a histogram. Notice the precise control of the center two states, each of which is approximately 0.3v (or 3,000 electrons) in width.

Figure 6: Two-bit/cell array threshold voltage histogram

Higher bit-per-cell densities are possible by even more precise charge placement control. Three bits per cell require eight distinct charge states and four bits per cell

<sup>&</sup>lt;sup>o</sup>StrataFlash is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

require sixteen distinct charge states. In general, the number of states required is equal to  $2^N$  where N is the desired number of bits.

The ability to precisely place charge on the floating gate and at some later time sense the amount of charge that was stored has required substantial innovations, and extensive characterization and understanding of cell device physics, memory design, and memory test. These innovations are discussed in detail in two earlier *Intel Technology Journal* papers [4,5].

#### LOW-VOLTAGE, HIGH-PERFORMANCE OPTIMIZATION FOR DISCRETE FLASH MEMORIES

Increasing read performance demands at low operating voltage taxes the ability of high-voltage transistors, which are required by flash program and erase. Cobalt-salicided complementary polysilicon gates are used to form lowthreshold NMOS and PMOS surface-channel transistors and low source/drain and gate resistance. Additionally, special low-threshold devices. for low-voltage performance and malog circuit design requirements, are provided by separate well and Vt-adjust implants. Continual application performance demands and further reductions in operating voltages require the inclusion at the 0.18mm technology generation of thin gate-oxide logic compatible NMOS and PMOS transistors. This is achieved with three additional masking layers (one for thin gate oxide and two for low-voltage wells). Source/drain and tip regions are shared between the low-voltage and high-voltage transistors to best balance performance with added processing steps. The thin gate-oxide architecture is bounded by optimization for low voltage (<1.8V), while maintaining compatibility for legacy voltage (3.3V), including balancing of device Vt with off-current leakage for minimization of standby currents. An 8nm gate oxide was chosen to balance these needs, with trench processing meeting charge-to-breakdown requirements, supporting three separate oxides: tunnel oxide, highperformance oxide, and high-voltage oxide. A triple well is provided for design flexibility of negative voltage switching and low-voltage optimization. Lastly. performance capability is provided by three layers of aluminum metalization, allowing additional wordline and bitline strapping of the flash array, for reduced resistancecapacitance, RC delay, and more efficient signal routing in the periphery.

In addition to low voltage and high performance, the trench isolation, thin-gate-oxide, salicided complementary poly gate transistors and the three layers of interconnect inclusion provide all the key architectural elements required for embedded logic capability. Higher degrees of thin-gate device performance can be achieved by further separating the process steps and reducing the oxide thickness for lower voltage operation, as discussed below.

Lastly, the cost sensitivity of the market for memory dictates requirements for low-cost process technologies. The described cell scaling and Intel StrataFlash<sup>â</sup> memory capability satisfy low cost. Additionally, process synergy of this memory process technology, with the basic process modules and equipment set with other high-volume logic technologies, lower cost through economies of scale by providing factory flexibility and shared process step and yield learning.

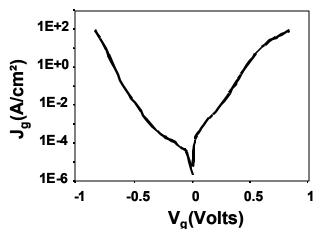

To reduce cost, the periphery transistors must also be scaled since they constitute a significant portion of the die area. The introduction of channel erase reduces the maximum voltage the periphery needs to support, and the introduction of more advanced lithography and etch gives better gate-patterning capability. These allow the channel length and gate oxides to be scaled, which is done in conjunction with traditional junction scaling, and which leads to a significant reduction in the gate length, while at the same time maintaining good transistor characteristics. For the embedded logic process, below, this leads to a gate length of 100nm. The reduction in the maximum voltage the periphery needs to support along with the dual trench scheme allows the isolation width to be scaled as well, since a deep trench can be maintained for logic devices independent of the shallow trench used in the flash array. These changes, combined with the advanced 0.13mm lithography tools, cobalt salicide, and complimentary gates consistent with Intel's 0.13mm logic process, deliver the required transistor performance and area savings.

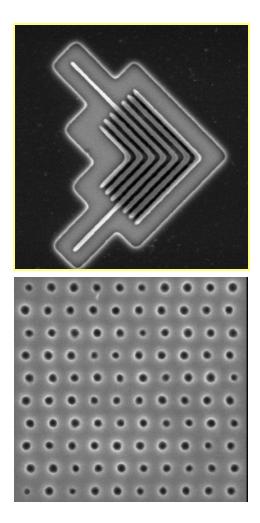

#### WIRELESS INTERNET ON A CHIP

Traditionally, flash and logic process technologies are optimized separately on separate process equipment sets and separate fabrication facilities. During the development of the 0.25mm flash process technology, Intel made the strategic decision to develop its flash processes synergistically with its logic processes. This initial decision was made with the goal of processing the two technologies, flash and logic, in the same fabrication facility, for improved manufacturing flexibility and shared learning and for maximum volume production efficiency. This decision also brought key process modules into the flash processes, which historically were not found on flash, such as trench isolation and salicided

<sup>&</sup>lt;sup>â</sup> StrataFlash is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

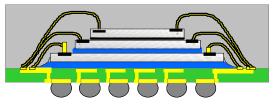

complimentary gates. Both of these process modules are examples of key enablers that not only achieve the manufacturing synergy goal, but also provide for dramatic advancement of scaling the flash memory cell and enhancing performance. (This was outlined in the previous sections.) Additionally, the incorporation of these features into flash memory technology has paved the way for the integration of a high-performance logic function with a dense flash memory on the same chip. This capability has led to the "wireless Internet on a chip" technology, where all the key elements of a typical cell phone and a typical handheld computer, the advanced digital logic functions, all the SRAM and flash memory functions, and the analog functions for interfacing to a radio are all integrated onto a single chip. This is costeffectively achieved without compromising the performance of the state-of-the-art digital logic or the density of the state-of-the-art flash memory.

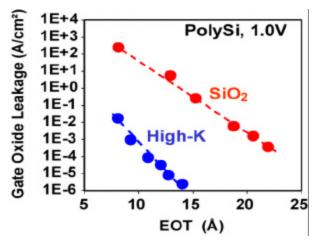

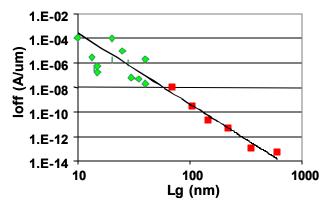

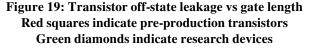

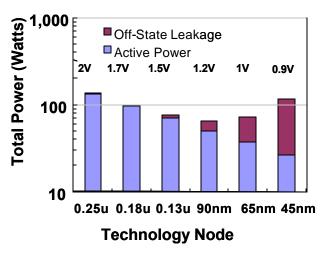

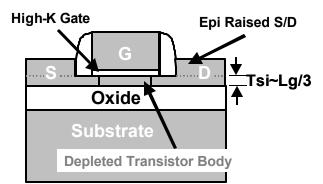

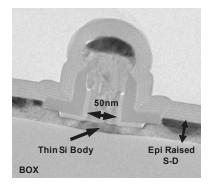

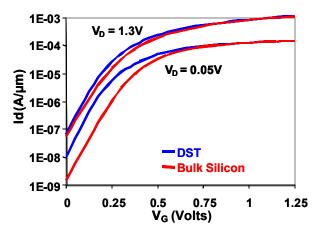

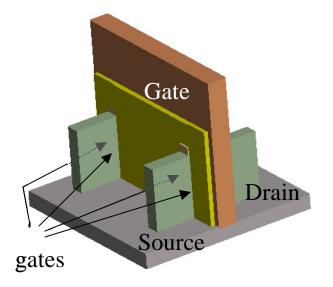

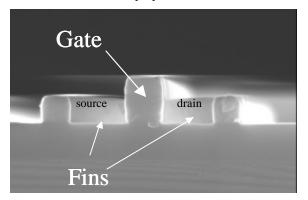

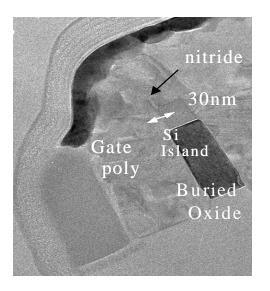

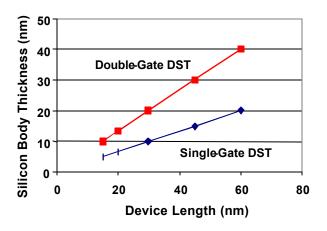

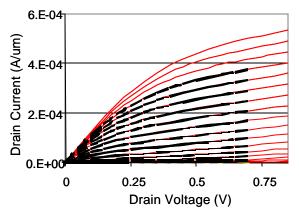

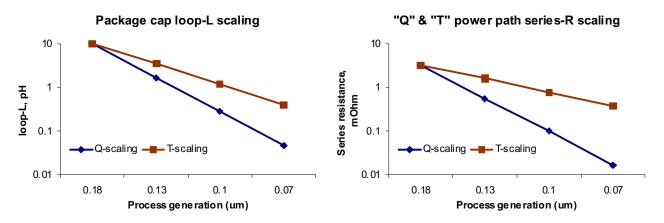

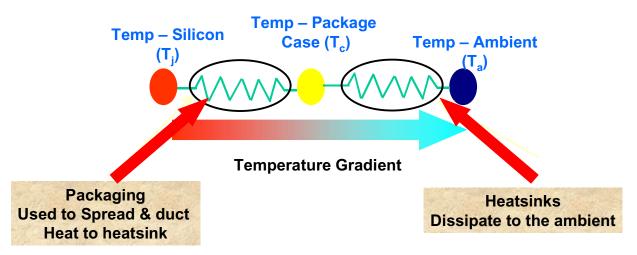

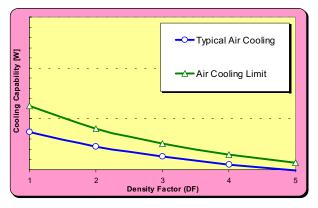

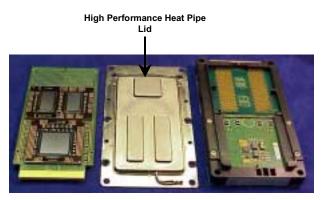

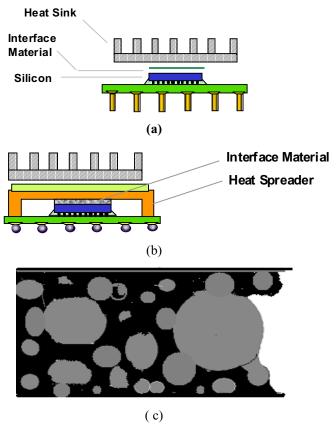

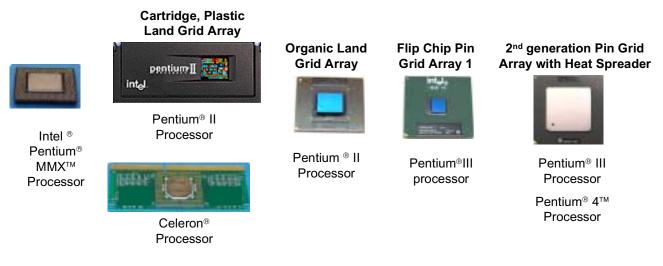

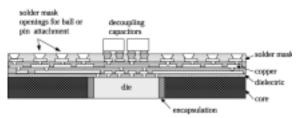

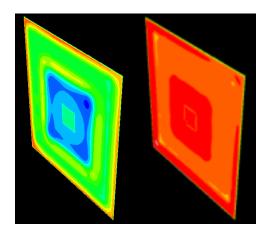

The value of this integration is several fold. First, the total number of devices can be reduced, thereby reducing the form factor of a wireless device, allowing for smaller lighter devices. What were previously several chips is now reduced to one. The reduction in the number of chips in a system also improves overall system reliability. Secondly, the integration of flash memory serves to enhance the performance of the digital logic computing functions. Memory latency is greatly reduced, and bandwidth is greatly enhanced by having logic and memory functions integrated onto the same chip. Lastly, this enhanced performance is achieved at lower power, as interconnect bus capacitance is significantly reduced with an integrated on-chip bus, versus a discrete external bus.