## Preface

#### <u>Lin Chao</u> Editor Intel Technology Journal

Microprocessor packages are the external "suits" for the complex and intricate world of silicon chips. The working part of a microprocessor is a small piece of silicon no larger than a postage stamp encased in a sealed "package." The chip itself must be sealed away to prevent external contaminants, such as dust, from adversely affecting the silicon chip. The art and science of semiconductor packaging has advanced radically over the last decade as faster and more powerful microprocessors with millions of transistors stressed the state of the art in microprocessor packaging. Thermal-heat dissipation, signal interconnects, and higher densities have required many advances. Pin-grid arrays with hundreds of pins, multicavity modules, leadless chip carrier and quad flat packs are the many types of microprocessor packages today.

The seven papers here present an engaging discussion on Intel's microprocessor packaging technologies. They highlight the technical challenges faced by packaging developers now and in the future, and in a broad sense, ties them into the many challenges faced by the semiconductor industry to achieve the next level of performance. The first paper traces the evolution of Intel's microprocessor packaging technologies. Flip-Chip Pin Grid Array (FCPGA) used in Intel's high-performance microprocessors uses balls of solder and gold that are melted (or reflowed) to connect the silicon chip to the package. The second and fifth papers look at this packaging technology.

The third paper explains the technical complexity of interconnect design to achieve optimal electrical performance. This paper discusses the design analysis and synthesis techniques used to ensure optimal electrical design. The fourth paper presents the challenges faced in thermal design. Ensuring that packaging continues to meet high standards of reliability is a key to success and is discussed in the sixth paper. Finally, the seventh paper discusses the practical problem of managing the thermal environment during microprocessor testing.

# Microprocessor Packaging: Evolution and Future Challenges

By <u>Nasser Grayeli</u> Director, Assembly Technology Development Intel Corp.

The past decade has seen the evolution of microprocessor packaging from a simple protective scheme to a complex combination of different elements that enable microprocessor performance while still providing the basic function of protection. Packaging today's microprocessor on the one hand entails tailoring the package to enable microprocessor performance, a complex task considering the rapid rate of microprocessor performance growth. This challenge is in terms of schedule and technical complexity. On the other hand, the package forms the interface between the microprocessor and the external world of the motherboard and the computing system. In this capacity, package design must allow for an easy interface and must meet a diverse set of form factor requirements.

The package provides a conduit for the microprocessor through a space transformation allowing small-scale features on the silicon to be electrically connected to environment. This is the external а problem challenging geometrical and requires that packaging interconnection densities must closely track the evolution of microprocessor interconnection densities. In connecting the die to the motherboard, the package must also ensure that the connections do not unduly inhibit the microprocessor performance by introducing unnecessary electrical impediments usually referred to as package "parasitics." As microprocessors have evolved, they have increased in speed, which in turn needs increasingly sophisticated power delivery

schemes. Another consequence of microprocessor evolution has been increasing power dissipation. Package design must now provide a path for thermal dissipation, requiring a better understanding of the thermal characteristics of packaging materials and design. Package design also requires a good understanding of the structural characteristics of the package to ensure it is designed for reliability and robustness. Attention is increasingly focused today on understanding the electrical, thermal and mechanical characteristics of packaging to optimize all these aspects.

The package is also the interface that connects the microprocessor to the motherboard. In this capacity it must have a compatible interface to allow for easy acceptance on the motherboard as well as the system design. The form factor of the package is a critical element for easy interface to motherboard. the The requirements are usually different in different market segments and often drive the need for form factors that are tailored to these different segments. For instance, the height of the package is critical to enable a microprocessor in a mobile market where a slim and low weight package is critical to success. On the other hand, the ability to dissipate high power, and hence features that enables this, are critical in a server or desktop market segment. Cost, compatibility and fit within the computer system are key parameters that must be designed for in making a microprocessor successful. This challenges us into concurrently developing

multiple solutions and technologies geared towards specific market segments.

Aside from the challenges of package design, there is a need to develop efficient and costeffective manufacturing processes that allow us to meet the schedule and volume demands of today's market places. These have presented us with interesting challenges in understanding the manufacturability, testability and reliability of packaging. Some of these issues are discussed in greater detail in this issue.

This Q3'00 issue of the Intel Technology Journal has been designed to provide the reader with a broad scope view of the in technical challenges the design, reliability manufacturing. testing and assessments of microelectronic packaging. By focusing on microprocessor packaging, which represents the technical envelope and the greatest challenges, the papers in this volume attempt to highlight different aspects of the evolution and future of packaging. A perusal of this journal will help the reader better appreciate the systematic manner in which we have successfully addressed the challenges of today and how we continue to plan for the future.

Copyright © Intel Corporation 2000. This publication was downloaded from <u>http://www.intel.com/</u>.

Legal notices at <a href="http://www.intel.com/sites/corporate/tradmar">http://www.intel.com/sites/corporate/tradmar</a> <a href="http://www.intel.com/sites/corporate/tradmar">http://www.intel.com/sites/corporate/tradmar</a>

# Flip-Chip Technology on Organic Pin Grid Array Packages

Mirng-Ji Lii, Assembly Technology Development, Intel Corp. Bob Sankman, Assembly Technology Development, Intel Corp. Hamid Azimi, Assembly Technology Development, Intel Corp. Hwai Peng Yeoh, Assembly Technology Development-M, Intel Corp. Yuejin Guo, Assembly Technology Development, Intel Corp.

Index words: flip chip, organic, pin grid array, surface mounted technology pin

## ABSTRACT

As microelectronic devices become more integrated with increased functionality and higher levels of performance, the complexity of packaging technology grows proportionally. Today's silicon processes have enabled microprocessor designs to achieve very high clock frequencies. As a result of the increase in feature integration, high clock frequencies, and the power supply requirements of the latest generation of microprocessors, the density of interconnects between processor chip and substrate has been increased remarkably. New package substrate technologies with enhanced interconnect density are required in order to take full advantage of these silicon advancements. This has created an array of challenges in package design, substrate technology development, and assembly processes development. To provide a highly integrated and lower cost package, the Flip Chip Pin Grid Array (FCPGA) package was proposed as an innovative packaging solution [1]. This package utilizes laser-drilled blind/buried vias stacked on a PTH to ease routing and to lower the power supply loop inductance. In addition, the integration of flip-chip technology on an organic substrate helps to provide adequate signal and power supply interconnects. The FCPGA package was designed as a socketable solution. By taking advantage of the existing PGA socket infrastructure, this package helped to expedite the Original Equipment Manufacturers (OEMs) acceptance of the new package. This paper also describes the challenges encountered in the past in package design, validation, and assembly process development. Several technical challenges such as meeting the stringent impedance requirement to enable RDRAM\* bus

functionality, the optimal pinning process to certify Surface Mounted Technology (SMT) pins, and Underfill material and process development to fulfill throughput and performance requirements were overcome. The FCPGA package not only delivered a package with high performance on a cost-effective substrate, but also intelligently reused existing assembly equipment to minimize overall packaging cost. With the success of the first-generation FCPGA package technology certification, which has been utilized in the Intel® Pentium<sup>®</sup> III microprocessors, future generations of this technology will be developed that should offer great advantages for future Intel products.

## **INTRODUCTION**

The need for high-density interconnects in a costeffective flip-chip package was the motivation for FCPGA technology development. This paper describes the challenges encountered during the first generation FCPGA package design, validation, assembly processes, and material development.

FCPGA was designed as a socketable solution. The pin side view of an FCPGA package is shown in Figure 1. The use of the existing 370 socket infrastructure helped with the OEM acceptance of this new package.

The key features of the FCPGA technology are as follows:

1. Stackup

The substrate is comprised of an FR-5 equivalent core with two resin build-up layers on each side. Both blind and buried vias are used to ease package routing.

2. Bump Pitch

The flip-chip interconnects are built on an organic substrate with a solder bump pitch of 11 mils (279.4  $\mu$ m).

<sup>\*</sup> Other brands and names are the property of their respective owners.

### 3. Decoupling Capacitors

Pin side decoupling capacitors were added to lower the power supply loop inductance.

4. Surface Mount Package Pins

SMT pins were used to ease package routing. This was an improvement over through hole mounted pins. The use of SnSb solder to join the package and pins provided solder joint reliability through subsequent reflow operations.

Figure 1: Pin side view of the FCPGA package

# Package Design and Validation Overview

### **Package Designs**

Several test vehicles and test structures were designed and analyzed to validate the package's electrical, thermal, mechanical, and reliability performance. Key attributes of several packages are tabulated in Table 1 [2, 3, 4, 5].

Table 1: Package design attributes

| Attributes        | Test Package A                                   | Test Package B                                                                       | Test Package C                                                           |  |

|-------------------|--------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

| FormFactor        | 1.95" x 1.95"                                    | 1.95" x 1.95"                                                                        | 1.95" x 1.95"                                                            |  |

| Thickness         | 1.1+/-0.1 mm                                     | 1.1+/-0.1 mm                                                                         | 1.1 +⁄- 0.1 mm                                                           |  |

| Package Layers    | 6 layers                                         | 6 layers                                                                             | 6 layers                                                                 |  |

| Min Bunp Pitch    | 279µm                                            | 279µm                                                                                | 279µm                                                                    |  |

| Bunp Pattern      | FCR in three I/Orows<br>Square gird in core area | FCR in three I/Orows<br>Square grid in core area                                     | FCR in three I/Orows<br>Slight offset parallelogram<br>grid in core area |  |

| #ofC4bunps        | 1199                                             | 1286                                                                                 | 1209                                                                     |  |

| Die Size          | 0.355" x 0.455"                                  | 0.440'' x 0.363''                                                                    | 0.438" x 0.386"                                                          |  |

| Die Layers        | short loop                                       | full loop                                                                            | full loop                                                                |  |

| Core Voltage      | >25V                                             | 1.5V/ 1.6 V                                                                          | 1.55V/ 1.8V                                                              |  |

| Padage Stackup    | L1/12: signal layers<br>1.3-1.6: plane layers    | L1 : signal layers<br>L2, L5 : partial signal<br>layers<br>L3, L4, L6 - plane layers | L1, L2: signal layers<br>L3-L6: plane layers                             |  |

| Vias              | Single-layer µ-vias<br>Two-layer µ-vias          | Single-layer µ-vias                                                                  | Single-layer µ-vias                                                      |  |

| Footprint         | PGA_370                                          | PGA_370                                                                              | PGA_370                                                                  |  |

| #of chip cap.     | 18                                               | 14                                                                                   | 7                                                                        |  |

| Power Dissipation | >30W                                             | 15~28 W                                                                              | 15~20W                                                                   |  |

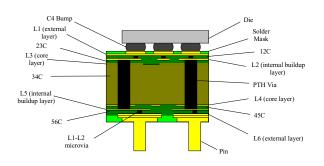

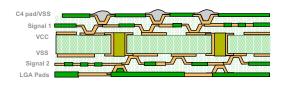

The layer structure of an FCPGA substrate is displayed in Figure 2; the targeted thickness of each layer and package key feature sizes are given in Table 2.

Figure 2: Cross section of FCPGA substrate

| Label    | Feature                           | Thickness (SI) |

|----------|-----------------------------------|----------------|

|          | Solder Resist over Copper         | 25 µm          |

| 12C, 56C | External Buildup Layer Dielectric | 30 µm          |

| 23C, 45C | Internal Buildup Layer Dielectric | 30 µm          |

| 34C      | Core Layer Dielectric             | 800 µm         |

| L1, L6   | External Buildup Layer Copper     | 17 µm          |

| L2, L5   | Internal Buildup Layer Copper     | 25 µm          |

|          | Copper over PTH                   | 17 µm          |

| L3, L4   | Core Layer Copper                 | 14 µm          |

|          | Total Package Thickness           | 1.1 mm         |

Table 2: Mean thickness of FCPGA stack up

#### **Electrical Characteristics**

Empirical measurements and electrical modeling were used to assess the characteristic impedance (Zo), inductance, capacitance, resistance, and dielectric of the package. These parameters will impact the overall design by influencing the signal integrity, power supply droop, and routing requirements [6].

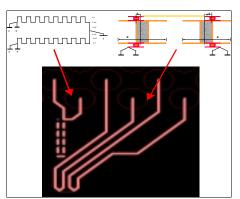

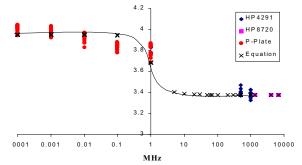

One of the resistance test structures built into the test packages is shown in Figure 3; four point probing was used for the resistance measurement. Multiple via chains and conductor sheet resistance data confirmed that the package manufacturing process was capable of meeting targeted specifications. In order to ensure impedance values satisfied the data bus requirements, dielectric constants across a wide range of frequencies were analyzed and measured. The comparison between modeled and measured values is shown in Figure 4. The empirical data is in good agreement with analytical prediction.

Figure 3: FCPGA resistance test structure

Figure 4: Comparison of calculated and measured dielectric constants in various frequency ranges

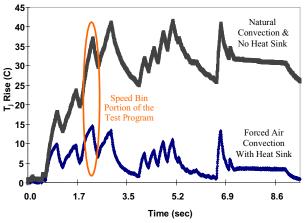

#### **Thermal Performance**

Both modeling and testing were conducted to validate the FCPGA thermal solutions. With increasing core speed and maximum power dissipation, both passive and active heat sinks were evaluated. Details of the thermal design challenges are discussed in the Thermal Designs section of this paper.

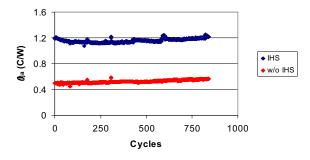

#### Mechanical and Package Reliability

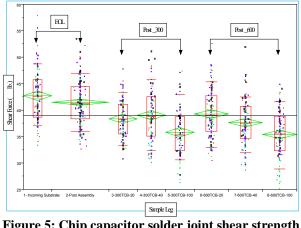

Mechanical tests and modeling were performed to address concerns about the structural integrity of the FCPGA package. A total of 100 FCPGA samples were tested with uniform and edge-loaded forces (20 to 100 lbs). Visual inspection and post-stress electrical test data confirmed that there was no change in the mechanical and electrical integrity of the package. Moreover, an additional 40 samples were uniformly loaded up to 100 lbs. and subjected to 600 cycles of T/C "B." No sign of failures was seen, and the chip cap solder joint strength retained a healthy level as illustrated in Figure 5.

Figure 5: Chip capacitor solder joint shear strength distribution at end-of-line, 300 and 600 cycles of T/C "B"

The collected data on maximum package/die loading and chip cap solder joint shear strength confirmed the

robustness of the FCPGA package. Various stresses specified for Intel assembly technology certification (such as Temperature Cycling, Bake, Power Cycling, Shock, and Vibration, etc.) were performed to accelerate other possible failure mechanisms. Several failure modes (such as metal migration and weak pin solder joint) were observed early on, but fixes were quickly implemented, which eliminated these issues. In conclusion, there were no high-risk issues that appeared during testing that impacted the technology certification.

Continuous data was collected at Intel and at supplier manufacturing sites. This included electrical, mechanical, and thermal measurements. These data, collected since early in the development phase, built sufficient confidence that the FCPGA package was a viable packaging solution for current as well as future microprocessors.

# SUBSTRATE DEVELOPMENT OVERVIEW

Photolithography and etch have been the most prevalent methods to create blind  $\mu$ -vias in high-density substrates. The photolithography process has two main disadvantages. First there is the limitation to the  $\mu$ -via diameter due to the limited resolution of commercial photosensitive materials. Second, photosensitive materials are prone to reliability issues with their mechanical properties, moisture absorption, and the value of the dielectric constant. Laser  $\mu$ -via drilled into an "off the shelf" dielectric can overcome these limitations.

Laser technology can potentially create via sizes down to the < 10  $\mu$ m range, while today's photolithography materials are limited to 50-60  $\mu$ m vias. Another plus is that the smaller the via size, the lower the cost of the laser  $\mu$ -via formation due to a shorter pulse time. In addition, by eliminating photosensitive resins, a large number of non-photo sensitive materials can be considered for dielectric material. The laminate material used in FCPGA is a commercially available film, which is lower in cost when compared to the dielectric materials used in other photo  $\mu$ -via based packages.

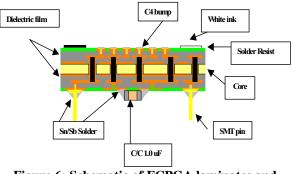

In the FCPGA package, the laser drill via technology was implemented in spite of the fact that the line/space design rules were not as challenging as the existing Organic Land Grid Array (OLGA) technology. The rationale was to save money on processing costs, while taking advantage of the higher routing density resulting from the smaller  $\mu$ -via pads. By using laser vias instead of photo vias, the FCPGA package had access to cheaper and better commercially available dielectric materials. Figure

6 shows a schematic of the laminates and materials used in the FCPGA.

Figure 6: Schematic of FCPGA laminates and materials

Comparing FCPGA with the previous OLGA package, there are several distinct differences:

- 1. FCPGA uses laser vias instead of photo vias, and SMT pins.

- 2. The size of the FCPGA package is larger with additional area for chip caps.

- 3. Commercially available dielectric and solder-resist materials are used in the FCPGA package.

- 4.  $\mu$ -via is used on PTH in the FCPGA package.

# FCPGA KEY CHALLENGES

## **Thermal Designs**

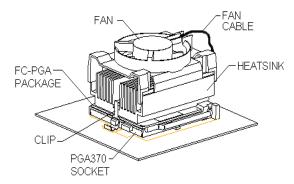

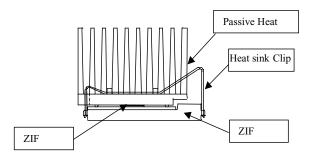

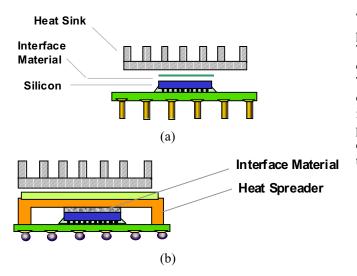

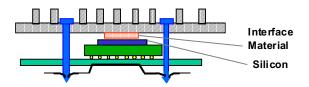

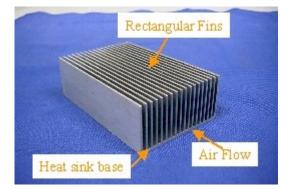

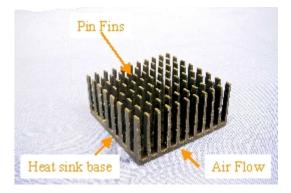

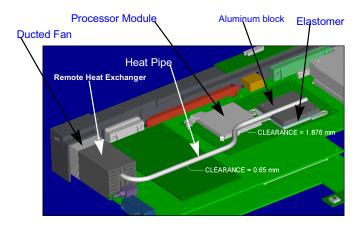

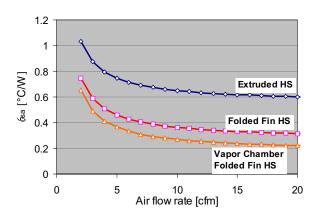

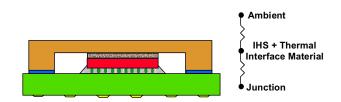

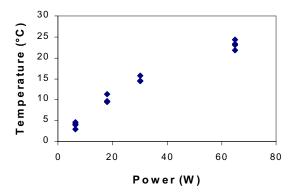

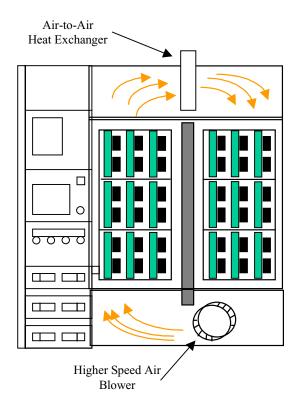

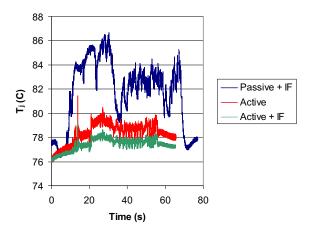

Thermal design solutions for the FCPGA package pose challenges because of the system chassis spatial constraints and the need to meet maximum power dissipation requirements. The design was also challenging because a heat sink ground feature that suppresses potential electromagnetic emission had to be integrated into the package. The key thermal design constraints are listed in Table 3. To broaden the variety of possible FCPGA package applications, both passive and active heat sink designs were evaluated. A schematic of passive and active heat sink solutions is shown in Figures 7 and 8. Preliminary empirical and modeling results suggested that passive and active solutions could support power of about 19W and 22W, respectively.

| Attributes             | Product A   | Product B  |

|------------------------|-------------|------------|

| Thermal Design Target  | 19.3 W      | 22 W       |

| Tj                     | 90 oC       | 85 oC      |

| Ta (system internal)   | 45 oC       | 45 oC      |

| Theta_ja               | 2.33 oC/W   | 1.59 oC/W  |

| Airflow = 200 fpm      | 200 fpm     | 150 fpm    |

| Clip force requirement | 12 - 20 lb  | 12 - 20 lb |

| HS design              | passive     | active     |

| HS weight              | 140 - 180 g | 140 g      |

Table 3: Summary of typical FCPGA thermal design attributes

Figure 7: Schematic of an active heat sink solution

Figure 8: Schematic of a passive heat sink solution

## **High-Speed Bus Impedance Requirement**

High-speed digital systems have problems that manifest themselves in three distinctive ways. First, conductor traces can experience reflections due to multiple impedance mismatches. Second, cross talk may occur because of unwanted electromagnetic coupling between adjacent traces. Third, ground bounce can be significant due to inductance in the ground return path of the IC package. The combined result of these effects could adversely impact timing margins in systems and thus limit the ultimate performance of the system. In the FCPGA package, a good deal of effort was put into controlling the impedance to limit the impact of the first problem. The design of a fixed-impedance bus structure makes it more sensitive to the physical dimension tolerances in the manufacture of the package. The FCPGA design rules will support multiple impedance targets in the package. The bus impedance specifications call for a tolerance target of  $\pm 10\%$ .

Impedance is a function of dielectric layer thickness, dielectric constant, and Cu trace width. This requires rigorous tolerance control of dielectric thickness. Nonuniformity in thickness of the Cu plating will directly add variability to the thickness of the dielectric layer between two adjacent Cu layers. Since there is inherent Cu thickness variation, the control of dielectric layer thickness variation becomes even more stringent.

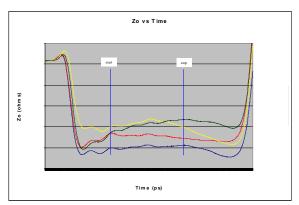

Initial data indicated this variation would be a challenge for the FCPGA package as there was a higher dielectric thickness variance than desired, and a correspondingly variable impedance value. However, as illustrated in Figure 9, impedance (Zo) measurements taken after process improvements showed that the mean impedance stabilized. The improvement was made possible through improving the Cu thickness uniformity and by making a smoother insulator surface.

Figure 9: Impedance measurements with two different dielectric thicknesses

## µ-Via Reliability Issues

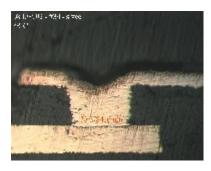

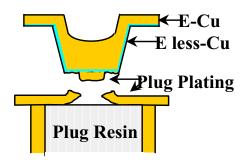

Preliminary reliability data showed  $\mu$ -via delamination. The  $\mu$ -via delamination resulted in a high-percentage falloff after 300 cycles of T/C "B" (-55C <-> 125C) stressing and higher cumulative fails after 1000 cycles of T/C "B". Figure 10 shows an example of a delaminated via that caused an electrical failure.

Figure 10: Example of a delaminated via

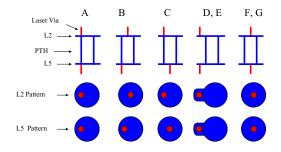

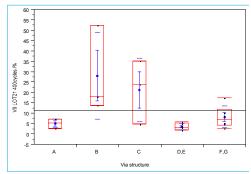

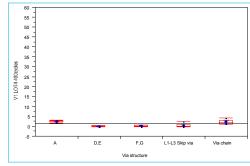

Failure analysis suggested that via delamination occurred at the interface between the electrolytic Cu and electroless Cu layers. Hot oil thermal shock tests were utilized as a quick-turn reliability monitor. The measurement of improvements in the manufacturing process were based on the shifts in the µ-via resistance. Test data confirmed that two factors were the significant modulators in µ-via delamination. Figure 11 shows a schematic drawing of various via structures, as well as the test data for µ-via resistance shift after hot oil thermal shock. The test results clearly indicated that via resistance increased more than 50% after thermal shock for some test structures. After process fixes were implemented, no via resistance shift was seen after 400 cycles of stress!

Figure 11a: Schematic of various via structures

Figure 11b: Via resistance before process fix

Figure 11c: Via resistance after process fix

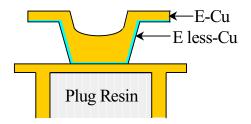

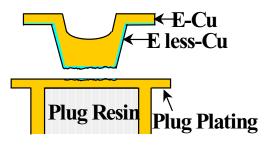

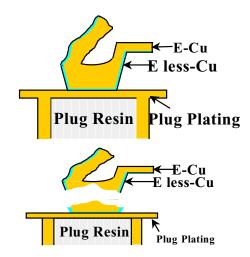

The improvement in via integrity was also verified through via "pop" tests. Three types of failure modes were observed and are shown in Figure 12. None of these failure modes appeared on FCPGA packages after the process fixes were implemented.

Figure 12a: Schematic of a PTH via structure

Figure 12b: Popped via failure indicating weak bonding at the two Cu layers interface on package before process fix

Figure 12c: Broken via edge indicating strong Cu layer interface on package after process fix

Figure 12d: Broken via plug plating indicating strong bonding at the two Cu layers interface after process fix

## **SMT Pin Development**

The FCPGA package utilizes SMT butt-mounted pins on an organic substrate. To determine the reliability of these pins, experiments were conducted to evaluate different combinations of pin solder joint structures. They were made from three solder materials, three different solder volumes, skew misalign pins, and smaller pin nail-head sizes. The attributes of each leg of the experiment are detailed in Table 4. Additionally, pin pull and pin shear testing were used to quantify the pin strength before and after stresses.

**Table 4 : SMT pin strength attributes**

| Legs | Nail Head<br>Diameter (mm) | Solder<br>Volume<br>(mg) | Solder<br>Composition | Pad<br>Opening<br>(mm) |

|------|----------------------------|--------------------------|-----------------------|------------------------|

| А    | 0.9                        | М                        | SnAg                  | 1.2                    |

| В    | 0.7                        | Н                        | SnAg                  | 1.2                    |

| С    | 0.9                        | Н                        | SnAg                  | 1.2                    |

| D    | 0.9                        | М                        | SnAg                  | 1.2                    |

| E    | 0.9                        | L                        | SnAg                  | 1.2                    |

| F    | 0.9                        | Н                        | SnSb (A%)             | 1.3                    |

| G    | 0.9                        | Н                        | SnSb (A%)             | 1.2                    |

| Н    | 0.9                        | М                        | SnSb (A%)             | 1.2                    |

| Ι    | 0.9                        | Н                        | SnSb (B%)             | 1.3                    |

| J    | 0.9                        | Н                        | SnSb (B%)             | 1.2                    |

| K    | 0.9                        | М                        | SnSb (B%)             | 1.2                    |

Test data confirmed that the smaller pin nail heads and intentional pin misalignment had lower pin strength as measured before assembly. Legs with M mg and H mg of SnAg and SnSb legs showed comparable pin pull strength and pin shear strength with the exception of the L mg SnAg lot, which had lower pin pull and pin shear strength. Interestingly, after assembly, the SnAg lots' pin pull strength was reduced significantly. Both SnSb (A%) and SnSb (B%) lots showed no sign of pin joint strength degradation after assembly. The SnSb (B%) was selected as the POR material because SnSb (A%) required a higher reflow temperature, which was undesirable.

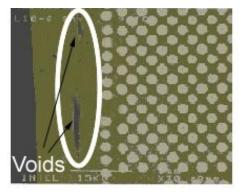

# Low Cost Underfill Material and Process Development [7]

The use of a two-step process and two separate materials for Underfill and fillet in C4-OLGA packages resulted in high equipment costs and a narrow process window. The challenge in FCPGA was to develop a low-cost, but highperformance Underfill material that would enable a simplified process and deliver high yields and improved unit per hour (UPH) capability.

Underfill material selection criteria included raw material cost, manufacturability, reliability and process integration performance, and supplier technical support and quality. The Underfill development team also reexamined the reliability and manufacturability success criteria such as alpha particle counts and the number of voids and voiding sizes, used in previous stages of development.

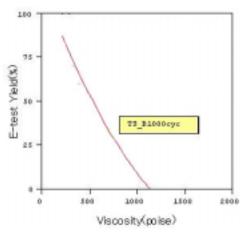

In developing the new Underfill process, viscosity and self-fillet formation are two key epoxy material properties. Based on material data sheets provided from fourteen suppliers worldwide, a total of four different materials was chosen for further evaluation. Score cards from each of the candidates were assessed to collect technical, business support, and quality data. Based on the collected information, the POR Underfill material was then selected. After the POR material was finalized, the epoxy module engineering team focused on Underfill process optimization. Collaborative effort from the development team resulted in an optimized and simplified Underfill flow that met the FCPGA cost targets.

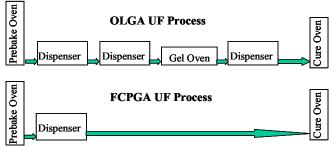

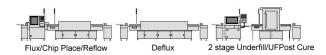

Figure 13: A comparison of the C4-OLGA and the FCPGA Underfill processes

Figure 13 illustrates the differences between the C4-OLGA and the FCPGA Underfill process flows. As shown in the POR flows, the FCPGA process has one, instead of two, dispensers and a BTU, which could save on equipment expenditures. Moreover, when results were evaluated, the FCPGA also improved the yield, and it had higher UPH throughput. The simplified Underfill process, together with the high performance of the Underfill material, was a plus for the FCPGA program.

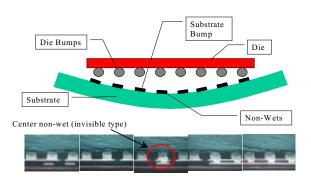

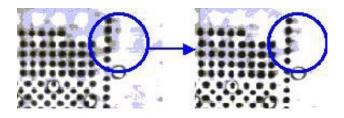

## Flip-Chip Solder Bump Non-Wet

Initial FCPGA data collection indicated the highest pareto of yield loss was attributed to open failures due to the non-wet of the C4 bumps. Low yield analysis revealed that the non-wet falls into two categories:

- edge non-wet, raccoon tail type, which can be detected with X-ray

- center non-wet, which is invisible with X-ray

However, in the second-phase data collection, a new oven was used for FCPGA reflow, and the open failures due to non-wet were reduced significantly. Low yield analysis confirmed the majority of non-wets were at the center of the die and invisible with X-ray.

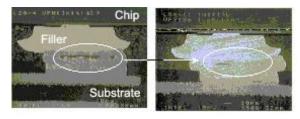

A root cause assessment of the center non-wet showed no correlation between the microprocessor chip's passivation oxide thickness or co-planarity, the substrate's bump oxide, flux quantity, or uniformity during the chip attach process. A cross section of the center non-wet unit's solder bump joints revealed the substrate's and chips' bumps were not adequately aligned, except for those at the middle of the die. The right and left sides of the bump joints were slightly misaligned at opposite directions. Because of these observations, a failure mechanism for center non-wet was proposed; as illustrated in Figure 14, it turned out that the lack of bump co-planarity in the substrate prevented solder joints from forming at the center region of the die. This model also explained the slight shift in the alignment of the substrate's and die's bumps near the edge of the die.

### Figure 14: Proposed center non-wet mechanism; excessive substrate bump co-planarity prevents solder joints from forming at the center area of the die

The proposed model was validated through experimentation. From the data, we also realized that a maximum substrate bump co-planarity was required to prevent center non-wet. This has been defined in the specification for incoming packages.

## **FUTURE DEVELOPMENTS**

The next generation of FCPGA package design rules have been defined and are currently under development. The performance enhancements in the new FCPGA2 package will be achieved with finer feature sizes (including bump pitches, Cu trace width and spacing, PTH size, stripline, etc.) and the addition of some new features (such as stacked vias and via-in-via). In addition, power delivery and removal capabilities will be improved through better decoupling capacitance and the use of a highly conductive package lid.

## CONCLUSION

The FCPGA package design and development efforts have resulted in the integration of high-density flip-chip interconnect, SMT pins on an organic substrate. This new package is also high yielding, manufacturable, reliable, and low in cost. This cost-effective packaging technology represents a shift in direction from the previous OLGA technology, and it also represents a significant milestone in the evolution of organic substrate technology.

# ACKNOWLEDGMENTS

The design and development of the FCPGA is a joint effort that spans several different organizations. We thank the entire FCPGA package design team, substrate development team, ATTD/QRE, and the assembly processes development staff for their hard work and devotion to support the development of this technology. We also acknowledge the great help received from the ATTD, ATTD/QRE/FA, and ATMO/CSMO divisions and other organizations. Finally, our special thanks to N. Grayeli, D. White, Jeff Watson, and M. Tay for their guidance and encouragement during packaging development. Finally, our thanks to the many others who contributed to the development of this program.

## REFERENCES

- [1] B. Sankman and M. Tay, "FCPGA Technology Target Specification," Intel internal document (1998).

- [2] Jim Irvine and J. Dunham, "FCPGA Package-B1 Design Requirements Document," Intel internal document (1999).

- [3] Jim Irvine and J. Dunham, "FCPGA Package-B2 Design Requirements Document," Intel internal document (1999).

- [4] Tim Takeuchi, A. Waizman, A. Hasan and C. Baldwin, "FCPGA Package-C Design Requirements Document," Intel internal document (1999).

- [5] C. Baldwin, "FCPGA Package-A Design Requirements Document," Intel internal document (1999).

- [6] Rao Tummala and Eugene Rymaszewski, *Microelectronics Packaging Handbook*, (1988).

- [7] Y. Guo, Y. Sha, C. Jayaram, and V. Wakharkar, "Low Cost Underfill Materials for Flip Chip Packages," *Intel Manufacturing for Excellence Conference* (*IMEC*), 2000.

## **AUTHORS' BIOGRAPHIES**

**Mirng-Ji Lii** is a Packaging Design Integrator in the Assembly Technology Development group at Intel. He has various experience in microprocessor packaging technology development and interconnect development such as flip chip, tape-automated bonding, and fine pitch wire bonding. He holds two U.S. patents and has published several technical papers. Currently, he leads a package design team to develop a cost-effective, highperformance packaging technology for future-generation microprocessors. His e-mail address is mirngji.lii@intel.com. **Bob Sankman** is the manager of the Design and Integration group in Assembly Technology and Development at Intel. He has held various technical positions in his career at Intel including wafer fab process engineer, failure analysis engineer, Q & R lab manager, and microprocessor package design manager. Bob has a B.S.Ch.E. degree from the University of Illinois. His email address is bob.sankman@intel.com.

Hamid Azimi is currently the program manager for x60 substrate supplier certification in the Assembly Technology Development group at Intel. Hamid and his team work with Intel substrate suppliers to develop and certify a substrate material/process, which can meet cost, quality, reliability, and electrical performance targets. This includes substrates for mobile, DT, and server applications within the x60 generation. Hamid graduated with a Ph.D. degree in materials science from Leigh University in 1994 with expertise in fatigue and fracture of polymer composites and metals. He joined Intel in 1995 and since then has been working in the Assembly Technology Development group in the Material Technology Development Department for different platforms including PLGA, OLGA, FCPGA1 and, now, X60. His e-mail address is hamid.azimi@intel.com .

**Hwai-Peng Yeoh** is an Integration and Substrate Development Manager in the Assembly Technology Development group in Intel, Malaysia. He has more than eight years of experience in advanced microprocessor packaging technology development that includes ceramic packaging for the P5 generation, dual cavity ceramic packaging for the P6 generation, Plastic Land Grid Array packaging, Multichip Module packaging for Itanium, and Flip-Chip Pin Grid Array packaging. He currently leads both integration and substrate development teams in FC-BGA1 packaging development for high-performance chipsets. His e-mail address is hp.yeoh@intel.com.

**Yuejin Guo** has worked at Intel for years in the areas of assembly material development, new technology transfer, assembly process development, and assembly HVM production. His current position is as a Sr. Materials Engineer in the Assembly Technology Development group. Before joining Intel he was at Los Alamos National Lab as a researcher. Yuejin's technical interests are primarily in the area of packaging materials. He graduated from Caltech with a Ph.D. in chemistry. His e-mail address is yuejin.guo@intel.com.

# The Evolution of Microprocessor Packaging

Ravi Mahajan, Assembly Technology Development, Intel Corp. Ken Brown, Assembly Technology Development, Intel Corp. Vasu Atluri, Assembly Technology Development, Intel Corp.

Index words: packaging, technology, building blocks, interconnect, power delivery/removal

## ABSTRACT

Microprocessor packaging is undergoing major changes driven by technical, business, and economic factors. From the traditional role of a protective mechanical enclosure, the modern microprocessor package has been transformed into a sophisticated thermal and electrical management platform. Furthermore, microprocessor architecture and design techniques can have significant impact on the complexity and cost of packaging. The need to optimize the total solution (chip, package, board, and assembly) has never been more important to maximize microprocessor performance and minimize cost. It is important to point out that the package represents a way of connecting the microprocessor to the motherboard. In this capacity, it enables the fine feature, silicon-level interconnects to be connected to the motherboard, i.e., the package assists in a space transformation in a controlled and economically viable manner. The key to packaging is to ensure that it enables and optimizes microprocessor performance. In its early evolution, the influence of the package on microprocessor performance was limited; however, as the microprocessor evolves to provide increasing performance, the package must evolve to keep up, and packaging design must ensure that it optimally enables the microprocessor. Package performance, in this context, implies a clear understanding and optimization of the package's electrical, thermal, and mechanical characteristics to enable overall electrical performance and power dissipation and to ensure mechanical robustness. Recent advances in microprocessor packaging indicate a migration from wirebond (where the chip or die is interconnected to the package only on the periphery of the die) to flip-chip (where the die is interconnected to the package using the entire die area); and from ceramic to organic packages, with cartridge and multichip technologies emerging as key form-factors. With the emergence of the segmented market (mobile, desktop, server and associated sub-segments), we see a significant proliferation of packaging types tailoring functionality and costs to the different markets. To address this proliferation, Intel focuses on packaging building blocks that can be configured for different applications. This paper traces the evolution of Intel's microprocessor packaging technologies, delineates the technical and business drivers, and highlights emerging trends. It then highlights the technical challenges faced by packaging developers now and in the future, and in a broad sense, it ties them into the challenges highlighted in the semiconductor industry technology roadmaps. Finally, it provides an introduction to the other papers in this issue of the *Intel Technology Journal*, which deal in greater detail with some of the technical challenges discussed in this paper.

## **INTRODUCTION**

In unit volume, microprocessors account for a small percentage ( $\sim \le 1\%$ ) of the semiconductor components sold worldwide. However, their technical and economic significance are far greater. Microprocessor packaging represents the technology envelope of this discipline. To better understand this statement, we present a historical perspective of microprocessors and follow with a review of the motivators and technology directions for this component of the semiconductor industry.

# THE EVOLUTION OF PACKAGING

## In the Beginning: The Mechanical Enclosure

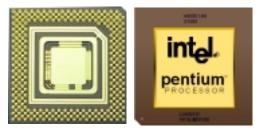

For many years, wirebonding and ceramic packages were the base assembly technologies for microprocessors because of their versatility and reliability. This was also true for Intel. Intel's 4004 microprocessor and later, the 8080, 8086, and 8088 microprocessors were all housed in ceramic dual-in-line packages (DIP) that used wirebond connections. By today's standards, these microprocessors had few Input/Output (I/O) pins (less than 40) and delivered very modest performance (<20MHz). The primary function of the package was to provide space transformation (i.e., fan out) of the I/Os in order to ease board routing and protect the chip from mechanical damage and from the environment. These were simple, single-layer packages. Figure 1 shows a typical example.

# Figure 1: A 40 Lead DIP package used to package the 8088 and 8086 microprocessors

## The Transition

In the  $i286^{\text{TM}}$  and  $i386^{\text{TM}}$  microprocessor generations, the number of I/O pins increased (~50 to 100) as greater functionality was incorporated into the microprocessor. This necessitated the use of Pin-Grid Array (PGA) packages in which a larger number of I/O connections could be accommodated in a small area. Also, in the i386 generation, it became evident that the increasing clock frequencies (a staggering 33MHz at the time) and simultaneous I/O switching could cause unwanted electrical coupling in the package manifesting itself as noise problems. Consequently, design and modeling competencies were substantially enhanced to account for these factors leading to the first use of multilayer ceramic packages at Intel. Figure 2 shows the i386 microprocessor package.

Figure 2: A 132L ceramic PGA package used for the i386<sup>TM</sup> microprocessor

### **Emergence of the Electrical/Thermal Platform**

The i486 microprocessor was also housed in a PGA package with 168 leads. In addition to the basic function of connecting the I/Os, advanced electrical design

concepts were incorporated. These included the use of power and ground planes as well as the inclusion of integrated capacitors in the package. These features transformed the package from a simple mechanical enclosure to a multilayer electrical distribution and signal-routing management platform.

The Intel® Pentium® processor helped in advancing this trend. In addition to the electrical features, the high-power dissipation, in the order of 15W, of the Pentium processor hastened the deployment of advanced thermal solutions such as an integrated heat spreader. These features, while effective, were expensive. An early version of the Pentium processor package is illustrated in Figure 3.

Figure 3: The Intel® Pentium® processor package in a ceramic PGA with a heat spreader

### The Need for Increased Integration

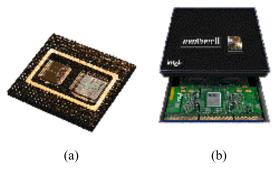

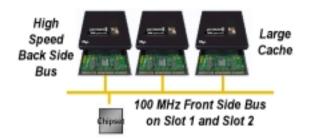

The next-generation microarchitecture, commonly referred to as the P6 microarchitecture, introduced in the mid 1990s, represented a new era of performance and complexity. The microprocessor architecture called for a dedicated cache chip connected to the microprocessor via a Backside Bus (BSB). The first implementation of this architecture was on the Intel® Pentium® Pro processor where the microprocessor and cache chips were housed in a dual-cavity ceramic PGA package and connected by wire bonding. Because of the special requirement in the I/O configuration and because of the electrical performance of the cache memory of this microprocessor, custom Static Random Access Memories (SRAMs) were used, an expensive solution.

The second-generation implementation of the same microarchitecture utilized a cartridge form-factor. In this instance, the microprocessor and cache chips were housed in separate component packages and were connected using a standard printed circuit board. To start with, the microprocessor was assembled using Plastic Land Grid Array (PLGA) packages with wirebond technology, which later transitioned to Organic Land Grid Array (OLGA) packages that utilized Controlled Collapse Chip Connection (C4) technology. Aside from the transition from peripheral interconnect to area array interconnect, this packaging transition also marked the use of a high-performance package substrate technology, i.e., OLGA technology. Plastic Quad Flat Package (PQFP) technology using wire bonding was used for the cache chips. This approach had two advantages over the dual-cavity ceramic PGA solution. First, it enabled the use of commodity Pipeline Burst SRAMs (PBSRAMs) thereby reducing cost. Second, the cartridge solution also allowed caches and other features to be customized for different market segments. The dual-cavity ceramic PGA and cartridge are shown in Figure 4. Figure 5 shows the portfolio of products packaged in a cartridge format.

Figure 4: (a) First-generation implementation of the P6 microarchitecture in a dual-cavity ceramic PGA (b) The Single Edge Cartridge Connector (SECC) cartridge is a second-generation form-factor

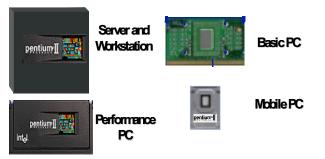

# Figure 5: Portfolio of products utilizing cartridge packaging

Although the cartridge form-factor was an effective technical solution, the emergence of the cost-sensitive Personal Computer (PC) market demanded even more aggressive cost/performance packaging solutions.

# Silicon Integration: Back to Single-Chip Packaging

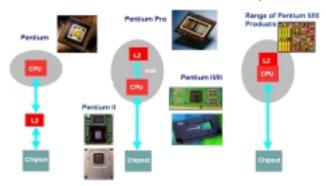

Silicon feature scaling and the integration of the Level 2 (L2) cache directly into the microprocessor die were key enablers to lower the cost of packaging. Without the need for the multidie package or cartridge to service the high-speed BSB, it was possible to move back to single-chip packaging. Several single-chip packages were developed with form-factors based on market segmentation requirements.

Some of these microprocessor packaging form-factors included

- low-profile and high-density pinned packages for mobile applications (Figure 6)

- pinned packages for sockets in desktops (Figure 7); the package substrate is referred to as the Flip-Chip PGA substrate, another version of the organic substrate technology

(b)

Figure 6: Views of low-profile micro-PGA for mobile socket applications; the micro-PGA uses an OLGA substrate surface mounted to an interposer

Figure 7: Pinned package for desktop socket; the package technology is referred to as Flip-Chip PGA (FC-PGA)

#### Figure 8: Intel® Itanium<sup>™</sup> processor packaging shows how different elements of packaging can be combined

The focus at Intel has been to create packaging technology building blocks that can be combined to provide multiple features and form-factors, while minimizing piece part, process, and manufacturing costs. An example of this can be seen in Figure 8, which illustrates the packaging for the Intel® Itanium<sup>™</sup> processor. However, before we discuss Intel's focus, we present an account of the technical and business drivers as well as the emerging directions for packaging technology.

## **TECHNICAL AND BUSINESS DRIVERS**

Microprocessor packaging requirements are closely and intricately tied to the performance and architecture of the microprocessor. Figure 9 depicts the evolution of microprocessor/cache/bus architecture. Using this evolution as a framework, we examine five major drivers:

## Figure 9: Evolution of the microprocessor and cache architecture from the i486<sup>™</sup> microprocessor to the Intel® Pentium® Pro microprocessor

### **Driver #1 : Connecting the Cache**

As the performance of microprocessors increased, the need to supply data and instructions to the microprocessor increased accordingly. This information normally resides in the main memories, such as the Dynamic Random Access Memory (DRAM) and disks, and it is channeled to the microprocessor via the bus, a parallel set of interconnects running between the microprocessor and the memory. The wider (i.e., more data lines) and faster the bus, the more data can be transferred at a given time. Since the days of the i486<sup>™</sup> microprocessor, the speed requirements for data to be transferred to the microprocessor have exceeded the speed of the main memories (DRAMs). As a result, an L2 cache system utilizing fast Static RAMs (SRAMs) was added to the microprocessor architecture. This L2 cache stores frequently used data thereby reducing the need for frequent access to the external main memories. Consequently, this speeds up execution and leads to enhanced performance.

As described in the previous section, the Intel® Pentium® II/Pro microprocessor architecture had a dedicated BSB connecting the microprocessor to the L2 cache to further enhance the performance. Initially, this architecture was implemented by connecting the microprocessor and cache inside a ceramic package using wire bonding. This required custom SRAMs and expensive packaging. The implementation evolved to the use of a cartridge form-factor whereby commodity PBSRAMs were connected to the microprocessor by using a printed circuit board.

In the later silicon technology generations, improved Very Large Scale Integration (VLSI) density made it practical to integrate the cache into the same microprocessor chip. This accomplished two major objectives:

- It lowered the cost by eliminating the need for external PBSRAMs and the cartridge.

- It gave higher performance because of a full-speed BSB integrated into the silicon.

This is the current trend for future microprocessors. Consider, for example, the die shown in Figure 10. These are similar die except some have integrated caches and some don't. For a small increase in die size, it is possible to accomplish the two objectives mentioned above.

As silicon features shrink, this mitigates the initial chip size penalty of adding the L2 cache.

Figure 10: P6 architecture die with and without integrated L2 cache

Future microprocessors may also integrate part of the chipset into the same silicon thereby further reducing the interconnect complexity and costs at the system level.

### **Driver #2: Connecting the Bus**

Although the incorporation of the L2 cache alleviates data traffic on the microprocessor bus, an increase in the bandwidth of the microprocessor bus is still necessary in many applications where I/O bandwidth is important, such as graphics and servers.

To enable high performance, the microprocessor bus speed evolved from an 8 MHz Industry-Standard Architecture (ISA) bus on the original PC-Advanced Technology (AT) to a 100 MHz bus on today's microprocessors. Moreover, there are clear indications that we need to further increase this speed and bandwidth. Aside from the raw speed, additional challenges in high-end systems include the use of multiple processors on a single microprocessor bus. This requires the support of several electrical loads on the same bus thereby necessitating very precise electrical designs to achieve the desired performance. Figure 11 illustrates this configuration.

Figure 11: Multiprocessor on a microprocessor bus

To manage these high-performance electrical environments, the interconnections from the silicon through the package to the system board must be designed as an integral unit in order to ensure the desired electrical characteristics. From a technology viewpoint, this requires high-conductivity interconnect traces, low capacitance, and matched impedance for high I/O speed to minimize noise generation. The design of the I/O drivers/receivers on the silicon must also account for package as well as system interconnects. Careful matching of impedance, voltage signal levels, and timing is essential to guarantee performance.

## **Driver #3: Power Delivery**

The third driver is delivering power to the chips. A key element that enabled the advances in silicon technology and the resultant density and performance improvements from generation to generation is the scaling of the supply voltage. While this approach is beneficial to silicon scaling and power dissipation, the challenge of delivering power to the silicon chip via the package is increased. There are two elements to power delivery:

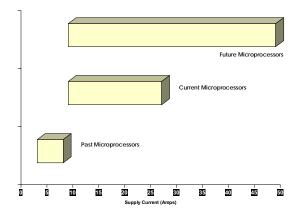

#### (a) DC (average) supply current

As the supply voltage was scaled, the integration of additional functions and operations at higher clock speeds kept the power dissipation high. As a result, the average supply current increased significantly. This high current was delivered from the power supply on the system motherboard to the chip through the package. As illustrated in Figure 12, the typical supply currents were in the 10 - 20 A range, a range that is expected to increase for future processors. To handle this high current, the package must provide a very low resistance path, in the order of < 1 mili-ohm.

#### (b) AC (di/dt switching) current

Even more challenging is the management of the switching current. The high clock speed circuits and power conservation design techniques such as clock gating and SLEEP mode result in fast, unpredictable, and large magnitude changes in the supply current. The rate of change of many Amps per nanosecond of this switching current far exceeds the ability of the power supply and the voltage regulator to respond. If not managed, these current transients manifest themselves as power supply noise that ultimately limits how fast the circuits can operate. This is further compounded by the reduced noise margin in the Complementary Metal-Oxide-Silicon (CMOS) logic circuits that result from power supply voltage scaling.

To mitigate this undesirable noise effect, the package must provide a very low inductance path for the switching current. In addition, charge storage devices, in the form of capacitors native to the silicon chip and augmented by capacitors on the package, are also necessary in some designs.

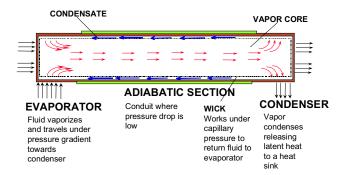

### **Driver #4: Dissipating Power**

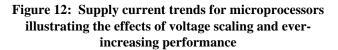

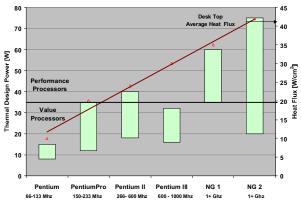

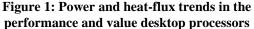

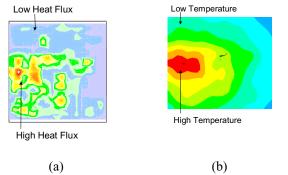

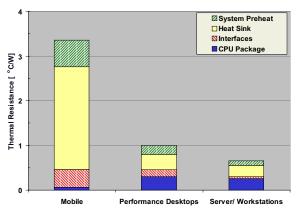

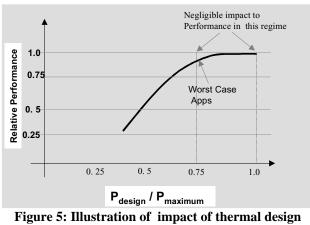

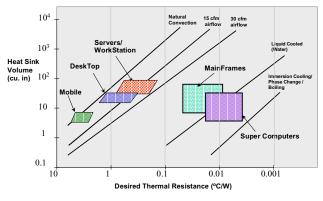

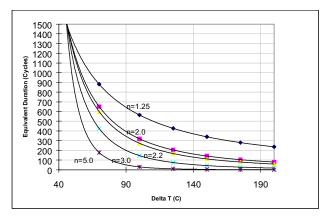

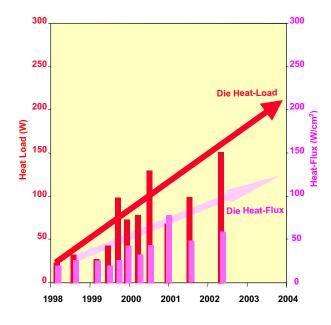

Dissipating high power, and managing high-power density, is another challenge. With the high density of integration and high clock rates, advanced microprocessors dissipate a significant amount of power in a very small physical area. Figure 13 illustrates the problem.

### Figure 13: Power density trends of microprocessors

Another factor that exacerbates the thermal management problem is that local areas of the die, depending on where different functions are executed, have higher power densities than the average power density. The challenge to packaging is to ensure that the thermal path from die to the environment is optimized to allow for effective spreading and ducting of heat to the environment. In a broad sense, thermal management involves

- accurately estimating the power dissipation requirements, including power, on-die power distribution, and die temperature expectations,

- managing the thermal performance of all interfaces in the thermal path from die to the environment,

- providing and optimizing the spreading characteristics of all the thermal elements from die to the environment including the package heat-spreader and the heat sink, and finally,

- managing the thermal environment in the chassis by ensuring that the local air temperature is as low as possible to provide a better environment for the microprocessor to dissipate heat.

It is clear that the increasing thermal challenge requires advanced thermal management to ensure chip functionality and reliability.

## **Driver #5: Silicon Density and Die Shrinks**

As silicon technologies advance, the size of the physical feature that can be fabricated gets smaller. Correspondingly, a given amount of circuitry can be built in a smaller die area. Both Intel and the rest of the semiconductor industry employ an aggressive die shrink or die compaction strategy to reduce the silicon area. This approach has two major benefits. First, by reducing the die area, more die can be fabricated on the wafer, hence the cost is lower. Second, a reduction in die area results in higher speed and lower power dissipation for the same speed. This trend is illustrated in Figure 14.

### Figure 14: Die shrinks driven by advances in silicon technologies necessitate corresponding improvements in chip-to-package interconnectivity

As the die size shrinks, the number of I/O connections does not change. Furthermore, the number of power supply connections is often increased to support the performance increases brought on by the die shrink. These factors result in a decrease in the bonding pitch for wire bonding or bump pitch for flip-chip. In order to keep pace with this trend, the package geometries and the assembly technologies must also evolve. Today, very fine pitch wire bonding has brought wire bonding down to a pitch of 65 microns. The pitch used on flip-chip arrays is considerably larger, currently in the range of 200 microns, as it utilizes the entire surface of the die to lay out the bumps. Nevertheless, this bump pitch still has to be scaled to keep pace with silicon scaling and die size reduction.

## **Driver #6: Socketability**

Socketability is a business requirement. The reasons for socketability include Original Equipment Manufacturer (OEM) inventory control, the impact of tax and duty, and manufacturing flexibility. From a technical standpoint, socketability is not desirable. In most cases, it makes the package larger, more expensive, and the performance is lower. Nevertheless, the quest for a low-cost, high-performance socketable package is a strong business-driven requirement.

## THE TECHNOLOGY AGENDA

To meet these challenges, the Assembly Technology Development group within Intel has been engaged in defining and creating many new technologies to serve as building blocks as well as integrating the design and analysis environments. The key building blocks are as follows:

- 1. A packaging technology that has high electrically conductive metallurgy that minimizes the IR drop and acts as a high-current conduit to deliver power from the power supply to the chip, such as copper conductors in organic packages.

- 2. Low-inductance connections from chip to the package and from the package to the socket, such as flip-chip interconnects.

- 3. Low-capacitance insulator materials, such as organic packages.

- 4. Advanced thermal-interface materials and a focus on thermal design to manage the high-power density.

- 5. An integrated analysis, design, and validation environment that enables dynamic trade-offs between chip and package design and layout in the interconnect continuum that includes Computer Aided Design (CAD) tool suites, test vehicles, etc.

- 6. Predictive models especially in power delivery, power dissipation, and Electromagnetic Interference (EMI).

These building blocks have been in development at Intel for the past several years. Accordingly, a number of significant technology transitions is already underway.

## Transitions

### Away from Wire Bond and Ceramics

Versatile, ceramic package technology can be expensive. Furthermore, as performance increases, the physical characteristics of ceramic packages may become limiting. Specifically, a ceramic material based on Al<sub>2</sub>O<sub>3</sub> has a relatively high dielectric constant ( $\varepsilon_r \sim 7$ -8). Additionally, because of the high-temperature processing, metallization is limited to refractory metals, such as Molybdenum and Tungsten, which are quite resistive. Wire bond connections have relatively poor electrical characteristics because of their high inductance. As described above, high-resistive, inductive, and capacitive structures are not conducive to high performance. Ceramic substrate suppliers are addressing some of these limitations with advances in their materials.

## **Use of Organic Packages**

A key thrust pursued at Intel, was the transition from ceramics to organic laminate packages. It started in 1996 with the introduction of the Intel® Pentium® processor in the Plastic Pin Grid Array (PPGA) package. Today, all of Intel's microprocessors are in organic laminated packages.

In contrast to ceramic packages, organic laminated packages utilize epoxy resin dielectric materials ( $\varepsilon_r \sim 4.2$ ) and copper conductors. These low dielectric characteristics and copper result in substantial improvements in power distribution and signal transmission characteristics.

The organic package is also indigenous to our latest flipchip packaging. The attributes of this package provide significant boosts to power distribution and signal routing on the chip. The table below contrasts the physical and electrical characteristics of a typical silicon circuit versus that of a flip-chip OLGA. In short, the routing density is much higher on the silicon, but the electrical characteristics are much better on the organic package. Hence, a judicious use of these capabilities in an interconnect continuum can result in optimal product performance and cost.

| Conductor | Pitch<br>(µ) | Mater<br>ial | Thk<br>(µ) | Sheet<br>Rho<br>(m ) | Insulator |

|-----------|--------------|--------------|------------|----------------------|-----------|

| Si        | 0.5          | Al-Cu        | 0.5        | ~85                  | Oxide     |

| C4-OLGA   | 70           | Cu           | 17         | ~0.01                | Epoxy     |

In order to meet the tight pitch demands for chip-area array interconnect (C4 discussed in next section), it was necessary to construct a new organic package. This package uses a laminated core set of layers with highdensity "build-up" layer(s). The high-density layers are used to match the pitch on the die. This package is illustrated in Figure 15.

### Figure 15: Cross-sectional view of organic flip-chip package illustrating core and high-density build-up layers

Refinements to this technology have been developed to allow alternative package form-factors, as described earlier, based on market segment needs.

Another advantage of organic packaging is that the Coefficient of Thermal Expansion (CTE) of the package is more closely matched to that of the motherboard as compared to a ceramic package. This ensures that the stresses induced in the package-to-motherboard interconnects are significantly lower, resulting in more reliable interconnections even when the interconnect count is large. This is especially true of Ball Grid Array (BGA) connections where interconnect reliability is of significant importance.

## C4 Flip-Chip

In order to optimally access the superior electrical characteristics of the organic package, we must also establish a high-density, high-performance method to connect the chip to the package. To that end, a solderbump-based C4 area array flip-chip capability was developed to replace wire bonding.

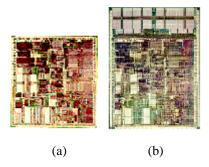

In contrast to traditional wire bonding, C4 utilizes an area array method for interconnection. The C4 bumps can be placed anywhere on the die, even over active circuitry. This enables the placing of many more bumps as virtual vias (through the thick electrical connections) connecting the metallization on the chip to the metallization on the package. In fact, the metallization on the package can be visualized as metal layers augmenting the metal layers on the chip. The primary benefit of this approach is in power/ground distribution and clock routing. The C4 connections, in combination with the electrical characteristics of the copper-based organic packages, result in a superior electrical environment where maximum performance can be realized. As an example of this implementation, consider the same die, P6 architecture, in both the wire-bonded and C4 versions as shown in Figure 16. The substantial increase in power/ground connections ensures maximum performance. Additionally, a native C4 die design eliminates the need for bond pads, which results in a small die, ~0.012 inches smaller per side.

Wirebonded C4 Flip-Chip ~250 P/G ~1600 P/G

# Figure 16: P6 architecture microprocessor implemented as wire-bonded die and in C4 Flip-Chip

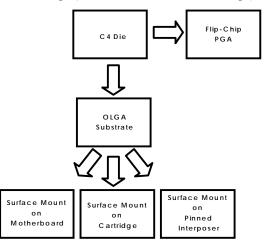

In this paper, we discuss packaging and technology building blocks as a key concept to cost effectively meet a wide range of both form-factor (surface-mount, highdensity pinned, low-density pinned, etc.) and performance needs for packaging by a judicious combination of these building blocks.

Figure 17 further illustrates this concept. A single bumped die is mounted on either a surface mount (OLGA) or a pinned substrate. The OLGA substrate can subsequently be surface mounted directly to a board, mounted to a pinned substrate for socketing, or mounted to a cartridge (to be combined with other chips).

Figure 17 : Building-block technologies

## **FUTURE CHALLENGES**

As microprocessors continue to improve in performance, technical challenges in packaging will also increase. A comprehensive view of these challenges can be found in the 1999 International Technology Roadmap for Semiconductors (ITRS) [1]. This roadmap discusses the need for improved materials and assembly processes as well as a need to have integrated simulation tools and methods to assess the reliability of the integrated diepackage-motherboard system. Since the design environment and the assembly processes and reliability aspects of packaging fall outside the scope of this paper, we limit this discussion to the technical challenges in packaging as they impact microprocessor performance. Technically, the challenges fall into three broad categories: power delivery, power removal, and also the provision of viable, i.e., appropriately scaled with optimal performance characteristics, interconnection strategies between silicon and board.

Power delivery challenges are highlighted in Figure 12. To move forward, the focus will have to be on continuing to understand and optimize the electrical path from power supply to the die. With increasing demand for performance, the general separation of market segment requirements and constraints, and the shortening of the time-to-market, it is expected that the power delivery solutions will continue to be challenging.

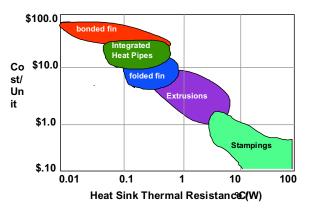

Power removal, i.e., thermal management of the processor, is another increasingly challenging aspect of packaging. As shown in Figure 13, the average power density of processors is expected to increase. problem will be exacerbated by the need to manage local power densities on die. The development of costeffective and technically viable thermal management solutions that maintain die temperature at acceptable levels will be key to ensuring future success. This can be accomplished through development and deployment of effective spreader solutions and thermal interface materials. Controlled assembly processes to manage the thermal interfaces are also a key to successful design. Finally understanding and managing the die power, power distribution, and the thermal environment in the chassis are important.

Silicon technology in the future is expected to scale aggressively, which will require intelligent space transformation methods from packaging. Ensuring that the interconnects have refined electrical characteristics so that packaging provides the appropriate space transformation while enabling the required electrical performance will be essential to future development.

# SUMMARY

In this paper, we discuss the evolution of microprocessor packaging from a simple protective enclosure to a more technically complex and challenging platform that enables optimal microprocessor performance. The general strategy adopted within Intel to address continuing challenges is to develop building blocks that can be effectively combined to meet the needs of current and future microprocessor packaging. The remaining papers in this issue of the *Intel Technology Journal* discuss different aspects of these challenges in greater detail.

The 2<sup>nd</sup> paper discusses the FC-PGA package, i.e., flipchip technology on organic pin grid array substrates. The paper looks at the motivations that led to the development of this package technology, its characteristic features and capabilities, and some of the issues that were successfully addressed during the development and deployment of this technology into high-volume manufacturing.

The 3<sup>rd</sup> paper discusses the technical complexity of interconnect design to achieve optimal electrical performance. This paper also discusses the design analysis and synthesis techniques used to ensure optimal electrical design.

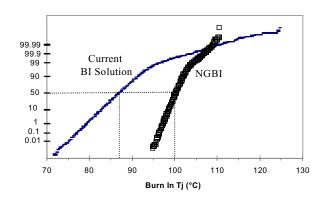

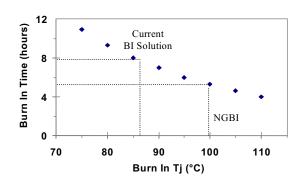

The 4<sup>th</sup> paper discusses challenges in power removal. Thermal solutions that are optimized for cost and performance and tailored to meet different market segment needs are a key enabler to successful microprocessor deployment. This paper discusses some of the considerations that must be taken into account to ensure successful thermal design.

Underfill processes and underfill material development are a major component of flip-chip packaging processes. The 5<sup>th</sup> paper discusses a novel method of accomplishing this objective.

Ensuring that packaging continues to meet high standards of reliability is a key to success. The 6<sup>th</sup> paper discusses how our assessment of reliability has evolved during the past few years. Intel has moved from a stress-based certification strategy to a more fundamental mechanism-based methodology that allows for a better linkage between stress testing and the end-user environment.

Finally, the 7<sup>th</sup> paper talks to the practical problem of managing the thermal environment during microprocessor testing. The goal of testing is to effectively assess performance and reliability without introducing artifacts due to the testing process. This paper examines how this goal can be accomplished and looks at some of the unique issues that should be addressed.

# CONCLUSIONS

High-performance and cost-effective microprocessor technologies require a holistic approach that comprehends the interconnect continuum including the silicon, the package, and the system. By properly exploiting the attributes of these regimes, optimal performance and cost can be realized. This review of the evolution of packaging reinforces the view that it will be a technically challenging and rewarding area of focus.

# ACKNOWLEDGEMENTS

The authors thank Bill Siu for providing the essential framework of this paper. We also acknowledge the support of Scott Shirley, Susan Coartney, and Keith Carnes in procuring some of the graphics for this paper.

# REFERENCES

[1]"International Technology Roadmap for Semiconductors," 1999 Edition, Semiconductor Industry Association.

# **AUTHORS' BIOGRAPHIES**

Ravi Mahajan is currently the manager of a Thermal and Mechanical Analysis group in Assembly Technology Development. His group provides design and analysis support in the development of advanced packaging for Intel processors and chipsets. He also leads a group of thermal experts from different organizations within Intel. This group is chartered with developing and maintaining the thermal roadmap for Intel microprocessors. Dr Mahajan received his B.S. degree in Mechanical Engineering from the University of Bombay (1985), his M.S. degree in Mechanical Engineering from the University of Houston (1987), and his Ph.D. degree in Mechanical Engineering specializing in fracture mechanics from Lehigh University (1992). Dr. Mahajan holds several patents in packaging, has edited two conference proceedings for the Society of Experimental Mechanics, and is currently one of the editors of an Intel Internal Technology Journal. His e-mail is ravi.v.mahajan@intel.com.

Ken Brown is manager for non-CPU Packaging Development in the Assembly Technology Development group at Intel. He has worked in the semiconductor industry for 19 years, and currently serves as Intel's representative to the SIA International Technology Roadmap for Semiconductors (ITRS) packaging committee. His first 17 years were with Digital Equipment Corporation, where his last position was as Manager of the Package Design & Development organization. He moved to Chandler and ATD about two years ago following Intel's acquisition of Digital Semiconductor. He received a B.S.M.E. degree (1981) from the University of Massachusetts, an MBA from Northeastern University (1985), holds two patents in has presented at several packaging. packaging conferences, and authored a chapter on packaging for a graduate book. His e-mail is text ken.m.atd.brown@intel.com.

**Vasu Atluri** is currently a Silicon Integration Manager in Assembly Technology Development. His group is responsible for ensuring that all technical issues are properly managed to enable a successful interface between silicon and assembly technology development groups. He is also responsible for the design of test chips that help validate performance and reliability of silicon after it has been packaged. He also helps in defining design rules for product designs.

Dr Atluri received a B.S. in Chemical Engineering from Osmania University (1982), anM.S. in Materials Science and Engineering from University of Arizona (1987), an M.S. in Chemical/Metallurgical Engineering (1988), and a Ph.D in Materials Science and Engineering from University of Arizona (1998) with a specialization in silicon fabrication. Dr. Atluri has more than twenty technical publications in conference proceedings and journals. He has presented at several technical conferences. He has filed for couple of patents in silicon processing. Dr. Atluri is currently one of the editors of Intel's Assembly and Test Technology Journal, which is Intel Corporation's Internal Technology Journal. Dr. Atluri is an active member of IEEE and is currently serving as Vice-Chair for IEEE Phoenix Section. Dr. Atluri maintains active participation in a wide array of academic forums associated with electronic packaging. His e-mail is vasudeva.atluri@intel.com.

# Simultaneous Chip-Join and Underfill Assembly Technology for Flip-Chip Packaging

Tom Dory, Assembly Technology Development, Intel Corp. Kenji Takahashi, Japan Package Technology Development, Intel Corp. Tomomi Kume, Japan Package Technology Development, Intel Corp. Jiro Kubota, Japan Package Technology Development, Intel Corp. Seiichiro Seki, Japan Package Technology Development, Intel Corp. Takaharu Fujiyama, Japan Package Technology Development, Intel Corp.

Index words: C4, underfill, packaging, flip chip

## ABSTRACT

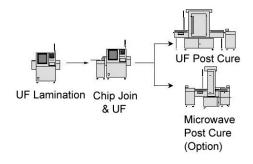

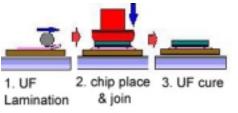

Controlled Collapse Chip Connection (C4) flip-chip packaging is the current state of the art assembly technique. The C4 Organic Land Grid Array (OLGA) technology process to attach a silicon die to a package substrate involves seven process steps.

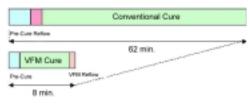

In the current plan of record (POR) C4 OLGA flip-chip assembly process, solder wetability is achieved by removing Pb/Sn oxide films from the bump material by means of a flux and deflux process. An epoxy material is placed between the die and package. This underfill (UF) process has a long epoxy application step and curing time.

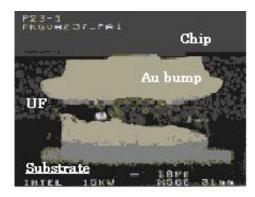

We present a three-step chip-join assembly process using a no-flow-type underfill material combined with nonlead-containing bump metal on the chip side. This process has fewer process steps than the POR assembly process, and the underfill cure time is also reduced.

The process described in this paper shortens the assembly process by eliminating fluxing, defluxing, and furnace reflow steps. We achieved more than a 90% assembly yield as a result of process parameter and material property optimization.

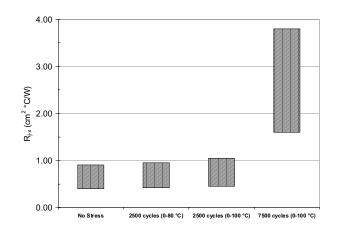

## INTRODUCTION