#### Preface

Lin Chao Editor Intel Technology Journal

This Q4'98 issue of the Intel Technology Journal (ITJ) describes Intel's manufacturing processes and strategies. Semiconductor manufacturing is characterized by very complex process flows made up of many process steps, all built to very close tolerances. Furthermore, there are complex interactions in these process flows. The papers in this issue describe how Intel develops components technology and manufacturing capability to deliver high-performance, costeffective, quality products.

In 1965, Gordon Moore, co-founder of Intel, was preparing a speech and made a memorable observation. He observed that device complexity doubles about every 18 months. This observation is now known as Moore's Law. While originally intended as a rule of thumb, it has become the guiding principle for the industry spearheading the delivery of ever-more-powerful semiconductor chips at proportionate decreased costs. Intel has expended enormous resources to meet the predictions of Moore's Law through factory modeling, knowledge management, operational and simulation modeling, capacity supply line management using Goldratt's Theory of Constraints, and defect yield monitoring. These techniques are described in detail in this issue.

Among these techniques is Intel's proven Copy EXACTLY! methodology for factory ramp and high-volume manufacturing, which is described in detail in this issue. Copy EXACTLY! enables Intel to bring factories on-line quickly with high-volume practices already in place; hence, decreasing time to market and increasing yields. Copy EXACTLY! solves the problem of getting production facilities up to speed quickly by "copying" everything--process flows, equipment set, suppliers, plumbing, manufacturing clean room, and even training methodologies--from the development plant to the volume-manufacturing plant.

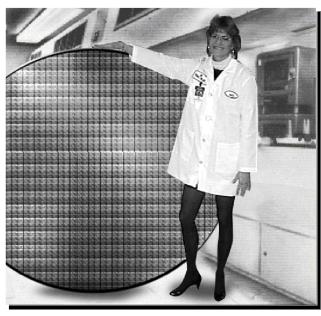

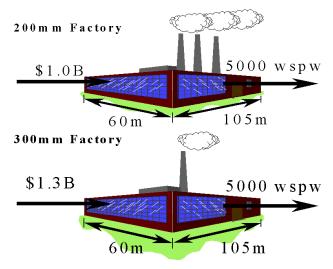

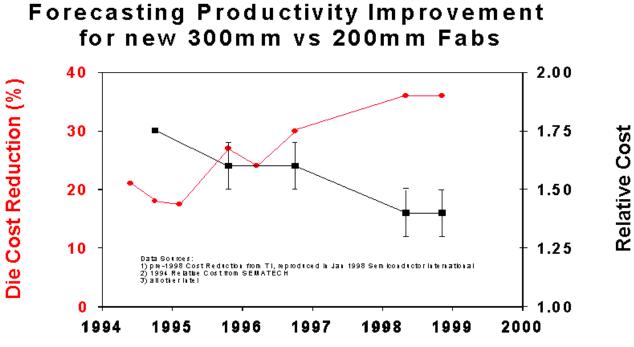

As we near the new millennium, the semiconductor industry is getting ready for the transition from 200mm to 300mm wafer size. This is a major milestone for the industry, and teams are in place at Intel to implement the transition. An interesting retrospective look at how the 300mm standard was selected is described in another paper in this issue.

# Intel's Manufacturing-a Competitive Edge

# By Mike Splinter,

Corporate Vice President and General Manager, Technology and Manufacturing Group Intel Corp.

Intel has a long history of technology innovations that have led the industry in establishing new capabilities in semiconductor technologies thereby enabling advances in computing. One of our successes in helping drive technology has been our ability to incorporate innovations in our manufacturing sciences. This is a critical strategy as technology alone will not ensure that products can be built at the right volumes with the right costs and then delivered to our customers at the right time.

During the 80's, we were driven to find methods to improve our manufacturing competence. Our competitors were achieving higher yields, transferring and ramping new technologies faster than us, and, overall, running their factories more efficiently. To remain competitive, we made the basics of manufacturing technology a key piece of our agenda.

One of the main issues we faced was the phenomenon of something called the Intel U. The Intel U was a predictable drop in factory performance every time a new technology or product was developed and transferred to manufacturing. This phenomenon, when plotted as a function of yield versus time, always showed a U-shaped curve. There were many approaches taken over the years to fix this problem but until the concept of Copy Exactly! was developed, we had limited success in eliminating the Intel U. Today, this phenomenon is non-existent, and Intel U stands for Intel University, not a yield problem.

There have been many innovations in manufacturing that have addressed, among others, defect improvements, modeling, capacity management, and improving the speed of our supply line. Today, Intel is faced with the challenges of developing new concepts and methods in manufacturing in order to address the changes we have seen in the marketplace. The world is moving at Internet speed fostering the concepts of build to order, E-Commerce, product segmentation, and so on. As we move into the future, we will need focus to not only on TECHNOLOGY, but also on COST, SPEED, AND FLEXIBILITY in order for manufacturing to continue to provide Intel with a key competitive advantage over the next decade.

Copyright © Intel Corporation 1998. This publication was downloaded from <u>http://www.intel.com/</u>.

Legal notices at <u>http://www.intel.com/sites/corporate/tradmar</u> <u>x.htm</u>

# 21st Century Semiconductor Manufacturing Capabilities

Eugene S. Meieran, Intel Fellow Technology Manufacturing Engineering, Intel Corp.

Index words: manufacturing, operational cost, NGM program

#### Abstract

Semiconductor device manufacturers face many difficult challenges as we enter the 21<sup>st</sup> century. Some are direct consequences of adherence to Gordon Moore's Law, which states that device complexity doubles about every 18 months. Feature size reduction, increased wafer diameter, increased chip size, ultra-clean processing, and defect reduction among others are manifestations that have a direct bearing on the cost and quality of products, factory flexibility in responding to changing technology or business conditions, and on the timelines of product delivery to the ultimate customer.

Regardless of these tremendously complex problems, the industry is focused on meeting the predictions of Moore's Law, for which enormous resources are expended.

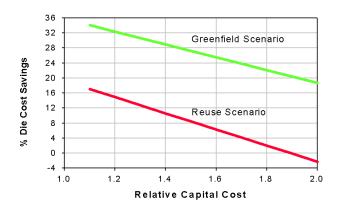

One of the great challenges ascribed to Moore's Law, that facility costs increase on a semi-log scale, is now known as Moore's Second Law. However, unlike his First Law, the industry would prefer to depart from Second Law predictions to avoid hugely expensive (\$20 Billion) future fabs and attendant high chip costs. Logistics control, inventory management, better facility design, supplier management programs, etc. are all responses to Second Law predictions, to which many resources have been devoted.

Other pressures on factory management are emerging. In addition to cost considerations, reduction in feature size and increasingly complex devices, the Massachusetts Institute of Technology/Leaders For Manufacturing-led program, "Next Generation Manufacturing" (NGM) identifies the following issues as significant:

- globalization of supplier, customer, and factory base

- exponential growth of information and knowledge management capabilities that enable faster and better decisions

- development of new materials and processes at atomic scale dimensions

- faster delivery of higher quality products to an increasingly demanding customer

- rising awareness of environmental and energy concerns This paper discusses the technological responses of indus-

try management and university faculty to the predictions of Moore's Second Law. Special attention is given to knowledge management and operational modeling and simulation technology. These processes help us better understand the benefits of various alternatives used to affect factory performance as traditional methods such as yield improvement, automation, increased wafer size, equipment reliability, etc. lose their leverage.

#### Introduction

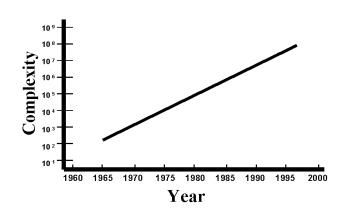

Gordon Moore first proposed the law that bears his name in the late '60's: chip complexity (as defined by the number of active elements on a single semiconductor chip) will double about every device generation, usually taken as about 18 calendar months [1]. This law has now been valid for more than three decades, and it appears likely to be valid for several more device generations, as shown in Figure 1.

Figure 1: Moore's First Law

The compelling desire of the semiconductor industry to follow Moore's Law has affected high-volume device manufacturing, driving both the cost per bit of the devices and the overall cost of the fabrication and assembly facilities needed to build them. (Additional effects such as those on the ramp rate towards high-volume manufacturing are also experienced, but these are not discussed in this paper.) For Moore's Law to remain valid, feature size must continue to be reduced, but since this reduction is insufficient in and of itself, chip size must continue to increase. Together, these two trends have not only maintained Moore's Law, but have accounted for the phenomenal success of our industry, since the cost per device element has now decreased by several orders of magnitude! Compared to *every* other commodity in the world, semiconductor chips are *cheap*, and continue to get cheaper (on a per element basis) every year.

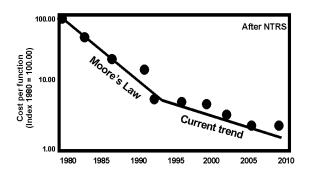

The reduction in cost per active chip element is shown in Figure 2. Notice that while this cost continues to decrease, there appears to be a break in the curve: one section follows early predictions of Moore's Law, and the other departs from these predictions. This will be discussed later.

Figure 2: Cost per chip element

Many programs are associated with following Moore's Law and each has consequences for the cost per chip element, as shown in Table 1.

|                                     | 1975 | 1997 | 2003 |

|-------------------------------------|------|------|------|

| Chip complexity (index to 1)        | 1    | 10   | 100  |

| Feature size reduction, µ m         | 2    | 0.25 | 0.08 |

| Chip size increase, mm <sup>2</sup> | 30   | 150  | 600  |

| Wafer diameter, mm                  | 50   | 200  | 300  |

| Facility automation, %              | 5    | 60   | 80   |

| Die yield, % good                   | 40   | 85   | 95   |

| Line yield, % good                  | 40   | 90   | 95   |

| Assembly/test yield, %              | 90   | 99   | 99   |

| Defect levels, DPM                  | 2%   | 500  | 50   |

Table 1: Programs to maintain Moore's Law

Most of these programs tend to contribute to a reduction in chip element cost, but some of them, especially those dealing directly with increased chip and process complexity, tend to increase that cost. Fortunately, scaling, reduced feature size, improved yield, and increased wafer diameter more than make up for the added costs of more expensive packages and more complex processing.

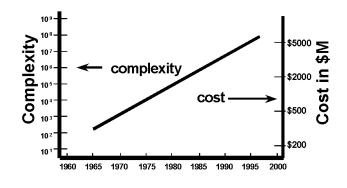

Figure 3 shows the other major consequence of following Moore's Law. The reduction in cost per chip element is just offset by the increase in element density, leading to an essentially constant cost per individual chip. However, as a result, overall factory costs increase almost exponentially as we struggle to meet the ever increasing demand for more and larger high-performance chips. In order to meet cost per chip goals, cost per factory has increased to the point where highvolume factories now cost several billion dollars! So being successful in reducing chip costs brings its own share of additional problems. Building, equipping, and maintaining billion dollar factories tax even the most successful companies. This explosion of factory cost has come to be known as Moore's Second Law—one we do NOT wish to follow with such great zeal!

Figure 3: Moore's Second Law

Many of the same programs that have driven cost per chip element down are also responsible for the trend shown in Figure 3. In addition, some operational programs that have had little direct influence on cost per chip element have significant influence on factory cost. These additional programs are shown in Table 2.

|                                     | 1975 | 1997 | 2003 |

|-------------------------------------|------|------|------|

| Chip complexity (index to 1)        | 1    | 10   | 100  |

| Feature size reduction, µ m         | 2    | 0.25 | 0.08 |

| Chip size increase, mm <sup>2</sup> | 30   | 150  | 600  |

| Wafer diameter, mm                  | 50   | 200  | 300  |

| Facility automation, %              | 5    | 60   | 80   |

| Die yield, % good                   | 40   | 85   | 95   |

| Line yield, % good                  | 40   | 90   | 95   |

| Assembly/test yield, %              | 90   | 99   | 99   |

| Operational efficiency              | 1    | 10   | 100  |

| Equipment cost                      | 1    | 10   | 50   |

| Defect levels, DPM                  | 2%   | 500  | 50   |

Table 2: Factory cost control programs

Tables 1 and 2 are combined, below, in Table 3, which shows two emerging problems with regard to both cost per chip element and factory cost containment:

- 1. Some goals of the programs are in conflict: lowering the cost per element actually adds to factory cost.

- 2. The leverage of some of the programs is diminishing: for example, we will not exceed 100% yield or 100% automation.

Hence, other means are necessary to meet cost projection goals for factories and chip elements.

|                        | Cost per function | Factory Cost |

|------------------------|-------------------|--------------|

| Complexity increase    | Up                | Up           |

| Feature size reduction | Down              | Up           |

| Chip size increase     | Down              | Up           |

| Wafer size increase    | Down              | Slowing      |

| Facility automation    | Down              | Slowing      |

| Die vield              | Down              | Slowing      |

| Line yield             | Down              | Slowing      |

| Assembly/test yield    | Down              | Even         |

| Operational efficiency | Down              | Down         |

Table 3: Comparison of programs

The major program that does **not** suffer from topping out or from conflict is improving operational efficiency. However, before we discuss this, some additional forces acting on the manufacturing environment are discussed.

# **Emerging Trends**

The additional forces acting on the manufacturing environment have little to do with Moore's Law. These forces are discussed in the National Science Foundation sponsored program, "Next Generation Manufacturing" conducted by the Leaders For Manufacturing program at MIT, the Agility Forum and the Technology to Enable Lean Manufacturing [2]. The major issues are listed in Table 4.

Globalization refers to the fact that for a number of reasons, industries are locating manufacturing facilities in many geographical locations, utilizing a supply of skilled workers at reasonable wages and servicing a widely dispersed customer base. As a result, suppliers of parts, materials, and equipment for these factories have had to become globalized, since operating conditions for manufacturers dictate that short time to delivery to the local customer is a matter of competitive necessity.

Manufacturing globalization:

Factories

|   | ~ !!                                |

|---|-------------------------------------|

|   | - Suppliers                         |

|   | - Customers                         |

| • | Increased global competition        |

| • | Increased customer expectations     |

| • | New technologies and processes      |

| • | Environmentally aware manufacturing |

| • | Human factors:                      |

|   | - Training and retraining           |

|   | - Redeployment                      |

|   | - Organizational structure          |

|   | - Wages and reward structure        |

|   | - Globally dispersed collaboration  |

| • | Pervasive information technology:   |

|   | - Computation                       |

|   | - Communication                     |

|   |                                     |

Table 4: Emerging manufacturing needs

Due to the pervasive and timely availability of information and knowledge, global competition is more aggressive: new products are developed and brought to market quickly to globally distributed customers. Consequently, there is an erosion of what had been known as customer loyalty. Just as industrial jobs are no longer secure for life, brand-name loyalty on the part of a customer is not likely to survive; customers shop around for the most convenient or persuasive supplier.

Customers' expectations are increasing: they expect on-time delivery of high-quality customized products at prices reflective of high-volume manufacturing costs, and great service; otherwise, they will find other suppliers without hesitation. Quality is a given, not a differentiator; if one producer's product does not exhibit high quality, the customer will quickly find someone else.

Environmental concerns are also becoming more important in response to government regulations and societal concerns. Industry is recognizing that environmentally sound manufacturing is more rewarding than environmentally insensitive manufacturing.

Firms expecting to compete in the next millennium will have to play this ball game, on this playing field, with these new rules, encumbered as well by the needs and requirements listed in Table 3. These are the challenges the semiconductor industry faces as markets change, customer requirements change, and political and socio-economic forces affect how business is carried out.

# **Information Technology Responses**

Two items listed in Table 4 were not discussed above: new technologies, materials, and processes; and greater access

to global information and knowledge. The first refers to the fact that we can now create materials and structures on an atomic scale, with properties hitherto not only unavailable, but undreamed of. New products such as micro-motors, micro-refrigerators, micro-turbines, device analysis tools, and packaging will probably generate significant business in the not-too-distant future. However, since these do not concern semiconductor chip costs at the moment, they are not discussed further here. For details on these opportunities, see the NGM report [2].

The explosion of information technology (IT) is however another story. Indeed, information technology—the pervasive generation, storage, distribution and use of information and knowledge—seems to be the technology that may help resolve ALL the dilemmas of cost and competitiveness. IT can help with the declining rate of cost per chip element and increased cost per factory, as well as those emerging manufacturing needs identified in Table 4. In the remainder of this paper, we discuss how specific elements of information technology can be used to significantly impact all these issues.

Two applications of information technology that appear to have the greatest leverage are operational modeling and simulation, and management of knowledge assets and intellectual capital. In addition, these programs also affect the third way of decreasing these costs, the ramp speed to high-volume manufacturing. (For example, Intel's Copy <u>EXACTLY!</u> policy is one way of managing our corporate knowledge and wisdom to increase ramp speed.) However, ramp rate improvement is not discussed further in this paper. Please refer to "The Evolution of Intel's Copy <u>EXACTLY!</u> Technology Transfer Method" in this issue of the *Intel Technology Journal* for a fuller description of this important program.

Operational modeling and simulation (OM&S) and management of knowledge assets and intellectual capital applications have different purposes. OM&S is used to lower the cost and speed up the process of trying alternative solutions to different operational scenarios. It can provide quicker and more accurate answers to questions such as how much equipment or how many people are needed to perform a given number of activities; how can a factory be laid out for improved efficiency; how can equipment be best located to provide high throughput and still be easily accessible for maintenance; or how equipment operation can be best scheduled to improve overall capital utilization. In order to answer these questions, different alternatives can be tried out on the computer, saving months or years of physical experimentation time, and millions or even tens of millions of dollars of experimental materials and equipment time.

In Knowledge Management (KM), ever more transient users can access vast sources of data, information and knowledge

in real time to enable them to make more informed and higher quality decisions. This information is wide in scope and sufficiently deep to enable one versed in the use of such technology to make and execute decisions with unparalleled ability. Considering that the value of a corporation is more and more dependent on intellectual assets (patents, knowhow, trade secrets, processing and product knowledge, bestknown methods, etc.) than on capital assets (equipment, buildings, rights of way, etc.) it is not surprising that significant attention is now being paid to knowledge management.

Both OM&S and KM can be beneficially applied to the many domains of manufacturing including scheduling, using the theory of constraints tied to operational models; enterprise integration tied to enterprise models; electronic commerce; capacity planning and factory layout improvements, tied to comprehensive factory models; improved equipment utilization and performance, tied to equipment and material handling models. All these domains can benefit significantly from OM&S and KM. Using these methods, we can now start to overcome some of the limitations we face as yields approach 100%, as factory automation approaches an economical limit, and as increased wafer diameter and increased package complexity continue to add to the cost of running a large factory.

Some examples of how these two information and knowledge capabilities can be used to help improve operational efficiency are illustrated below.

#### **Operational Modeling**

OM&S is used widely in process development, wafer fabrication, assembly test, manufacturing support, and other parts of the manufacturing enterprise. Savings accrued through the use of OM&S can be substantial, in the hundreds of millions of dollars.

Generally speaking, OM&S capabilities are directly linked to improvement of major factory performance metrics: cost reduction, delivery improvement, quality improvement or product performance improvement. Factory improvement issues are often stated thus: "If I change this and that, how does the result affect my bottom line performance?" or "What if I did this instead of that (if I added or removed people from the line; if I laid out the equipment differently; if I used this strategy vs. that one to schedule downtime, and so on), how would factory performance be changed?" Consequently, OM&S programs are often called "what-if" scenarios. They are used to save time and money. Running a physical experiment, i.e., re-laying out a product line, can take months or years compared to running a simulation, which can take minutes or hours. Or, running a physical experiment can cost too much. Running a single experiment in an operating fab could cost hundreds of thousands of dollars.

#### Application of OM&S Technology

The following are examples of how OM&S technology can be applied:

- Comparison of Continuous Flow Manufacturing (CFM) to current Functional Flow Manufacturing practices in the production of Single Edge Connector Cartridge (SECc) modules may be applicable to other manufacturing facilities.

- Dedication of particular stepper lenses to particular lots in fabs to improve overall factory performance.

- Increase in WIP turns using full factory simulation to enhance use of information to improve performance.

- Evaluation of the effects of lot size on factory performance to determine optimum lot size.

- Evaluation of the effects of modifying operational policies on scheduling use of factory equipment to increase utilization without adding more equipment.

More detailed discussions of applications of operational modeling may be found in Court Hilton's paper entitled "Manufacturing Operations System Design and Analysis" and Karl Kempf's paper "Improving Throughput Across the Factory Life-Cycle" also appearing in this Q4'98 issue of the *Intel Technology Journal*.

Note that all of the above examples are specific applications; they do something for someone who has a specific issue to resolve. As such, they are highly beneficial. But the real payoff comes when all these applications are linked through some integrated, hierarchical model. The benefits of such a model can be imagined by comparing it to Microsoft Windows\*. In Microsoft Windows, each application (Word\*, Excel\*, PowerPoint\*, etc.) is individually very useful, but the ability to share textual and image objects between applications greatly enhances the whole. The total Windows environment is more than just the sum of its parts.

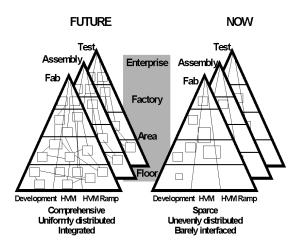

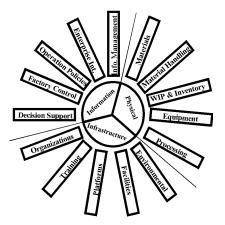

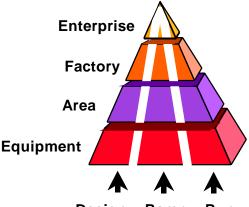

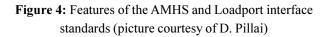

So part of the evolving OM&S effort is aimed at defining a modeling hierarchy, and establishing the links and infrastructure between modeling elements, to make the entire modeling environment much more than the sum of the individual components. This is schematically illustrated in Figure 4, where the NOW environment shows individual models, distributed through the manufacturing enterprise, and the FUTURE scenario shows an evenly distributed, linked hierarchy of models.

Figure 4: Modeling hierarchy

The scope of operational modeling is very broad, as illustrated in Figure 5. For convenience, the operational environment has been divided into three roughly equal domains: those dealing *directly* with product (the PHYSICAL DO-MAIN), those dealing with the data and information associated both with the product and with the factory itself (the INFORMATION DOMAIN), and those dealing with background and support issues (the INFRASTRUCTURE DO-MAIN). Each of these domains is itself sub-categorized, as shown in Figure 5.

Figure 5: Model scope

Each sub-category is made up of sub-sub-categories, and so on, until one reaches the lowest level of the model hierarchy. Hence, each topic can have applications, roadmaps, goals, interfaces, etc.; the question is, how many of these topics

<sup>\*</sup> Other brands and names are the property of their respective owners.

have common elements and should actually be integrated with one another. This integration is both lateral, meaning across equivalent levels of hierarchy, as well as being up and down the chain of model hierarchy. It raises interesting philosophical questions about model integration, as well as deep practical questions of how one may make modeling capabilities more cost-effective and efficient.

# **Knowledge Management**

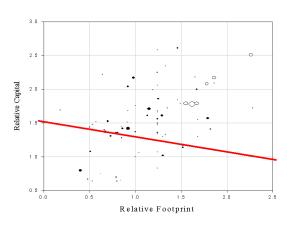

Whereas OM&S technology provides a fairly direct link between the capability of a technology and factory performance, knowledge management (KM) technology is one step removed from such a direct link. Indeed, KM is a logical counterpart of physical asset management, the leveraging of our physical capital (land, factories, computers, equipment, etc.) to improve profitability. KM leverages "knowledge capital" (patents, trademarks, know-how, competencies, skills, tacit or unwritten knowledge, relationships, etc.). Since, at the present time, the value of these intellectual assets is not really understood, the first goal of KM is to define a set of metrics that allows one to know even if there is any leverage to intellectual capital.

One rough estimate may be made by comparing the value of a company in the eyes of its stockholders to the paper value of the company's physical assets. In the case of Intel, the stock value (shares outstanding times price) is about \$120 Billion, while the physical assets have a value of about \$25 Billion. The difference, about \$95 Billion, or four times the physical asset value, may be ascribed to non-physical assets!

KM capabilities may be defined using the following model. KM is divided into four large domains: the creation of knowledge, the capture and structure of knowledge, the dissemination of knowledge, and the application of knowledge. Some attributes of each of these four categories are shown below in Table 5.

The two areas that require most attention are items 2 and 3 in Table 5: the collection, structuring, and indexing of knowledge, and the secure, rapid dissemination of knowledge to potential users. Of primary interest are metrics: understanding how to value the intellectual assets of the enterprise, and indexing: the categorization of knowledge for rapid and ubiquitous application. Also of great significance is the knowledge tool environment. Much like the information tools of prior generations, knowledge tools are rapidly emerging and evolving. We expect that a knowledge tool environment similar in concept to the Windows\* information environment will emerge, thereby allowing us to exchange knowledge objects in much the same way as we already exchange information objects.

|                                | _ |

|--------------------------------|---|

| 1. Knowledge Creation          |   |

| - Research                     |   |

| - Brainstorming                |   |

| - Strategizing                 |   |

| - Synthesizing                 |   |

| 2. Knowledge Structure         |   |

| - Data and knowledge databases |   |

| - Indexing                     |   |

| - Training development         |   |

| - Report generation            |   |

| - Knowledge management tools   |   |

| 3. Knowledge Dissemination     |   |

| - Inter- and Intranet          |   |

| - Education and training       |   |

| - Electronic mail              |   |

| - Reading                      |   |

| - Browsers and interfaces      |   |

| - Security precautions         |   |

| 4. Knowledge Application       |   |

| - Problem solving              |   |

| - Strategizing                 |   |

| - Decision making              |   |

| - Managing and metrics         |   |

|                                |   |

Table 5: Knowledge management domain

Some potential areas where knowledge management can be applied are as follows:

- Understanding and matching of core competencies of individuals with attributes of job needs.

- Providing a "Knowledge Atlas," a visual environment in which employees can guide themselves to find knowledge items, for example, "how do I do this?"; "who do I see to do that?"; or "who is the expert on this?".

- Developing tools that leverage an employee's job skills, allowing people to take on more responsible jobs using knowledge assistants for help.

- Better problem solving by providing access to vast and comprehensive knowledge bases of past occurrences, tied to the nature of a problem rather than to simple keyword searches.

Knowledge management tools will help make us a more efficient company by providing access to knowledge to people who need it, wherever they are and whatever the problem set. We should then be able to make faster and wiser decisions, resulting in significant improvements in factory and even enterprise performance.

#### **Organizational Issues**

Pursuit of information and knowledge technology, as given in the examples above, is not free. In particular, in addition to the obvious need for technical skills, there is a need to understand and respond to the managerial and organizational skills required for success.

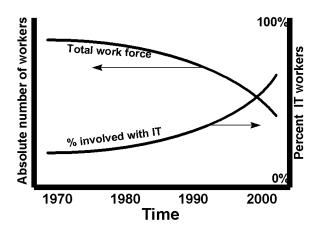

At one time, the resources required to operate a factory consisted almost universally of people who had their hands on the product: moving it, processing it, assembling it, storing it. Currently, the trend is towards having a greater percentage of the workforce spending time on the processing of data and information. They gather data, analyze data, and convert these data to information. This information is then stored, transmitted, and disseminated, so that decisions can be made and our knowledge increased. Meanwhile, the total workforce is decreasing through physical and logical productivity improvement.

The result of these two trends is schematically illustrated in Figure 5 below. The total workforce is decreasing, while the percentage of IT and software personnel is increasing.

Figure 6: IT headcount projections

There are two personnel issues to confront as a result of these trends: the first is the evolution of the factory workforce from process-centric to one that is more information-centric. The processing domain is equipment dominated, where our equipment suppliers own the core competencies. As more and more information processing is incorporated into the factory, more technologists will be necessary in the IT processing field. However, this problem is fairly manageable; Intel is an expert at managing technology.

The real issues are those of organization and management. Managing process is straightforward: align the management organizations functionally, for example, with cross-cutting metrics such as yield, cost, delivery, etc. Managing the information organization is different, however. The cross-cutting disciplines such as platforms, software, and databases are not conducive to factory management, but the information technology does not map well to the traditional metrics of yield, delivery, etc. Furthermore, the skills of management need to be different. Management needs to be more proficient in IT skills; their current skill set is technologically oriented towards processing technology.

These management and organizational issues need to be dealt with concurrent with the growth of IT technology.

## Conclusions

It seems clear that our industry is departing from at least some of Gordon Moore's earlier quantitative predictions. One of these is illustrated in Figure 6. Gordon's 1974 tongue-incheek but genuine extrapolation of wafer sizes suggested that by the year 2000, we would have 57-inch diameter wafers! Clearly, this is off by about an order of magnitude. Yet simple extrapolations of Gordon's trends does lead to qualitatively correct predictions.

Figure 7: "Extrapolated" Year 1999 wafer size[1]

Regardless, two trends seem inescapable: everything in the production of semiconductor devices is moving toward more expensive factories, and there is swiftly expanding use of information and knowledge to reduce costs, improve delivery, and improve quality. These two trends need to be linked to try to alleviate the effects of the former by using the latter. At the same time, one must also recognize the emergence of other forces: the need for cleaner, safer, and less energyconsuming manufacturing enterprises, the evolution and indeed revolution of materials and materials' processing, and the change from local politics and culture to global politics and culture. All these trends will result in a significantly greater emphasis being put on manufacturing as a competitive weapon in the  $21^{\text{st}}$  century.

#### Acknowledgments

I would like to thank Gordon Moore, Karl Kempf, Court Hilton, Sri Sridharan, Scot Ruska, Bruce Sohn and John Birchak for valuable discussions that helped formulate the concepts discussed in this paper.

# References

- 1. Gordon Moore, *Electronic Materials Symposium* Santa Clara, CA, March 1998.

- 2. "Next Generation Manufacturing: A Framework for Action," *Agility Forum*, Bethlehem, PA, 1997.

# **Author's Biography**

Gene Meieran received his B.S. degree from Purdue University in 1959 and his Sc.D degree in materials science from MIT in 1963. He joined Fairchild R&D in 1963, where he specialized in the analysis and characterization of semiconductor device materials. He joined Intel in 1973 as manager of Package Development, responsible for developing new lines of packages for the emerging memory and microprocessor products. In 1977, he joined the Quality and Reliability staff, with responsibility for all Intel materials, the Materials Analysis Laboratory, and for manufacturing reliability functions. He has worked in Statistical Process Control (SPC) and advanced manufacturing strategy development in Intel's Technology Manufacturing Engineering group for the past 12 years.

Dr. Meieran taught technical courses in leading US universities and has given seminars and invited talks to many international universities. He has about 50 technical awards and has received three international awards based on technical talks.

He served on the Scientific/Education Advisory Board for Lawrence Berkeley Labs and on advisory boards for several university departments. He has been Director for Research for the MIT Leaders For Manufacturing Program since 1993 and has served on numerous government and industry panels dealing with manufacturing technology and policy issues.

In 1985, Gene was appointed an Intel Fellow, Intel's most senior technical position. In 1987, Purdue University elected him a Distinguished Engineering Alumni, and in 1998, he was elected to the National Academy of Engineering.

His e-mail is gene.s.meieran@intel.com.

# The Evolution of Intel's Copy <u>EXACTLY!</u> Technology Transfer Method

Chris J. McDonald, Intel SEMATECH

Index words: copy exactly, technology transfer

#### Abstract

Semiconductor manufacturing is characterized by very complex process flows made up of individual process steps, many of which are built to very close tolerances. Furthermore, there are complex interactions in these process flows, whereby each process step can affect many other steps, and each final device parameter might be determined by the results from many inputs. This level of complexity is increasing with each new technology generation. Items that were once considered second-order effects, such as barometric pressure and ultra pure water temperature, are now important variables affecting process results.

The costs of technology development and capital equipment for production are very high and are increasing with each generation, thus making technology transfer very important. Once a new process flow and product portfolio have been developed, it is essential that the technology transfer to mass production take place as quickly as possible, without disruptive quality issues, and with the highest possible yield. No time is available to debug new problems that occur during the transfer.

The traditional technology transfer approach often allows many equipment and process changes to be made. These changes are intended as improvements in the process, or they are for the convenience of the production factory, which may be already producing other products. As semiconductor technology becomes more complex, these changes have resulted in unforeseen problems that cause production startup delays and inferior results.

The Copy <u>EXACTLY!</u> philosophy and systems were developed [6] in order to minimize the time required for a technology to be transferred and to ensure product quality and yields are not compromised. The methodology has been improved and refined, and has become an important element in Intel's overall manufacturing strategy [1]. This paper describes the Copy <u>EXACTLY!</u> methodology and the increase in technology transfer performance that it has brought about. Some side benefits of this methodology are also discussed.

#### Introduction

Table 1 shows the typical technology transfer approaches used over the last ten years or so. At the 1.5-micron generation, process flows were much simpler than they are today. A small band of technical experts would typically be employed to orchestrate a successful technology transfer. Generally there would be few ground rules. Since there is always a lengthy "certification" or "qualification" exercise to prove product quality and reliability, the transfer from R&D to manufacturing, or to a new factory, offered the opportunity to introduce improvements to the equipment and process. The latest model equipment or even a new vendor might be chosen. Process recipes could be changed to improve them. In the case of an existing factory picking up a new process flow, changes were made to match existing processes and methods to improve efficiency and productivity. Sometimes, a wafer size conversion would even be made at the same time, involving many changes. Overall, however, the number of variables was relatively small, which made it simple to trouble shoot any results that did not come out as expected.

| Technology<br>Generation | Transfer<br>Strategy            | Comments                                                |

|--------------------------|---------------------------------|---------------------------------------------------------|

| 1.5 micron               | "Make It<br>Work"               | Small band of engineers. Few ground rules needed.       |

| 1.0 and 0.8<br>micron    | "Process<br>Output<br>Matching" | Copy selectively. Match to existing factory conditions. |

| 0.5 micron               | "Copy<br><u>EXACTLY!</u> "      | Copy everything that might affect the process.          |

| 0.35 and<br>0.25 micron  | "Systems<br>Synergy"            | Copy all manufacturing systems.                         |

Table 1: Technology transfer strategies

For the one-micron generation, technology transfer started to get more complicated. A structured methodology was needed, whereby each process step would be measured to ensure it matched a target value or complied with a set of specification limits [2] [3]. Most projects, however, only focused on matching device and final product parameters. As long as these were correct, changes would still be introduced as a part of the transfer process.

For the sub-micron generation, the above approach has had its share of problems. There are many more process steps today, and many of them are made up of several components. For example, a typical metal or dielectric layer is now a sandwich of multiple layers of different materials and compositions. Very fine device structures are subject to different effects, such as inter-layer stresses and adhesion. Phenomena that were once considered second-order effects now have a significant effect on the process result. Among these are barometric pressure and ultra pure rinse water temperature. In general, the process is manufactured with much closer tolerances, increasing the importance of process control. Even the length of an electrode cooling hose has had a catastrophic effect, but this is a very subtle variable to find. With larger die sizes, defect control becomes even more critical, and the way the process is actually run becomes a more important factor. An example is preventive maintenance intervals and workmanship. Many of the factors just mentioned are difficult to measure and quantify, which makes them dangerous "unknowns" during a technology transfer project. When many changes are made, the risk of something going wrong is greatly increased. Moreover, if something does not come out as expected, the number of variables that have to be studied when trouble shooting the problem is greatly increased. The amount of experimentation and therefore, time, required to find the problem increases as a power function of the number of variables involved. If the problem is a showstopper, for example affecting the product reliability, the end result is a costly delay. Even if this is not the case, yields may be depressed for an extended period.

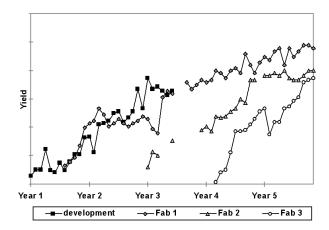

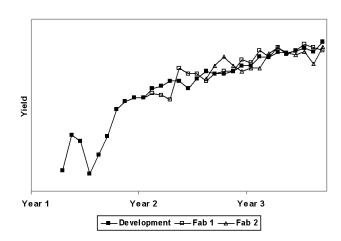

Figure 1 shows one example of using the traditional approach for the 1.0-micron technology generation. The die per wafer yield is one of the most important variables in wafer fabrication and is used in this example. (The graph is normalized for die size). Other factors affecting product performance or manufacturing efficiency showed similar trends. The first production factory in this example, which was a brand new facility, obtained results that reasonably matched the parent R&D line. You can see the yields improve further as improvements were made and the organizations moved down their learning curves. Note, however, the divergence at the end of Year 2. The technology transfer results were good [2]; however, yields diverged as the R&D line focussed on yield improvement, and the manufacturing line concentrated on increasing volume.

# Figure 1: Traditional technology transfer method for the 1.0-micron generation

Eventually the yields did converge. The second and third factories, which were already manufacturing different process flows, made many changes to the process and equipment and used their existing manufacturing methods. It took several months of task force actions to catch up, by which time the first factory was moving further ahead. In effect, the same learning curve was repeated independently by every factory. For the 0.8-micron generation, a new factory start up and a new product introduction were delayed by three months while a device reliability problem was solved, and it took approximately one year to obtain equivalent yields [4].

#### Method

For sub-micron technology, it was realized that a fundamentally new approach would be needed in order to accomplish an "order of magnitude improvement" in the effectiveness of technology transfer. The Copy <u>EXACTLY</u>! philosophy and systems were developed [5] [6] for the 0.5-micron generation, and they have become a key part of Intel's manufacturing strategy [1]. The capital letters, underline, and exclamation point emphasize the paradigm shift that is required to transfer technology using this method.

#### Copy EXACTLY! Philosophy

Stated in its simplest form, "everything which might affect the process, or how it is run" is to be copied down to the finest detail, unless it is either *physically\_impossible* to do so, or there is an *overwhelming\_competitive benefit* to introducing a change. This philosophy differs greatly from the traditional method. In practice, there are always some issues that crop up and prevent an exact copy being made, so it was important to provide for making some changes in a controlled fashion without opening the field too much. For example, in Europe the supply voltage and frequency can be different than those in the U.S., so these had to be accommodated. Moreover, engineers are typically trained and rewarded for making improvements, which in the semiconductor industry implies orchestrating change. Even the educational system stresses independent work, and copying is seen as cheating. Making a philosophical statement is obviously much easier than implementing it within a large team of R&D and manufacturing engineers. Therefore, a comprehensive set of systems was put in place to ensure it would be implemented, and this set of systems is discussed in the next section.

#### Systems

The systems that were implemented are as follows:

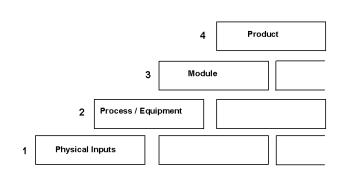

*Four level matching*: Traditionally, it has been considered acceptable if the final product parameters are matched between the R&D line and manufacturing. However, the Copy <u>EXACTLY!</u> approach requires four levels of matching. These are illustrated in Figure 2.

Figure 2: Four-level matching

• Firstly, the physical inputs have to be matched. These are the energies and materials supplied to the process chambers: for example, gas flows, temperatures, pressures, RF power, and so forth. These might be supplied to the equipment by external sources or be generated within the equipment itself. Everything about the equipment and its installation must be an exact copy down to the diameters of piping and the number of bends, board revisions, software, etc. The settings for these parameters and anything that might affect them are copied. Standards are generated to allow measurement and comparison, and the values are measured and matched.

- Secondly, data is collected at the process step output level on parameters such as film thickness, resistance, composition, etc., and they are compared to results at the R&D site.

- Thirdly, a comparison is made at the module level, using test structures such as oxide capacitors and metal serpentine patterns.

- Fourthly, the actual product characteristics are measured and matched.

Formal statistical tests are used at each level. If the match passes these tests, then we proceed to the next level and so on. If the match does not pass the tests, the root cause must be found and eliminated. If it can't be found, trouble shooting occurs to find out which of the previous level inputs is responsible because, despite best efforts, something may have been overlooked. It is vitally important to avoid the temptation to make a compensating adjustment. Due to the complexities involved, an adjustment may result in an interacting parameter, possibly something not measured, being mismatched.

A change control system: Most factories have some kind of approval process for making changes to a production process, either in the form of a sign-off list or a formal changecontrol committee. Generally there is some kind of record of the data showing the benefits of the change. The R&D line continues to make improvements to finish off the technology development and, in many cases, they may also run some level of samples and production output. With Copy EX-ACTLY! change control is started before technology transfer, and all changes are implemented directly into both the R&D and production lines within one week, or according to an approved schedule. The pace of R&D work is not allowed to slow, so careful planning is required to ensure the new line is ready to accept the changes in real time. Any engineer from the manufacturing line who has a good idea for improvement is encouraged to pursue it. The only difference from the traditional approach is that the idea must be implemented simultaneously at all sites. The change control board is responsible for the smooth operation of the system, which includes ensuring that the additional requirements do not slow down the rate of improvement.

*Equipment difference form*: In the Copy <u>EXACTLY</u>! system, each first piece of equipment in the new factory or on the new process flow in the existing factory is treated as a change, subject to change control. Audits are conducted and an Equipment Difference Form is prepared from each. This form documents the actual difference, what risks it might pose, and the corrective action plan. This is formally reviewed by management. Supplier education: Equipment and materials' suppliers are constantly improving their products in response to demands from the semiconductor industry for improvement. These changes are still desirable; however, with Copy <u>EXACTLY!</u> they are first introduced into the R&D line and from there transferred to production. The suppliers are a vital part of the technology transfer and need to be thoroughly educated on the new concept and systems.

*Audits*: An audit is a formal procedure whereby engineers from R&D and from production audit both lines. These audits are required and scheduled as part of the technology transfer and are ongoing for a period thereafter. A report is written for each audit, detailing plans to correct all differences found.

*Joint specifications*: Since the equipment, process recipes, and procedures are all the same, there is no reason why the documents provided for training and manufacturing operations cannot be the same. These are not copies; they are the same documents, either paper or electronic.

*Questions and answers (Q&A)*: Different engineers tend to interpret the Copy <u>EXACTLY!</u> message in different ways. For example, some engineers might say, "Surely if I make sure the pressure is the same, then it doesn't matter if I use a different pump with less bends in the vacuum line." The answer to this particular question is "*Yes*, it does make a difference, and *no*, it's not ok to make a change." The rationale is that you might be able to get the same result under ideal conditions, but the only way to guarantee you will always get the same results, both steady state and transients, under all possible conditions of environment, age, etc., is to copy the configuration exactly. To deal with this type of question, a detailed Q&A list was prepared and communicated to all engineers involved on the project.

#### Systems Synergy

The scope of copy <u>EXACTLY!</u> for the 0.5-micron technology was for the most part limited to anything that might have an impact on the process, or how it is run. The motivation was to guarantee equivalent yields, starting with the first wafer, and to ensure there were no reliability problems to delay production. One recommendation [7] from this program was that the concept could be extended into other areas as a way to further accelerate new factory start-ups and the manufacturing ramp of new-generation technologies.

The 0.35- and 0.25-micron generation technology transfers [8] took the Copy <u>EXACTLY!</u> method a step further into what has been described as total "Systems Synergy," where almost every aspect of the fabs are identical at multiple geographic sites. The 0.8- and 0.5-micron generations both had a "virtual factory" organization structure and a series of com-

mittees to set the strategic direction and manage the technology. For the 0.35- and 0.25-micron technology, this has been expanded: a Steering Committee at the plant manager level sets the overall direction, Joint Engineering Managers' Teams manage the technology, and individual Joint Engineering Teams work the details at the process and equipment level. Similar structures exist in other areas, such as Manufacturing Operations and Automation, and a "Joint Synergy Team" manages the overall system.

## Results

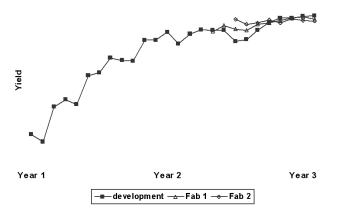

Figure 3 shows some typical results obtained from Copy <u>EXACTLY!</u> Two new factories were successfully brought on line with the same yield results as the parent R&D line. Furthermore, all three lines were able to improve their yields together by implementing improvements simultaneously. Other parameters such as product quality and reliability and manufacturing efficiency also matched very closely.

Figure 3: Copy <u>EXACTLY</u>! technology transfer method for the 0.5-micron generation

As always with projects of this magnitude and complexity, there were some issues encountered along the way. For example, a very subtle problem affecting the integrity of the sub-micron metal lines was found. However, since the process had been copied so precisely, trouble shooting became an exercise in revisiting the exceptions that had been made and auditing to look for unforeseen errors in copying. In this example, two variables were identified as suspects, and a simple experiment on test wafers identified the cause within a week. A simple typographical error had been made in entering a process recipe. The problem was very subtle and would have taken many weeks to identify if a traditional transfer approach had been used. In addition, areas for improvement in the technology were known and found in both sites. Since no new problems were introduced as a result of the technology transfer, the number of engineers and other resources available for basic improvement work was greatly increased. Moreover, the overall technology transfers to two new 0.5micron factories were accomplished in record time with very few problems along the way.

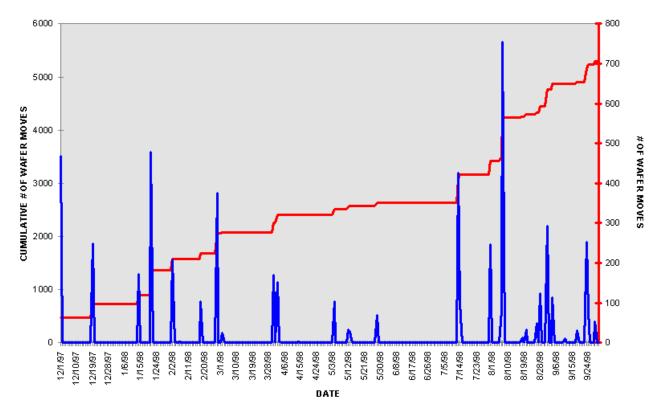

Figure 4 shows the results obtained on the 0.25-micron technology generation, using copy <u>EXACTLY!</u> and Systems Synergy.

It is now routine for new Intel factories or new technologies that were transferred to obtain equivalent yield starting with the first check-out wafer. Production quantities of products are started immediately since there is such confidence the product will be good.

#### Discussion

The difficulties in implementing this new philosophy and system are not to be underestimated. Any major project, such as a new factory or new process flow in an existing factory, is started with the ambition to get the best ever results. Engineers are trained and rewarded for doing improvement projects, and product re-qualification affords them such an opportunity. The natural tendency is thus to use the new start-up as an opportunity to implement improvements. To change the mind set of a large body of technical experts requires a very simple message, consistently delivered, and backed up by a set of systems that make it difficult to behave differently from the desired state. With Copy EXACTLY!, the message to the production engineers was to achieve the best ever replication in the fastest possible time, and it will be considered the "best ever." Once the new products are up and running, with good stability and in high volume, the production line engineers earn the right to take a leadership role in making improvements. In the meantime, ideas are still welcome, but they are implemented through the R&D organization and at the same time at both sites. The R&D engineers also need to make some sacrifices. To make changes they now need the support of the production line engineers.

The results obtained clearly show the merit of the Copy <u>EXACTLY!</u> philosophy and systems. The process flow was transferred to two new factories in record time with equivalent yield and other indicators, and with no product quality issues. The new lines were able to precisely intercept the technology learning curve.

A number of other benefits were also realized and are as follows:

*Customer acceptance*: Many major customers for integrated circuits are well aware of the risks in changing manufacturing plants and will typically demand the opportunity to re-qualify a second source. If the supplier has a high credibility rating, this may simply require a study of all the data from the new line. However, in many cases the customer may want sample devices to submit to his/her own testing, or to a third party laboratory. He/she may also require a site visit and an opportunity to audit the new line. In all cases there will be additional costs and delays in time to market. However, once the customers understood the Copy <u>EXACTLY</u>! method, many of these concerns, costs, and delays were eliminated.

*On-going mutual synergy and shared learning*: In the example outlined here, the R&D line continued to manufacture the new products along with the two manufacturing lines. By keeping the process in lock step at all three sites it was possible to share the improvement projects among them. Improvements were characterized in one site and transferred to the others with minimal effort. In effect, the number of engineers per process step or per area for improvement is increased, as is the number of improvement ideas generated.

*Manufacturing flexibility*: With three sites running the exact same process, products were easily transferred back and forth with no re-qualification, other than checking the mask set. Using free capacity at another site has also solved manufacturing bottlenecks.

#### Conclusion

The Copy <u>EXACTLY</u>! method has proven itself as a technique for semiconductor technology transfer. A new process flow and products can be introduced to production in minimum time with equivalent yields and without the introduction of product-quality issues. Both manufacturer and customers can reduce their time to market. This approach could equally be employed in other industries where the technology is complex and has many interacting variables affecting the end result. The concept has been successfully expanded to cover all systems used in manufacturing.

### Caution

Copy <u>EXACTLY</u>! is a powerful method for technology transfer, but should not be applied during technology development. By definition, technology development means taking new processes and improving and integrating them to create a new generation process flow with greater capabilities. While it may be decided that some existing process modules and equipment can be reused as they are, in general, technology development requires great creativity and innovation. Technology development would be dampened by the rigid discipline required during technology transfer and manufacturing.

High-volume manufacturing also demands a high degree of change. Yields must be continuously increased, efficiencies improved, and costs reduced. It is vitally important that the systems used to manage change strike a good balance between the discipline required to keep the factory under control and the creativity and innovation required for continuous improvement. Manufacturing improvement systems need to be very fast-moving and flexible. Multiple factories running the same process and products should remain matched, but not necessarily identical at all times. New approaches should be tested in one site and proliferated to others when proven.

Finally, the Copy <u>EXACTLY!</u> method is designed to match all factors that impact the process or how it is run. Other systems might benefit from matching, but time and money should not be wasted on matching factors that have no impact on the overall process.

# Acknowledgments

The author would like to recognize Tom Hartman for his leadership through two new factory start-ups. The author also acknowledges Bob Jecmen and Bruce Leising for their sponsorship in the implementation of these new approaches, and for their support in the publication of this paper.

# References

[1] G.H. Parker, "Intel's Manufacturing Strategy," presented at the 5th International Symposium on Semiconductor Manufacturing.

[2] C.J. McDonald, "Fab 9.1 Start-Up Methodology." *Intel Internal Document*, June 1988.

[3] M. Bohr and S.Ruska, "P650 Transfer Methodology Proposal," *Intel Internal Document*, December 1989.

[4] S. Ruska, "Post-Mortem of Fab 9.2 Yield/Undercut Issues," *Intel Internal Document*, December 1991.

[5] C.J. McDonald, "Fab 10 Start-Up Methodology – Copy EXACTLY!," Intel Internal Document, February 1992.

[6] C.J. McDonald, "Copy <u>EXACTLY!</u> A Paradigm Shift in Technology Transfer Method." Presented at the *IEEE Advanced Semiconductor Manufacturing Conference*, 1997.

[7] J. Multani, C.J. McDonald et al., "P852 Virtual Factory Vision Through Copy <u>EXACTLY!</u>." Presented at the *Intel iMEC Conference*, 1994.

[8] G. Gimpelson et al., "Rapid Technology Transfer: BKM's from the P856 Process Transfer." Presented at the *Intel iMEC Conference*, 1998.

# **Author's Biography**

Chris J. McDonald holds a B.Sc. in electronics from the University of Southampton, UK and an M.Sc. in electrical engineering from the National Technological University, USA. He is a sixteen-year employee of Intel, currently assigned to SEMATECH where he is director of the Advanced Technology Development Facility. His other positions included that of manufacturing manager and yield/Q&R manager for the start-up and ramp of Intel's high-volume manufacturing facility in Ireland and a process/equipment engineering manager in Albuquerque. He has twenty-four years experience in semiconductor process development and manufacturing, and he has worked in all areas of wafer fab engineering with a wide range of memory, microprocessor, and other products. His echris.mcdonald@sematech.org mail is or chris.mcdonald@intel.com.

# Manufacturing Operations System Design and Analysis

C. Hilton

Manufacturing Strategic Support Technology and Manufacturing Engineering, Intel Corp.

Index words: factory, manufacturing, discrete-event, simulation, modeling

#### Abstract

This paper describes manufacturing operations design and analysis at Intel. The complexities and forces of both the market and the manufacturing process combine to make the development of improved semiconductor fabrication manufacturing strategies (like lot dispatching, micro and macro scheduling policies, labor utilization, layout, etc.) particularly important. We present modeling as an effective way to further this improvement. We describe various categories of models and why they are useful. We present an overview of eight examples of how we are using modeling to improve manufacturing performance and cost. These summaries illustrate how millions of dollars have been saved in direct cost and/or cost avoidance. We conclude with a brief discussion of next steps and cautions for those establishing a manufacturing operations' group.

# Introduction

In *A Tale of Two Cities*, Charles Dickens begins, "It was the best of times, it was the worst of times..." [1]. Never in history has more reliable semiconductor power been available to the consumer at such a low price. And never in history have the pressures on the manufacturers of these devices been more severe. In essence, it is the best and worst of times. Product complexity is rising, market and product segmentation is increasingly fracturing the market, lead times are shrinking, available margins are shrinking, the cost to bring a semiconductor fab on line is doubling every three to six years, and the historical avenues of cost improvement—device yields, line yields, and even device shrinking—are all approaching limits.

Intel's product manufacturing occurs in several phases: fabrication of the silicon-based device, testing, assembly and packing of the device, testing again, and sometimes assembly of the computer system or sub-system together with its testing yet again. Further complexity is introduced into each of these manufacturing processes in an effort to meet the demands for special market-driven product features.

The wafer fabs, which produce the silicon-based devices, use complex processes involving two billion dollars of equipment and 300-500 operational steps all housed in an ultra-clean environment. Fabs typically require on the order of a thousand direct staff to operate. The material does not move through the factory in a linear fashion from front to back, but loops back on itself, revisiting some areas sometimes more than twenty times. This creates all sorts of "feedback loops" (known as reentrancy) in the dynamic response of the factory to perturbations on the factory floor and in the marketplace. These perturbations can be dampened or amplified depending on factory design, operational policies, and the current state of the material being manufactured. The majority of wafer fab cost arises from capital equipment costs. Wafer fabs feed other assembly and test operations where the devices are packaged and tested under a variety of additional constraints. Assembly and test manufacturing flows are generally linear and have several dozen processing steps. To build and equip a factory costs in the order of hundreds of millions of dollars. These factories require hundreds of direct staff to operate.

Most of the high-revenue products being manufactured today did not exist two years ago. Market forces, often not well understood, can drive product functionality as well as product packaging through radical changes within a short period of time. Each new generation of product, introduced every 12-24 months, requires new and even more costly process equipment. Often this equipment is itself on the cutting edge of technology and does not always have the performance or reliability desired for cost-effective operation. This short product lifecycle makes the reuse of equipment and the flexibility of factory use very important. At the SEMI-Advanced Semiconductor Manufacturing Conference in 1997, Clark Fuhs, Director/Principle Analyst of the Semiconductor Manufacturing Group for Dataquest said, "The next productivity leap in the semiconductor industry will have to come through the implementation of manufacturing science and of industrial engineering practices" [2]. Manufacturing science, or "factory physics" as we like to refer to it, "is a systematic description of the underlying behavior of manufacturing systems" [3]. To understand this underlying behavior of systems of this complexity and cost, we typically do not experiment directly with the manufacturing operation. Rather, validated computerbased models are built to describe the behavior, and these models are used to develop and test factory design and operational practices that will optimize factory performance and flexibility at the lowest cost.

# **Models: Lies Or Oracles?**

From a certain point of view, a model is a lie. From another perspective, it may be an oracle. A model is a lie in the sense that it is a purposeful simplification of a problem with the intent of focusing attention on what are believed to be the critical-few discriminating attributes or salient concepts. A model can be an oracle in the sense that an appropriate model allows us to conveniently manipulate complex systems and find answers to questions we could not approach in any other way. Models may be very detailed or very general (i.e., they are written at different levels of abstraction). Various model evaluation techniques are used within computerbased models, from simple spreadsheets to complex fullfactory discrete-event simulations. Table 1 is a comparison of various types of model abstractions used in a study of a representative assembly plant operation. [4]. Note in Table 1, MTTF and MTTR refer to equipment Mean-Time-To-Fail and Mean-Time-To-Repair.

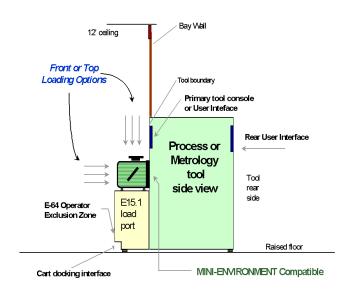

This paper focuses primarily on describing applications of computer-based models that attempt to represent complex and dynamic manufacturing interrelationships. This class of models is known as discrete-event simulations (DES). DES models are used at Intel to evaluate a variety of system performance, design, automation, and operational issues in a cost-effective, non-disruptive, statistical, and realistic fashion. Figure 1 shows the 12 areas in which we focus our efforts.

DES models can often help in decision making whenever one or more of the following conditions exists [5]:

- equipment utilization is greater than ~80%

- synchronization or merging of separate operations occurs

- manufacturing actions interact with outside events

- operations with widely variable completion times interact

- contention for resources or timing constraints exists

Design Ramp Run

| Analytic<br>Method<br>(model<br>abstraction)                                    | Level                    | Assumptions                                               | Accuracy                                  |

|---------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------|-------------------------------------------|

| Static<br>algebraic<br>analysis of<br>linked<br>systems<br>without<br>buffering | System                   | No buffering<br>allowed<br>Simple MTTF<br>& MTTR<br>model | Good<br>model,<br>Averages                |

| Linked static<br>analysis with<br>buffering                                     | System                   | Buffering<br>allowed<br>Simple MTTF<br>& MTTR<br>model    | Better<br>model,<br>Averages              |

| Monte Carlo<br>analysis of<br>static models                                     | System<br>Area           | Distributions<br>of input<br>parameters<br>are available  | Better<br>model,<br>variability           |

| Dynamic<br>discrete-event<br>simulation<br>analysis                             | System<br>Area<br>Equip. | Buffering<br>Failure &<br>repair<br>distributions         | Best<br>model,<br>dynamic,<br>variability |

| State-space<br>analysis                                                         | Equipment                | Accurate<br>observation<br>Fast<br>transitions            | Best<br>validity<br>(i.e.,<br>nature)     |

Table 1: Example comparison of various types of model abstractions used in solving an equipment linking design problem for an assembly operation

### The Design of Experiments

#### **Infinite Possibilities**

A number of designed experiments, using static and discrete-event simulation models, are required to determine the expected factory performance under various conditions. To limit the infinite number of possible experiments, fractional and full-factorial designs can be iteratively used to define efficient sets of factory conditions to simulate.

#### Inputs and outputs

Our simulated factory inputs and outputs are similar to those found in an actual factory. Inputs include equipment count and layout; process time (units per hour); distributions for mean time to fail, repair, and assist; preventive maintenance (PM) time profiles; work in process (WIP) management policies including materials release; setup and batching policies; transportation times; labor availability profiles; and process flow definitions. Likewise, model outputs include equipment utilization, throughput times (TPT), and factory output (often referred to as "outs").

#### How Outputs are Reported

Simulation outputs are normally reported as differences or ratios of one scenario versus a baseline scenario. For example, rather than report a TPT, one would instead report that the simulation has a TPT that is 2.3 times the theoretical TPT, or that scenario B provides 10 percent more capacity than a baseline scenario A. This type of comparative reporting is useful because it allows the experimenter to focus on the key differences under study while normalizing away model simplifications in areas of less interest. For example, in this report we employ a "TPT Ratio," which is the ratio of a scenario of the simulated TPT, to an arbitrary baseline-theoretic TPT. The intent is for the ratio to be interpreted conceptually as a TPT.

#### **Insight Through Sensitivity Studies**

In a sensitivity study, outputs are measured over a range of input variable values. This is an excellent technique for understanding the expected range of the modeled factory performance, for developing intuition about how a specific manufacturing floor will perform, for understanding the impact on the study of questionable input data, and for verifying model performance. We have made extensive use of sensitivity studies in the majority of work reported here.

# **Example Model-Based Manufacturing Studies**

#### **Ergonomic Simulations**

As unit volumes increase in the back-end, and as wafer size and weight increase in the front-end, our factory personnel experience ever increasing physical demands. In an industry unaccustomed to dealing with heavy and/or sustained physical labor, this poses new challenges for factory operation and design. We applied a specialized simulation-modeling environment that combines advanced software and computational techniques with standard ergonomic metrics and detailed full-motion models of humans [8]. The DES models, which define task type and frequency, are seamlessly merged with ergo models, which evaluate the physical impact of programmed actions on the worker. To enable visualization of the stresses, a display environment capable of stereoscopic 3-D showed worker actions in real-time from any perspective (including that of the wafer if you are so inclined!). In this environment, the upper limbs of virtual workers dynamically changed color to express the degree of strain to which they were subject during their activities. Ergonomic evaluations included reachability, field of view, RULA (rapid upper limb assessment), posture analysis, NIOSH lifting guidelines, energy expenditure, and activity timing. These models, together with other factory, cost, and strategic models were used to support our selection of an optimized waferlot size of 25 wafers to be used in our next generation 300mm wafer fabs.

#### **Design for Environment**

Intel is active in assuring safe and high-quality environmental conditions for its workers and the families that live in the communities where it operates. In addition, the environmental permitting process, required by our operations, often requires more lead time than it does to build and start up a manufacturing facility.

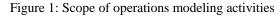

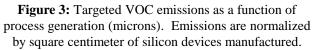

Design for Environment is integrated into our process introduction business plans and has targets that must be met, just like other process goals. Key to a Design for Environment program is the use of a variety of models including an integrated mass and energy balance model. This static model incorporates the best data and models from throughout the corporation and is interfaced with our factory design models. These models allow us to project, years in advance, the effluent and energy demands of our processes. Where needed, process changes can be made to assure environmental quality. This also allows us to effectively target R&D efforts with suppliers, universities, and national labs to assure more benign processes. This approach is working successfully. As shown in Figures 2 and 3 we continue to use less water / (silicon area manufactured), and our air emissions are better from generation to generation.

Figure 2: NM site water consumption per amount of silicon manufactured

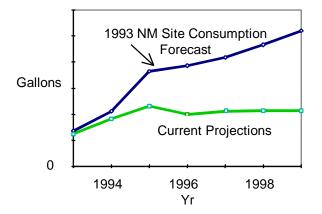

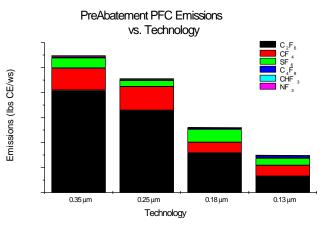

We also have comprehensive programs to reduce, recover, and/or recycle a variety of our processing chemicals. Modeling also plays a role in these efforts. For example, one of the difficult challenges we face is dealing with the changes in the chemical content in the emissions from generation to generation. Our ability to effectively measure and model individual tools is key to determining the correct solution path. For example, in Figure 4 we can see that the total quantity and chemistry is changing for Per Flouro Compound (PFC) going from our 0.35 micron generation by a factor of nearly 3X. In addition, the early generations contained relatively greater quantities of  $C_2F_6$  and  $CF_4$  when compared to the other effluent gases. The optimal technologies to deal

with these kinds of emissions are fundamentally different. Models help us understand these requirements and assure appropriate technology is in place [6].

Figure 4: Pre-abatement PFC emmissions vs. technology

#### Assembly Floor Layout and Operation [7]