# **External Memory Interface Handbook Volume 3: Reference Material**

# For UniPHY-based Device Families

Updated for Intel® Quartus® Prime Design Suite: 17.0

# **Contents**

| 1. Fu | unctional Description—UniPHY                                          | 8    |

|-------|-----------------------------------------------------------------------|------|

|       | 1.1. I/O Pads                                                         | 9    |

|       | 1.2. Reset and Clock Generation                                       |      |

|       | 1.3. Dedicated Clock Networks                                         |      |

|       | 1.4. Address and Command Datapath                                     |      |

|       | 1.5. Write Datapath                                                   |      |

|       | 1.5.1. Leveling Circuitry                                             |      |

|       | 1.6. Read Datapath                                                    |      |

|       | 1.7. Sequencer                                                        |      |

|       | 1.7.1. Nios II-Based Sequencer                                        |      |

|       | 1.7.2. RTL-based Sequencer                                            |      |

|       | 1.8. Shadow Registers                                                 |      |

|       | 1.8.1. Shadow Registers Operation                                     |      |

|       | 1.9. UniPHY Interfaces                                                |      |

|       | 1.9.1. The DLL and PLL Sharing Interface                              |      |

|       | 1.9.2. The OCT Sharing Interface                                      | . 25 |

|       | 1.10. UniPHY Signals                                                  |      |

|       | 1.11. PHY-to-Controller Interfaces                                    | . 30 |

|       | 1.12. Using a Custom Controller                                       | . 34 |

|       | 1.13. AFI 3.0 Specification                                           | 35   |

|       | 1.13.1. Bus Width and AFI Ratio                                       | 35   |

|       | 1.13.2. AFI Parameters                                                | . 36 |

|       | 1.13.3. AFI Signals                                                   | .37  |

|       | 1.14. Register Maps                                                   | .41  |

|       | 1.14.1. UniPHY Register Map                                           | . 42 |

|       | 1.14.2. Controller Register Map                                       |      |

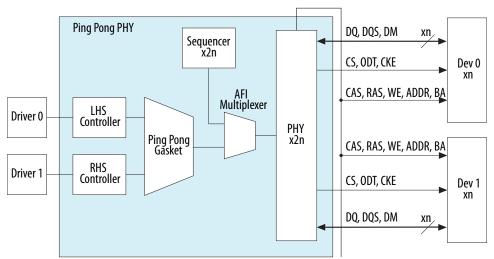

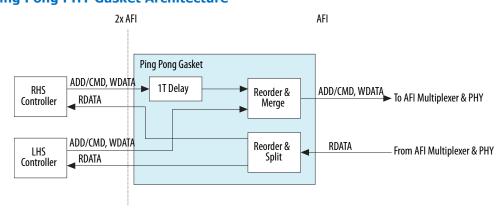

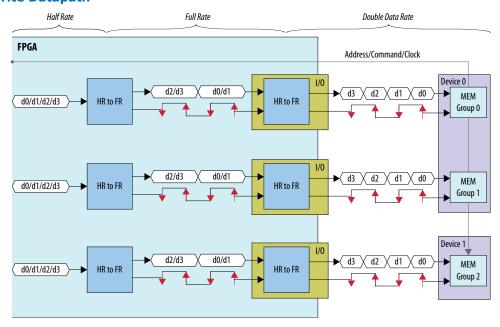

|       | 1.15. Ping Pong PHY                                                   |      |

|       | 1.15.1. Ping Pong PHY Feature Description                             |      |

|       | 1.15.2. Ping Pong PHY Architecture                                    |      |

|       | 1.15.3. Ping Pong PHY Operation                                       |      |

|       | 1.16. Efficiency Monitor and Protocol Checker                         |      |

|       | 1.16.1. Efficiency Monitor                                            |      |

|       | 1.16.2. Protocol Checker                                              |      |

|       | 1.16.3. Read Latency Counter                                          |      |

|       | 1.16.4. Using the Efficiency Monitor and Protocol Checker             |      |

|       | 1.16.5. Avalon CSR Slave and JTAG Memory Map                          |      |

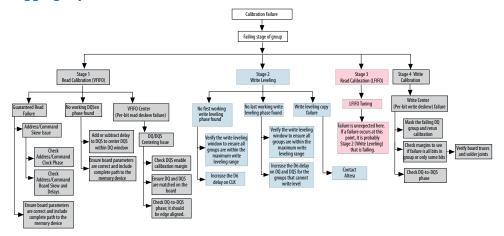

|       | 1.17. UniPHY Calibration Stages                                       |      |

|       | 1.17.1. Calibration Overview                                          |      |

|       | 1.17.2. Calibration Stages                                            |      |

|       | 1.17.3. Memory Initialization                                         | . 52 |

|       | 1.17.4. Stage 1: Read Calibration Part One—DQS Enable Calibration and |      |

|       | DQ/DQS Centering                                                      |      |

|       | 1.17.5. Stage 2: Write Calibration Part One                           |      |

|       | 1.17.6. Stage 3: Write Calibration Part Two—DQ/DQS Centering          |      |

|       | 1.17.7. Stage 4: Read Calibration Part Two—Read Latency Minimization  |      |

|       | 1.17.8. Calibration Signals                                           |      |

|       | 1.17.9. Calibration Time                                              | วร   |

|          | 1.18. Document Revision History                                            | 59 |

|----------|----------------------------------------------------------------------------|----|

| 2. F     | Functional Description—Intel MAX® 10 EMIF IP                               | 62 |

|          | 2.1. Intel MAX 10 EMIF Overview                                            |    |

|          | 2.2. External Memory Protocol Support                                      |    |

|          | 2.3. Intel MAX 10 Memory Controller                                        |    |

|          | 2.4. Intel MAX 10 Low Power Feature                                        |    |

|          | 2.5. Intel MAX 10 Memory PHY                                               |    |

|          | 2.5.1. Supported Topologies                                                |    |

|          | 2.5.2. Read Datapath                                                       |    |

|          | 2.5.3. Write Datapath                                                      |    |

|          | 2.5.4. Address and Command Datapath                                        |    |

|          | 2.5.5. Sequencer                                                           |    |

|          | 2.6. Calibration                                                           |    |

|          | 2.6.1. Read Calibration                                                    |    |

|          | 2.6.2. Write Calibration                                                   |    |

|          | 2.7. Sequencer Debug Information                                           |    |

|          | 2.8. Register Maps                                                         |    |

|          | 2.9. Document Revision History                                             |    |

| <u> </u> | •                                                                          |    |

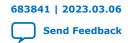

| 3. F     | Functional Description—Hard Memory Interface                               |    |

|          | 3.1. Multi-Port Front End (MPFE)                                           |    |

|          | 3.2. Multi-port Scheduling                                                 |    |

|          | 3.2.1. Port Scheduling                                                     |    |

|          | 3.2.2. DRAM Burst Scheduling                                               |    |

|          | 3.2.3. DRAM Power Saving Modes                                             |    |

|          | 3.3. MPFE Signal Descriptions                                              |    |

|          | 3.4.1 Classing                                                             |    |

|          | 3.4.1. Clocking                                                            |    |

|          | 3.4.3. DRAM Interface                                                      |    |

|          | 3.4.4. ECC                                                                 |    |

|          | 3.4.5. Bonding of Memory Controllers                                       |    |

|          | 3.5. Hard PHY                                                              |    |

|          | 3.5.1. Interconnections                                                    |    |

|          | 3.5.2. Clock Domains                                                       |    |

|          | 3.5.3. Hard Sequencer                                                      |    |

|          | 3.5.4. MPFE Setup Guidelines                                               |    |

|          | 3.5.5. Soft Memory Interface to Hard Memory Interface Migration Guidelines |    |

|          | 3.5.6. Bonding Interface Guidelines                                        |    |

|          | 3.6. Document Revision History                                             |    |

|          | ,                                                                          |    |

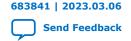

| 4. F     | Functional Description—HPS Memory Controller                               |    |

|          | 4.1. Features of the SDRAM Controller Subsystem                            |    |

|          | 4.2. SDRAM Controller Subsystem Block Diagram                              |    |

|          | 4.3. SDRAM Controller Memory Options                                       |    |

|          | 4.4. SDRAM Controller Subsystem Interfaces                                 |    |

|          | 4.4.1. MPU Subsystem Interface                                             |    |

|          | 4.4.2. L3 Interconnect Interface                                           |    |

|          | 4.4.3. CSR Interface                                                       |    |

|          | 4.4.4. FPGA-to-HPS SDRAM Interface                                         |    |

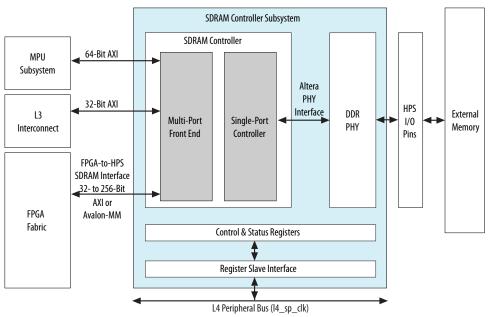

|          | 4.5. Memory Controller Architecture                                        | 92 |

|      | 4.5.1. Multi-Port Front End                                         | 93  |

|------|---------------------------------------------------------------------|-----|

|      | 4.5.2. Single-Port Controller                                       | 94  |

|      | 4.6. Functional Description of the SDRAM Controller Subsystem       | 96  |

|      | 4.6.1. MPFE Operation Ordering                                      |     |

|      | 4.6.2. MPFE Multi-Port Arbitration                                  | 96  |

|      | 4.6.3. MPFE SDRAM Burst Scheduling                                  |     |

|      | 4.6.4. Single-Port Controller Operation                             |     |

|      | 4.7. SDRAM Power Management                                         |     |

|      | 4.8. DDR PHY                                                        |     |

|      | 4.9. Clocks                                                         |     |

|      | 4.10. Resets                                                        | 112 |

|      | 4.10.1. Taking the SDRAM Controller Subsystem Out of Reset          |     |

|      | 4.11. Port Mappings                                                 |     |

|      | 4.12. Initialization                                                |     |

|      | 4.12.1. FPGA-to-SDRAM Protocol Details                              |     |

|      | 4.13. SDRAM Controller Subsystem Programming Model                  |     |

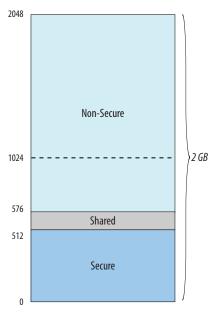

|      | 4.13.1. HPS Memory Interface Architecture                           |     |

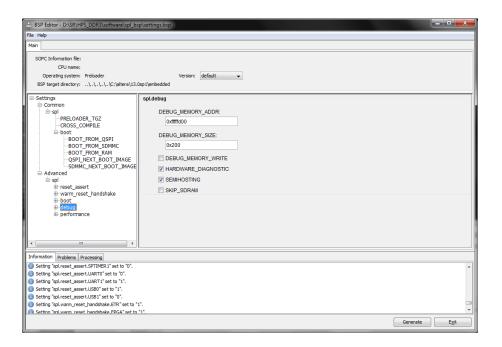

|      | 4.13.2. HPS Memory Interface Configuration                          |     |

|      | 4.13.3. HPS Memory Interface Simulation                             |     |

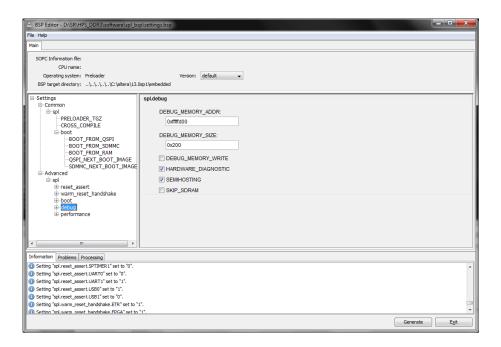

|      | 4.13.4. Generating a Preloader Image for HPS with EMIF              |     |

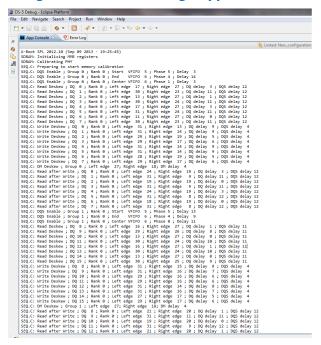

|      | 4.14. Debugging HPS SDRAM in the Preloader                          |     |

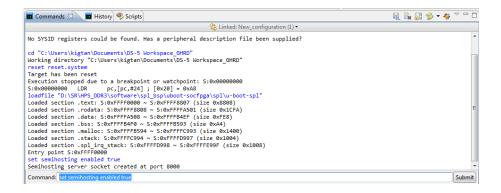

|      | 4.14.1. Enabling UART or Semihosting Printout                       |     |

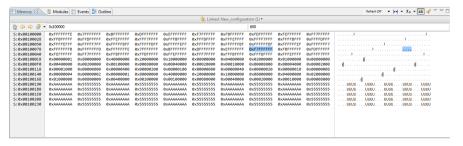

|      | 4.14.2. Enabling Simple Memory Test                                 |     |

|      | 4.14.3. Enabling the Debug Report                                   |     |

|      | 4.14.4. Writing a Predefined Data Pattern to SDRAM in the Preloader |     |

|      | 4.15. SDRAM Controller Address Map and Register Definitions         |     |

|      | 4.15.1. SDRAM Controller Address Map                                |     |

|      | 4.16. Document Revision History                                     | 155 |

|      | unctional Description—HPC II Controller                             | 457 |

| 5. F |                                                                     |     |

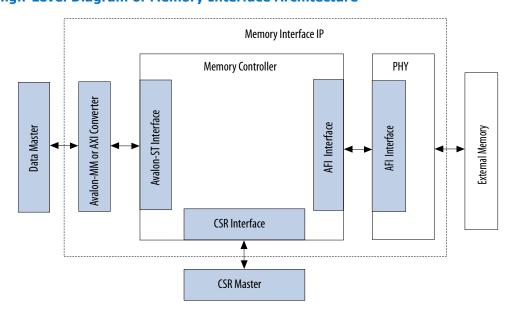

|      | 5.1. HPC II Memory Interface Architecture                           |     |

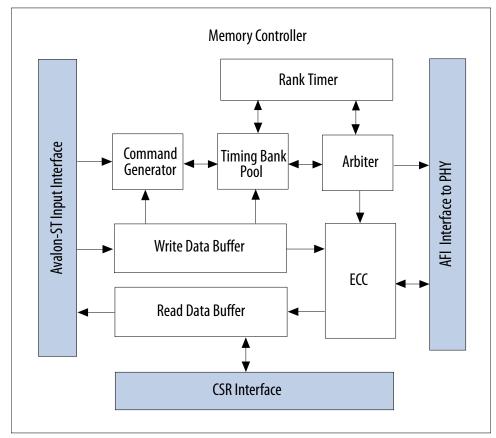

|      | 5.2. HPC II Memory Controller Architecture                          |     |

|      | 5.2.1. Backpressure Support                                         |     |

|      | 5.2.2. Command Generator                                            |     |

|      | 5.2.3. Timing Bank Pool                                             |     |

|      | 5.2.4. Arbiter                                                      |     |

|      | 5.2.5. Rank Timer                                                   |     |

|      | 5.2.6. Read Data Buffer and Write Data Buffer                       |     |

|      | 5.2.7. ECC Block                                                    | 161 |

|      | 5.2.8. AFI and CSR Interfaces                                       |     |

|      | 5.3. HPC II Controller Features                                     |     |

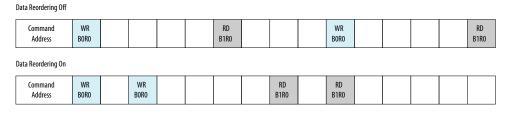

|      | 5.3.1. Data Reordering                                              |     |

|      | 5.3.2. Pre-emptive Bank Management                                  |     |

|      | 5.3.3. Quasi-1T and Quasi-2T                                        |     |

|      | 5.3.4. User Autoprecharge Commands                                  |     |

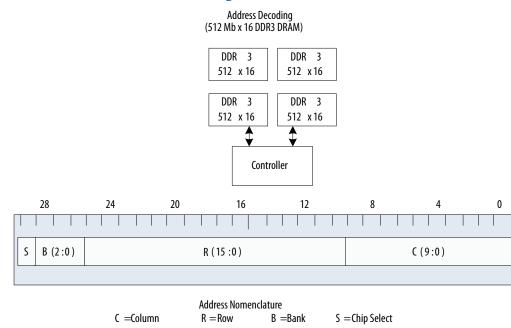

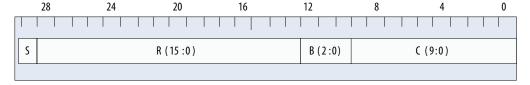

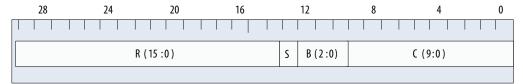

|      | 5.3.5. Address and Command Decoding Logic                           |     |

|      | 5.3.6. Low-Power Logic                                              |     |

|      | 5.3.7. ODT Generation Logic                                         | 163 |

|      |                                                                     |     |

|      | 5.3.8. Burst Merging                                                |     |

|      | 5.3.8. Burst Merging                                                | 165 |

| 5.4.1. Clock and Reset Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 5.4.2. Avalon-ST Data Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

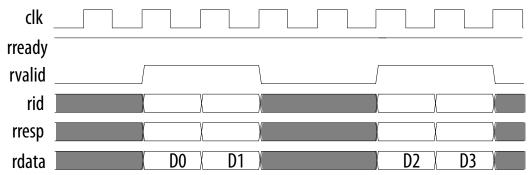

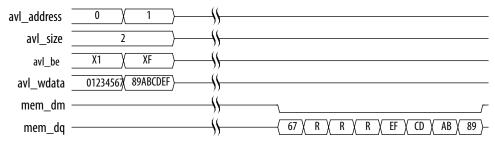

| 5.4.3. AXI Data Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 169               |

| 5.4.4. Controller-PHY Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 174               |

| 5.4.5. Memory Side-Band Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| 5.4.6. Controller External Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 175               |

| 5.5. Top-Level Signals Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 176               |

| 5.5.1. Clock and Reset Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 176               |

| 5.5.2. Local Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 177               |

| 5.5.3. Controller Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 181               |

| 5.5.4. CSR Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 182               |

| 5.5.5. Soft Controller Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 183               |

| 5.5.6. Hard Controller Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 187               |

| 5.6. Sequence of Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 190               |

| 5.7. Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 192               |

| 6. Functional Description—QDR II Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 104               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

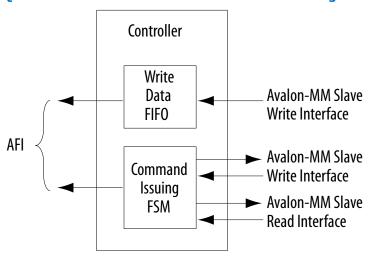

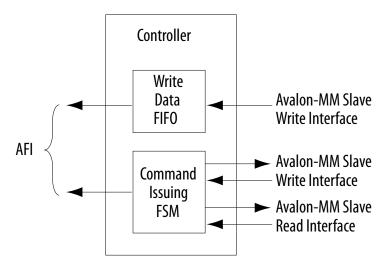

| 6.1. Block Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

| 6.1.1. Avalon-MM Slave Read and Write Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| 6.1.2. Command Issuing FSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 6.1.3. AFI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                   |

| 6.2. Avalon-MM and Memory Data Width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

| 6.3. Signal Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

| 6.4. Document Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |

| 7. Functional Description—RLDRAM II Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 198               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| 7.1. Block Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 198               |

| 7.1. Block Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                   |

| 7.1.1. Avalon-MM Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 198               |

| 7.1.1. Avalon-MM Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 198<br>199        |

| 7.1.1. Avalon-MM Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 198<br>199<br>199 |

| 7.1.1. Avalon-MM Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 198<br>199<br>199 |

| 7.1.1. Avalon-MM Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| 7.1.1. Avalon-MM Slave Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI 7.2. User-Controlled Features.                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI 7.2. User-Controlled Features 7.2.1. Error Detection Parity 7.2.2. User-Controlled Refresh                                                                                                                                                                                                                                                                                                                                             |                   |

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI 7.2. User-Controlled Features 7.2.1. Error Detection Parity                                                                                                                                                                                                                                                                                                                                                                            |                   |

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI 7.2. User-Controlled Features 7.2.1. Error Detection Parity 7.2.2. User-Controlled Refresh 7.3. Avalon-MM and Memory Data Width                                                                                                                                                                                                                                                                                                        |                   |

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI 7.2. User-Controlled Features 7.2.1. Error Detection Parity 7.2.2. User-Controlled Refresh 7.3. Avalon-MM and Memory Data Width 7.4. Signal Descriptions 7.5. Document Revision History                                                                                                                                                                                                                                                |                   |

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI 7.2. User-Controlled Features 7.2.1. Error Detection Parity 7.2.2. User-Controlled Refresh 7.3. Avalon-MM and Memory Data Width 7.4. Signal Descriptions 7.5. Document Revision History 8. Functional Description—RLDRAM 3 PHY-Only IP                                                                                                                                                                                                 |                   |

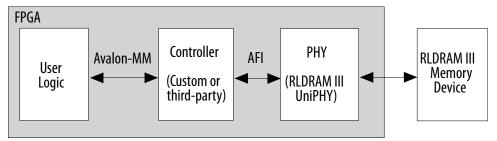

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI 7.2. User-Controlled Features 7.2.1. Error Detection Parity 7.2.2. User-Controlled Refresh 7.3. Avalon-MM and Memory Data Width 7.4. Signal Descriptions 7.5. Document Revision History.  8. Functional Description—RLDRAM 3 PHY-Only IP 8.1. Block Description                                                                                                                                                                        |                   |

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI 7.2. User-Controlled Features 7.2.1. Error Detection Parity 7.2.2. User-Controlled Refresh 7.3. Avalon-MM and Memory Data Width 7.4. Signal Descriptions 7.5. Document Revision History.  8. Functional Description—RLDRAM 3 PHY-Only IP 8.1. Block Description 8.2. Features                                                                                                                                                          |                   |

| 7.1.1. Avalon-MM Slave Interface. 7.1.2. Write Data FIFO Buffer. 7.1.3. Command Issuing FSM. 7.1.4. Refresh Timer. 7.1.5. Timer Module. 7.1.6. AFI. 7.2. User-Controlled Features. 7.2.1. Error Detection Parity. 7.2.2. User-Controlled Refresh. 7.3. Avalon-MM and Memory Data Width. 7.4. Signal Descriptions. 7.5. Document Revision History.  8. Functional Description—RLDRAM 3 PHY-Only IP. 8.1. Block Description. 8.2. Features. 8.3. RLDRAM 3 AFI Protocol.                                                                                                                |                   |

| 7.1.1. Avalon-MM Slave Interface 7.1.2. Write Data FIFO Buffer 7.1.3. Command Issuing FSM 7.1.4. Refresh Timer 7.1.5. Timer Module 7.1.6. AFI 7.2. User-Controlled Features 7.2.1. Error Detection Parity 7.2.2. User-Controlled Refresh 7.3. Avalon-MM and Memory Data Width 7.4. Signal Descriptions 7.5. Document Revision History.  8. Functional Description—RLDRAM 3 PHY-Only IP 8.1. Block Description 8.2. Features                                                                                                                                                          |                   |

| 7.1.1. Avalon-MM Slave Interface. 7.1.2. Write Data FIFO Buffer. 7.1.3. Command Issuing FSM. 7.1.4. Refresh Timer. 7.1.5. Timer Module. 7.1.6. AFI. 7.2. User-Controlled Features. 7.2.1. Error Detection Parity. 7.2.2. User-Controlled Refresh. 7.3. Avalon-MM and Memory Data Width. 7.4. Signal Descriptions. 7.5. Document Revision History.  8. Functional Description—RLDRAM 3 PHY-Only IP. 8.1. Block Description. 8.2. Features. 8.3. RLDRAM 3 AFI Protocol.                                                                                                                |                   |

| 7.1.1. Avalon-MM Slave Interface. 7.1.2. Write Data FIFO Buffer. 7.1.3. Command Issuing FSM. 7.1.4. Refresh Timer. 7.1.5. Timer Module. 7.1.6. AFI. 7.2. User-Controlled Features. 7.2.1. Error Detection Parity. 7.2.2. User-Controlled Refresh. 7.3. Avalon-MM and Memory Data Width. 7.4. Signal Descriptions. 7.5. Document Revision History.  8. Functional Description—RLDRAM 3 PHY-Only IP. 8.1. Block Description. 8.2. Features. 8.3. RLDRAM 3 AFI Protocol. 8.4. Document Revision History.                                                                                |                   |

| 7.1.1. Avalon-MM Slave Interface. 7.1.2. Write Data FIFO Buffer. 7.1.3. Command Issuing FSM. 7.1.4. Refresh Timer. 7.1.5. Timer Module. 7.1.6. AFI. 7.2. User-Controlled Features. 7.2.1. Error Detection Parity. 7.2.2. User-Controlled Refresh. 7.3. Avalon-MM and Memory Data Width. 7.4. Signal Descriptions. 7.5. Document Revision History.  8. Functional Description—RLDRAM 3 PHY-Only IP. 8.1. Block Description. 8.2. Features. 8.3. RLDRAM 3 AFI Protocol. 8.4. Document Revision History.                                                                                |                   |

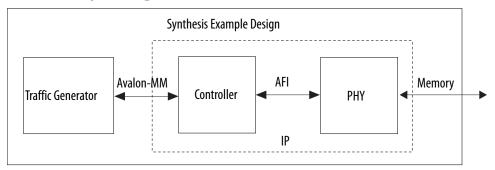

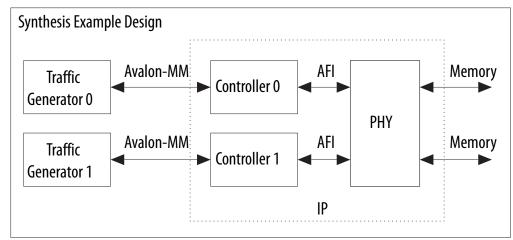

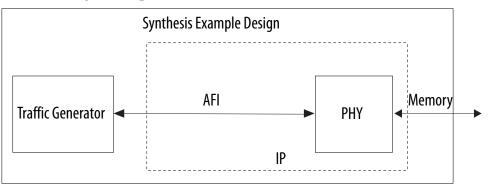

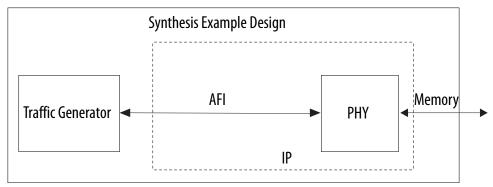

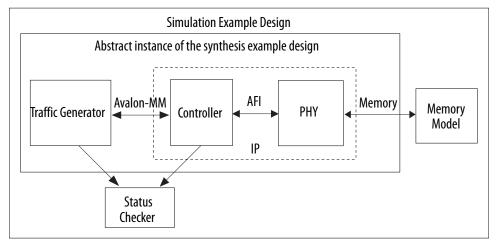

| 7.1.1. Avalon-MM Slave Interface. 7.1.2. Write Data FIFO Buffer. 7.1.3. Command Issuing FSM. 7.1.4. Refresh Timer. 7.1.5. Timer Module. 7.1.6. AFI. 7.2. User-Controlled Features. 7.2.1. Error Detection Parity. 7.2.2. User-Controlled Refresh. 7.3. Avalon-MM and Memory Data Width. 7.4. Signal Descriptions. 7.5. Document Revision History.  8. Functional Description—RLDRAM 3 PHY-Only IP. 8.1. Block Description. 8.2. Features. 8.3. RLDRAM 3 AFI Protocol. 8.4. Document Revision History.  9. Functional Description—Example Designs. 9.1. UniPHY-Based Example Designs. |                   |

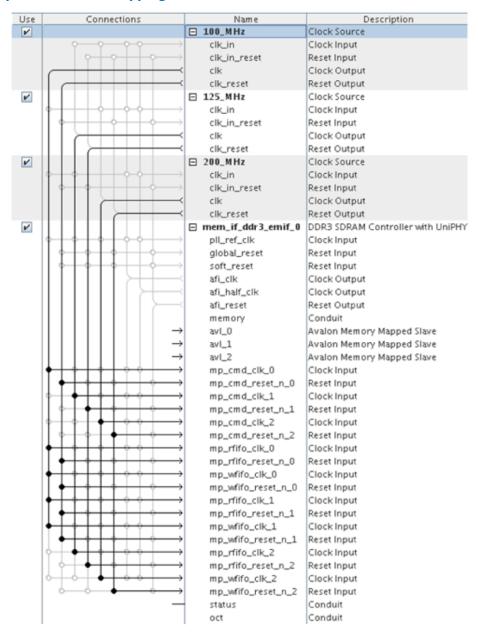

|     | 9.1.4. Creating and Connecting the UniPHY Memory Interface and the Traffic       |       |

|-----|----------------------------------------------------------------------------------|-------|

|     | Generator in Platform Designer                                                   |       |

|     | 9.2. Document Revision History                                                   | 215   |

| 10. | Introduction to UniPHY IP                                                        | . 217 |

|     | 10.1. Release Information                                                        | 217   |

|     | 10.2. Device Support Levels                                                      |       |

|     | 10.3. Device Family and Protocol Support                                         |       |

|     | 10.4. UniPHY-Based External Memory Interface Features                            |       |

|     | 10.5. System Requirements                                                        |       |

|     | 10.6. Intel FPGA IP Core Verification.                                           |       |

|     | 10.7. Resource Utilization                                                       |       |

|     | 10.7.1. DDR2, DDR3, and LPDDR2 Resource Utilization in Arria V Devices           |       |

|     | 10.7.2. DDR2 and DDR3 Resource Utilization in Arria II GZ Devices                | 221   |

|     | 10.7.3. DDR2 and DDR3 Resource Utilization in Stratix III Devices                | 223   |

|     | 10.7.4. DDR2 and DDR3 Resource Utilization in Stratix IV Devices                 | 224   |

|     | 10.7.5. DDR2 and DDR3 Resource Utilization in Arria V GZ and Stratix V Devices   | 225   |

|     | 10.7.6. QDR II and QDR II+ Resource Utilization in Arria V Devices               | 227   |

|     | 10.7.7. QDR II and QDR II+ Resource Utilization in Arria II GX Devices           | 227   |

|     | 10.7.8. QDR II and QDR II+ Resource Utilization in Arria II GZ, Arria V GZ,      |       |

|     | Stratix III, Stratix IV, and Stratix V Devices                                   |       |

|     | 10.7.9. RLDRAM II Resource Utilization in Arria V Devices                        | 228   |

|     | 10.7.10. RLDRAM II Resource Utilization in Arria II GZ, Arria V GZ, Stratix III, | 220   |

|     | Stratix IV, and Stratix V Devices                                                |       |

|     | 10.8. Document Revision History                                                  | 229   |

| 11. | Latency for UniPHY IP                                                            | 231   |

|     | 11.1. DDR2 SDRAM LATENCY                                                         | 231   |

|     | 11.2. DDR3 SDRAM LATENCY                                                         |       |

|     | 11.3. LPDDR2 SDRAM LATENCY                                                       | 232   |

|     | 11.4. QDR II and QDR II+ SRAM Latency                                            | 233   |

|     | 11.5. RLDRAM II Latency                                                          | 233   |

|     | 11.6. RLDRAM 3 Latency                                                           | 234   |

|     | 11.7. Variable Controller Latency                                                |       |

|     | 11.8. Document Revision History                                                  | 234   |

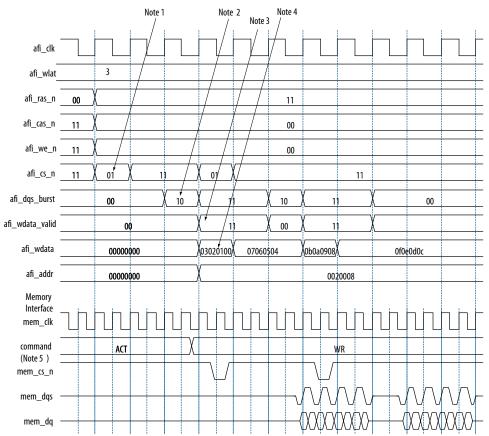

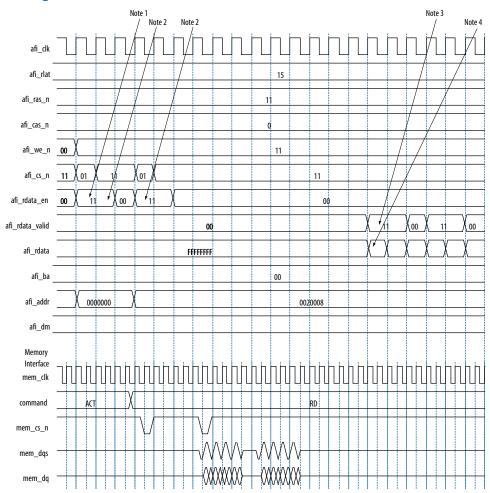

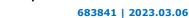

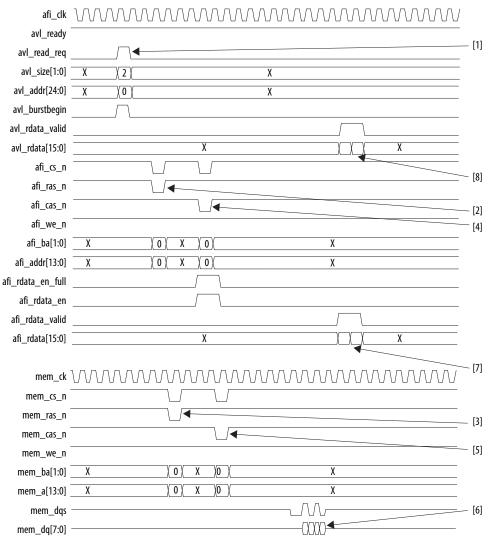

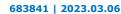

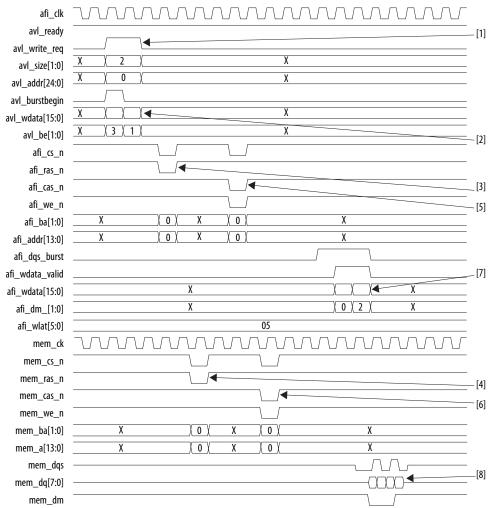

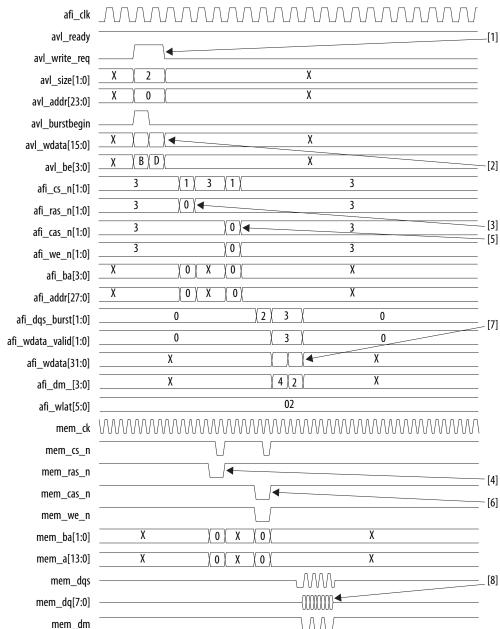

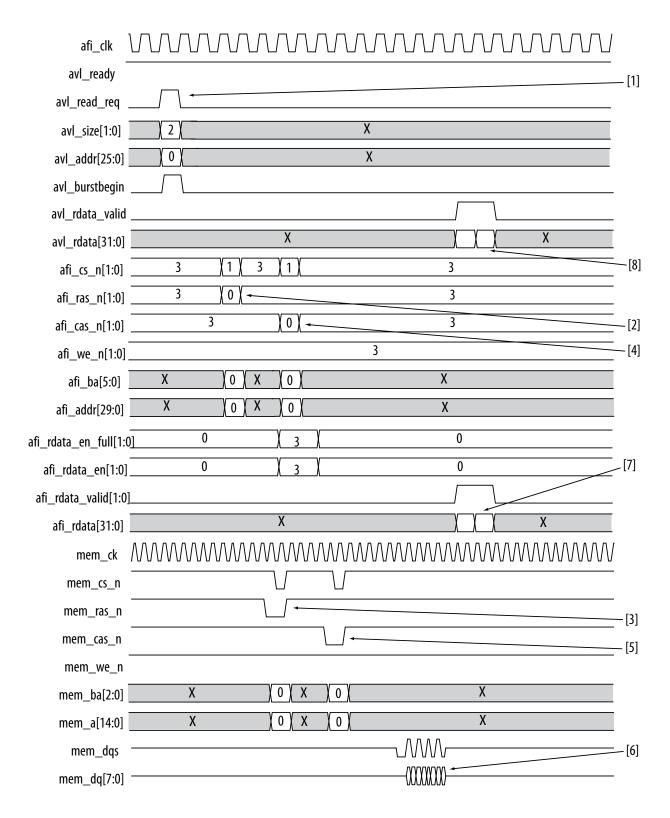

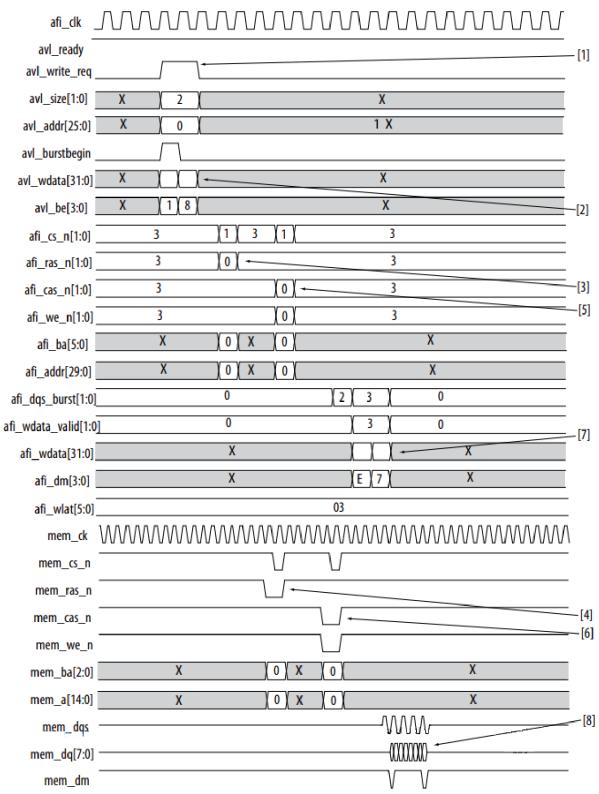

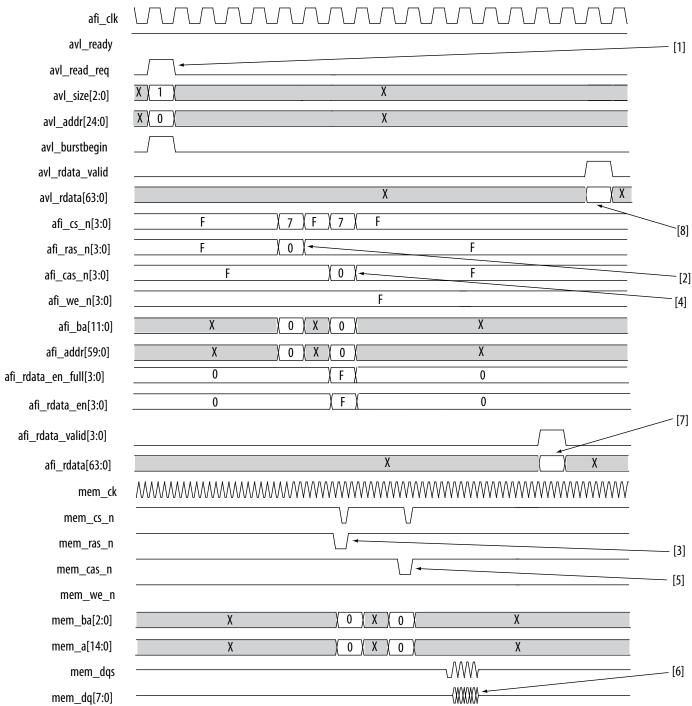

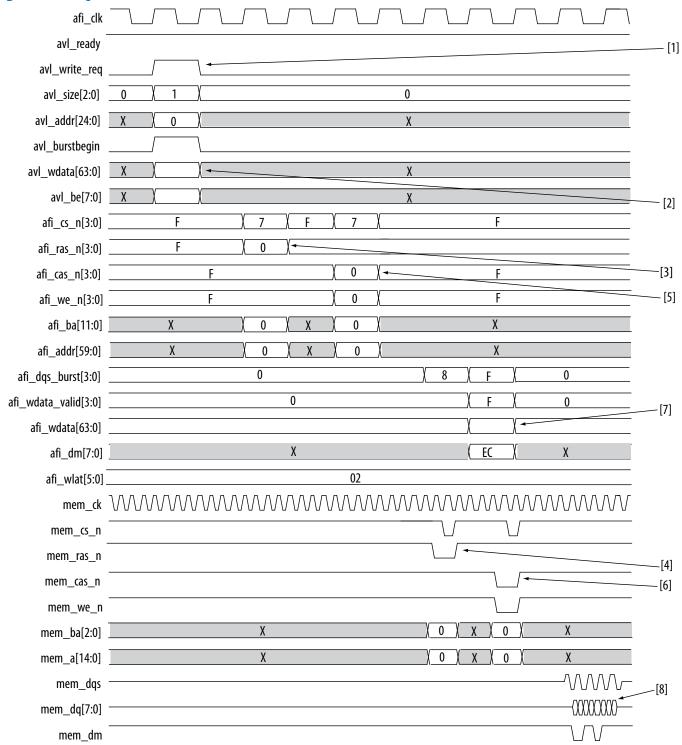

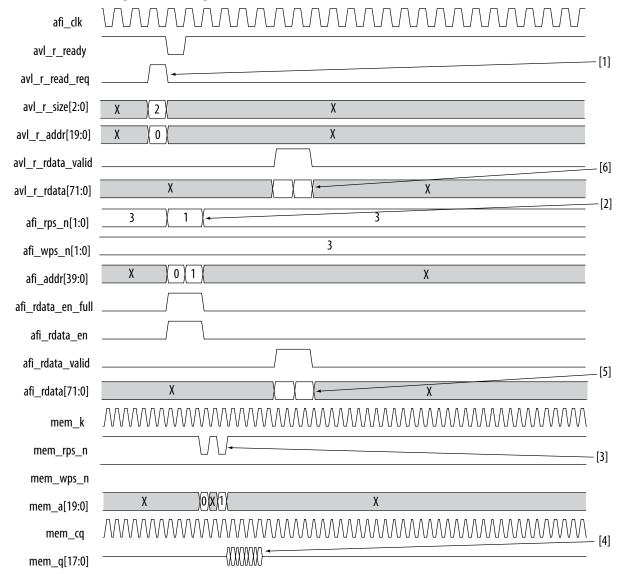

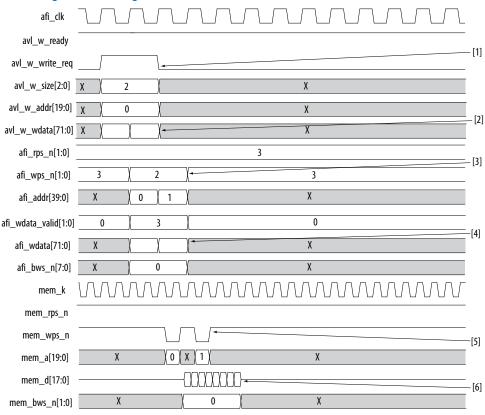

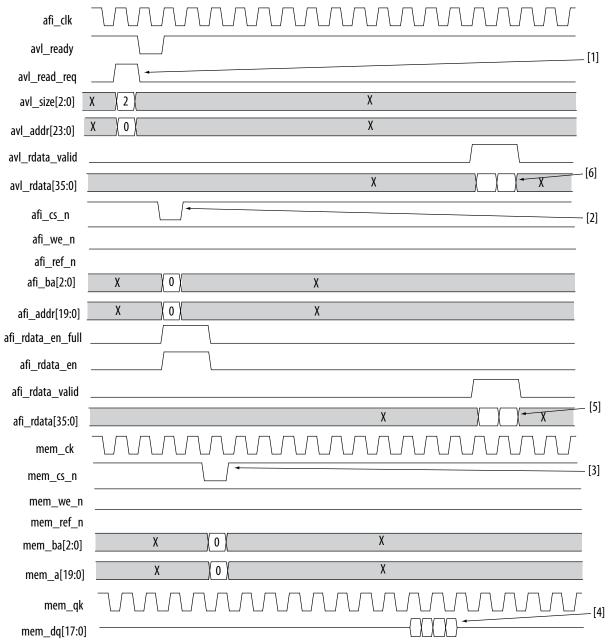

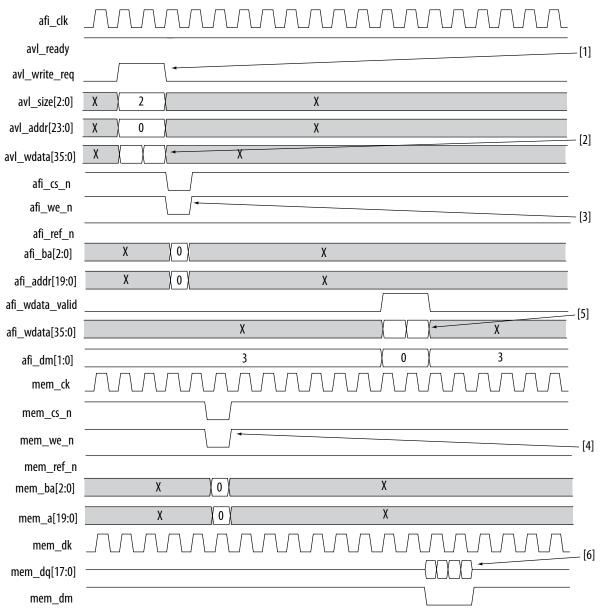

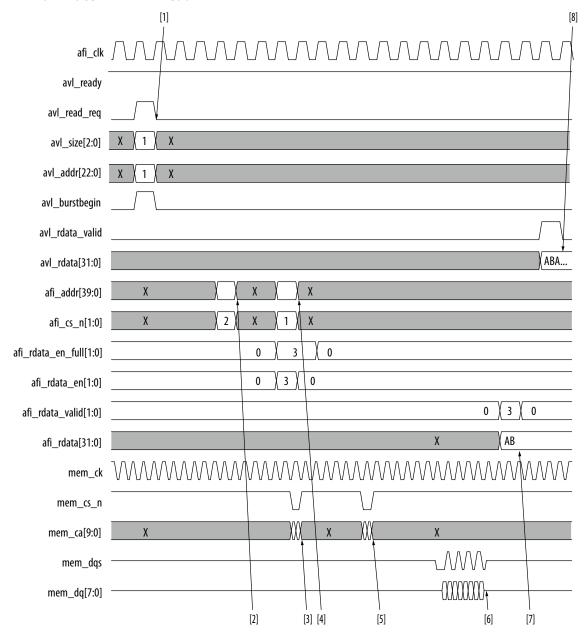

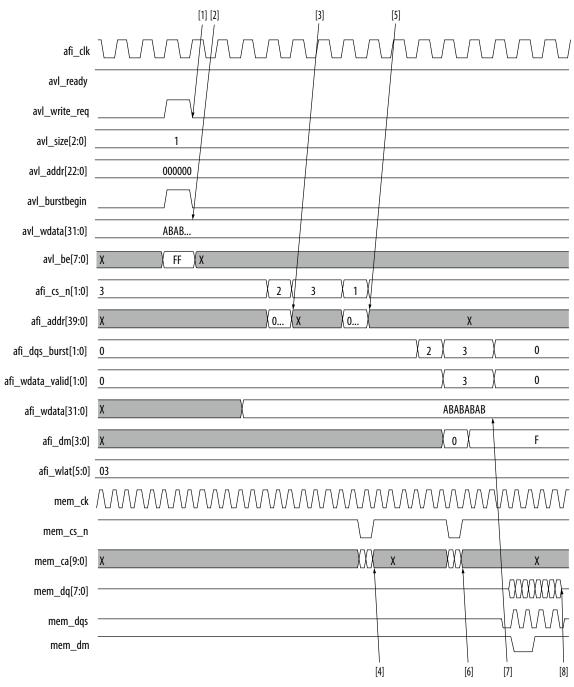

| 12. | Timing Diagrams for UniPHY IP                                                    | - 236 |

|     | 12.1. DDR2 Timing Diagrams                                                       |       |

|     | 12.2. DDR3 Timing Diagrams                                                       |       |

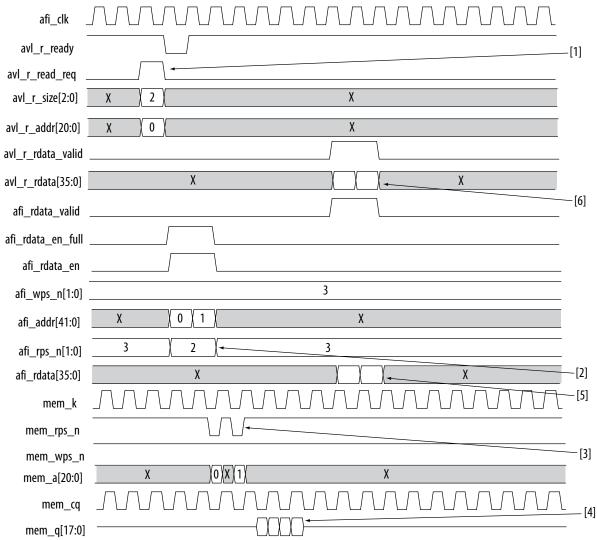

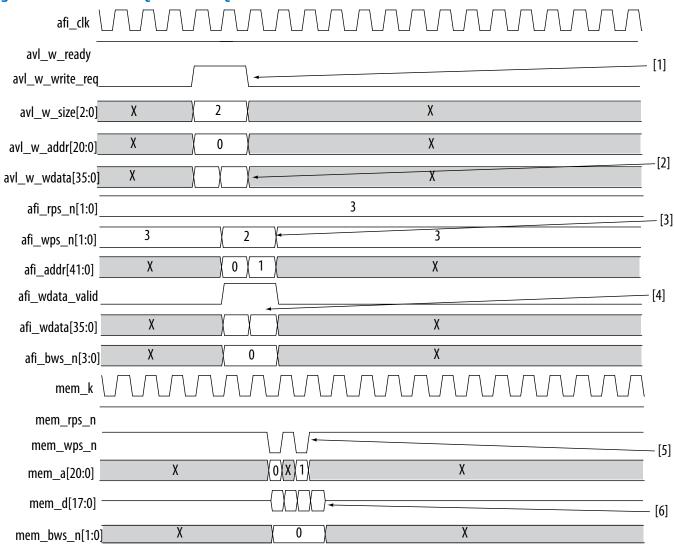

|     | 12.3. QDR II and QDR II+ Timing Diagrams                                         |       |

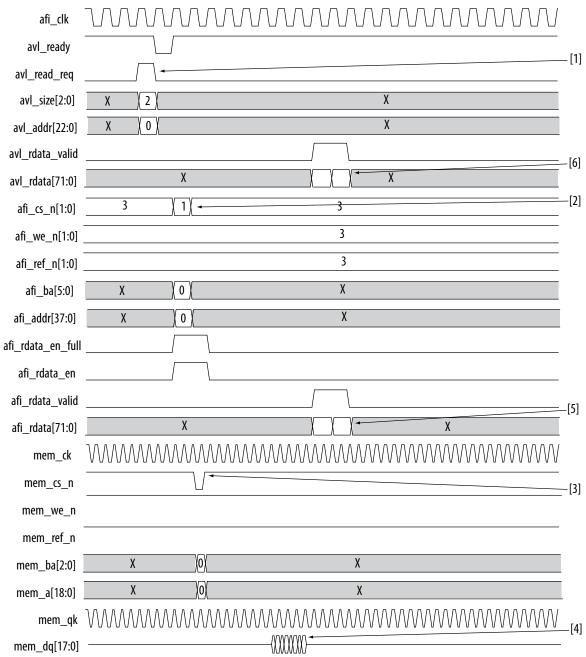

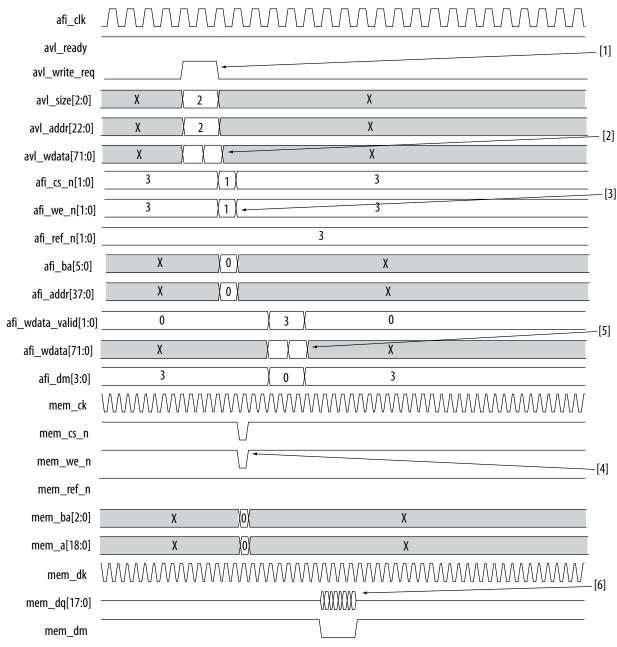

|     | 12.4. RLDRAM II Timing Diagrams                                                  |       |

|     | 12.5. LPDDR2 Timing Diagrams                                                     |       |

|     | 12.6. RLDRAM 3 Timing Diagrams                                                   |       |

|     | 12.7. Document Revision History                                                  |       |

|     | ·                                                                                |       |

| 13. | External Memory Interface Debug Toolkit                                          |       |

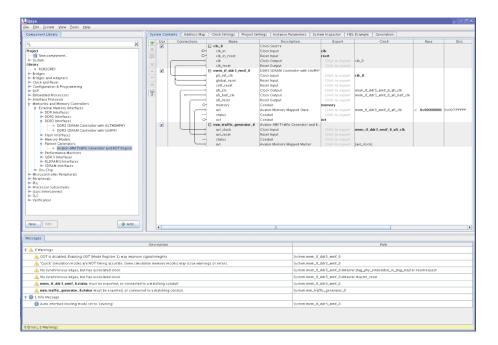

|     | 13.1. User Interface                                                             |       |

|     | 13.1.1. Communication                                                            |       |

|     | 13.1.2. Calibration and Report Generation                                        |       |

|     | 13.2. Setup and Use                                                              |       |

|     | 13.2.1. General Workflow                                                         |       |

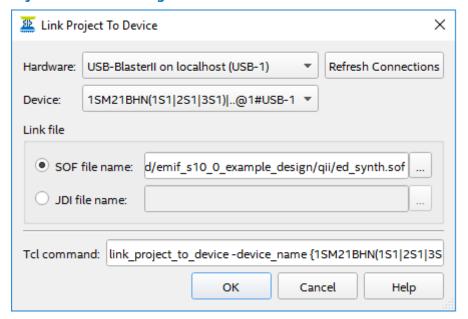

|     | 15 / / LINVING TOO PROJECT TO 2 LIGVICA                                          | 1/4   |

|       | 13.2.3. Establishing Communication to Connections                                | . 275 |

|-------|----------------------------------------------------------------------------------|-------|

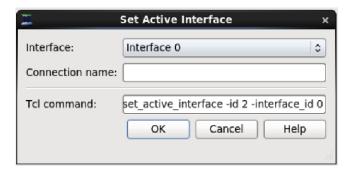

|       | 13.2.4. Selecting an Active Interface                                            | 275   |

|       | 13.2.5. Reports                                                                  | . 276 |

|       | 13.3. Operational Considerations                                                 | . 277 |

|       | 13.4. Troubleshooting                                                            | . 278 |

|       | 13.5. Debug Report for Arria V and Cyclone V SoC Devices                         |       |

|       | 13.5.1. Enabling the Debug Report for Arria V and Cyclone V SoC Devices          | . 279 |

|       | 13.5.2. Determining the Failing Calibration Stage for a Cyclone V or Arria V HPS |       |

|       | SDRAM Controller                                                                 |       |

|       | 13.6. On-Chip Debug Port for UniPHY-based EMIF IP                                | . 280 |

|       | 13.6.1. Access Protocol                                                          |       |

|       | 13.6.2. Command Codes Reference                                                  |       |

|       | 13.6.3. Header Files                                                             |       |

|       | 13.6.4. Generating IP With the Debug Port                                        |       |

|       | 13.6.5. Example C Code for Accessing Debug Data                                  |       |

|       | 13.7. Example Tcl Script for Running the Legacy EMIF Debug Toolkit               |       |

|       | 13.8. Document Revision History                                                  | . 285 |

| 14. I | Upgrading to UniPHY-based Controllers from ALTMEMPHY-based Controllers           | .287  |

|       | 14.1. Generating Equivalent Design                                               | . 287 |

|       | 14.2. Replacing the ALTMEMPHY Datapath with UniPHY Datapath                      |       |

|       | 14.3. Resolving Port Name Differences                                            |       |

|       | 14.4. Creating OCT Signals                                                       |       |

|       | 14.5. Running Pin Assignments Script                                             |       |

|       | 14.6. Removing Obsolete Files                                                    |       |

|       | 14.7. Simulating your Design                                                     |       |

|       | 14.8. Document Revision History                                                  |       |

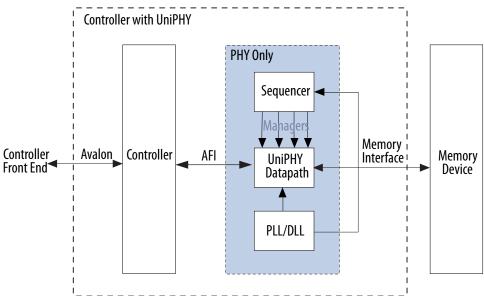

# 1. Functional Description—UniPHY

Note:

The External Memory Interface Handbook describes the UniPHY-based external memory interface IP available for use with Intel®'s V-series and earlier devices using UniPHY-based IP.

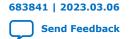

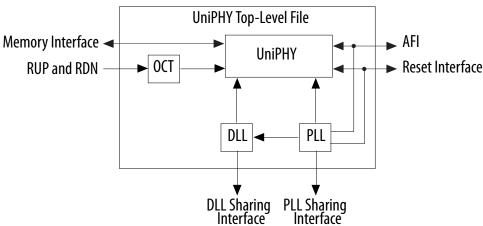

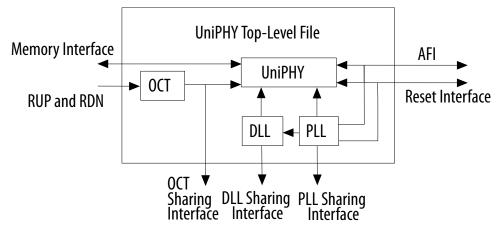

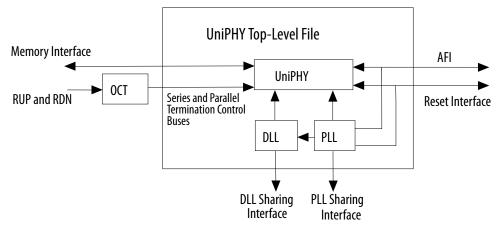

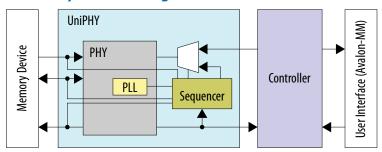

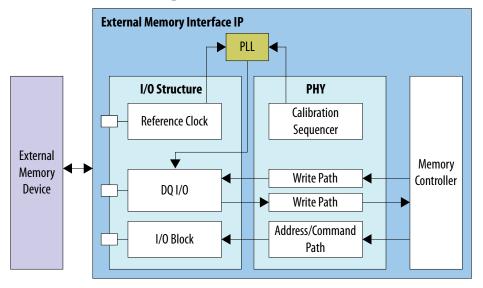

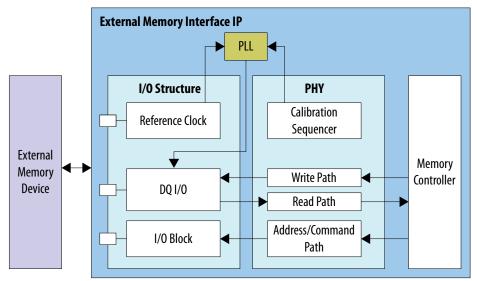

UniPHY is the physical layer of the external memory interface. The major functional units of the UniPHY layer include the following:

- · Reset and clock generation

- · Address and command datapath

- Write datapath

- Read datapath

- Sequencer

The following figure shows the PHY block diagram.

Figure 1. PHY Block Diagram

## **Related Information**

• UniPHY Interfaces on page 23

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

- UniPHY Signals on page 27

- PHY-to-Controller Interfaces on page 30

- Using a Custom Controller on page 34

- AFI 3.0 Specification on page 35

- Register Maps on page 41

- Ping Pong PHY on page 44

- Efficiency Monitor on page 48

- Calibration Stages on page 51

# 1.1. I/O Pads

The I/O pads contain all the I/O instantiations.

## 1.2. Reset and Clock Generation

At a high level, clocks in the PHY can be classified into two domains: the PHY-memory domain and the PHY-AFI domain.

The PHY-memory domain interfaces with the external memory device and always operate at full-rate. The PHY-AFI domain interfaces with the memory controller and can be a full-rate, half-rate, or quarter-rate clock, based on the controller in use.

The number of clock domains in a memory interface can vary depending on its configuration; for example:

- At the PHY-memory boundary, separate clocks may exist to generate the memory clock signal, the output strobe, and to output write data, as well as address and command signals. These clocks include pll\_dq\_write\_clk, pll\_write\_clk, pll\_mem\_clk, and pll\_addr\_cmd\_clk. These clocks are phase-shifted as required to achieve the desired timing relationships between memory clock, address and command signals, output data, and output strobe.

- For quarter-rate interfaces, additional clock domains such as pll\_hr\_clock are required to convert signals between half-rate and quarter-rate.

- For high-performance memory interfaces using Arria V, Cyclone V, or Stratix V devices, additional clocks may be required to handle transfers between the device core and the I/O periphery for timing closure. For core-to-periphery transfers, the latch clock is pll\_c2p\_write\_clock; for periphery-to-core transfers, it is pll\_p2c\_read\_clock. These clocks are automatically phase-adjusted for timing closure during IP generation, but can be further adjusted in the parameter editor. If the phases of these clocks are zero, the Fitter may remove these clocks during optimization.Also, high-performance interfaces using a Nios II-based sequencer require two additional clocks, pll\_avl\_clock for the Nios II processor, and pll\_config\_clock for clocking the I/O scan chains during calibration.

For a complete list of clocks in your memory interface, compile your design and run the **Report Clocks** command in the Timing Analyzer.

#### 1.3. Dedicated Clock Networks

The UniPHY layer employs three types of dedicated clock networks:

- Global clock network

- Dual-regional clock network

- PHY clock network (applicable to Arria V, Cyclone V, and Stratix V devices, and later)

The PHY clock network is a dedicated high-speed, low-skew, balanced clock tree designed for high-performance external memory interface. For device families that support the PHY clock network, UniPHY always uses the PHY clock network for all clocks at the PHY-memory boundary.

For families that do not support the PHY clock network, UniPHY uses either dual-regional or global clock networks for clocks at the PHY-memory boundary. During generation, the system selects dual-regional or global clocks automatically, depending on whether a given interface spans more than one quadrant. UniPHY does not mix the usage of dual-regional and global clock networks for clocks at the PHY-memory boundary; this ensures that timing characteristics of the various output paths are as similar as possible.

The <variation\_name>\_pin\_assignments.tcl script creates the appropriate clock network type assignment. The use of the PHY clock network is specified directly in the RTL code, and does not require an assignment.

The UniPHY uses an active-low, asychronous assert and synchronous de-assert reset scheme. The global reset signal resets the PLL in the PHY and the rest of the system is held in reset until after the PLL is locked.

# 1.4. Address and Command Datapath

The memory controller controls the read and write addresses and commands to meet the memory specifications.

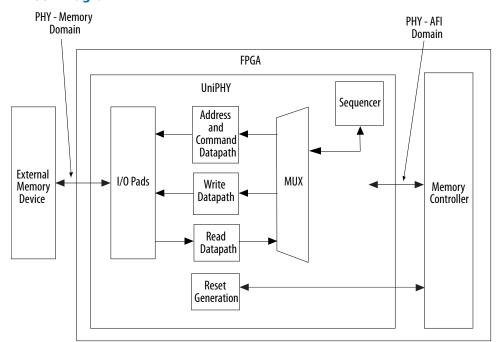

The PHY is indifferent to address or command—that is, it performs no decoding or other operations—and the circuitry is the same for both. In full-rate and half-rate interfaces, address and command is full rate, while in quarter-rate interfaces, address and command is half rate.

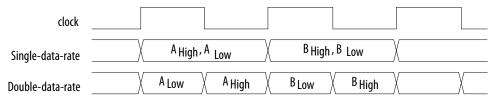

Address and command signals are generated in the Altera PHY interface (AFI) clock domain and sent to the memory device in the address and command clock domain. The double-data rate input/output (DDIO) stage converts the half-rate signals into full-rate signals, when the AFI clock runs at half-rate. For quarter-rate interfaces, additional DDIO stages exist to convert the address and command signals in the quarter-rate AFI clock domain to half-rate.

The address and command clock is offset with respect to the memory clock to balance the nominal setup and hold margins at the memory device (center-alignment). In the example below, this offset is 270 degrees. The Fitter can further optimize margins based on the actual delays and clock skews. In half-rate and quarter-rate designs, the full-rate cycle shifter blocks can perform a shift measured in full-rate cycles to implement the correct write latency; without this logic, the controller would only be able to implement even write latencies as it operates at half the speed. The full-rate cycle shifter is clocked by either the AFI clock or the address and command clock, depending on the PHY configuration, to maximize timing margins on the path from the AFI clock to the address and command clock.

Figure 2. Address and Command Datapath (Half-rate example shown)

# 1.5. Write Datapath

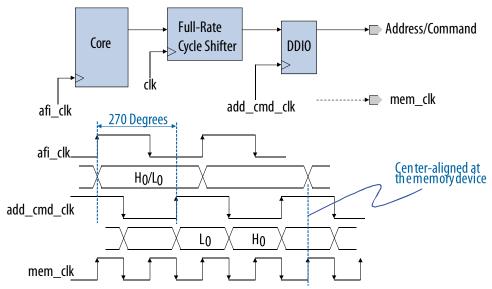

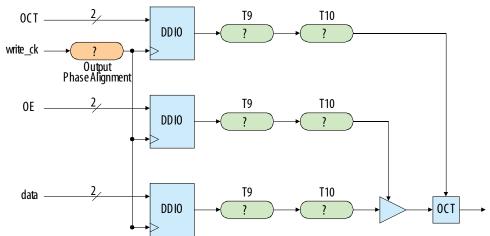

The write datapath passes write data from the memory controller to the I/O. The write data valid signal from the memory controller generates the output enable signal to control the output buffer. For memory protocols with a bidirectional data bus, it also generates the dynamic termination control signal, which selects between series (output mode) and parallel (input mode) termination.

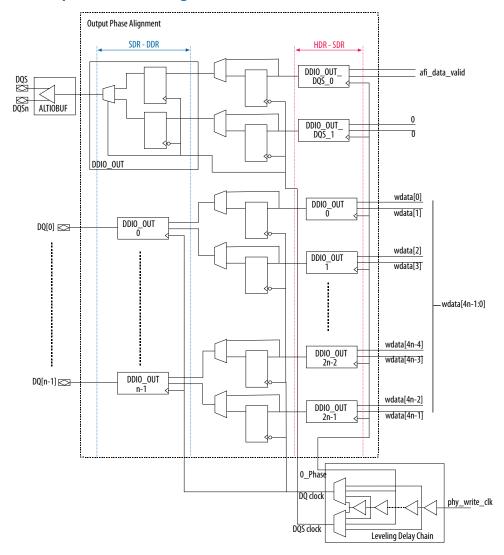

The figure below illustrates a simplified write datapath of a typical half-rate interface. The full-rate DQS write clock is sent to a DDIO\_OUT cell. The output of DDIO\_OUT feeds an output buffer which creates a pair of pseudo differential clocks that connects to the memory. In full-rate mode, only the SDR-DDR portion of the path is used; in half-rate mode, the HDR-SDR circuitry is also required. The use of DDIO\_OUT in both the output strobe and output data generation path ensures that their timing characteristics are as similar as possible. The

<variation\_name>\_pin\_assignments.tcl script automatically specifies the logic

option that associates all data pins to the output strobe pin. The Fitter treats the pins

as a DQS/DQ pin group.

Figure 3. Write Datapath

# 1.5.1. Leveling Circuitry

Leveling circuitry is dedicated I/O circuitry to provide calibration support for fly-by address and command networks. For DDR3, leveling is always invoked, whether the interface targets a DIMM or a single component. For DDR3 implementations at higher frequencies, a fly-by topology is recommended for optimal performance. For DDR2, leveling circuitry is invoked automatically for frequencies above 240 MHz; no leveling is used for frequencies below 240 MHz.

For DDR2 at frequencies below 240 MHz, you should use a tree-style layout. For frequencies above 240 MHz, you can choose either a leveled or balanced-T or Y topology, as the leveled PHY calibrates to either implementation. Regardless of protocol, for devices without a levelling block—such as Arria II GZ, Arria V, and Cyclone V—a balanced-T PCB topology for address/command/clock must be used because fly-by topology is not supported.

For details about leveling delay chains, consult the memory interfaces hardware section of the device handbook for your FPGA.

The following figure shows the write datapath for a leveling interface. The full-rate PLL output clock <code>phy\_write\_clk</code> goes to a leveling delay chain block which generates all other periphery clocks that are needed. The data signals that generate DQ and DQS signals pass to an output phase alignment block. The output phase alignment block feeds an output buffer which creates a pair of pseudo differential clocks that connect to the memory. In full-rate designs, only the SDR-DDR portion of the path is used; in half-rate mode, the HDR-SDR circuitry is also required. The use of DDIO\_OUT in both the output strobe and output data generation paths ensures that their timing characteristics are as similar as possible. The

<variation\_name>\_pin\_assignments.tcl script automatically specifies the logic

option that associates all data pins to the output strobe pin. The Quartus Prime Fitter

treats the pins as a DQS/DQ pin group.

Figure 4. Write Datapath for a Leveling Interface

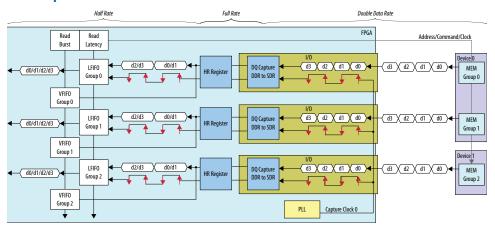

# 1.6. Read Datapath

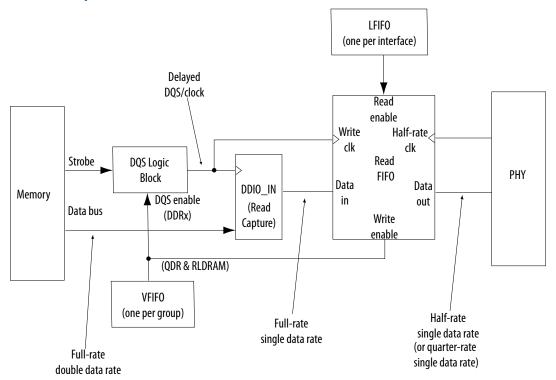

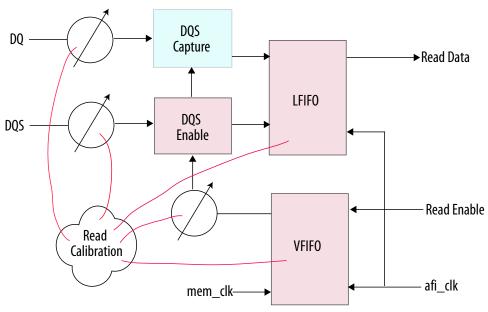

The read datapath passes read data from memory to the PHY. The following figure shows the blocks and flow in the read datapath.

For all protocols, the DQS logic block delays the strobe by 90 degrees to center-align the rising strobe edge within the data window. For DDR2, DDR3, and LPDDR2 protocols, the logic block also performs strobe gating, holding the DQS enable signal high for the entire period that data is received. One DQS logic block exists for each data group.

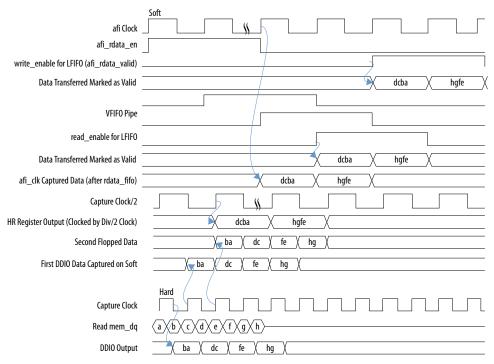

One VFIFO buffer exists for each data group. For DDR2, DDR3, and LPDDR2 protocols, the VFIFO buffer generates the DQS enable signal, which is delayed (by an amount determined during calibration) to align with the incoming DQS signal. For QDR and RLDRAM protocols, the output of the VFIFO buffer serves as the write enable signal for the Read FIFO buffer, signaling when to begin capturing data.

DDIO\_IN receives data from memory at double-data rate and passes data on to the Read FIFO buffer at single-data rate.

The Read FIFO buffer temporarily holds data read from memory; one Read FIFO buffer exists for each data group. For half-rate interfaces, the Read FIFO buffer converts the full-rate, single data-rate input to a half-rate, single data-rate output which is then passed to the PHY core logic. In the case of a quarter-rate interface, soft logic in the PHY performs an additional conversion from half-rate single data rate to quarter-rate single data rate.

One LFIFO buffer exists for each memory interface; the LFIFO buffer generates the read enable signal for all Read FIFO blocks in an interface. The read enable signal is asserted when the Read FIFO blocks have buffered sufficient data from the memory to be read. The timing of the read enable signal is determined during calibration.

Figure 5. Read Datapath

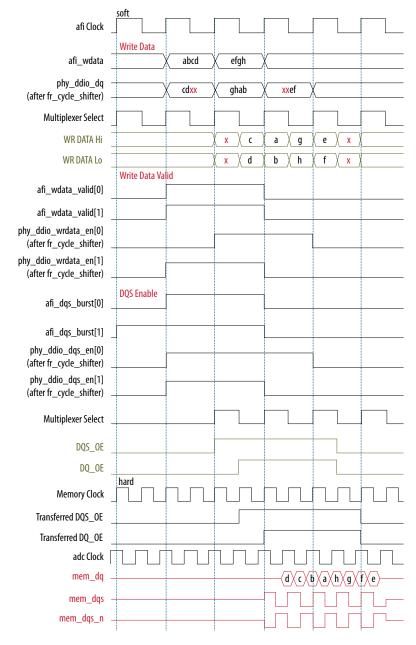

# 1.7. Sequencer

The sequencer initializes and calibrates the external memory interface. Depending on the combination of protocol and IP architecture in your external memory interface, you may have either an RTL-based sequencer or a Nios<sup>®</sup> II-based sequencer.

683841 | 2023.03.06

RTL-based sequencer implementations and Nios II-based sequencer implementations can have different pin requirements. You may not be able to migrate from an RTL-based sequencer to a Nios II-based sequencer and maintain the same pinout.

For information on sequencer support for different protocol-architecture combinations, refer to *Introduction to Intel FPGA Memory Solutions* in Volume 1 of this handbook. For information on pin planning, refer to *Planning Pin and FPGA Resources* in Volume 2 of this handbook.

#### **Related Information**

- Protocol Support Matrix

- Planning Pin and FPGA Resources

# 1.7.1. Nios II-Based Sequencer

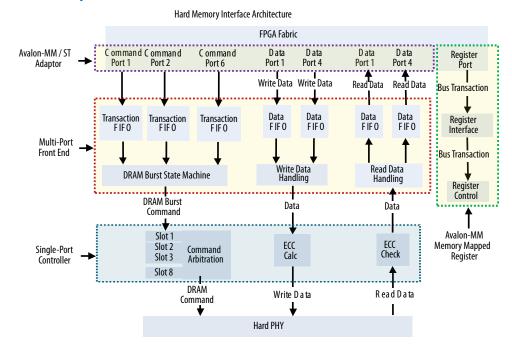

The DDR2, DDR3, and LPDDR2 controllers with UniPHY employ a Nios II-based sequencer that is parameterizable and is dynamically generated at run time. The Nios II-based sequencer is also available with the QDR II and RLDRAM II controllers.

# 1.7.1.1. Nios II-based Sequencer Function

The sequencer enables high-frequency memory interface operation by calibrating the interface to compensate for variations in setup and hold requirements caused by transmission delays.

UniPHY converts the double-data rate interface of high-speed memory devices to a full-rate or half-rate interface for use within an FPGA. To compensate for slight variations in data transmission to and from the memory device, double-data rate is usually center-aligned with its strobe signal; nonetheless, at high speeds, slight variations in delay can result in setup or hold time violations. The sequencer implements a calibration algorithm to determine the combination of delay and phase settings necessary to maintain center-alignment of data and clock signals, even in the presence of significant delay variations. Programmable delay chains in the FPGA I/Os then implement the calculated delays to ensure that data remains centered. Calibration also applies settings to the FIFO buffers within the PHY to minimize latency and ensures that the read valid signal is generated at the appropriate time.

When calibration is completed, the sequencer returns control to the memory controller.

For more information about calibration, refer to *UniPHY Calibration Stages*, in this chapter.

#### **Related Information**

UniPHY Calibration Stages on page 50

# 1.7.1.2. Nios II-based Sequencer Architecture

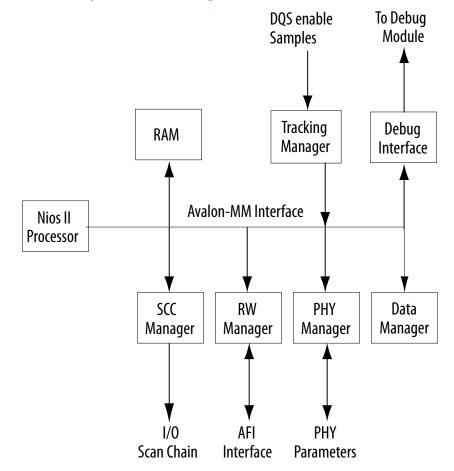

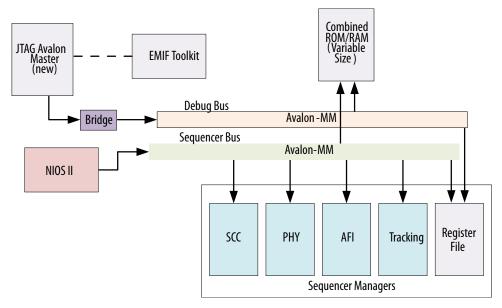

The sequencer is composed of a Nios II processor and a series of hardware-based component managers, connected together by an Avalon® bus. The Nios II processor performs the high-level algorithmic operations of calibration, while the component managers handle the lower-level timing, memory protocol, and bit-manipulation operations.

The high-level calibration algorithms are specified in C code, which is compiled into Nios II code that resides in the FPGA RAM blocks. The debug interface provides a mechanism for interacting with the various managers and for tracking the progress of the calibration algorithm, and can be useful for debugging problems that arise within the PHY. The various managers are specified in RTL and implement operations that would be slow or inefficient if implemented in software.

Figure 6. NIOS II-based Sequencer Block Diagram

The C code that defines the calibration routines is available for your reference in the  $\c$ name>\_s0\_software subdirectory. Intel recommends that you do not modify this C code.

#### 1.7.1.3. Nios II-based Sequencer SCC Manager

The scan chain control (SCC) manager allows the sequencer to set various delays and phases on the I/Os that make up the memory interface. The latest Intel device families provide dynamic delay chains on input, output, and output enable paths which can be reconfigured at runtime. The SCC manager provides the calibration routines access to these chains to add delay on incoming and outgoing signals. A master on the Avalon-MM interface may require the maximum allowed delay setting on input and output paths, and may set a particular delay value in this range to apply to the paths.

The SCC manager implements the Avalon-MM interface and the storage mechanism for all input, output, and phase settings. It contains circuitry that configures a DQ- or DQS-configuration block. The Nios II processor may set delay, phases, or register settings; the sequencer scans the settings serially to the appropriate DQ or DQS configuration block.

# 1.7.1.4. Nios II-based Sequencer RW Manager

The read-write (RW) manager encapsulates the protocol to read and write to the memory device through the Altera PHY Interface (AFI). It provides a buffer that stores the data to be sent to and read from memory, and provides the following commands:

- Write configuration—configures the memory for use. Sets up burst lengths, read and write latencies, and other device specific parameters.

- Refresh—initiates a refresh operation at the DRAM. The command does not exist

on SRAM devices. The sequencer also provides a register that determines whether

the RW manager automatically generates refresh signals.

- Enable or disable multi-purpose register (MPR)—for memory devices with a special register that contains calibration specific patterns that you can read, this command enables or disables access to the register.

- Activate row—for memory devices that have both rows and columns, this

command activates a specific row. Subsequent reads and writes operate on this

specific row.

- Precharge—closes a row before you can access a new row.

- Write or read burst—writes or reads a burst length of data.

- Write guaranteed—writes with a special mode where the memory holds address

and data lines constant. Intel guarantees this type of write to work in the presence

of skew, but constrains to write the same data across the entire burst length.

- Write and read back-to-back—performs back-to-back writes or reads to adjacent banks. Most memory devices have strict timing constraints on subsequent accesses to the same bank, thus back-to-back writes and reads have to reference different banks.

- Protocol-specific initialization—a protocol-specific command required by the initialization sequence.

#### 1.7.1.5. Nios II-based Sequencer PHY Manager

The PHY Manager provides access to the PHY for calibration, and passes relevant calibration results to the PHY. For example, the PHY Manager sets the VFIFO and LFIFO buffer parameters resulting from calibration, signals the PHY when the memory initialization sequence finishes, and reports the pass/fail status of calibration.

# 1.7.1.6. Nios II-based Sequencer Data Manager

The Data Manager stores parameterization-specific data in RAM, for the software to query.

# 1.7.1.7. Nios II-based Sequencer Tracking Manager

The Tracking Manager detects the effects of voltage and temperature variations that can occur on the memory device over time resulting in reduced margins, and adjusts the DQS enable delay as necessary to maintain adequate operating margins.

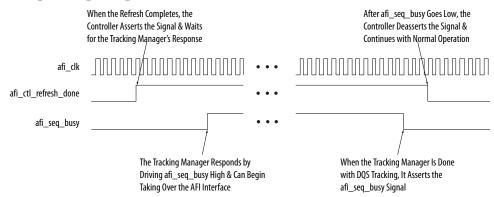

The Tracking Manager briefly assumes control of the AFI interface after each memory refresh cycle, issuing a read routine to the RW Manager, and then sampling the DQS tracking. Ideally, the falling edge of the DQS enable signal would align to the last rising edge of the raw DQS signal from the memory device. The Tracking Manager determines whether the DQS enable signal is leading or trailing the raw DQS signal.

Each time a refresh occurs, the Tracking Manager takes a sample of the raw DQS signal; any adjustments of the DQS enable signal occur only after sufficient samples of raw DQS have been taken. When the Tracking Manager determines that the DQS enable signal is either leading or lagging the raw DQS signal, it adjusts the DQS enable appropriately.

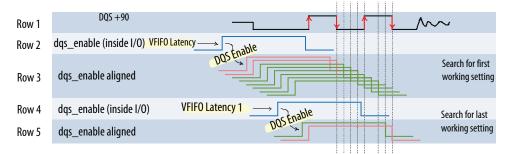

The following figure shows the Tracking manager signals.

## Figure 7. Tracking Manager Signals

Some notes on Tracking Manager operation:

- The time taken by the Tracking Manager is arbitrary; if the period taken exceeds the refresh period, the Tracking Manager handles memory refresh.

- afi\_seq\_busy should go high fewer than 10 clock cycles after afi\_ctl\_refresh\_done or afi\_ctl\_long\_idle is asserted.

- afi\_refresh\_done should deassert fewer than 10 clock cycles after afi seq busy deasserts.

- afi\_ctl\_long\_idle causes the Tracking Manager to execute an algorithm different than periodic refresh; use afi\_ctl\_long\_idle when a long session has elapsed without a periodic refresh.

- The Tracking Manager is instantiated into the sequencer system when DQS Tracking is turned on.

Table 1. Configurations Supporting DQS Tracking

| Device Family                      | Protocol             | Memory Clock Frequency                                       |

|------------------------------------|----------------------|--------------------------------------------------------------|

| Arria V (GX/GT/SX/ST) , Cyclone V  | LPDDR2 (single rank) | All frequencies.                                             |

| Arria V (GX/GT/SX/ST)              | DDR3 (single rank)   | 450 MHz or higher for speed grade 5, or higher than 534 MHz. |

| Arria V GZ, Stratix V (E/GS/GT/GX) |                      | 750 MHz or higher.                                           |

• If you do not want to use DQS tracking, you can disable it (at your own risk), by opening the Verilog file <variant\_name</pre>>\_if0\_c0.v in an editor, and changing the value of the USE\_DQS\_TRACKING parameter from 1 to 0.

# 1.7.1.8. Nios II-based Sequencer Processor

The Nios II processor manages the calibration algorithm; the Nios II processor is unavailable after calibration is completed.

The same calibration algorithm supports all device families, with some differences. The following sections describe the calibration algorithm for DDR3 SDRAM on Stratix III devices. Calibration algorithms for other protocols and families are a subset and significant differences are pointed out when necessary. As the algorithm is fully contained in the software of the sequencer (in the C code) enabling and disabling specific steps involves turning flags on and off.

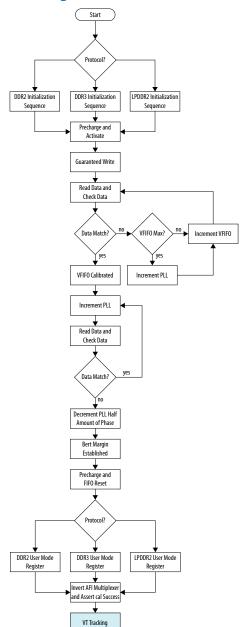

Calibration consists of the following stages:

- Initialize memory.

- Calibrate read datapath.

- Calibrate write datapath.

- Run diagnostics.

# 1.7.1.9. Nios II-based Sequencer Calibration and Diagnostics

Calibration must initialize all memory devices before they can operate properly. The sequencer performs this memory initialization stage when it takes control of the PHY at startup.

Calibrating the read datapath comprises the following steps:

- Calibrate DQS enable cycle and phase.

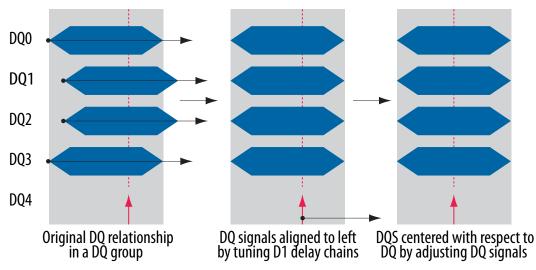

- Perform read per-bit deskew to center the strobe signal within data valid window.

- Reduce LFIFO latency.

Calibrating the write datapath involves the following steps:

- Center align DQS with respect to DQ.

- Align DQS with mem\_clk.

The sequencer estimates the read and write margins under noisy conditions, by sweeping input and output DQ and DQS delays to determine the size of the data valid windows on the input and output sides. The sequencer stores this diagnostic information in the local memory and you can access it through the debugging interface.

When the diagnostic test finishes, control of the PHY interface passes back to the controller and the sequencer issues a pass or fail signal.

#### **Related Information**

External Memory Interface Debug Toolkit on page 272

# 1.7.2. RTL-based Sequencer

The RTL-based sequencer is available for QDR II and RLDRAM II interfaces, on supported device families other than Arria V. The RTL sequencer is a state machine that processes the calibration algorithm.

The sequencer assumes control of the interface at reset (whether at initial startup or when the IP is reset) and maintains control throughout the calibration process. The sequencer relinquishes control to the memory controller only after successful calibration. The following tables list the major states in the RTL-based sequencer.

**Table 2.** Sequencer States

| RTL-based Sequencer State    | Description                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                        | Remain in this state until reset is released.                                                                                                                                                                                                                                                                                                                |

| LOAD_INIT                    | Load any initialization values for simulation purposes.                                                                                                                                                                                                                                                                                                      |

| STABLE                       | Wait until the memory device is stable.                                                                                                                                                                                                                                                                                                                      |

| WRITE_ZERO                   | Issue write command to address 0.                                                                                                                                                                                                                                                                                                                            |