# **AN 556: Using the Design Security Features in Intel FPGAs**

Version: **2021.05.21**

ID: 683269

# **Contents**

| Usin | $oldsymbol{\mathsf{Ig}}$ the Design Security Features in Intel $^oldsymbol{\mathsf{g}}$ FPGAs | 3  |

|------|-----------------------------------------------------------------------------------------------|----|

|      | Overview of the Design Security Feature                                                       | 4  |

|      | Security Encryption Algorithm                                                                 |    |

|      | Non-Volatile and Volatile Key Storage                                                         |    |

|      | Key Programming                                                                               |    |

|      | Intel Arria 10 and Intel Cyclone 10 GX Qcrypt Security Tool                                   | 8  |

|      | Hardware and Software Requirements                                                            | 11 |

|      | Hardware Requirements                                                                         | 11 |

|      | Software Requirements                                                                         | 12 |

|      | Steps for Implementing a Secure Configuration Flow                                            | 12 |

|      | Step 1: Generating .ekp File and Encrypting Configuration File                                | 13 |

|      | Step 2a: Programming Volatile Key into the FPGAs                                              | 18 |

|      | Step 2b: Programming Non-Volatile Key into the FPGAs                                          | 18 |

|      | Step 3: Configuring the 40-nm, 28-nm, or 20-nm FPGAs with Encrypted                           |    |

|      | Configuration Data                                                                            |    |

|      | Steps to Enable Tamper-Protection Bit Programming                                             |    |

|      | Supported Configuration Schemes                                                               |    |

|      | Security Mode Verification                                                                    |    |

|      | Verification During JTAG Secure Mode                                                          |    |

|      | Serial Flash Loader Support with Encryption Enabled                                           |    |

|      | Serial Flash Loader Support with Encryption Enabled for Single FPGA Device Chain              |    |

|      | JTAG Secure Mode for 28-nm and 20-nm FPGAs                                                    |    |

|      | Internal JTAG Interface                                                                       |    |

|      | Design Example for JTAG Secure Mode                                                           |    |

|      | Document Revision History for AN 556: Using the Design Security Features in Intel FPGAs       | 39 |

# Using the Design Security Features in Intel® FPGAs

This application note describes how you can use the design security features in Intel® 40-, 28- and 20-nm FPGAs to protect your designs against unauthorized copying, reverse engineering, and tampering of your configuration files. This application note provides the hardware and software requirements for the 40-, 28- and 20-nm FPGAs design security features. This application note also provides steps for implementing secure configuration flow.

Note:

This application note uses the term "40-nm", "28-nm" or "20-nm" FPGAs. The following table lists the supported FPGAs and its applicable devices.

#### **Table 1. Supported FPGAs**

| FPGA  | Devices                                           |

|-------|---------------------------------------------------|

| 40 nm | Arria <sup>®</sup> II and Stratix <sup>®</sup> IV |

| 28 nm | Arria V, Cyclone <sup>®</sup> V, and Stratix V    |

| 20 nm | Intel Arria 10 and Intel Cyclone 10 GX            |

In the commercial and military environments, design security is an important consideration for digital designers. As FPGAs start to play a role in larger and more critical system components, it is important to protect the designs from unauthorized copying, reverse engineering, and tampering. Intel FPGAs address these concerns by encrypting their configuration bitstreams with the 256-bit Advanced Encryption Standard (AES) algorithm.

#### Table 2. AES Modes in Supported Intel FPGAs

| FPGA  | AES Mode                                              |

|-------|-------------------------------------------------------|

| 40 nm | Counter Mode (CTR)                                    |

| 28 nm | Cipher-block chaining (CBC)                           |

| 20 nm | CTR and keyed-hash message authentication code (HMAC) |

During device operation, FPGAs store configuration data in SRAM configuration cells. Because SRAM memory is volatile, the SRAM cells must be loaded with configuration data each time the device powers up. Configuration data is typically sent from an external memory source, such as a flash memory or a configuration device, to the FPGA. It is possible to intercept the configuration data when it is being sent from the memory source to the FPGA. If the configuration data were not encrypted, you could use the intercepted configuration data to configure another FPGA.

Intel FPGAs offer both volatile and non-volatile key storage. The key is stored in FPGAs when using the design security feature. Depending on the security mode, you can configure the FPGAs with a configuration file that is encrypted with the same key, or for board testing, configure with a normal configuration file.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

The design security feature is available when configuring the FPGAs with fast passive parallel (FPP) configuration scheme with an external host (such as a MAX<sup>®</sup> II or MAX V device or microprocessor) or when using active serial (AS) or passive serial (PS) configuration schemes.

#### **Related Information**

- AN 680: Product Security Features for Altera Devices

Provides more information about the product security features.

- Configuration, Design Security, and Remote System Upgrades in Arria II Devices Provides more information about the design security for Arria II devices.

- Configuration, Design Security, and Remote System Upgrades in Stratix IV Devices

Provides more information about the design security for Stratix IV devices.

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Provides more information about the design security for Arria V devices.

- Configuration, Design Security, and Remote System Upgrades in Cyclone V Devices

Provides more information about the design security for Cyclone V devices.

- Configuration, Design Security, and Remote System Upgrades in Stratix V Devices

Provides more information about the design security for Stratix V devices.

- Configuration, Design Security, and Remote System Upgrades in Intel Arria 10 Devices

Provides more information about the design security for Intel Arria 10 devices.

- Configuration, Design Security, and Remote System Upgrades in Intel Cyclone 10 GX Devices

- Provides more information about the design security for Intel Cyclone 10 devices.

- Configuration Design Security in Intel MAX 10 FPGA

# **Overview of the Design Security Feature**

The design security feature for Intel FPGAs protects against unauthorized copying , reverse engineering, and tampering. The following table lists some of the design approaches to make the solution secure.

The 20-nm FPGAs have additional security features that you can enable by burning a fuse, or by setting an option bit in the configuration bit-stream by using the standalone Qcrypt tool or the Intel Quartus<sup>®</sup> Prime Convert Programming File tool. Tamper-protection bit and JTAG Secure mode can be enabled separately in 20-nm FPGAs only.

#### Table 3. Design Security Approach for 40-nm and 28-nm FPGAs

Caution:

Enabling the tamper-protection bit disables the test mode in 40-nm and 28-nm FPGAs. Disabling the test mode is irreversible and prevents Intel from carrying out failure analysis. To enable the tamper protection bit, refer to the *Steps to Enable Tamper-Protection Bit Programming* section.

| Design Security Element | 40-nm FPGA                                                                                                                                                                                                                                                                                                                                                                                        | 28-nm FPGA <sup>(1)</sup>                                                                                                                           |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Non-Volatile key        | The non-volatile key is securely stored in fuses within the device. Proprietary security features make it difficult to determine this key.                                                                                                                                                                                                                                                        |                                                                                                                                                     |  |

| Volatile Key            |                                                                                                                                                                                                                                                                                                                                                                                                   | The volatile key is securely stored in battery-backed RAM within the device. Proprietary security features make it difficult to determine this key. |  |

| Key Generation          | Two user provided 256-bit strings are processed to generate a 256-bit key that is programmed into the device.                                                                                                                                                                                                                                                                                     | A user provided 256-bit key is processed by a one-way function before being programmed into the device.                                             |  |

| Key Choice              | User only set either 1 security key type (non-volatile key or volatile key) into the device.                                                                                                                                                                                                                                                                                                      |                                                                                                                                                     |  |

| Tamper Protection Mode  | Tamper protection mode prevents the FPGA from being loaded with an unencrypted configuration file. When you enable this mode, the FPGA can only be loaded with a configuration that has been encrypted with your key. Unencrypted configurations and configurations encrypted with the wrong key result in a configuration failure. You can enable this mode by setting a fuse within the device. |                                                                                                                                                     |  |

| Configuration Readback  | These devices do not support a configuration readback feature which makes readback of your unencrypted configuration data infeasible.                                                                                                                                                                                                                                                             |                                                                                                                                                     |  |

### Table 4. Design Security Approach for 20-nm FPGAs

| Design Security<br>Element | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Non-Volatile key           | The non-volatile key is securely stored in fuses within the device. Proprietary security features make it difficult to determine this key.                                                                                                                                                                                                                                                        |

| Volatile Key               | The volatile key is securely stored in battery-backed RAM within the device. Proprietary security features make it difficult to determine this key.                                                                                                                                                                                                                                               |

| Key Generation             | A user provided 256-bit key is processed by a one-way function before being programmed into the device.                                                                                                                                                                                                                                                                                           |

| Key Choice                 | Both volatile and non-volatile key can exist in a device. User can choose which key to use by setting the option bits in encrypted configuration file through the Convert Programming File tool or the Qcrypt tool.                                                                                                                                                                               |

| Tamper Protection<br>Mode  | Tamper protection mode prevents the FPGA from being loaded with an unencrypted configuration file. When you enable this mode, the FPGA can only be loaded with a configuration that has been encrypted with your key. Unencrypted configurations and configurations encrypted with the wrong key result in a configuration failure. You can enable this mode by setting a fuse within the device. |

|                            | continued                                                                                                                                                                                                                                                                                                                                                                                         |

<sup>(1)</sup> When you enable the tamper-protection bit in 28-nm FPGAs, the device is in the JTAG secure mode.

| Design Security<br>Element | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration<br>Readback  | These devices do not support a configuration readback feature. From a security perspective, this makes readback of your unencrypted configuration data infeasible.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Security Key Control       | By using different JTAG instructions and the security option in the Qcrypt tool, you have the flexibility to permanently or temporarily disable the use of the non-volatile or volatile key. You can also choose to lock the volatile key to prevent it from being overwritten or reprogrammed.                                                                                                                                                                                                                                                                                                    |

| JTAG Access Control        | You can enable various levels of JTAG access control by setting the OTP fuses or option bits in the configuration file using the Qcrypt tool:  1. Force full configuration or partial configuration to be done through HPS only.  2. Bypass external JTAG pin or HPS JTAG. This feature disables external JTAG or HPS JTAG access, but can be unlocked through internal core access. (2)  3. Disable all AES key related JTAG instructions from external JTAG pins.  4. Allows only a limited set of mandatory JTAG instruction to be accessed through external JTAG, similar to JTAG Secure mode. |

Note:

For additional details on these and other security features, contact Intel FPGA Technical Support.

#### **Related Information**

- Intel Arria 10 and Intel Cyclone 10 GX Qcrypt Security Tool on page 8

- Steps to Enable Tamper-Protection Bit Programming on page 23

- Steps for Implementing a Secure Configuration Flow on page 12

- JTAG Secure Mode for 28-nm and 20-nm FPGAs on page 30

# **Security Encryption Algorithm**

Intel FPGAs have a dedicated AES decryptor block than can decrypt configuration bitstreams prior to configuring the FPGA device. The 28-nm FPGAs use the AES block in CBC mode, while the 40-nm and 20-nm FPGAs use the AES block in CTR mode. In addition, the 20nm devices implement techniques to mitigate side-channel attacks against the standard NIST CTR mode of encryption. If the security feature is not used, the AES decryptor is bypassed. The FPGAs AES implementation is validated as conforming to the Federal Information Processing Standards FIPS-197.

#### **Related Information**

### Computer Security Resource Center (CSRC)

For the AES algorithm, refer to the Federal Information Processing Standards Publication FIPS-197 or the AES Algorithm (Rijndael) Information. For the AES validation for FPGAs, refer to the Advanced Encryption Standard Algorithm Validation List.

### Non-Volatile and Volatile Key Storage

Intel FPGAs offer both volatile and non-volatile key storage. The volatile key storage registers are reprogrammable and erasable. The contents of the key registers are retained between power-cycles with a coin-cell battery. Non-volatile key registers are fuse-based and are one-time programmable.

<sup>(2)</sup> Intel Cyclone 10 GX does not support force full configuration or partial configuration through HPS and HPS JTAG Bypass.

Note: Examples of lithium coin-cell type batteries that are used for volatile key storage purposes are BR1220 (-30°C to 80°C) and BR2477A (-40°C to 125°C).

#### Table 5. Volatile and Non-Volatile Key Comparison

| Option                                | Volatile Key                                               | Non-Volatile Key                           |

|---------------------------------------|------------------------------------------------------------|--------------------------------------------|

| Key Length                            | 256 bits                                                   | 256 bits                                   |

| Key Programmability                   | Reprogrammable and erasable key                            | One-time programmable key                  |

| External Battery                      | Required                                                   | Not required                               |

| Key Programming Method <sup>(3)</sup> | On-board                                                   | Both on-board and off-board <sup>(4)</sup> |

| Design Protection <sup>(5)</sup>      | Secure against copying, reverse engineering, and tampering |                                            |

### **Key Programming**

#### Table 6. Key Programming Methods

| <b>Programming Procedure</b> | Method      | Programming Tool/Support                                                                                                                                                                                                    |

|------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-Board Programming         | Prototyping | Intel FPGA Ethernet Cable <sup>(6)</sup> , JTAG Technologies <sup>(7)</sup> , Intel FPGA Parallel Port Cable <sup>(8)</sup> , Intel FPGA Download Cable <sup>(9)</sup> , and Intel FPGA Download Cable II <sup>(10)</sup> . |

|                              | Production  | JTAG Technologies*                                                                                                                                                                                                          |

| Off-Board Programming        | Prototyping | System General*                                                                                                                                                                                                             |

|                              | Production  | System General                                                                                                                                                                                                              |

<sup>(10)</sup> Intel FPGA Download Cable II supports both volatile and non-volatile key programming.

<sup>(3)</sup> Key programming is carried out through JTAG interface. You need to use valid MSEL pin settings for the JTAG interface.

<sup>(4)</sup> Programming the non-volatile key fuses uses the standard voltage sources used by the FPGA during normal operation. No additional voltage rails are necessary for programming non-volatile key.

<sup>(5)</sup> Volatile key tamper-protection is only available for Arria II, Arria V, Cyclone V, Stratix V, Intel Arria 10, and Intel Cyclone 10 GX devices.

<sup>(6)</sup> Intel FPGA Ethernet Cable supports both volatile and non-volatile key programming.

<sup>(7)</sup> JTAG Technologies\* supports both volatile and non-volatile key programming.

<sup>(8)</sup> Intel FPGA Parallel Port Cable supports only volatile key programming.

<sup>(9)</sup> Intel FPGA Download Cable support only volatile key programming except in 20-nm FPGAs, where it supports both volatile and non-volatile key programming.

683269 | 2021.05.21

Key programming uses the following definitions:

- On-board: procedure in which the device is programmed on your board

- Off-board: procedure in which the device is programmed on a separate programming system

- Prototyping: method initially used to verify proper operation of a particular method

- **Production:** method used for large-volume production

Note:

For other third-party non-volatile key programming, you must regulate the JTAG  $\tiny TCK$  pulse width (period) for proper polyfuse programming, as listed in Table 10 on page 11.

#### **Related Information**

Intel FPGA Technical Support

Provides information about programming support.

### Intel Arria 10 and Intel Cyclone 10 GX Qcrypt Security Tool

The Qcrypt tool is a stand-alone encryption tool for encrypting and decrypting Intel Arria 10 and Intel Cyclone 10 GX FPGA configuration bit-stream files. The Qcrypt tool can also be used to encrypt HPS boot images through a script. Different kinds of security settings that are currently not accessible from the Intel Quartus Prime graphical user interface can be set through the Qcrypt tool.

The Qcrypt tool encrypts and decrypts raw binary files (.rbf) only and not other configuration files, such as .sof and .pof files. Throughout the encryption flow, the Qcrypt tool generates an authentication tag while encrypting the .rbf file. The authentication tag prevents any modification or tampering of the configuration bitstream. Besides encryption and decryption, the Qcrypt tool allows you to enable and set various security features and settings. By incorporating security features and settings into the .rbf file, you have the flexibility to use different kinds of security features on Intel Arria 10 and Intel Cyclone 10 GX devices without permanently burning the security fuses. To generate the .ekp file or encrypted configuration file other than .rbf, you have to use the Intel Quartus Prime Convert Programming File tool.

Note:

The Qcrypt tool is not license-protected and can be used by all Intel Quartus Prime software user.

#### **Related Information**

- Overview of the Design Security Feature on page 4

- Steps to Enable Tamper-Protection Bit Programming on page 23

- Steps for Implementing a Secure Configuration Flow on page 12

- JTAG Secure Mode for 28-nm and 20-nm FPGAs on page 30

- Qcrypt Tool Options on page 9

Provides more information about Ocrypt tool features.

- AN 759: Intel Arria 10 SoC Secure Boot User Guide Provides more information about encrypting HPS boot images.

# **Using Qcrypt Tool**

You can use the following command to encrypt and decrypt .rbf files. This command is the only way to set the advanced security options.

qcrypt [options] <input\_file.rbf> <output\_file.rbf>

# **Qcrypt Tool Options**

### **Table 7.** Basic Options in Qcrypt Tool

| Basic Option                           | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| encrypt                                | Encrypts input_file.rbf with default behavior.                                                                                                                                                                                                                                                                                                                                                                                    |

| decrypt                                | Decrypts input_file.rbf to obtain the original bit-stream. The decrypted .rbf is not the same as original bit-stream if you had previously enabled any security options. You must explicitly reset these security options to level 0 if you want the decrypted .rbf to match the original preencrypted .rbf. Note that there are minor differences between the original and decrypted .rbf files. The differences can be ignored. |

| keyfile= <key_file></key_file>         | Default name for this key file is keyfile.key. This option allows you to specify an alternate name for the keyfile.key. The key file is located in the current project directory where the input_file.rbf is also stored. Refer example key file in Generating Single-Device .ekp File and Encrypting Configuration File using Intel Quartus Prime Software on page 14.                                                           |

| keyname= <key_name></key_name>         | Specify a named key to use from the key file. By default, the tool uses the first key from the key file.                                                                                                                                                                                                                                                                                                                          |

| keystore= <types key="" of=""></types> | Specify which security key to be use:  otp (non-volatile key)  battery (volatile key)  One-time programmable (otp) is the default value.                                                                                                                                                                                                                                                                                          |

| iv= <hex_value></hex_value>            | Optional seed value for creating a non-random initialization vector (IV). By default, an .rbf generates a different encrypted .rbf every time it is encrypted. This option allows you to specify a seed value to ensure the same encrypted .rbf is generated when using sameiv value. HEX_VALUE can be any arbitrary 32-bit hexadecimal value.                                                                                    |

# **Table 8.** Security Options in Qcrypt Tool

| Security Option                         | Descriptions                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lockto= <file_name.qlk></file_name.qlk> | Locks authentication to corresponding prior base bitstream.                                                                                                                                                                                                                                                                                                                   |

|                                         | The .qlk file is automatically created when a base configuration file, such as a CvP core image bitstream, is encrypted. Use this option when you want a follow-on core CvP or partial reconfiguration image to be usable only with that base configuration. This prevents a follow-on bitstream from being loaded over a wrong (but otherwise authenticated) base bitstream. |

| no-lockto                               | Overrides any mandatorylockto requirement                                                                                                                                                                                                                                                                                                                                     |

| epof-only=[0:3]                         | Only allow encrypted and authenticated bit-streams to be used for external configuration.                                                                                                                                                                                                                                                                                     |

| no-config=[0:3]                         | Disables configuration from external pins. With this option set, configuration can only be controlled by the internal HPS.  Note: This security option is not supported in Intel Cyclone 10 GX.                                                                                                                                                                               |

|                                         | Note: This security option is not supported in Intel Cyclone 10 GX.                                                                                                                                                                                                                                                                                                           |

| no-pr=[0:3]                             | Disables external partial-configuration.                                                                                                                                                                                                                                                                                                                                      |

|                                         | continued                                                                                                                                                                                                                                                                                                                                                                     |

| Security Option        | Descriptions                                                                                                        |

|------------------------|---------------------------------------------------------------------------------------------------------------------|

| no-jtag-key=[0:3]      | Disables key-related JTAG instructions.                                                                             |

| no-jtag-ext=[0:3]      | Enables JTAG Secure mode.                                                                                           |

| no-jtag=[0:3]          | Forces the external JTAG pins into BYPASS mode.                                                                     |

| no-hps-jtag=[0:3]      | Forces the internal HPS JTAG into BYPASS mode.  Note: This security option is not supported in Intel Cyclone 10 GX. |

| no-otp-key=[0:3]       | Disables use of the non-volatile OTP fuse key.                                                                      |

| no-battery-key=[0:3]   | Disables use of the battery-backed key.                                                                             |

| lock-battery-key=[0:3] | Prevents the battery-backed volatile key from being changed or overwritten.                                         |

| secure=[2:3]           | Disables Test Mode <default=2>.</default=2>                                                                         |

#### **Related Information**

- Intel Arria 10 and Intel Cyclone 10 GX Qcrypt Security Tool on page 8

- AN 759: Intel Arria 10 SoC Secure Boot User Guide Provides more information about encrypting HPS boot images.

#### **Security Levels of Qcrypt Tool Security Option**

The Qcrypt tool allows the flexibility to determine the security level of the security options in Table 8 on page 9. You can choose the minimum or maximum requirement by specifying the level of security from 0 to 3.

**Table 9. Qcrypt Tool Security Option Security Levels**

| Security Level | Descriptions                                                                                                                                                                                                        |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | The security feature is not enabled unless by the corresponding OTP fuse.                                                                                                                                           |

| 1              | The security feature is enabled from the start of the current full- or partial-reconfiguration until the start of the next full configuration.                                                                      |

| 2              | The security feature is enabled until the next power-on-reset. Additionally, configuration does not proceed if any action normally prevented by the security feature has taken place since the last power-on-reset. |

| 3              | Configuration does not proceed unless the security feature has been permanently enabled by blowing the corresponding fuses in the device.                                                                           |

The security level of 2 provides a level of security almost as powerful as setting the corresponding OTP security fuse, but with some flexibility. For example, the use of JTAG may be required for manufacturing test or debug, but you may want to totally disable JTAG while a secured (encrypted) bit-stream is loaded in the device. Furthermore, you may not want to load a secured bit-stream into a device that had previously been probed with any kind of JTAG command.

Intel recommends that you use the strictest security level for each option that is consistent with your design requirements.

Note: You can find information on the Qcrypt tool by using the --help option.

# **Hardware and Software Requirements**

When using the design security feature, a volatile or non-volatile key is stored in the FPGA. The key must be programmed before the FPGA is configured with an encrypted configuration file.

# **Hardware Requirements**

The following table lists the specifications that you must follow for a successful key programming.

Table 10. Specifications for Key Programming

| Parameter           | Key Programming Mode         |              |  |  |

|---------------------|------------------------------|--------------|--|--|

|                     | Non-Volatile Key             | Volatile Key |  |  |

| TCK period          | 10 μs ± 1 μs <sup>(11)</sup> | _            |  |  |

| Ambient Temperature | 25°C ± 5°C                   | 25°C ± 5°C   |  |  |

| Voltage (VCCBAT)    | _                            | (12)         |  |  |

$V_{CCBAT}$  is a dedicated power supply for the volatile key storage and is not shared with other on-chip power supplies, such as  $V_{CCIO}$  or  $V_{CC}$ .  $V_{CCBAT}$  continuously supplies power to the volatile register regardless of the on-chip supply condition.

Note:

After power up, you must wait for the device to exit power-on reset (POR) before beginning the key programming. You may encounter verification error when programming the volatile Encryption Key Programming (.ekp) file if you have the VCCBAT pin tied to GND. The VCCBAT pin must be tied to the recommended  $V_{CCBAT}$  voltage provided in the respective device family pin connection guidelines for proper operation.

#### **Related Information**

- Device Datasheet for Arria II Devices

- Provides more information about JTAG, POR, and voltage specifications.

- DC and Switching Characteristics for Stratix IV Devices

Provides more information about JTAG, POR, and voltage specifications.

- Arria V Device Datasheet

Provides more information about JTAG, POR, and voltage specifications.

Cyclone V Device Datasheet

Provides more information about JTAG, POR, and voltage specifications.

• Stratix V Device Datasheet

Provides more information about JTAG, POR, and voltage specifications.

• Intel Arria 10 Device Datasheet

Provides more information about JTAG, POR, and voltage specifications.

<sup>(12)</sup> If you do not use the volatile key, refer to the respective device family pin connection guidelines for VCCBAT connection.

<sup>(11)</sup> Applies to 40-nm and 28-nm FPGAs only.

- Intel Cyclone 10 GX Device Datasheet

Provides more information about JTAG, POR, and voltage specifications.

- Stratix V E, GS, and GX Device Family Pin Connection Guidelines

- Stratix V GT Device Family Pin Connection Guidelines

- Arria V GT, GX, ST and SX Device Family Pin Connection Guidelines

- Arria V GZ Device Family Pin Connection Guidelines

- Stratix IV GX and E Device Family Pin Connection Guidelines

- Stratix IV GT Device Family Pin Connection Guidelines

- Arria II Device Family Pin Connection Guidelines

- Intel Arria 10 GX, GT, and SX Device Family Pin Connection Guidelines

# **Software Requirements**

#### Table 11. Supported Quartus Version for Intel FPGAs

You are required to use the supported Quartus software version below to enable the design security feature based on your FPGA type.

| Device                                                              | Supported Quartus Version                 |  |

|---------------------------------------------------------------------|-------------------------------------------|--|

| 40-nm FPGA                                                          | Quartus II software version 9.0 or later. |  |

| 28-nm FPGA Quartus II software version 11.0 or later.               |                                           |  |

| 20-nm FPGA Intel Quartus Prime software version 15.1 or later. (13) |                                           |  |

Note:

To enable the design security feature for Intel Quartus Prime Lite Edition, obtain a license file from Intel FPGA Technical Support.

#### **Related Information**

Intel FPGA Technical Support

# **Steps for Implementing a Secure Configuration Flow**

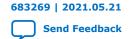

To implement a secure configuration flow, follow these steps:

1. Generate the .ekp file and encrypt the configuration data.

The Intel Quartus Prime configuration software always uses the user-defined 256-bit key to generate a key programming file and an encrypted configuration file. The encrypted configuration file is stored in an external memory, such as a flash memory or a configuration device. For details, refer to Step 1: Generating .ekp File and Encrypting Configuration File on page 13.

Note: For the 20-nm FPGAs, you can also encrypt an .rbf by using the standalone Qcrypt tool with extended security options.

2. Program the user-defined 256-bit key into the FPGAs.

<sup>(13)</sup> For 20-nm FPGAs, you can also enable the design security features by using the stand-alone Qcrypt tool available in the Intel Quartus Prime software.

For details, refer to Step 2a: Programming Volatile Key into the FPGAs on page 18 and Step 2b: Programming Non-Volatile Key into the FPGAs on page 18.

3. Configure the 40-nm, 28-nm or 20-nm FPGA device.

At power up, the external memory source sends the encrypted configuration file to the FPGA. The device uses the stored key to decrypt the file and to configure itself. For details about how to configure FPGAs with encrypted configuration data, refer to Step 3: Configuring the 40-nm, 28-nm, or 20-nm FPGAs with Encrypted Configuration Data on page 22.

#### Figure 1. Secure Configuration Flow

# Step 1: Generating .ekp File and Encrypting Configuration File

To use the design security feature in the FPGAs, you must encrypt your 20-nm design using the Qcrypt tool, or generate an **.ekp** file and encrypt your configuration files using the Intel Quartus Prime software. The key is not saved into any Intel Quartus Prime-generated configuration files and the actual 256-bit key is generated from the bit sequences.

To enable the design security feature, you can obtain a license file from Intel FPGA Technical Support.

The **.ekp** file has different formats, depending on the hardware and system used for programming. There are three file formats supported by the Intel Quartus Prime software:

- JAM Byte Code (.ibc) file

- JAM<sup>™</sup> Standard Test and Programming Language (STAPL) Format (.jam) file

- Serial Vector Format (.svf) file

Only the **.ekp** file type is generated automatically from the Intel Quartus Prime software. You must create the **.jam** and **.svf** files using the Intel Quartus Prime software if these files are required in the key programming. The Intel Quartus Prime software generates the JBC format of the **.ekp** file in the same project directory.

*Note:* Intel recommends that you keep the **.ekp** file confidential.

Use the **.ekp** file with the Intel FPGA Ethernet Cable communications cable or Intel FPGA Download Cable and the Intel Quartus Prime software. The Intel FPGA Ethernet Cable communications cable can support both volatile and non-volatile key

programming whereas the Intel FPGA Download Cable is used only for volatile key programming. The **.jam** file format is generally used with third-party programming vendors and JTAG programmer vendors. The **.svf** file format is used with JTAG programmer vendors.

# **Generating Single-Device .ekp File and Encrypting Configuration File using Intel Quartus Prime Software**

To generate a single device **.ekp** file and encrypt your configuration file, follow these steps:

- 1. Obtain a license file to enable the design security feature from Intel FPGA Technical Support.

- 2. Start the Intel Quartus Prime software.

- 3. On the Tools menu, click **License Setup**. The **Options** dialog box displays the **License Setup** options.

- 4. In the **License file** field, enter the location and name of the license file, or browse to and select the license file.

- 5. Click OK.

- 6. Compile your design with one of the following options:

- a. On the Processing menu, click Start Compilation.

- b. On the Processing menu, point to **Start** and click **Start Assembler**.

An unencrypted SRAM Object File (.sof) is generated.

- 7. On the File menu, click **Convert Programming Files**. The **Convert Programming Files** dialog box appears.

- a. In the **Convert Programming Files** dialog box, select the programming file type from the **Programming file type** list.

- b. If applicable, select the appropriate configuration device from the **Configuration device** list.

- c. Select the mode from the **Mode** list.

- d. Type the file name in the **File name** field, or browse to and select the file.

- e. Under the Input files to convert section, click SOF Data.

- f. Click **Add File** to open the **Select Input File** dialog box.

- g. Browse to the unencrypted SOF file and click Open.

- h. Under the **Input files to convert** section, select- the SOF file name. The field is highlighted.

- Click Properties. The SOF Files Properties: Bitstream Encryption dialog box appears.

- j. In the **SOF Files Properties: Bitstream Encryption** dialog box, turn on **Generate encrypted bitstream**.

- k. Turn on **Generate key programming file** and type the **.ekp** file path and file name in the text area, or browse to and select <filename>**.ekp**.

- Additional step for 20-nm FPGAs only: Turn on Enable volatile security key check box to encrypt the .sof file with volatile security key or turn it off to use non-volatile security key.

- m. Additional step for 20-nm FPGAs only: Turn on **Generate encryption lock file** and insert the .qlk file path and file name in the text area, or browse to the desired <filename>.qlk.

- n. Add the keys to the pull-down list either with a .key file or the Add button. The Add and Edit buttons bring up the Key Entry dialog box. The Delete button deletes the currently selected key from the pull-down list.

Note: 40-nm FPGAs require entry of two 256-bit keys. The encryption derived from a combination of the two 256-bit keys. 28-nm and 20-nm FPGAs require entry of a single 256-bit key. The final encryption key is derived using a one-way function.

Using the **.key** file option allows you to specify one or two key files in the corresponding drop-down box. You may use different files for the **Key 1** and **Key 2** fields, or use one **.key** file for both.

The **.key** file is a plain text file in which each line represents a key unless the line starts with "#". The "#" symbol is used to denote comments. Each valid key line has the following format: <key identity><white space><256-bit hexadecimal key>.

```

# This is an example key file

key1 0123456789ABCDEF0123456789ABCDEF0123456789ABCDEF0123456789ABCDEF

key2 ABCDEF0123456789ABCDEF0123456789ABCDEF0123456789

```

The key identity is an alphanumeric name that is used to identify the keys (similar to the key file entry). The key is also the text displayed when the **Show entered keys** button is turned off. It is displayed together with the full key when **Show entered keys** is turned on.

You can save the keys in the pull-down list to a **.key** file. You must click the corresponding **Save** button to save a key and to display the standard **File** dialog box. All keys in the pull-down list are saved to the selected or created **.key** file.

Select the **Key Entry Method** to enter the encryption key either with the onscreen keypad or keyboard.

The on-screen keypad allows you to enter the keys using the keypad. Select a key and click on the on-screen keypad to enter values. You have the option of allowing the keys to be shown as they are entered. If you use this option, you do not need to confirm the keys.

While the on-screen keypad is being used, any attempt to use the keyboard to enter the keys generates a pop-up notification and the key press is ignored. Alternatively, you can enter the encryption key from the keyboard.

- Read the design security feature disclaimer. If you agree to and acknowledge the design security feature disclaimer, turn on the acknowledgment box.

- ii. Click OK.

- o. Additional step for 20-nm FPGAs only: Under **Security Options**, select the level from the **Disable external partial reconfiguration** list.

- p. Additional step for 20-nm FPGAs only: Under **Security Options**, select the level from the **Disable key-related JTAG instructions** list.

- q. Additional step for 20-nm FPGAs only: Under Security Options, select the level from the Disable other extended JTAG instructions list.

683269 | 2021.05.21

- 8. In the **Convert Programming Files** dialog box, click **OK**. The *<filename>.ekp* and encrypted configuration file are generated in the same project directory.

- 9. On the Tools menu, click **Programmer**. The **Programmer** dialog box appears.

- 10. In the **Mode** list, select **JTAG** as the programming mode.

- 11. Click **Hardware Setup**. The **Hardware Setup** dialog box appears.

- a. In the currently selected hardware list, select **Intel FPGA Ethernet Cable** as the programming hardware.

- b. Click Done.

- 12. Click Add File. The Select Programmer File dialog box appears.

- a. Type <filename>.ekp in the File name field.

- b. Click Open.

- 13. Highlight the .ekp file you added and click Program/Configure.

- 14. On the File menu, point to **Create/Update** and click **Create JAM, SVF, or ISC File**. The **Create JAM, SVF, or ISC File** dialog box appears.

- 15. Select the file format required (JEDEC STAPL Format [.jam]), for the .ekp file in the File format field.

- 16. Type the file name in the **File name** field, or browse to and select the file.

- 17. Click **OK** to generate the .jam file.

- 18. On the Tools menu, click **Programmer Options**. The **Programmer Options** dialog box appears.

Note: For non-volatile secure design feature, you must turn off the **Configure**volatile design security key option to generate a non-volatile .svf file of

the .ekp file.

- 19. Click OK.

- 20. Repeat steps 15 on page 16 to 17 on page 16 to generate a .svf file of the .ekp file. Use the default setting in the Create JAM, SVF, or ISC File dialog box when generating a .svf file of the .ekp file.

# Generating Single-Device .ekp File and Encrypting Configuration File using Command-Line Interface in Intel Quartus Prime Software

There is a command-line interface that allows you to generate a single-device **.ekp** file and encrypt Raw Binary File (**.rbf**). The command-line interfaces uses the Intel Quartus Prime software command-line executable, quartus\_cpf, and requires the following syntax or options:

- --key/-k <path to key file>:<key identity>

- A .sof file (user design)

- An .ekp file (the required encryption key programming file name)

You can create a compressed and uncompressed .rbf for configuration by using the following command with an option file which contains the string compression=on.

```

quartus_cpf -c --option=<option file> --key

<keyfile>:<keyid1>:<keyid2> <input_sof_file> <output_rbf_file>

```

683269 | 2021.05.21

Note:

- 1. Encryption and compression cannot be used simultaneously in 20 nm FPGAs.

- For 20 nm FPGAs, use non\_volatile\_key=off to control the Enable volatile key security option during the .rbf file creation.

You can learn more on the option file from the Intel Quartus Prime software command line help. Run quartus\_cpf --help=option to learn more on the available options. For 20 nm FPGAs, use the Qcrypt tool command line to encrypt or decrypt the .rbf file. To generate the .ekp or encrypted configuration file other than .rbf, you have to go through quartus\_cpf.

#### Example 1.

The following example shows two sets of keys that are stored in two different key files: key1 in **key1.key** and key2 in **key2.key**.

```

quartus_cpf --key D: \SIV_DS\key1.key:key1 --key

D:\SIV DS\key2.key:key2 D:\SIV DS\test.sof D:\SIV DS\test.ekp

```

#### Example 2.

The following example shows two sets of keys that are stored in the same key file: key1 and key2 in **key12.key**.

```

quartus_cpf --key

D:\SIV_DS\key12.key:key1:key2 D:\SIV_DS\test.sof D:\SIV_DS\

\test.ekp

```

# Generating Multi-Device .ekp File and Encrypting Configuration File using Intel Ouartus Prime Software

To generate a multi-device **.ekp** file and encrypt your configuration file, follow these steps:

- 1. Start the Intel Quartus Prime software.

- Repeat step 9 on page 16-step 11 on page 16 in Generating Single-Device .ekp

File and Encrypting Configuration File using Intel Quartus Prime Software on page

14

- 3. Click **Add File**. The **Select Programmer File** dialog box appears.

- a. Select the single-device .ekp file, and type <single\_ekp>.ekp in the File name field.

- b. Click Open.

Note: For the correct sequence of devices in the same JTAG chain, you can use the **Auto-Detect** option in the Intel Quartus Prime programmer. If one of the FPGA is not required to be key-programmed, you are not required to replace the device with the <single\_ekp>.ekp file in the Intel Quartus Prime programmer.

- 4. Repeat step 3 on page 17 for each device in the same chain. Ensure the right device sequence is used when adding the **.ekp** files to the programmer window.

- 5. Highlight all the .ekp files you added and click Program/Configure.

- On the File menu, point to Create/Update and click Create JAM, SVF, or ISC File. The Create JAM, SVF, or ISC File dialog box appears.

- 7. Select the required file format (.jam), for all the .ekp files in the File format field.

- 8. Type the file name in the **File name** field, or browse to and select the file.

- 9. Click **OK** to generate the .jam file.

- On the Tools menu, click Programmer Options. The Programmer Options dialog box appears.

Note: You must turn off **Configure volatile design security key** to generate a non-volatile **.svf** file of the **.ekp** file.

- 11. Click OK.

- 12. Repeat steps 7 on page 18 to 9 on page 18 to generate a .svf file for all the .ekp files. Use the default setting in the Create JAM, SVF, or ISC File dialog box when generating a .svf file of the .ekp file.

# Step 2a: Programming Volatile Key into the FPGAs

Before programming the volatile key into the FPGAs, ensure that you can successfully configure the FPGA with an unencrypted configuration file. The volatile key is a reprogrammable and erasable key. Before you program the FPGAs with the volatile key, you must provide an external battery to retain the volatile key. FPGAs with the volatile key successfully programmed can accept both encrypted and unencrypted configuration bitstreams. This enables the use of unencrypted configuration bitstreams for board-level testing.

Any attempt to configure the FPGAs containing the volatile key with a configuration file encrypted with the wrong key causes the configuration to fail. If this occurs, the nSTATUS signal from the FPGA pulses low and continues to reset itself if you enable the **Auto-restart configuration after error** option in the Intel Quartus Prime software.

You can program the key into the FPGAs with on-board prototyping listed in Key Programming on page 7.

### **Step 2b: Programming Non-Volatile Key into the FPGAs**

Before programming the non-volatile key into the devices, ensure that you can successfully configure the FPGA with an unencrypted configuration file. The non-volatile key is one-time programmable through the JTAG interface. You can program the non-volatile key into the devices without an external battery. Devices with the non-volatile key successfully programmed can accept both encrypted and unencrypted configuration bitstreams. If you set the tamper protection bit, only encrypted configuration bitstreams are accepted. This enables the use of unencrypted configuration bitstreams for board-level testing.

Any attempt to configure the FPGAs containing the volatile key with a configuration file encrypted with the wrong key causes the configuration to fail. If this occurs, the  ${\tt nSTATUS}$  signal from the FPGA pulses low and continues to reset itself if you enable the **Auto-restart configuration after error** option in the Intel Quartus Prime software.

You can program the non-volatile key into the devices using on-board prototyping, volume production, and off-board prototyping and production listed in Key Programming on page 7.

# Programming Volatile or Non-Volatile Key using Intel FPGA Ethernet Cable and Intel Quartus Prime Software

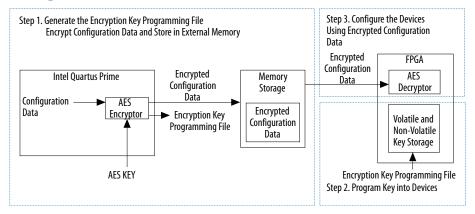

Connect the Intel FPGA Ethernet Cable communications cable to the Intel FPGA Ethernet Cable header as shown in the following figure.

#### Figure 2. Intel FPGA Ethernet Cable Header

The Intel FPGA Ethernet Cable header and Intel FPGA Download Cable header are identical for key programming.

Note: For Intel FPGA Ethernet Cable, set the TCK speed to the required TCK period.

#### **Related Information**

- EthernetBlaster Communications Cable User Guide

- EthernetBlaster II Communications Cable User Guide

Provides more information about changing the TCK clock speed for Intel FPGA Ethernet Cable.

- Device Datasheet for Arria II Devices

Provides more information about the specific voltages required using the JTAG download cable.

• DC and Switching Characteristics for Stratix IV Devices

Provides more information about the specific voltages required using the JTAG download cable.

• Arria V Device Datasheet

Provides more information about the specific voltages required using the JTAG download cable.

• Cyclone V Device Datasheet

Provides more information about the specific voltages required using the JTAG download cable.

Stratix V Device Datasheet

Provides more information about the specific voltages required using the JTAG download cable.

• Intel Arria 10 Device Datasheet

Provides more information about the specific voltages required using the JTAG download cable.

Intel Cyclone 10 GX Device Datasheet

Provides more information about the specific voltages required using the JTAG download cable.

# Programming Single-Device Volatile or Non-Volatile Key using Intel Quartus Prime Software

To perform single-device volatile or non-volatile key programming using the Intel Quartus Prime software through the Intel FPGA Ethernet Cable, follow these steps:

1. Check the firmware version of the Intel FPGA Ethernet Cable. Verify that the JTAG firmware build are up-to-date.

Note: Refer to the Cable and Adapter driver page to find the latest Intel FPGA Ethernet Cable firmware build version.

- 2. Start the Intel Quartus Prime software.

- 3. On the Tools menu, click **Programmer**. The **Programmer** dialog box appears.

- 4. In the Mode list, select JTAG as the programming mode.

- 5. Click **Hardware Setup**. The **Hardware Setup** dialog box appears.

- a. In the **Currently selected hardware** list, select **Intel FPGA Ethernet Cable** as the programming hardware.

- b. Click Done.

- 6. Click Add File. The Select Programmer File dialog box appears.

- a. Type <filename>.ekp in the File name field.

- b. Click Open.

- 7. Highlight the .ekp file you added and click Program/Configure.

- 8. On the Tools menu, click **Options**. The **Options** dialog box appears.

- In the Category list, click Programmer. You can choose to turn on or turn off the Configure volatile design security key option to perform volatile or nonvolatile key programming.

- 10. Click **OK** to close the **Options** dialog box.

- 11. Click **Start** to program the key.

*Note:* The Intel Quartus Prime software message window provides information about the success or failure of the key programming operation.

#### **Related Information**

EthernetBlaster Communications Cable User Guide

Provides more information about JTAG firmware upgrade instructions.

# Programming Single-Device Volatile or Non-Volatile Key using the Command-Line Interface in Intel Quartus Prime Software

To perform single-device volatile or non-volatile key programming using the Intel Quartus Prime software command-line interface through the Intel FPGA Ethernet Cable, follow these steps:

- Perform step 1 on page 20 of Programming Single-Device Volatile or Non-Volatile Key using Intel Quartus Prime Software on page 20.

- 2. To determine the Intel FPGA Ethernet Cable cable port number that is connected to the JTAG server, type quartus\_jli -n at the command-line prompt.

- 3. With the **single\_ekp.jam** file generated in Step 1: Generating .ekp File and Encrypting Configuration File on page 13, execute volatile or non-volatile key programming to a single FPGA with the following command line:

- Volatile key programming:

```

quartus_jli -c<n> single_ekp.jam -aKEY_CONFIGURE

```

Non-volatile key programming:

```

quartus_jli -c<n> single_ekp.jam -aKEY_PROGRAM

```

<n> is the port number returned with the -n option.

*Note:* The Intel Quartus Prime software command-line provides information about the success or failure of the key programming operation.

#### **Related Information**

AN 425: Using the Command-Line Jam STAPL Solution for Device Programming Provides more information about quartus\_jli.

# Programming Multi-Device Volatile or Non-Volatile Key using Intel Quartus Prime Software

To perform multi-device volatile or non-volatile key programming using the Intel Quartus Prime software through the Intel FPGA Ethernet Cable, follow these steps:

- 1. Repeat step 1 on page 20-step 5 on page 20 in Programming Single-Device Volatile or Non-Volatile Key using Intel Quartus Prime Software on page 20.

- 2. Click **Add File**. The **Select Programmer File** dialog box appears.

- a. Programming using single-device .ekp files:

- i. Type < single\_device > .ekp in the File name field.

- ii. Click Open.

- iii. Repeat steps 2.a.i on page 21 to 2.a.ii on page 21 for the number of devices in the same chain.

- iv. Highlight the .ekp files you added and click Program/Configure.

*Note:* For the correct sequence of the devices in the same JTAG chain, you can use the **Auto-Detect** option in the Intel Quartus Prime programmer.

- b. Programming using a multi-device .jam file:

- i. Type < multi device > .jam in the File name field.

- ii. Click Open.

- iii. Highlight the .jam file you added and click Program/Configure.

- 3. Repeat step 8 on page 20-step 10 on page 20 of Programming Single-Device Volatile or Non-Volatile Key using Intel Quartus Prime Software on page 20 to perform volatile or non-volatile key programming.

- 4. Click **Start** to program the key.

*Note:* The Intel Quartus Prime software message window provides information about the success or failure of the key programming operation.

# Programming Multi-Device Volatile or Non-Volatile Key using the Command-Line Interface in Intel Quartus Prime Software

To perform multi-device volatile or non-volatile key programming using the Intel Quartus Prime software command-line interface through the Intel FPGA Ethernet Cable, follow these steps:

- 1. Perform step 1 on page 20 of Programming Single-Device Volatile or Non-Volatile Key using Intel Quartus Prime Software on page 20.

- 2. To determine the Intel FPGA Ethernet Cable cable port number that is connected to the JTAG server, type quartus\_jli -n at the command-line prompt.

- 3. With the **multi\_ekp.jam** file generated in Step 1: Generating .ekp File and Encrypting Configuration File on page 13, execute volatile or non-volatile key programming for multiple FPGAs with the following command line:

- Volatile key programming:

```

quartus_jli -c<n> multi_ekp.jam -aKEY_CONFIGURE

```

Non-volatile key programming:

```

quartus_jli -c<n> multi_ekp.jam -aKEY_PROGRAM <n> is the port number returned with the -n option.

```

*Note:* The Intel Quartus Prime software command-line provides information about the success or failure of the key programming operation.

# **Programming Key using JTAG Technologies**

The key programming for your design is performed using a **.svf** file (**.ekp** file in **.svf** format) and a JT 37xx boundary scan controller in combination with a JT2147 QuadPod system.

Information about creating a .svf file to support multi-device programming is described in Generating Multi-Device .ekp File and Encrypting Configuration File using Intel Quartus Prime Software on page 17.

#### **Related Information**

JTAG Technologies

Provides more information about procedures for JTAG programming.

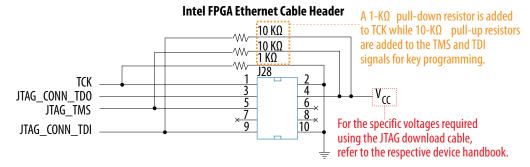

# Step 3: Configuring the 40-nm, 28-nm, or 20-nm FPGAs with Encrypted Configuration Data

The final step is to configure the protected 40-nm, 28-nm, or 20-nm FPGAs with the encrypted configuration file.

During configuration, the encrypted configuration data is sent to the 40-nm, 28-nm, or 20-nm FPGAs. Using the previously stored key, the FPGA decrypts the configuration data and uses the unencrypted data to configure itself. Only configuration files encrypted using the correct key are accepted by the FPGA for successful configuration. Without a correct key, a stolen encrypted file is useless.

# **Steps to Enable Tamper-Protection Bit Programming**

The default .ekp file generated in the *Steps for Implementing a Secure Configuration Flow* section contains only volatile or non-volatile key programming. To enable the tamper-protection bit programming, follow these steps:

- 1. Create a quartus.ini file using the text editor, with this key-value pair: PGM\_GEN\_KEY\_SECURE\_EKP=ON.

- 2. Save the quartus.ini in one of the following folders:

- Project folder

- <Quartus installation folder>\bin64 folder for Windows OS

- <Quartus installation folder>/linux64 folder for Linux OS

- 3. When the Intel Quartus Prime Convert Programming File tool read the quartus.ini during .ekp file generation process, the additional tamper-protection bit programming instruction is inserted into the generated .ekp file.

**Caution:** The .ekp file generated with this quartus.ini contain tamper-protection bit programming. When the .ekp file is used to program into the devices, the tamper-protection bit is programmed, and this programming is not reversible. You need to manage the .ekp file to avoid unintentional programming of tamper-protection bit into your device.

As the .ekp file contains the tamper bit programming instruction, therefore if you generate .jam or .svf files from this .ekp file for key programming, the .jam or .svf files program the tamper-protection bit without the need for the quartus.ini with the specified key-value pair.

# **Supported Configuration Schemes**

The design security feature is available in all configuration schemes except JTAG-based configuration.

Table 12. Design Security Support for Each Configuration Scheme

| Configuratio n Scheme | Configuration Method                                             | Design<br>Security | Notes                                                                             |

|-----------------------|------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------|

| FPP                   | A MAX II or MAX V device, or a microprocessor and a flash memory | Yes                | In this mode, the host system must send a DCLK signal that is 4x the data rate.   |

| AS                    | Serial configuration device                                      | Yes                | _                                                                                 |

| PS                    | A MAX II or MAX V device, or a microprocessor and a flash memory | Yes                | -                                                                                 |

|                       | Intel FPGA Download Cable and Intel FPGA<br>Download Cable II    | Yes                | Configure encrypted .rbf to FPGA using PS mode in Intel Quartus Prime Programmer. |

| JTAG                  | Intel FPGA Download Cable and Intel FPGA<br>Download Cable II    | _                  | For key programming.                                                              |

If your system contains a common flash interface (CFI) flash memory, you can also use it for the FPGA configuration. The MAX II and MAX V together with the Parallel Flash Loader Intel FPGA IP core provides an efficient method to program CFI flash memory through the JTAG interface.

You can use the design security feature with other configuration features, such as the compression and remote system upgrade features. When compression is used with the design security feature, the configuration file is first compressed and then encrypted in the Intel Quartus Prime software. During configuration, the FPGA first decrypts and then uncompresses the configuration file.

Note: Encryption and compression cannot be used simultaneously in 20-nm FPGAs.

You can either perform boundary-scan test (BST) or use the Signal Tap logic analyzer to analyze functional data within the FPGA. However, you cannot perform JTAG configuration after the key with tamper-protection bit set is programmed into the 40-nm, 28-nm or 20-nm FPGAs.

When using the Signal Tap logic analyzer, you must first configure the device with an encrypted configuration file using PS, FPP, or AS configuration schemes. The design must contain at least one instance of the Signal Tap logic analyzer. After the FPGA is configured with a Signal Tap logic analyzer instance in the design. Open the Signal Tap logic analyzer window in the Intel Quartus Prime software and click **Scan Chain**. Once the scanning is complete, the Signal Tap logic analyzer is ready to acquire data using JTAG interface.

#### **Related Information**

- Configuration, Design Security, and Remote System Upgrades in Arria II Devices Provides more information about the design security for Arria II devices.

- Configuration, Design Security, and Remote System Upgrades in Stratix IV Devices Provides more information about the design security for Stratix IV devices.

- Configuration, Design Security, and Remote System Upgrades in Arria V Devices

Provides more information about the design security for Arria V devices.

- Configuration, Design Security, and Remote System Upgrades in Cyclone V Devices

Provides more information about the design security for Cyclone V devices.

- Configuration, Design Security, and Remote System Upgrades in Stratix V Devices Provides more information about the design security for Stratix V devices.

- Configuration, Design Security, and Remote System Upgrades in Intel Arria 10

Devices

Provides more information about the design security for Intel Arria 10 devices.

Configuration, Design Security, and Remote System Upgrades in Intel Cyclone 10 GX Devices

Provides more information about the design security for Intel Cyclone 10 devices.

# **Security Mode Verification**

Intel FPGAs support the KEY\_VERIFY JTAG instruction that allows you to verify the existing security mode of the device. To check if you have successfully programmed the volatile key, use the .jam files to automate the security mode verification steps.

Table 13. KEY\_VERIFY JTAG Instruction

| JTAG Instruction | Instruction Code | Description                                                      |

|------------------|------------------|------------------------------------------------------------------|

| KEY_VERIFY       | 00 0001 0011     | Connects the key verification scan register between TDI and TDO. |

The  $\mathtt{KEY\_VERIFY}$  JTAG instruction allows you to read out the information on the security features that are enabled on the chip. This instruction scans out associated bit values.

Table 14. Security Mode Verification for 40-nm FPGAs

| Security Mode                | <b>Supported Device</b>    | Bit 0 | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Bit 5 |

|------------------------------|----------------------------|-------|-------|-------|-------|-------|-------|

| No key                       | Arria II GX                | 0     | 0     | 0     | 0     | 0     | 0     |

|                              | Arria II GZ     Stratix IV | 0     | 0     | 0     | 0     | Х     | Х     |

| Volatile key                 | Arria II GX                | 1     | 0     | 0     | 0     | 0     | 0     |

|                              | Arria II GZ     Stratix IV | 1     | 0     | 0     | 0     | х     | Х     |