### Introduction

Altera® HardCopy devices provide a comprehensive alternative to ASICs. HardCopy structured ASICs offer a complete solution from prototype to high-volume production, and maintain the powerful features and high-performance architecture of their equivalent FPGAs with the programmability removed. You can use the Quartus II design software to design HardCopy devices in a manner similar to the traditional ASIC design flow and you can prototype with Altera's high density Stratix, APEX 20KC, and APEX 20KE FPGAs before seamlessly migrating to the corresponding HardCopy device for high-volume production.

HardCopy structured ASICs provide the following key benefits:

- Improves performance, on the average, by 40% over the corresponding -6 speed grade FPGA device

- Lowers power consumption, on the average, by 40% over the corresponding FPGA

- Preserves the FPGA architecture and features and minimizes risk

- Guarantees first-silicon success through a proven, seamless migration process from the FPGA to the equivalent HardCopy device

- Offers a quick turnaround of the FPGA design to a structured ASIC device—samples are available in about eight weeks

Altera's Quartus II software has built-in support for HardCopy Stratix devices. The HardCopy design flow in Quartus II software offers the following advantages:

- Unified design flow from prototype to production

- Performance estimation of the HardCopy Stratix device allows you to design systems for maximum throughput

- Easy-to-use and inexpensive design tools from a single vendor

- An integrated design methodology that enables system-on-a-chip designs

This section discusses the following areas:

- How to design HardCopy Stratix and HardCopy APEX structured ASICs using the Quartus II software

- An explanation of what the HARDCOPY\_FPGA\_PROTOTYPE devices are and how to target designs to these devices

- Performance and power estimation of HardCopy Stratix devices

- How to generate the HardCopy design database for submitting HardCopy Stratix and HardCopy APEX designs to the HardCopy Design Center

## Features

Beginning with version 4.2, the Quartus II software contains several powerful features that facilitate design of HardCopy Stratix and HardCopy APEX devices:

- **HARDCOPY\_FPGA\_PROTOTYPE Devices**

These are virtual Stratix FPGA devices with features identical to HardCopy Stratix devices. You must use these FPGA devices to prototype your designs and verify the functionality in silicon.

- **HardCopy Timing Optimization Wizard**

Using this feature, you can target your design to HardCopy Stratix devices, providing an estimate of the design's performance in a HardCopy Stratix device.

- **HardCopy Stratix Floorplans and Timing Models**

The Quartus II software supports post-migration HardCopy Stratix device floorplans and timing models and facilitates design optimization for design performance.

- **Placement Constraints**

Location and LogicLock constraints are supported at the HardCopy Stratix floorplan level to improve overall performance.

- **Improved Timing Estimation**

Beginning with version 4.2, the Quartus II software determines routing and associated buffer insertion for HardCopy Stratix designs, and provides the Timing Analyzer with more accurate information about the delays than was possible in previous versions of the Quartus II software. The Quartus II Archive File automatically receives buffer insertion information, which greatly enhances the timing closure process in the back-end migration of your HardCopy Stratix device.

■ **Design Assistant**

This feature checks your design for compliance with all HardCopy device design rules and establishes a seamless migration path in the quickest time.

■ **HardCopy Files Wizard**

This wizard allows you to deliver to Altera the design database and all the deliverables required for migration. This feature is used for HardCopy Stratix and HardCopy APEX devices.

The HardCopy Stratix and HardCopy APEX PowerPlay Early Power Estimator is available on the Altera website at [www.altera.com](http://www.altera.com).

## HARDCOPY\_FPGA\_PROTOTYPE, HardCopy Stratix and Stratix Devices

You must use the HARDCOPY\_FPGA\_PROTOTYPE virtual devices available in the Quartus II software to target your designs to the actual resources and package options available in the equivalent post-migration HardCopy Stratix device. The programming file generated for the HARDCOPY\_FPGA\_PROTOTYPE can be used in the corresponding Stratix FPGA device.

The purpose of the HARDCOPY\_FPGA\_PROTOTYPE is to guarantee seamless migration to HardCopy by making sure that your design only uses resources in the FPGA that can be used in the HardCopy device after migration. You can use the equivalent Stratix FPGAs to verify the design's functionality in-system, then generate the design database necessary to migrate to a HardCopy device. This process ensures the seamless migration of the design from a prototyping device to a production device in high volume. It also minimizes risk, assures samples in about eight weeks, and guarantees first-silicon success.

HARDCOPY\_FPGA\_PROTOTYPE devices are only available for HardCopy Stratix devices and are not available for the HardCopy II or HardCopy APEX device families.

**Table 5–1** compares HARDCOPY\_FPGA\_PROTOTYPE devices, Stratix devices, and HardCopy Stratix devices.

| <b>Table 5–1. Qualitative Comparison of HARDCOPY_FPGA_PROTOTYPE to Stratix and HardCopy Stratix Devices (Part 1 of 2)</b> |                                        |                                        |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|

| <b>Stratix Device</b>                                                                                                     | <b>HARDCOPY_FPGA_PROTOTYPE Device</b>  | <b>HardCopy Stratix Device</b>         |

| FPGA                                                                                                                      | Virtual FPGA                           | Structured ASIC                        |

| FPGA                                                                                                                      | Architecture identical to Stratix FPGA | Architecture identical to Stratix FPGA |

**Table 5–1. Qualitative Comparison of HARDCOPY\_FPGA\_PROTOTYPE to Stratix and HardCopy Stratix Devices (Part 2 of 2)**

| Stratix Device                     | HARDCOPY_FPGA_PROTOTYPE Device                             | HardCopy Stratix Device                                     |

|------------------------------------|------------------------------------------------------------|-------------------------------------------------------------|

| FPGA                               | Resources identical to HardCopy Stratix device             | M-RAM resources different than Stratix FPGA in some devices |

| Ordered through Altera part number | Cannot be ordered, use the Altera Stratix FPGA part number | Ordered by Altera part number                               |

Table 5–2 lists the resources available in each of the HardCopy Stratix devices.

**Table 5–2. HardCopy Stratix Device Physical Resources**

| Device      | LEs    | ASIC Equivalent Gates (K) (1) | M512 Blocks | M4K Blocks | M-RAM Blocks | DSP Blocks | PLLs | Maximum User I/O Pins |

|-------------|--------|-------------------------------|-------------|------------|--------------|------------|------|-----------------------|

| HC1S25F672  | 25,660 | 250                           | 224         | 138        | 2            | 10         | 6    | 473                   |

| HC1S30F780  | 32,470 | 325                           | 295         | 171        | 2 (2)        | 12         | 6    | 597                   |

| HC1S40F780  | 41,250 | 410                           | 384         | 183        | 2 (2)        | 14         | 6    | 615                   |

| HC1S60F1020 | 57,120 | 570                           | 574         | 292        | 6            | 18         | 12   | 773                   |

| HC1S80F1020 | 79,040 | 800                           | 767         | 364        | 6 (2)        | 22         | 12   | 773                   |

**Notes to Table 5–2:**

- (1) Combinational and registered logic do not include digital signal processing (DSP) blocks, on-chip RAM, or phase-locked loops (PLLs).

- (2) The M-RAM resources for these HardCopy devices differ from the corresponding Stratix FPGA.

For a given device, the number of available M-RAM blocks in HardCopy Stratix devices is identical with the corresponding HARDCOPY\_FPGA\_PROTOTYPE devices, but may be different from the corresponding Stratix devices. Maintaining the identical resources between HARDCOPY\_FPGA\_PROTOTYPE and HardCopy Stratix devices facilitates seamless migration from the FPGA to the structured ASIC device.

For more information about HardCopy Stratix devices, refer to the *HardCopy Stratix Device Family Data Sheet* section in volume 1 of the *HardCopy Series Handbook*.

The three devices, Stratix FPGA, HARDCOPY\_FPGA\_PROTOTYPE, and HardCopy device, are distinct devices in the Quartus II software. The HARDCOPY\_FPGA\_PROTOTYPE programming files are used in the

Stratix FPGA for your design. The three devices are tied together with the same netlist, thus a single SRAM Object File (**.sof**) can be used to achieve the various goals at each stage. The same SRAM Object File is generated in the HARDCOPY\_FPGA\_PROTOTYPE design, and is used to program the Stratix FPGA device, the same way that it is used to generate the HardCopy Stratix device, guaranteeing a seamless migration.

For more information about the SRAM Object File and programming Stratix FPGA devices, refer to the *Programming and Configuration* chapter of the *Introduction to Quartus II Manual*.

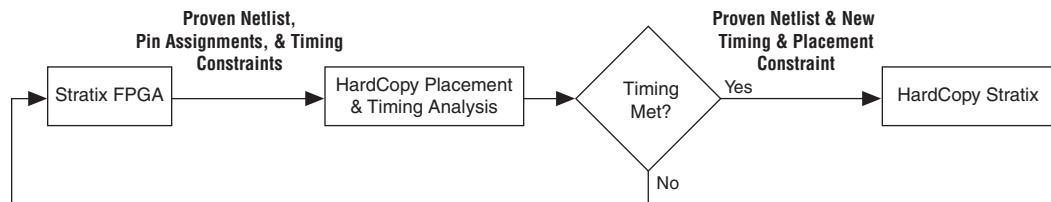

## HardCopy Design Flow

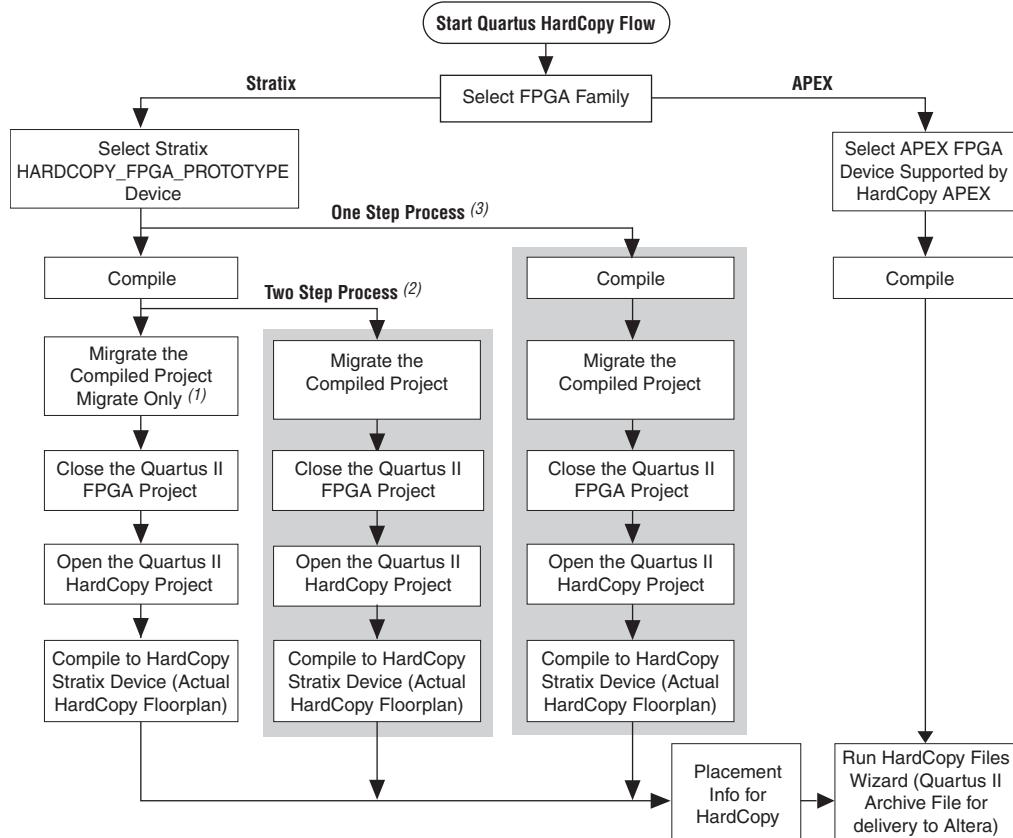

**Figure 5-1** shows a HardCopy design flow diagram. The design steps are explained in detail in the following sections of this chapter. The HardCopy Stratix design flow utilizes the HardCopy Timing Optimization Wizard to automate the migration process into a one-step process. The remainder of this section explains the tasks performed by this automated process.

For a detailed description of the HardCopy Timing Optimization Wizard and HardCopy Files Wizard, refer to “HardCopy Timing Optimization Wizard Summary” and “Generating the HardCopy Design Database”.

Figure 5-1. HardCopy Stratix and HardCopy APEX Design Flow Diagram

**Notes to Figure 5-1:**

- (1) Migrate Only Process: The displayed flow is completed manually.

- (2) Two Step Process: Migration and Compilation are done automatically (shaded area).

- (3) One Step Process: Full HardCopy Compilation. The entire process is completed automatically (shaded area).

## The Design Flow Steps of the One Step Process

The following sections describe each step of the full HardCopy compilation (the One Step Process), Figure 5-1.

### Compile the Design for an FPGA

This step compiles the design for a HARDCOPY\_FPGA\_PROTOTYPE device and gives you the resource utilization and performance of the FPGA.

### *Migrate the Compiled Project*

This step generates the Quartus II Project File (**.qpf**) and the other files required for HardCopy implementation. The Quartus II software also assigns the appropriate HardCopy Stratix device for the design migration.

### *Close the Quartus FPGA Project*

Because you must compile the project for a HardCopy Stratix device, you must close the existing project which you have targeted your design to a **HARDCOPY\_FPGA\_PROTOTYPE** device.

### *Open the Quartus HardCopy Project*

Open the Quartus II project that you created in the “[Migrate the Compiled Project](#)” step. The selected device is one of the devices from the HardCopy Stratix family that was assigned during that step.

### *Compile for HardCopy Stratix Device*

Compile the design for a HardCopy Stratix device. After successful compilation, the Timing Analysis section of the compilation report shows the performance of the design implemented in the HardCopy device.

## **How to Design HardCopy Stratix Devices**

This section describes the process for designing for a HardCopy Stratix device using the **HARDCOPY\_FPGA\_PROTOTYPE** as your initial selected device. In order to use the HardCopy Timing Optimization Wizard, you must first design with the **HARDCOPY\_FPGA\_PROTOTYPE** in order for the design to migrate to a HardCopy Stratix device.

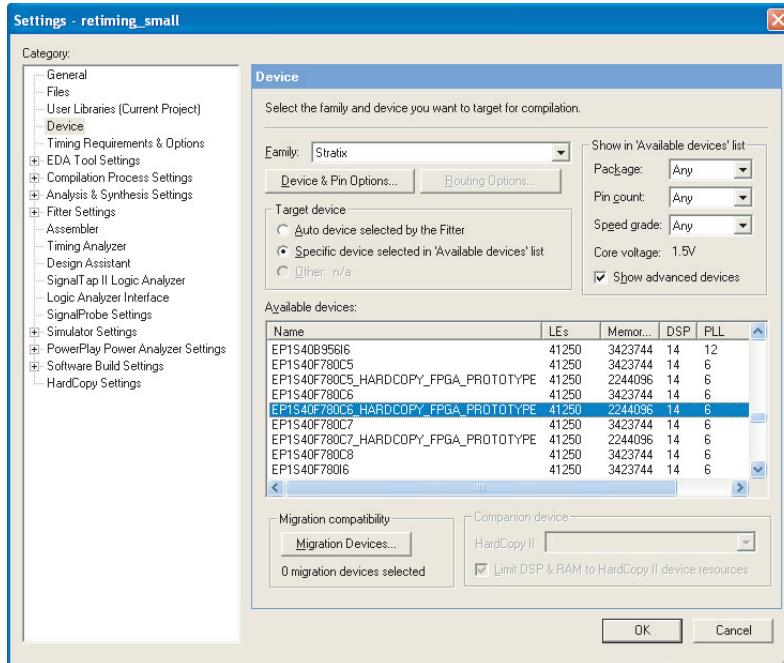

To target a design to a HardCopy Stratix device in the Quartus II software, follow these steps:

1. If you have not yet done so, create a new project or open an existing project.

2. On the Assignments menu, click **Settings**. In the **Category** list, select **Device**.

3. On the **Device** page, in the **Family** list, select **Stratix**. Select the desired **HARDCOPY\_FPGA\_PROTOTYPE** device in the **Available Devices** list ([Figure 5–2](#)).

Figure 5–2. Selecting a HARDCOPY\_FPGA\_PROTOTYPE Device

By choosing the HARDCOPY\_FPGA\_PROTOTYPE device, all the design information, available resources, package option, and pin assignments are constrained to guarantee a seamless migration of your project to the HardCopy Stratix device. The netlist resulting from the HARDCOPY\_FPGA\_PROTOTYPE device compilation contains information about the electrical connectivity, resources used, I/O placements, and the unused resources in the FPGA device.

4. On the Assignments menu, click **Settings**. In the **Category** list, select **HardCopy Settings** and specify the input transition timing to be modeled for both clock and data input pins. These transition times are used in static timing analysis during back-end timing closure of the HardCopy device.

5. Add constraints to your HARDCOPY\_FPGA\_PROTOTYPE device, and on the Processing menu, click **Start Compilation** to compile the design.

### *HardCopy Timing Optimization Wizard*

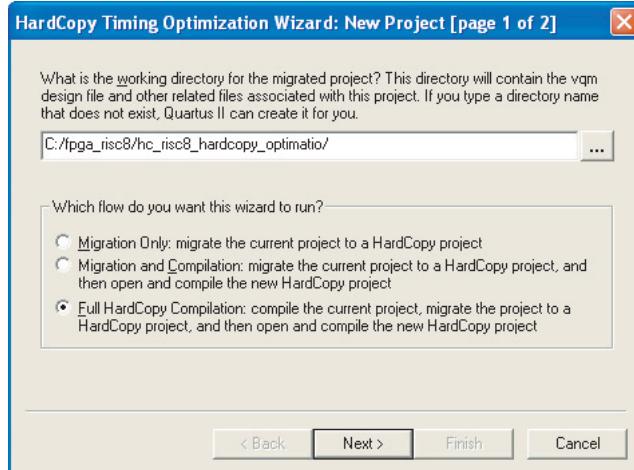

After you have successfully compiled your design in the HARDCOPY\_FPGA\_PROTOTYPE, you must migrate the design to the HardCopy Stratix device to get a performance estimation of the HardCopy Stratix device. This migration is required before submitting the design to Altera for the HardCopy Stratix device implementation. To perform the required migration, on the Project menu, point to HardCopy Utilities and click **HardCopy Timing Optimization Wizard**.

At this point, you are presented with the following three choices to target the designs to HardCopy Stratix devices ([Figure 5-3](#)).

- **Migration Only:** You can select this option after compiling the HARDCOPY\_FPGA\_PROTOTYPE project to migrate the project to a HardCopy Stratix project.

You can now perform the following tasks manually to target the design to a HardCopy Stratix device. Refer to ["Performance Estimation" on page 5-12](#) for additional information about how to perform these tasks.

- Close the existing project

- Open the migrated HardCopy Stratix project

- Compile the HardCopy Stratix project for a HardCopy Stratix device

- **Migration and Compilation:** You can select this option after compiling the project. This option results in the following actions:

- Migrating the project to a HardCopy Stratix project

- Opening the migrated HardCopy Stratix project and compiling the project for a HardCopy Stratix device

- **Full HardCopy Compilation:** Selecting this option results in the following actions:

- Compiling the existing HARDCOPY\_FPGA\_PROTOTYPE project

- Migrating the project to a HardCopy Stratix project

- Opening the migrated HardCopy Stratix project and compiling it for a HardCopy Stratix device

**Figure 5–3. HardCopy Timing Optimization Wizard Options**

The main benefit of the HardCopy Timing Wizard's three options is flexibility of the conversion process automation. The first time you migrate your HARDCOPY\_FPGA\_PROTOTYPE project to a HardCopy Stratix device, you may want to use Migration Only, and then work on the HardCopy Stratix project in the Quartus II software. As your prototype FPGA project and HardCopy Stratix project constraints stabilize and you have fewer changes, the Full HardCopy Compilation is ideal for one-click compiling of your HARDCOPY\_FPGA\_PROTOTYPE and HardCopy Stratix projects.

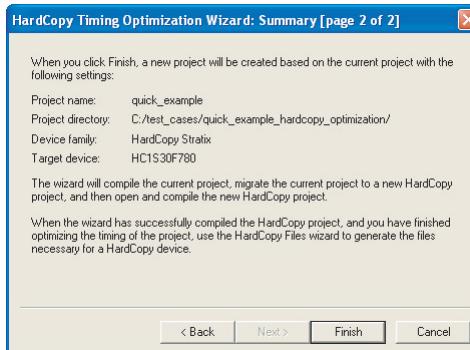

After selecting the wizard you want to run, the “HardCopy Timing Optimization Wizard: Summary” page shows you details about the settings you made in the Wizard, as shown in (Figure 5-4).

**Figure 5-4. HardCopy Timing Optimization Wizard Summary Page**

When either of the second two options in Figure 5-4 are selected (**Migration and Compilation** or **Full HardCopy Compilation**), designs are targeted to HardCopy Stratix devices and optimized using the HardCopy Stratix placement and timing analysis to estimate performance. For details on the performance optimization and estimation steps, refer to “[Performance Estimation](#)” on page 5-12. If the performance requirement is not met, you can modify your RTL source, optimize the FPGA design, and estimate timing until you reach timing closure.

## Tcl Support for HardCopy Migration

To complement the GUI features for HardCopy migration, the Quartus II software provides the following command-line executables (which provide the tool command language (Tcl) shell to run the `--flow` Tcl command) to migrate the HARDCOPY\_FPGA\_PROTOTYPE project to HardCopy Stratix devices:

- `quartus_sh --flow migrate_to_hardcopy <project_name> [-c <revision>]`

This command migrates the project compiled for the HARDCOPY\_FPGA\_PROTOTYPE device to a HardCopy Stratix device.

■ `quartus_sh --flow hardcopy_full_compile <project_name> [-c <revision>]` ↵

This command performs the following tasks:

- Compiles the existing project for a HARDCOPY\_FPGA\_PROTOTYPE device.

- Migrates the project to a HardCopy Stratix project.

- Opens the migrated HardCopy Stratix project and compiles it for a HardCopy Stratix device.

## Design Optimization and Performance Estimation

The HardCopy Timing Optimization Wizard creates the HardCopy Stratix project in the Quartus II software, where you can perform design optimization and performance estimation of your HardCopy Stratix device.

### Design Optimization

Beginning with version 4.2, the Quartus II software supports HardCopy Stratix design optimization by providing floorplans for placement optimization and HardCopy Stratix timing models. These features allow you to refine placement of logic array blocks (LAB) and optimize the HardCopy design further than the FPGA performance. Customized routing and buffer insertion done in the Quartus II software are then used to estimate the design's performance in the migrated device. The HardCopy device floorplan, routing, and timing estimates in the Quartus II software reflect the actual placement of the design in the HardCopy Stratix device, and can be used to see the available resources, and the location of the resources in the actual device.

### Performance Estimation

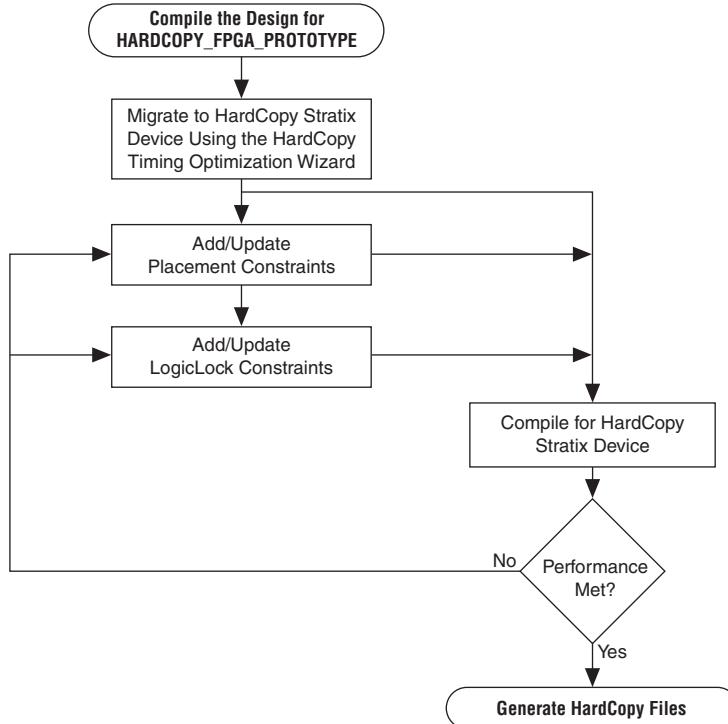

Figure 5–5 illustrates the design flow for estimating performance and optimizing your design. You can target your designs to HARDCOPY\_FPGA\_PROTOTYPE devices, migrate the design to the HardCopy Stratix device, and get placement optimization and timing estimation of your HardCopy Stratix device.

In the event that the required performance is not met, you can:

- Work to improve LAB placement in the HardCopy Stratix project.

*or*

- Go back to the HARDCOPY\_FPGA\_PROTOTYPE project and optimize that design, modify your RTL source code, repeat the migration to the HardCopy Stratix device, and perform the optimization and timing estimation steps.

On average, HardCopy Stratix devices are 40% faster than the equivalent -6 speed grade Stratix FPGA device. These performance numbers are highly design dependent, and you must obtain final performance numbers from Altera.

**Figure 5–5. Obtaining a HardCopy Performance Estimation**

To perform Timing Analysis for a HardCopy Stratix device, follow these steps:

1. Open an existing project compiled for a HARDCOPY\_FPGA\_PROTOTYPE device.

2. On the Project menu, point to HardCopy Utilities and click **HardCopy Timing Optimization Wizard**.

3. Select a destination directory for the migrated project and complete the HardCopy Timing Optimization Wizard process.

On completion of the HardCopy Timing Optimization Wizard, the destination directory created contains the Quartus II project file, and all files required for HardCopy Stratix implementation. At this stage, the design is copied from the HARDCOPY\_FPGA\_PROTOTYPE project directory to a new directory to perform the timing analysis. This two-project directory structure enables you to move back and forth between the HARDCOPY\_FPGA\_PROTOTYPE design database and the HardCopy Stratix design database. The Quartus II software creates the *<project name>\_hardcopy\_optimization* directory.

You do not have to select the HardCopy Stratix device while performing performance estimation. When you run the HardCopy Timing Optimization Wizard, the Quartus II software selects the

HardCopy Stratix device corresponding to the specified HARDCOPY\_FPGA\_PROTOTYPE FPGA. Thus, the information necessary for the HardCopy Stratix device is available from the earlier HARDCOPY\_FPGA\_PROTOTYPE device selection.

All constraints related to the design are also transferred to the new project directory. You can modify these constraints, if necessary, in your optimized design environment to achieve the necessary timing closure. However, if the design is optimized at the HARDCOPY\_FPGA\_PROTOTYPE device level by modifying the RTL code or the device constraints, you must migrate the project with the HardCopy Timing Optimization Wizard.

If an existing project directory is selected when the HardCopy Timing Optimization Wizard is run, the existing information is overwritten with the new compile results.

The project directory is the directory that you chose for the migrated project. A snapshot of the files inside the `<project name>_hardcopy_optimization` directory is shown in [Table 5–3](#).

**Table 5–3. Directory Structure Generated by the HardCopy Timing Optimization Wizard**

```

<project name>_hardcopy_optimization \

<project name>.qsf

<project name>.qpf

<project name>.sof

<project name>.macr

<project name>.gclk

db\

hardcopy_fpga_prototype\

fpga_<project name>_violations.datasheet

fpga_<project name>_target.datasheet

fpga_<project name>_rba_pt_hcpy_v.tcl

fpga_<project name>_pt_hcpy_v.tcl

fpga_<project name>_hcpy_v.sdo

fpga_<project name>_hcpy.vo

fpga_<project name>_cpld.datasheet

fpga_<project name>_cksum.datasheet

fpga_<project name>_tan.rpt

fpga_<project name>_map.rpt

fpga_<project name>_map.atm

fpga_<project name>_fit.rpt

fpga_<project name>_db_info

fpga_<project name>_cmp.xml

fpga_<project name>_cmp.rcf

fpga_<project name>_cmp.atm

fpga_<project name>_asm.rpt

fpga_<project name>_qarlog

fpga_<project name>_qar

fpga_<project name>_qsf

fpga_<project name>_pin

fpga_<project name>_qpf

db_export\

<project name>.map.atm

<project name>.map.hdbx

<project name>.db_info

```

4. Open the migrated Quartus II project created in Step 3.

5. Perform a full compilation.

After successful compilation, the Timing Analysis section of the Compilation Report shows the performance of the design.

Performance estimation is not supported for HardCopy APEX devices in the Quartus II software. Your design can be optimized by modifying the RTL code or the FPGA design and the constraints. You should contact Altera to discuss any desired performance improvements with HardCopy APEX devices.

## Buffer Insertion

Beginning with version 4.2, the Quartus II software provides improved HardCopy Stratix device timing closure and estimation, to more accurately reflect the results expected after back-end migration. The Quartus II software performs the necessary buffer insertion in your HardCopy Stratix device during the Fitter process, and stores the location of these buffers and necessary routing information in the Quartus II Archive File. This buffer insertion improves the estimation of the Quartus II Timing Analyzer for the HardCopy Stratix device.

## Placement Constraints

Beginning with version 4.2, the Quartus II software supports placement constraints and LogicLock regions for HardCopy Stratix devices. [Figure 5-6](#) shows an iterative process to modify the placement constraints until the best placement for the HardCopy Stratix device is achieved.

---

Figure 5–6. Placement Constraints Flow for HardCopy Stratix Devices

## Location Constraints

This section provides information about HardCopy Stratix logic location constraints.

### LAB Assignments

Logic placement in HardCopy Stratix is limited to LAB placement and optimization of the interconnecting signals between them. In a Stratix FPGA, individual logic elements (LE) are placed by the Quartus II Fitter into LABs. The HardCopy Stratix migration process requires that LAB contents cannot change after the Timing Optimization Wizard task is done. Therefore, you can only make LAB-level placement optimization and location assignments after migrating the HARDCOPY\_FPGA\_PROTOTYPE project to the HardCopy Stratix device.

The Quartus II software supports these LAB location constraints for HardCopy Stratix devices. The entire contents of a LAB is moved to an empty LAB when using LAB location assignments. If you want to move the logic contents of LAB A to LAB B, the entire contents of LAB A are moved to an empty LAB B. For example, the logic contents of LAB\_X33\_Y65 can be moved to an empty LAB at LAB\_X43\_Y56 but individual logic cell LC\_X33\_Y65\_N1 can not be moved by itself in the HardCopy Stratix Timing Closure Floorplan.

## LogicLock Assignments

The LogicLock feature of the Quartus II software provides a block-based design approach. Using this technique you can partition your design and create each block of logic independently, optimize placement and area, and integrate all blocks into the top level design.

To learn more about this methodology, refer to the *Quartus II Analyzing and Optimizing Design Floorplan* chapter in volume 2 of the *Quartus II Handbook*.

LogicLock constraints are supported when you migrate the project from a HARDCOPY\_FPGA\_PROTOTYPE project to a HardCopy Stratix project. If the LogicLock region was specified as “Size=Fixed” and “Location=Locked” in the HARDCOPY\_FPGA\_PROTOTYPE project, it is converted to have “Size=Auto” and “Location=Floating” as shown in the following LogicLock examples. This modification is necessary because the floorplan of a HardCopy Stratix device is different from that of the Stratix device, and the assigned coordinates in the HARDCOPY\_FPGA\_PROTOTYPE do not match the HardCopy Stratix floorplan. If this modification did not occur, LogicLock assignments would lead to incorrect placement in the Quartus II Fitter. Making the regions auto-size and floating, maintains your LogicLock assignments, allowing you to easily adjust the LogicLock regions as required and lock their locations again after HardCopy Stratix placement.

The following are two examples of LogicLock assignments.

### LogicLock Region Definition in the HARDCOPY\_FPGA\_PROTOTYPE Quartus II Settings File

```

set_global_assignment -name LL_HEIGHT 15 -entity risc8 -section_id test

set_global_assignment -name LL_WIDTH 15 -entity risc8 -section_id test

set_global_assignment -name LL_STATE LOCKED -entity risc8 -section_id test

set_global_assignment -name LL_AUTO_SIZE OFF -entity risc8 -section_id test

```

### LogicLock Region Definition in the Migrated HardCopy Stratix Quartus II Settings File

```

set_global_assignment -name LL_HEIGHT 15 -entity risc8 -section_id test

set_global_assignment -name LL_WIDTH 15 -entity risc8 -section_id test

set_global_assignment -name LL_STATE FLOATING -entity risc8 -section_id test

set_global_assignment -name LL_AUTO_SIZE ON -entity risc8 -section_id test

```

## Checking Designs for HardCopy Design Guidelines

When you develop a design with HardCopy migration in mind, you must follow Altera-recommended design practices that ensure a straightforward migration process or the design will not be able to be implemented in a HardCopy device. Prior to starting migration of the design to a HardCopy device, you must review the design and identify and address all the design issues. Any design issues that have not been addressed can jeopardize silicon success.

### Altera Recommended HDL Coding Guidelines

Designing for Altera PLD, FPGA, and HardCopy structured ASIC devices requires certain specific design guidelines and hardware description language (HDL) coding style recommendations be followed.

For more information about design recommendations and HDL coding styles, refer to the *Design Guidelines* section in volume 1 of the *Quartus II Handbook*.

### Design Assistant

The Quartus II software includes the Design Assistant feature to check your design against the HardCopy design guidelines. Some of the design rule checks performed by the Design Assistant include the following rules:

- Design should not contain combinational loops

- Design should not contain delay chains

- Design should not contain latches

To use the Design Assistant, you must run Analysis and Synthesis on the design in the Quartus II software. Altera recommends that you run the Design Assistant to check for compliance with the HardCopy design guidelines early in the design process and after every compilation.

### *Design Assistant Settings*

You must select the design rules in the **Design Assistant** page prior to running the design. On the Assignments menu, click **Settings**. In the **Settings** dialog box, in the Category list, select **Design Assistant** and turn on **Run Design Assistant during compilation**. Altera recommends enabling this feature to run the Design Assistant automatically during compilation of your design.

### *Running Design Assistant*

To run Design Assistant independently of other Quartus II features, on the Processing menu, point to Start and click **Start Design Assistant**.

The Design Assistant automatically runs in the background of the Quartus II software when the HardCopy Timing Optimization Wizard is launched, and does not display the Design Assistant results immediately to the display. The design is checked before the Quartus II software migrates the design and creates a new project directory for performing timing analysis.

Also, the Design Assistant runs automatically whenever you generate the HardCopy design database with the HardCopy Files Wizard. The Design Assistant report generated is used by the Altera HardCopy Design Center to review your design.

## **Reports and Summary**

The results of running the Design Assistant on your design are available in the Design Assistant Results section of the Compilation Report. The Design Assistant also generates the summary report in the `<project name>\hardcopy` subdirectory of the project directory. This report file is titled `<project name>_violations.datasheet`. Reports include the settings, run summary, results summary, and details of the results and messages. The Design Assistant report indicates the rule name, severity of the violation, and the circuit path where any violation occurred.

To learn about the design rules and standard design practices to comply with HardCopy design rules, refer to the Quartus II Help and the *HardCopy Series Design Guidelines* chapter in volume 1 of the *HardCopy Series Handbook*.

## Generating the HardCopy Design Database

You can use the HardCopy Files Wizard to generate the complete set of deliverables required for migrating the design to a HardCopy device in a single click. The HardCopy Files Wizard asks questions related to the design and archives your design, settings, results, and database files for delivery to Altera. Your responses to the design details are stored in `<project name>_hardcopy_optimization\<project name>.hps.txt`.

You can generate the archive of the HardCopy design database only after compiling the design to a HardCopy Stratix device. The Quartus II Archive File is generated at the same directory level as the targeted project, either before or after optimization.

The Design Assistant automatically runs when the HardCopy Files Wizard is started.

Figure 5–4 shows the archive directory structure and files collected by the HardCopy Files Wizard.

**Table 5–4. HardCopy Stratix Design Files Collected by the HardCopy Files Wizard**

```

<project name>_hardcopy_optimization\

<project name>.flow.rpt

<project name>.qpf

<project name>.asm.rpt

<project name>.blf

<project name>.fit.rpt

<project name>.gclk

<project name>.hps.txt

<project name>.macr

<project name>.pin

<project name>.qsf

<project name>.sof

<project name>.tan.rpt

hardcopy\

<project name>.apc

<project name>_cksum.datasheet

<project name>_cpld.datasheet

<project name>_hcpy.vo

<project name>_hcpy_v.sdo

<project name>_pt_hcpy_v.tcl

<project name>_rba_pt_hcpy_v.tcl

<project name>_target.datasheet

<project name>_violations.datasheet

hardcopy_fpga_prototype\

fpga_<project name>.asm.rpt

fpga_<project name>.cmp.rcf

fpga_<project name>.cmp.xml

fpga_<project name>.db_info

fpga_<project name>.fit.rpt

fpga_<project name>.map.atm

fpga_<project name>.map.rpt

fpga_<project name>.pin

fpga_<project name>.qsf

fpga_<project name>.tan.rpt

fpga_<project name>_cksum.datasheet

fpga_<project name>_cpld.datasheet

fpga_<project name>_hcpy.vo

fpga_<project name>_hcpy_v.sdo

fpga_<project name>_pt_hcpy_v.tcl

fpga_<project name>_rba_pt_hcpy_v.tcl

fpga_<project name>_target.datasheet

fpga_<project name>_violations.datasheet

db_export\

<project name>.db_info

<project name>.map.atm

<project name>.map.hdbx

```

After creating the migration database with the HardCopy Timing Optimization Wizard, you must compile the design before generating the project archive. You will receive an error if you create the archive before compiling the design.

## Static Timing Analysis

In addition to performing timing analysis, the Quartus II software also provides all of the requisite netlists and Tcl scripts to perform static timing analysis (STA) using the Synopsys STA tool, PrimeTime. The following files, necessary for timing analysis with the PrimeTime tool, are generated by the HardCopy Files Wizard:

- `<project name>_hcpy.vo`—Verilog HDL output format

- `<project name>_hcpy_v.sdo`—Standard Delay Format Output File

- `<project name>_pt_hcpy_v.tcl`—Tcl script

These files are available in the `<project name>\hardcopy` directory. PrimeTime libraries for the HardCopy Stratix and Stratix devices are included with the Quartus II software.

Use the HardCopy Stratix libraries for PrimeTime to perform STA during timing analysis of designs targeted to HARDCOPY\_FPGA\_PROTOTYPE device.

For more information about static timing analysis, refer to the *Classic Timing Analyzer* and the *Synopsys PrimeTime Support* chapters in volume 3 of the *Quartus II Handbook*.

## Early Power Estimation

You can use PowerPlay Early Power Estimation to estimate the amount of power your HardCopy Stratix or HardCopy APEX device will consume. This tool is available on the Altera website. Using the Early Power Estimator requires some knowledge of your design resources and specifications, including:

- Target device and package

- Clock networks used in the design

- Resource usage for LEs, DSP blocks, PLL, and RAM blocks

- High speed differential interfaces (HSDI), general I/O power consumption requirements, and pin counts

- Environmental and thermal conditions

### HardCopy Stratix Early Power Estimation

The PowerPlay Early Power Estimator provides an initial estimate of  $I_{CC}$  for any HardCopy Stratix device based on typical conditions. This calculation saves significant time and effort in gaining a quick understanding of the power requirements for the device. No stimulus vectors are necessary for power estimation, which is established by the clock frequency and toggle rate in each clock domain.

This calculation should only be used as an estimation of power, not as a specification. The actual  $I_{CC}$  should be verified during operation because this estimate is sensitive to the actual logic in the device and the environmental operating conditions.

For more information about simulation-based power estimation, refer to the *Power Estimation and Analysis* Section in volume 3 of the *Quartus II Handbook*.

On average, HardCopy Stratix devices are expected to consume 40% less power than the equivalent FPGA.

### HardCopy APEX Early Power Estimation

The PowerPlay Early Power Estimator can be run from the Altera website in the device support section

(<http://www.altera.com/support/devices/dvs-index.html>). You cannot open this feature in the Quartus II software.

With the HardCopy APEX PowerPlay Early Power Estimator, you can estimate the power consumed by HardCopy APEX devices and design systems with the appropriate power budget. Refer to the web page for instructions on using the HardCopy APEX PowerPlay Early Power Estimator.

HardCopy APEX devices are generally expected to consume about 40% less power than the equivalent APEX 20KE or APEX 20KC FPGA devices.

### Tcl Support for HardCopy Stratix

The Quartus II software also supports the HardCopy Stratix design flow at the command prompt using Tcl scripts.

For details on Quartus II support for Tcl scripting, refer to the *Tcl Scripting* chapter in volume 2 of the *Quartus II Handbook*.

## Targeting Designs to HardCopy APEX Devices

Beginning with version 4.2, the Quartus II software supports targeting designs to HardCopy APEX device families. After compiling your design for one of the APEX 20KC or APEX 20KE FPGA devices supported by a HardCopy APEX device, run the HardCopy Files Wizard to generate the necessary set of files for HardCopy migration.

The HardCopy APEX device requires a different set of design files for migration than HardCopy Stratix. **Table 5–5** shows the files collected for HardCopy APEX by the HardCopy Files Wizard.

**Table 5–5. HardCopy APEX Files Collected by the HardCopy Files Wizard**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre> &lt;project name&gt;.tan.rpt &lt;project name&gt;.asm.rpt &lt;project name&gt;.fit.rpt &lt;project name&gt;.hps.txt &lt;project name&gt;.map.rpt &lt;project name&gt;.pin &lt;project name&gt;.sof &lt;project name&gt;.qsf &lt;project name&gt;_cksum.datasheet &lt;project name&gt;_cpId.datasheet &lt;project name&gt;_hcpy.vo &lt;project name&gt;_hcpy_vsdo &lt;project name&gt;_pt_hcpy_vtcl &lt;project name&gt;_rba_pt_hcpy_vtcl &lt;project name&gt;_target.datasheet &lt;project name&gt;_violations.datasheet </pre> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Refer to “[Generating the HardCopy Design Database](#)” on page 5–21 for information about generating the complete set of deliverables required for migrating the design to a HardCopy APEX device. After you have successfully run the HardCopy Files Wizard, you can submit your design archive to Altera to implement your design in a HardCopy device. You should contact Altera for more information about this process.

## Conclusion

The methodology for designing HardCopy Stratix devices using the Quartus II software is the same as that for designing the Stratix FPGA equivalent. You can use the familiar Quartus II software tools and design flow, target designs to HardCopy Stratix devices, optimize designs for higher performance and lower power consumption than the Stratix FPGAs, and deliver the design database for migration to a HardCopy Stratix device. Compatible APEX FPGA designs can migrate to HardCopy APEX after compilation using the HardCopy Files Wizard to archive the design files. Submit the files to the HardCopy Design Center to complete the back-end migration.

## Related Documents

For more information, refer to the following documentation:

- The *HardCopy Series Design Guidelines* chapter in volume 1 of the *HardCopy Series Handbook*.

- The *HardCopy Series Back-End Timing Closure* chapter in volume 1 of the *HardCopy Series Handbook*.

## Document Revision History

**Table 5–6. Document Revision History**

| Date and Document Version | Changes Made                                                                                                                                            | Summary of Changes |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| September 2008 v3.4       | Updated chapter number and metadata.                                                                                                                    | —                  |

| June 2007 v3.3            | Updated with the current Quartus II software version 7.1 information.                                                                                   | —                  |

| December 2006 v3.2        | Updated revision history.                                                                                                                               | —                  |

| March 2006                | Formerly chapter 20; no content change.                                                                                                                 | —                  |

| October 2005 v3.1         | <ul style="list-style-type: none"> <li>● Updated for technical contents for Quartus II 5.1 release</li> <li>● Minor edits</li> </ul>                    | Minor edits.       |

| May 2005 v3.0             | Added PowerPlay early Power estimator information.                                                                                                      | —                  |

| January 2005 v2.0         | This revision was previously the <i>Quartus® II Support for HardCopy Devices</i> chapter in the <i>Quartus II Development Software Handbook, v4.1</i> . | —                  |

| August 2003 v1.1          | Overall edit; added Tcl script appendix.                                                                                                                | —                  |

| June 2003 v1.0            | Initial release of Chapter 20, Quartus II Support for HardCopy Stratix Devices.                                                                         | —                  |