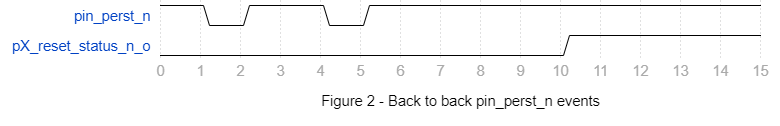

The pX_reset_status_n_o signal from the R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express includes an accumulative characteristic related to the number of back-to-back pin_perst_n assertions.

Each back-to-back pin_perst_n event will be queued and executed one after the other, affecting the total time it takes for the R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express to come out of reset and de-assert the pX_reset_status_n_o signal.

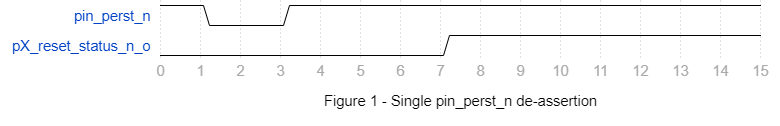

Figure 1 shows the R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express behavior when a single pin_perst_n assertion is issued from the host. Figure 2 shows the accumulative characteristic when multiple pin_perst_n assertions are issued.

The R-Tile Avalon® Streaming Intel® FPGA IP for PCI Express User Guide has been updated to include this information starting with version 22.2.