Critical Issue

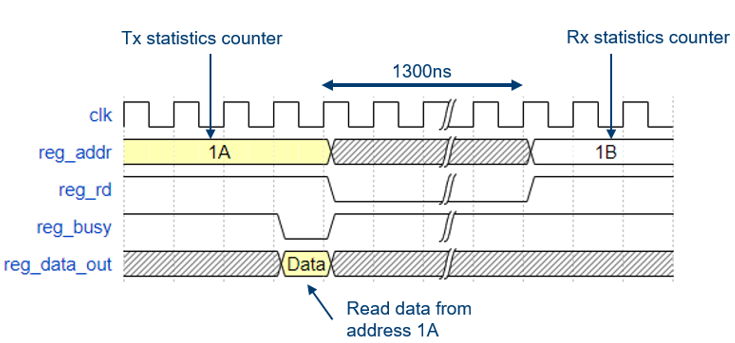

Due to a problem in the Intel® Quartus® Prime Software version 19.1 and 19.2, inconsistent CSR latency will be observed during back-to-back interleaved reads between TX and RX statistics counters in the Triple-Speed Ethernet Intel® FPGA IP operating in 10Mbps speed mode.

To work around this problem, add interval of more than 1300ns between any Tx path statistics counter read to Rx path statistics counter read.

This problem has been fixed starting in the Intel® Quartus® Prime Pro Software version 19.3.