During an ATX PLL user re-calibration process in an Intel® Arria® 10 device, there will be momentarily increased TX jitter and BER risk on the neighboring channel. The ATX PLLs placement location that violates the "skip 6" ATX PLL spacing requirement rule indicated in "Intel® Arria 10 Transceiver PHY User Guide" will observe this failure. The primary application and protocol that might be impacted is the OTN protocol.

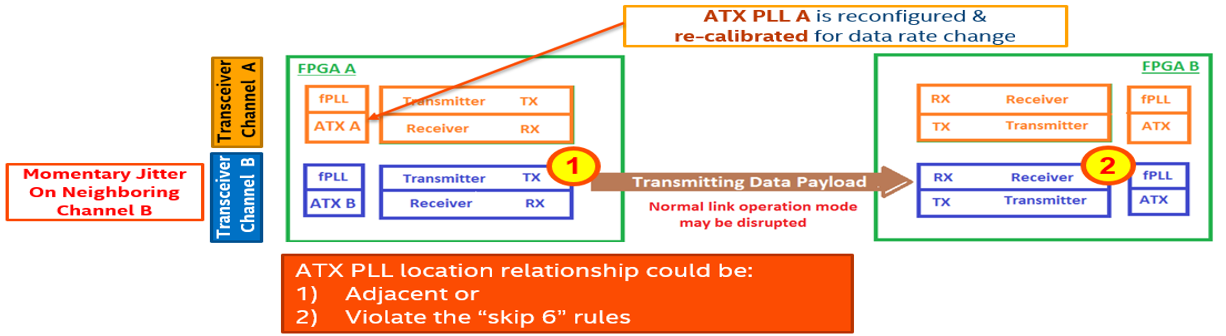

By referring to the example diagram below, when ATX PLL A is being re-calibrated, there will be a risk on the neighboring channel that is clocked by ATX PLL B, which is in normal data transmission mode (user mode):

- Neighboring TX channel with momentary increased TX jitter.

- BER risk on the far end neighboring RX channel.

To avoid this issue, you must follow the ATX PLL-to-ATX PLL Spacing Guidelines in the Intel® Arria 10 Transceiver PHY User Guide. If the spacing requirement cannot be followed, you need to create a pre-calibration IP (by user) as a workaround.

The pre-calibration solution is to avoid the user recalibration process of ATX PLL towards the neighboring channel that is clocked by another ATX PLL during data transmission mode. Follow the steps below to implement the functionality.

The overall pre-calibration and reload flow is separated into two stages:

Stage 1: Store the “Pre-calibrated Diff MIF” value of the ATX PLL before data transmission mode

Perform once after system boot-up and before actual data transmission mode:

- Reconfigure the ATX PLL to the desired data rate and note down the "Diff MIF" information.

- Re-calibrate ATX PLL (whichever ATX PLL is used).

- Record and store the pre-calibrated value in memory (can be M20K).

- Record the reconfiguration of "Diff MIF" content in the same memory space.

- Reconfigure to other data rates and repeat steps 2. to 4.

- Move on to other channels that require a rate switch. Repeat steps 2. to 5.

Stage 2: Reload the “Pre-calibrated Diff MIF” value during the dynamic reconfiguration process.

During the data transmission mode:

- Reload the “Diff MIF pre-calibrated” value from memory to ATX PLL (This step skips the ATX PLL recalibration).

- Start normal channel operation.

Note:

- The reloading sequence is to avoid ATX PLL user recalibration.

- TX / RX PMA channel reconfiguration process can be done before or after the reload process.

- Transceiver channels are held in reset during the entire reloading sequence.