The MegaWizard™ Plug-in Manager does not have an option to select ATX PLL while creating Ethernet MAC with 1000BASE-X/SGMII PCS and PMA. Stratix® IV GX/GT devices have an additional Auxiliary Transmit (ATX) PLL which can be used in Ethernet MAC 1000BASE-x transceivers. The steps below show you how to use ATX PLL in transceiver design.

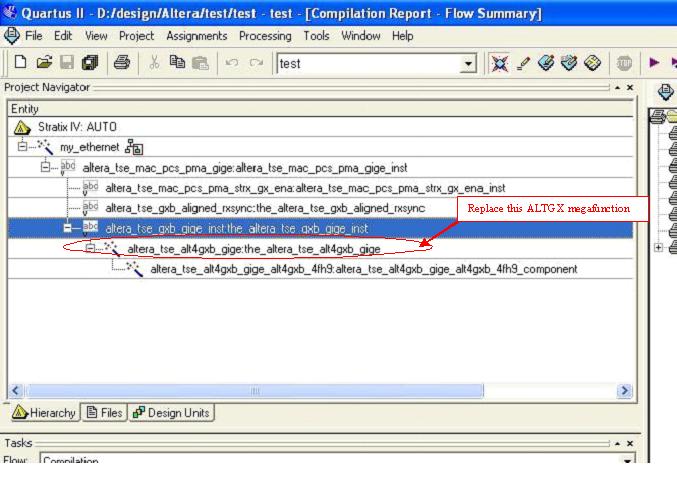

1. To use the ATX PLL in Ethernet MAC with 1000BASE-X/SGMII PCS and PMA design, you have to run your design in Quartus. Expand all the hierarchy in your design after Analysis & synthesis; you'll see the AltGX Megafunction within your Ethernet MAC IP.

2. You can open the ALTGX core with Megawizard Plug-in Manager by double click on it. You can see all the settings made by Megawizard at this point. Unfortunately, the use ATX PLL option (under PLL settings) is grayed out.

3. Go through all the pages on Megawizard plug-in Manager and copy all the setting made by Megawizard on ALTGX. Close Megawizard Manager.

4. The next step is to create a new ALTGX megafunction with ATX PLL selected. Open Megawizard Plug-in Manager again and this time create a new AltGX megafunction, (located under IO/ALTGX). Use all the settings copied on step 3. However this time, select "use ATX PLL".

5. Generate the new ALTGX Megafunction.

6. Locate and open the design file which instantiate ALTGX in Ethernet IP. In this case the file is "altera_tse_gxb_gige_inst.v". Replace the old ALTGXB with the new ALTGXB with ATX PLL generated on step 5.

Note: the new ALTGX does not have 'fixedclk' and 'fixedclk_fast' ports. Be sure to comment them out.

The code for ATXPLL looks like this after modification:

generate if ( DEVICE_FAMILY == "STRATIXIV" || DEVICE_FAMILY == "HARDCOPYIV")

begin

// altera_tse_alt4gxb_gige the_altera_tse_alt4gxb_gige // ALTGXB without ATX PLL

my_ALTGX_with_ATXPLL the_altera_tse_alt4gxb_gige // ALTGXB with ATX PLL

(

.cal_blk_clk (cal_blk_clk),

//.fixedclk(wire_reconfig_clk),

//.fixedclk_fast(1'b0),

.gxb_powerdown (gxb_powerdown),

7. Recompile the design. Confirm the changes in the fitter report.

The figure below shows the location of AltGX core, "altera_tse_alt4gxb_gige", within TSE megacore “my_ethernet”.