When generating an output clock frequency with C-counter exceeding 512, a post-scale counter cascading is implemented. If you are generating a MIF/HEX from the ALTPLL Intel® FPGA IP where the C-counter exceeds 512, cascaded C-counter is not supported. After reconfiguration, you may see that output clock frequency is incorrect.

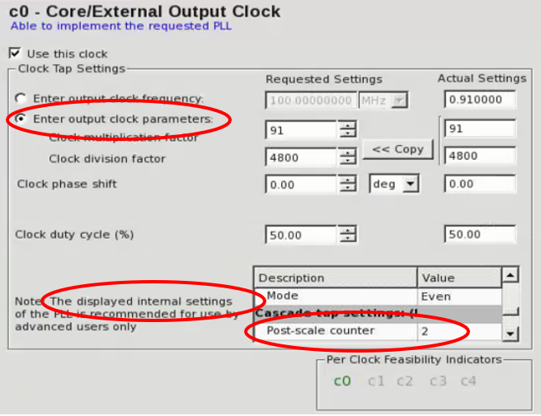

Enable Enter output clock parameters in the ALTPLL Intel® FPGA IP and manually adjust the output clock parameters. Ensure that the C-counter does not exceed the value of 512 and the internal setting isn't injecting post-scale counter cascading before generating the MIF/HEX file as shown in Figure 1.

Figure 1.

As an alternative, cascading of PLLs in normal or direct mode through the Global Clock (GCLK) network can be used to achieve the desired output clock frequency.