A newer version of this document is available. Customers should click here to go to the newest version.

2.1. Clock Signals

2.2. Reset Signals

2.3. TX MII Interface (64b/66b)

2.4. RX MII Interface (64b/66b)

2.5. Status Interface for 64b/66b Line Rate

2.6. TX Interface (8b/10b)

2.7. RX Interface (8b/10b)

2.8. Status Interface for 8b/10b Line Rate

2.9. Serial Interface

2.10. CPRI PHY Reconfiguration Interface

2.11. Datapath Avalon Memory-Mapped Interface

2.12. PMA Avalon Memory-Mapped Interface

4.4. Dynamic Reconfiguration Settings

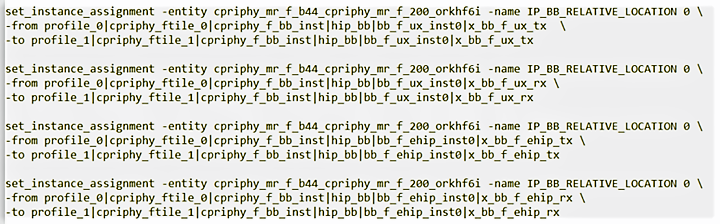

When you generate the IP, the UX transceiver and EHIP relative location assignment of the sub profiles (profile 1 onwards) are generated at the IP QIP file. The value of these assignments is 0 from the profile 0 (power up).

Figure 9. Sub Profile Relative Location Assignment

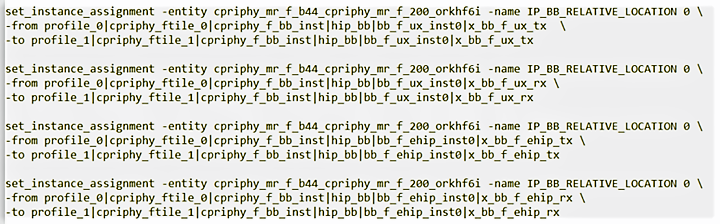

When you generate the IP, the necessary IP reconfiguration assignments are generated in IP QIP file. Brief explanation of these assignments:

- Create a reconfiguration group using the IP_RECONFIG_GROUP_TYPE assignment.

- Assign all the profiles (power up and sub) to the above reconfiguration group using the IP_RECONFIG_GROUP assignment.

- Specify the start-up profile using the IP_RECONFIG_GROUP_STARTUP_INSTANCE ON assignment. By default, the start-up profile is the power up profile.

- Specify the shared sip instance of the IP using the IP_RECONFIG_GROUP_SHARED_SIP ON assignment. This must always be the power up profile.

- Specify the clocking master instance of the IP using the IP_RECONFIG_GROUP_MASTER_CLOCK_CHANNEL assignment. This must always be the power up profile.

- Assign all profiles (power up and sub) with a relative reconfig ID using the IP_RECONFIG_ID assignment.

For more information on the dynamic reconfiguration settings, refer to the F-Tile Dynamic Reconfiguration Suite Intel® FPGA IP User Guide.