Visible to Intel only — GUID: GUID-71A0A574-1F64-48F4-A620-9783B73F691C

Visible to Intel only — GUID: GUID-71A0A574-1F64-48F4-A620-9783B73F691C

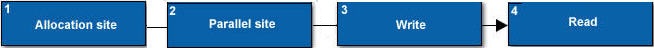

Data Communication

Occurs when a task writes a value that a different task reads.

ID |

Code Location |

Description |

|---|---|---|

1 |

Allocation site |

If present, represents the location and associated call stack when the memory block was allocated. |

2 |

Parallel site |

If present, represents the location and associated call stack of the parallel site containing the Data Communication problem. |

3 |

Write |

Represents the instruction and associated call stack where the memory was written. |

4 |

Read |

Represents the instruction and associated call stack where the memory was read in a different task execution. |

Example

In this example, the write to the heap variable in task1 might occur either before or after the read in task2.

void problem()

{

int* pointer = new int; // Allocation site

ANNOTATE_SITE_BEGIN(datacomm_site1); // Begin parallel site

ANNOTATE_TASK_BEGIN(task1);

*pointer = 999; // Write

ANNOTATE_TASK_END();

ANNOTATE_TASK_BEGIN(task2);

assert(*pointer == 999); // Read

ANNOTATE_TASK_END();

ANNOTATE_SITE_END();

}

In this example, each task execution reads the variable communication, adds one to its value, and writes the result back to the variable. The write in each task execution might occur either before or after the read in the other task instance execution.

void data_communication()

{

ANNOTATE_SITE_BEGIN(site); // Parallel site

for (int i = 0; i < 2; i++) {

ANNOTATE_TASK_BEGIN(task); // Write and Read in different task execution

communication++; /* data communication */

ANNOTATE_TASK_END();

}

ANNOTATE_SITE_END();

}

Possible Correction Strategies

If two accesses to the same memory must occur in a specific order, then the accesses must not be in different task executions in a single site execution. You will have to change the structure of your sites and tasks.

If the order of memory modifications in two task executions is not important, but the executions of the modifications must not occur simultaneously, use locks to synchronize them.

Induction and reduction annotations can tell the Dependencies tool about programs where the program behavior will be correct, regardless of the order of the accesses.