# SCC External Architecture Specification (EAS) Revision 0.94

Please read the SCC Documentation Disclaimer on the next page.

Intel Labs solicits and appreciates feedback. If you have comments about this documentation, please email them to <a href="mailto:SCC\_Technical\_Questions@intel.com">SCC\_Technical\_Questions@intel.com</a>.

#### IMPORTANT - READ BEFORE COPYING, DOWNLOADING OR USING

Do not use or download this documentation and any associated materials (collectively, "Documentation") until you have carefully read the following terms and conditions. By downloading or using the Documentation, you agree to the terms below. If you do not agree, do not download or use the Documentation.

USER SUBMISSIONS: You agree that any material, information or other communication, including all data, images, sounds, text, and other things embodied therein, you transmit or post to an Intel website or provide to Intel under this agreement will be considered non-confidential ("Communications"). Intel will have no confidentiality obligations with respect to the Communications. You agree that Intel and its designees will be free to copy, modify, create derivative works, publicly display, disclose, distribute, license and sublicense through multiple tiers of distribution and licensees, incorporate and otherwise use the Communications, including derivative works thereto, for any and all commercial or non-commercial purposes.

THE DOCUMENTATION IS PROVIDED "AS IS" WITHOUT ANY EXPRESS OR IMPLIED WARRANTY OF ANY KIND INCLUDING WARRANTIES OF MERCHANTABILITY, NONINFRINGEMENT, OR FITNESS FOR A PARTICULAR PURPOSE. Intel does not warrant or assume responsibility for the accuracy or completeness of any information, text, graphics, links or other items contained within the Documentation.

IN NO EVENT SHALL INTEL OR ITS SUPPLIERS BE LIABLE FOR ANY DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, LOST PROFITS, BUSINESS INTERRUPTION, OR LOST INFORMATION) ARISING OUT OF THE USE OF OR INABILITY TO USE THE DOCUMENTATION, EVEN IF INTEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. SOME JURISDICTIONS PROHIBIT EXCLUSION OR LIMITATION OF LIABILITY FOR IMPLIED WARRANTIES OR CONSEQUENTIAL OR INCIDENTAL DAMAGES, SO THE ABOVE LIMITATION MAY NOT APPLY TO YOU. YOU MAY ALSO HAVE OTHER LEGAL RIGHTS THAT VARY FROM JURISDICTION TO JURISDICTION.

Copyright © 2010, Intel Corporation. All rights reserved.

\*Other names and brands may be claimed as the property of others.

# **Table of Contents**

| 1 | Revision History                                                   | 6  |

|---|--------------------------------------------------------------------|----|

| 2 | Introduction                                                       | 6  |

| 3 | SCC System Architecture                                            | 7  |

|   | 3.1 Top level                                                      | 7  |

| 4 | SCC Design                                                         | 8  |

|   | 4.1 Overview                                                       | 8  |

|   | 4.1.1 Top level description                                        | 8  |

|   | 4.1.2 Tile level description                                       | 8  |

|   | 4.2 Functional Unit Descriptions                                   | 9  |

|   | 4.2.1 P54C IA core                                                 | 9  |

|   | 4.2.2 L2 Cache                                                     | 10 |

|   | 4.2.3 LMB (Local Memory buffer)                                    | 10 |

|   | 4.2.4 DDR3 Memory Controllers                                      | 10 |

|   | 4.2.5 LUT (Lookup Table)                                           | 10 |

|   | 4.2.6 MIU (Mesh Interface Unit)                                    | 10 |

|   | 4.2.6.1 Configuration Registers within Configuration Block         | 12 |

|   | 4.2.6.2 Configuration Registers                                    | 13 |

|   | 4.2.6.2.1 Global Clock Unit (GCU) Configuration Register           | 14 |

|   | 4.2.6.2.2 GCU (Global Clocking Unit) and CCF (Clock Crossing FIFO) | 16 |

|   | 4.2.6.2.3 Core Configuration Registers                             | 17 |

|   | 4.2.6.2.4 L2 Cache Configuration Register                          | 20 |

|   | 4.2.6.3 CRB – Sensor Register (rw)                                 | 20 |

|   | 4.2.7 Traffic Generator                                            | 20 |

| 5 | SCC Power Controller (VRC)                                         | 21 |

| 6 | SCC Mesh                                                           | 22 |

|   | 6.1 Router (RXB)                                                   | 22 |

|   | 6.2 Packet Structure and Flit Types                                | 22 |

|   | 6.3 Flow Control in SCC                                            | 22 |

|   | 6.4 Error Checking                                                 | 23 |

| 7 | Dynamic Frequency and Power Management                             | 24 |

|   | 7.1 Clock Distribution                                             | 25 |

| 8 | SCC Programmability                                                | 25 |

**Intel Labs**

|    | 8.1 Syste | em Memory Map                         | 25 |

|----|-----------|---------------------------------------|----|

|    | 8.2 Syste | em Address Lookup Table (LUT)         | 26 |

|    | 8.2.1     | Address Translation Fields            | 26 |

|    | 8.3 Inter | rupts                                 | 28 |

| 9  | SCC Ope   | ration                                | 28 |

|    | 9.1 Mod   | es of Operation                       | 28 |

|    | 9.1.1     | Processor Mode                        | 28 |

|    | 9.1.2     | Mesh Mode                             | 28 |

|    | 9.2 Rese  | rt                                    | 28 |

|    | 9.2.1     | Hard Reset                            | 28 |

|    | 9.2.2     | Soft Reset                            | 28 |

|    | 9.2.3     | Direct Single Core Reset              | 29 |

|    | 9.2.4     | Direct Single L2 Cache Reset          | 29 |

|    | 9.3 Gene  | eral Hardware Startup Sequence        | 29 |

| 10 | Message   | Passing                               | 29 |

|    | 10.1 Mess | sage Passing Support                  | 29 |

|    | 10.1.1    | Instruction CL1INVMB                  | 29 |

|    | 10.1.2    | Internal Cache Changes                | 29 |

| 11 | Appendix  | C                                     | 31 |

|    | 11.1 Look | xup Table Defaults                    | 31 |

|    | 11.1.1    | Default Map for 64GB of System Memory | 31 |

|    | 11.1.2    | Default Map for 32GB of System Memory | 35 |

|    | 11.1.3    | Default Map for 16GB of System Memory | 38 |

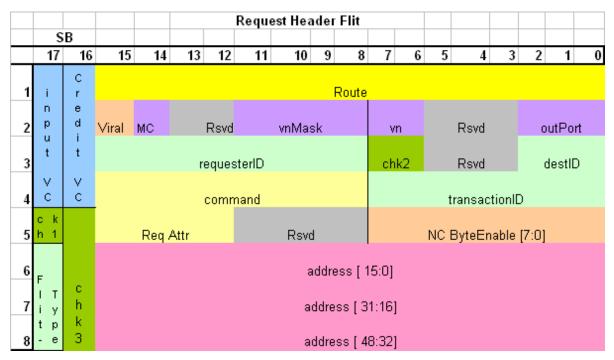

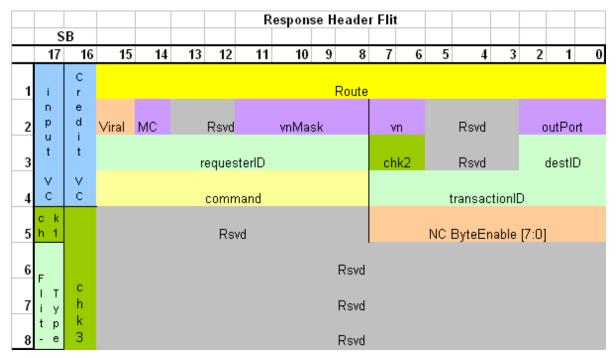

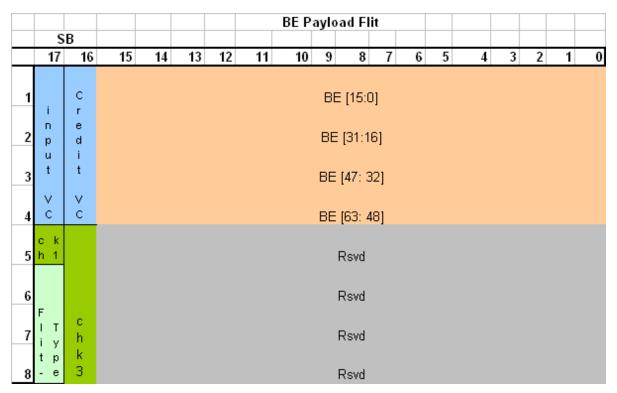

|    | 11.2 Rout | er Flit Structures                    | 41 |

|    | 11.3 Rout | er Flit Types                         | 44 |

# **List of Tables**

| Table 1 Revision History                                                                                                                                                                                                                                                                                                                                     | 0      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                                                                                                                                                                                                                                                                              |        |

| Table 3. Global Clock Unit (GCU) Configuration Register                                                                                                                                                                                                                                                                                                      |        |

| Table 4 Tile Frequency Settings for Router Clock of 800MHz                                                                                                                                                                                                                                                                                                   |        |

| Table 5 Tile Frequency Settings for Router Clock of 1.6GHz                                                                                                                                                                                                                                                                                                   |        |

| Table 6. Interrupt Request Portion of the Core Configuration Register                                                                                                                                                                                                                                                                                        |        |

| Table 7. Control Portion of the Core Configuration Register                                                                                                                                                                                                                                                                                                  |        |

| Table 8. Status Portion of the Core Configuration Register                                                                                                                                                                                                                                                                                                   |        |

| Table 9 L2 Cache Configuration Register                                                                                                                                                                                                                                                                                                                      |        |

| Table 10. CRB - Sensor Register (rw)                                                                                                                                                                                                                                                                                                                         |        |

| Table 11. Address Translation Fields                                                                                                                                                                                                                                                                                                                         |        |

| Table 12. Memory Type Determined by PCD, PWT, and PMB                                                                                                                                                                                                                                                                                                        | 30     |

| Table 13 Breakdown of LUT Entries for 64GB of System Memory                                                                                                                                                                                                                                                                                                  |        |

| Table 14 Default LUT Entries for 64GB Memory Space                                                                                                                                                                                                                                                                                                           |        |

| Table 15 Breakdown of LUT Entries for 32GB of System Memory                                                                                                                                                                                                                                                                                                  | 35     |

| Table 16 Default LUT Entries for 32GB of System Memory                                                                                                                                                                                                                                                                                                       | 37     |

| Table 17 Breakdown of LUT Entries for 16GB of System Memory                                                                                                                                                                                                                                                                                                  | 38     |

| Table 18 Default LUT Entries for 16GB of System Memory                                                                                                                                                                                                                                                                                                       | 40     |

| Table 19 Router Flit Types                                                                                                                                                                                                                                                                                                                                   | 44     |

|                                                                                                                                                                                                                                                                                                                                                              |        |

| List of Figures                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                                                                                                                                                                                                                                                                              | 7      |

| List of Figures  Figure 1. SCC Top-Level Architecture                                                                                                                                                                                                                                                                                                        |        |

| Figure 1. SCC Top-Level Architecture                                                                                                                                                                                                                                                                                                                         | 8      |

| Figure 1. SCC Top-Level Architecture                                                                                                                                                                                                                                                                                                                         | 8<br>9 |

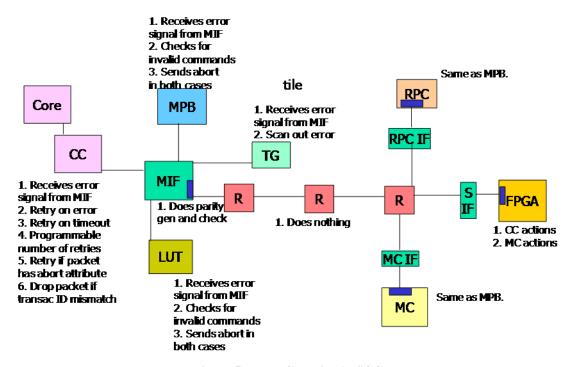

| Figure 1. SCC Top-Level Architecture  Figure 2. SCC Top-Level Block Diagram  Figure 3. Tile Level Block Diagram  Figure 4. Flow Control in SCC  Figure 5. Error Checking in SCC                                                                                                                                                                              |        |

| Figure 1. SCC Top-Level Architecture                                                                                                                                                                                                                                                                                                                         |        |

| Figure 1. SCC Top-Level Architecture Figure 2. SCC Top-Level Block Diagram Figure 3. Tile Level Block Diagram Figure 4. Flow Control in SCC Figure 5. Error Checking in SCC Figure 6. Clock Domains and CCFs Figure 7. Address Translation                                                                                                                   |        |

| Figure 1. SCC Top-Level Architecture                                                                                                                                                                                                                                                                                                                         |        |

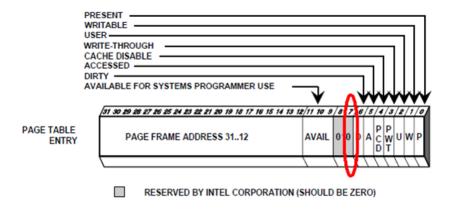

| Figure 1. SCC Top-Level Architecture Figure 2. SCC Top-Level Block Diagram Figure 3. Tile Level Block Diagram Figure 4. Flow Control in SCC Figure 5. Error Checking in SCC Figure 6. Clock Domains and CCFs Figure 7. Address Translation Figure 8 subdestID fields Figure 9. Page Table Entry                                                              |        |

| Figure 1. SCC Top-Level Architecture Figure 2. SCC Top-Level Block Diagram Figure 3. Tile Level Block Diagram Figure 4. Flow Control in SCC Figure 5. Error Checking in SCC Figure 6. Clock Domains and CCFs Figure 7. Address Translation Figure 8 subdestID fields Figure 9. Page Table Entry Figure 10 Request Header Flit                                |        |

| Figure 1. SCC Top-Level Architecture Figure 2. SCC Top-Level Block Diagram Figure 3. Tile Level Block Diagram Figure 4. Flow Control in SCC Figure 5. Error Checking in SCC Figure 6. Clock Domains and CCFs Figure 7. Address Translation Figure 8 subdestID fields Figure 9. Page Table Entry Figure 10 Request Header Flit Figure 11 Response Header Flit |        |

| Figure 1. SCC Top-Level Architecture Figure 2. SCC Top-Level Block Diagram Figure 3. Tile Level Block Diagram Figure 4. Flow Control in SCC Figure 5. Error Checking in SCC Figure 6. Clock Domains and CCFs Figure 7. Address Translation Figure 8 subdestID fields Figure 9. Page Table Entry Figure 10 Request Header Flit                                |        |

# 1 Revision History

| Date    | Revision | Author   | Description                                                          |  |

|---------|----------|----------|----------------------------------------------------------------------|--|

| 7/16/09 | 0        | yhoskote | First draft.                                                         |  |

| 9/3/09  | 0.9      | geruhl   | Public release candidate                                             |  |

| 9/16/09 | 0.91     | geruhl   | Added CFG register information                                       |  |

| 11/2/09 | 0.92     | jpheld   | Corrected Interrupts, core register info                             |  |

| 3/9/10  | 0.93     | tkubaska | Some editing, some clarification, added explanations to LUT Defaults |  |

| 3/11/10 | 0.932    | jpheld   | Updated with current information, clarified language.                |  |

| 4/12/10 | 0.933    | mkonow   | Information about subdestID, rmw for config registers, SIF           |  |

| 5/23/10 | 0.94     | gruhl    | Information about the VRC and the GCU                                |  |

**Table 1 Revision History**

# 2 Introduction

The Single-chip Cloud Computer (SCC) is a 48-core Intel Architecture (IA) many-core experimental processor prototype. It is a research chip built to study many-core CPUs, their architectures, and the techniques used to program them. The research has the following goals:

- 1. To demonstrate a shared memory message-passing architecture for a large number of cores and to experiment with its programmability and scalability.

- 2. To design and explore the performance and power characteristics of an on-die 2D mesh fabric.

- 3. To explore the benefits and costs of software-controlled dynamic voltage and frequency scaling for multiple cores.

The IA core on the SCC is based on the P54C core. The 48 cores are placed in a tile formation, two cores to a tile. The tiles are connected by a 6x4 2D fully synchronous mesh fabric with rigorous performance and power requirements.

The SCC has multiple voltage and frequency domains, some configurable at startup, others that may be dynamically varied for application-controlled fine grain dynamic power and performance management.

The SCC die has four on-die memory controllers capable of addressing a total of up to 64GB of external memory. It also has a small amount of fast local memory located in each tile. Message-passing support is provided that use shared regions of local memory or off-die main memory. The SCC has a new memory type and a new processor cache instruction to facilitate memory management.

The entire system is controlled by a board management microcontroller (BMC) that initializes and shuts down critical system functions. It is commonly connected by PCI-Express cable to a PC acting as a Management Console (MCPC).

The SCC runs a variety of applications and boots a Linux OS. A programming environment with various APIs has been developed and is available for the application programmer.

# 3 SCC System Architecture

# 3.1 Top level

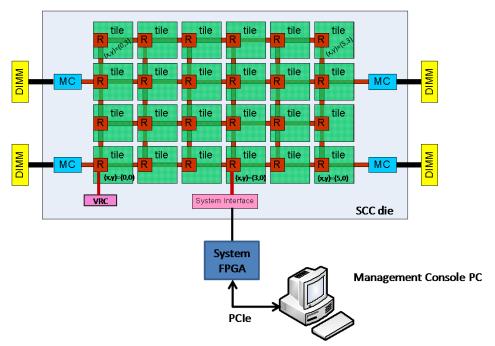

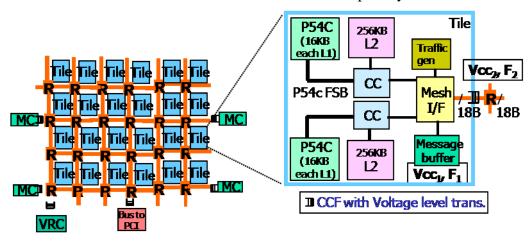

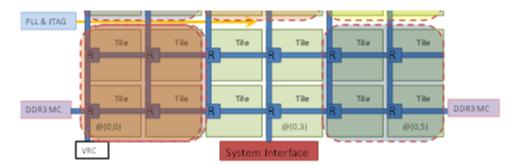

The top level system architecture for the SCC system is shown in <u>Figure 1</u>.

- Programs may be loaded into SCC memory by the Management Console through the system interface and via the SCC on-die mesh.

- The memory on the SCC may be dynamically mapped to the address space of the 48 cores. It may also be mapped to the memory space of the Management Console, for program loading or debug.

- I/O instructions on the SCC processor cores are also mapped to the system interface and by default to the Management Console interface. Programs on the MCPC can capture and display such programmed I/O.

SCC uses four memory controllers at the mesh border. The default boot configuration of memory configuration registers gives each SCC core access to a private memory region on one memory controller and shared access to the local memory buffers located in each tile. One use of this shared memory is to pass messages between cores, for example, to maintain coherency.

Main memory may be remapped to share regions among one or more cores by dynamic reconfiguration of the mappings using the configuration registers in each tile. Thus, shared memory may be off-chip and accessed through the memory controllers, or it may be on-die local memory in the tiles.

Figure 1. SCC Top-Level Architecture

# 4 SCC Design

A brief overview of the design is given in this section.

### 4.1 Overview

### 4.1.1 Top level description

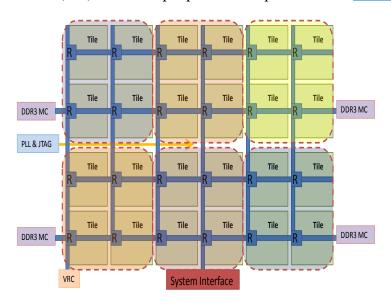

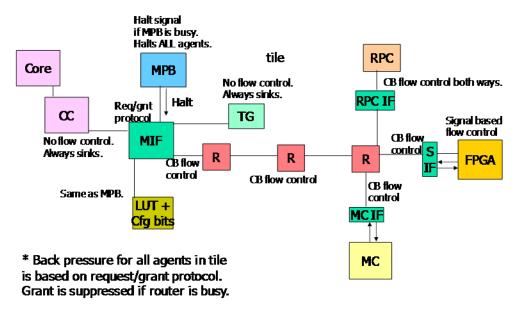

The 6x4 mesh shown in Figure 2. SCC Top-Level Block Diagram connects the following:

- 24 tiles.

- Four on-die memory controllers. Each DDR3 memory controller can address 2 DIMMS, each containing 8GB of memory. This results in a maximum of 64GB of DDR3 memory for the system.

- A voltage regulator controller (VRC). This SCC power controller allows any core or the system interface to adjust the voltage in any of the dotted-line regions shown in the figure plus the voltage for the entire router mesh. This method allows full application control of the power state of the cores.

- An external system interface controller (SIF). To communicate between the controller located on the system board and the router on the mesh network, an external system interface controller (SIF) uses a simple parallel bus protocol. See Section 6.1.

Figure 2. SCC Top-Level Block Diagram

### 4.1.2 Tile level description

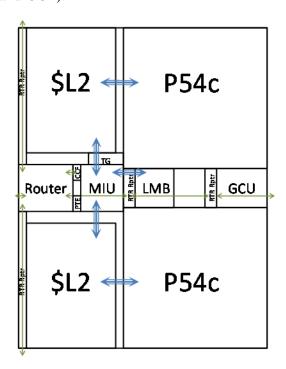

<u>Figure 3. Tile Level Block Diagram</u> shows a more detailed view of an individual tile. Each of the 24 tiles contains the following:

Two P54C-based IA processing cores with associated L1 and L2 caches.

- A five-port crossbar router.

- A traffic generator (TG) for testing the mesh (not software accessible).

- A mesh interface unit (MIU) that handles all memory and message passing requests. The MIU is the sole interface for the tile agents with the router (through the clock crossing FIFO) and the router is the sole interface between tiles.

- Memory lookup tables (LUT).

- A message-passing buffer (MPB), sometimes called the local memory buffer (LMB).

- Assorted clock generation and synchronization circuitry for crossing asynchronous boundaries (GCU and CCF).

Figure 3. Tile Level Block Diagram

# 4.2 Functional Unit Descriptions

### 4.2.1 P54C IA core

The core is a P54C Pentium® design that has been altered to increase the L1 data and instruction cache size to 16KB each. These caches are 8-way set associative. Additionally, the original front side bus-to-cache controller interface (M-unit) has been integrated into the core.

The P54C ISA (instruction set architecture) was extended with a new instruction (CL1INVMB) and a new memory type MPBT) introduced to facilitate the use of message data. All accesses to MPBT data bypass the L2 cache. The new instruction was added to invalidate all L1 cache lines typed as MPBT. These changes were added to facilitate maintaining coherency between caches and message data. Finally, a write combine buffer was added to the M-unit to accelerate the message transfer between cores.

#### 4.2.2 L2 Cache

Each core has its own private 256KB L2 cache and an associated controller. During a miss, the cache controller sends the address to the Mesh Interface Unit (MIU) for decoding and retrieval. Each core can have only one outstanding memory request and will stall on missed reads until data are returned. On missed writes, the processor will continue operation until another miss of either type occurs. Once the data have arrived, the processor continues normal operation. Tiles with multiple outstanding requests can be supported by the network and memory system.

### 4.2.3 LMB (Local Memory buffer)

In addition to the traditional cache structures, a local memory buffer (MPB) capable of fast R/W operations has been added to each tile. This 16KB buffer provides the equivalent of 512 full cache lines of memory. Any core or the system interface can write or read data from these 24 on-die message buffers. One of the intended uses for the MPB is message passing.

### 4.2.4 DDR3 Memory Controllers

The four memory controllers provide a maximum capacity of 64GB of DDR3 memory. This memory physically exists on the SCC board.

Each memory controller supports two unbuffered DIMMs per channel with two ranks per DIMM. The supported DRAM type is DDR3-800 x8 with 1Gb, 2Gb or 4Gb capacity, leading to up to 16GB capacity per channel. The DDR3 protocol includes automatic training, calibration, and compensation as well as periodic refresh of the DRAM. Memory accesses are processed in order, while accesses to different banks and ranks are interleaved to improve throughput.

### 4.2.5 LUT (Lookup Table)

Each core has a lookup table (LUT) which is a set of configuration registers in the Configuration Block (see Section 4.2.6.1 Configuration Registers within Configuration Block) that map a core's physical addresses to the extended memory map of the system. Each LUT contains 256 entries, one for each 16MB segment of the core's 4GB physical memory address space. Each entry can point to any memory location (private memory, local memory buffer, configuration registers, system interface, SCC power controller, or system memory).

LUTs may be programmed by writes through the system interface from the Management Console at any time. They are normally set during the bootstrap process to an initial configuration. After boot, the memory map can be dynamically altered by any core that has a mapping to their location in system address space.

On an L2 cache miss, the MIU looks through the LUT to determine where the memory request should be sent. See <u>Section 8.2</u> <u>System Address Lookup Table (LUT)</u> for a description of the LUT fields and their use in converting a core physical address into a system address.

Although the LUT can be programmed in any way a user sees fit, a default memory map for all system memory sizes has been developed and is located in <u>Section 11 Appendix</u>.

# 4.2.6 MIU (Mesh Interface Unit)

The Mesh Interface Unit (MIU) contains the following:

- Packetizer and De-Packetizer

- Command interpretation and address decode/lookup

- Local configuration registers

- Link level flow control and Credit Management

- Arbiter

The packetizer/de-packetizer translates the data to/from the agents and to/from the mesh. The Data, Command and Address Buffers provide queuing for flit organization. Specifically, the MIU takes a cache miss and decodes the address, using the LUT to map from core address to system address. It then places the request into the appropriate queue. The queues are the following:

- Router->DDR3 request

- Message Passing Buffer access

- Local configuration register access

For traffic coming from the router, the MIU routes the data to the appropriate local destination. The link level flow control ensures flow of data on the mesh using a <u>credit-based</u> protocol. Finally, the arbiter controls tile element access to the MIU at any given time via a round robin scheme.

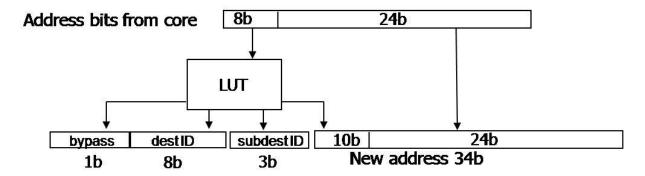

The core reads and writes a 32-bit local address. The top 8 bits of this address directly index the LUT on any cache miss. The LUT returns 22 bits – a 10-bit system address extension, 8-bit tile ID, a 3-bit subdestID, and a bypass bit. The system address is 46 bits – the bypass bit + 3-bit subdestID + 8-bit tile ID + 10-bit address extension + 24 lower bits of the 32-bit core address. Figure 7. Address Translation shows the bit pattern of what is returned from the LUT.

The sub-destination ID (subdestID) defines the port where the packet leaves the router. <u>Table 11.</u> <u>Address Translation Fields</u> lists the values for the subdestID. The tileID gets the packet to the tile and from there, the subdestID can choose a memory controller, the VRC, or the system interface (SIF). The bypass bit specifies local tile memory buffer access.

The lower 34 bits of the 46-bit system address get sent to the destination specified by the tile ID. The tile ID represents the tile coordinates in a Y, X format (4 bits each). For example, the bottom left tile ID is  $0000\ 0000\ (y=0,x=0)$  and the upper right tile ID is  $0011\ 0101\ (y=3,x=5)$ . This code gives the MIU and router all the information it needs to route the 34 bit address plus control and data to the appropriate destination (which may be the local tile).

When the request is in the appropriate tile, the MIU looks at the lower 13 bits of the address to see what operation it will perform. Table 2 is the address table for this operation. For the LUT R/W operations, bits 10:09 control which bank you are accessing and bits 08:03 control the physical address. The remaining operations have the operation specifics (read, write, etc.) automatically sent as part of the command code by the originator of the request. Note that each operation will only R/W a certain number of data bits (located in the least significant bits of the data field).

# 4.2.6.1 Configuration Registers within Configuration Block

| Register Name                | Desired Operation            | SubAddress<br>(12:0)                                 | Valid data<br>bits    |

|------------------------------|------------------------------|------------------------------------------------------|-----------------------|

| LUT register core 1          | R/W LUT 1                    | 1 <mark>0xxx</mark> xxxx <mark>xxxx</mark><br>0x1000 | 22                    |

| LUT register core 0          | R/W LUT 0                    | 0 <mark>1xxx</mark> xxxx <mark>xxxx</mark><br>0x0800 | 22                    |

| Atomic Flag Core1<br>(LOCK1) | R/W Test & Set Core 1 atomic | 0 <mark>0100</mark> 0000 <mark>0000</mark><br>0x0400 | 1                     |

| Atomic Flag Core0<br>(LOCK0) | R/W Test & Set Core 0 atomic | 0 <mark>0010</mark> 0000 <mark>0000</mark><br>0x200  | 1                     |

| Tile ID register             | Read Tile ID config          | 0 <mark>0001</mark> 0000 <mark>0000</mark><br>0x0100 | 11                    |

| Global Clock Unit (GCU)      | R/W GCU config               | 0 <mark>0000</mark> 1000 <mark>0000</mark><br>0x0080 | 26                    |

| Sensor Register              | R/W Thermal Sensor control   | 0 <mark>0000</mark> 0100 <mark>0000</mark><br>0x0040 | 14                    |

| Sensor Register              | Read Thermal Sensor value    | 0 <mark>0000</mark> 0100 <mark>1000</mark><br>0x0048 | 26                    |

| L2 Cache Configuration 0     | R/W L2 Cache 0 config        | 0 <mark>0000</mark> 0010 <mark>0000</mark><br>0x0020 | 14                    |

| L2 Cache Configuration 1     | R/W L2 Cache 1 config        | 0 <mark>0000</mark> 0010 <mark>1000</mark><br>0x0028 | 14                    |

| Core Configuration 0         | R/W Core 0 (P54C) config     | 0 <mark>0000</mark> 0001 <mark>0000</mark><br>0x0010 | 26 (top 14 read only) |

| Core Configuration 1         | R/W Core 1 (P54C) config     | 0 <mark>0000</mark> 0001 <mark>1000</mark><br>0x0018 | 26 (top 14 read only) |

**Table 2 Configuration Registers**

#### 4.2.6.2 Configuration Registers

The tile configuration registers provide a method for applications to control the operating modes of various tile hardware elements. <u>Table 2 Configuration Registers</u> showed how to address these registers. These registers control enabling local reset assertion/de-assertion, local clock divider settings, core initialization and configuration, core interrupt handling, and L2 Cache configuration.

Each SCC core, L2 cache controller, and global clocking unit (GCU) has a dedicated configuration register that is writable by any core or the system interface unit. Additionally, there are test-and-set registers that enable communication protocols (such as message passing) in a multi-processor environment.

On a hard reset, the configuration registers are set to a known safe starting value for each element. The recommended usage is that the user read the configuration register, edit the appropriate bits (keeping the other values) and then write the result back into the register. **Some configuration register controls can result in hard failures.** In all the sections below, the bit positions refer to the location in the data word.

Byte-wise access to the configuration registers is not supported, even though the partial read and write packet formats carry byte enable bits. Programmers should perform a read-modify-write on all 32 bits of a configuration register to ensure that other bits are not mistakenly modified.

<u>Table 3</u> shows the values for the 26 valid bits of the global clock unit (GCU) register. <u>Table 4</u> and <u>Table 5</u> list GCU values for various tile frequencies.

The core configuration registers are described in the next three tables. <u>Table 6</u> shows the interrupt request portion; <u>Table 7</u> shows the control portion; and <u>Table 8</u> shows the status portion.

<u>Table 9</u> shows the values for L2 cache configuration registers. <u>Table 10</u> shows the values for the sensor registers.

#### 4.2.6.2.1 Global Clock Unit (GCU) Configuration Register

| Description                                                                                               | <b>Bit Position</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>Default Setting</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tile Frequency Setting. These bits determine the tile frequency for pre-defined router and memory clocks. | 25:08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 00 0111 0000 1110 0001<br>for router clock = 1.6GHz<br>00 1010 1000 1110 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | for router clock – 800MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Synchronization Reset Enable for L2 0.                                                                    | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| When enabled, the soft reset package pin will be able to reset this unit. Active high.                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Synchronization Reset Enable for L2 1.                                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| When enabled, the soft reset package pin will be able to reset this unit. Active high.                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Synchronization Reset Enable for Core 1.                                                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| When enabled, the soft reset package pin will be able to reset this unit. Active high.                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Synchronization Reset Enable for Core 0 .                                                                 | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| When enabled, the soft reset package pin will be able to reset this unit. Active high.                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reset for L2 1.                                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Direct SW method for resetting this unit. Active high.                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reset for L2 0.                                                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Direct SW method for resetting this unit.<br>Active high.                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reset for Core 1.                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Direct SW method for resetting this unit.<br>Active high.                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reset for Core 0.                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Direct SW method for resetting this unit.<br>Active high.                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                           | Tile Frequency Setting. These bits determine the tile frequency for pre-defined router and memory clocks.  Synchronization Reset Enable for L2 0.  When enabled, the soft reset package pin will be able to reset this unit. Active high.  Synchronization Reset Enable for L2 1.  When enabled, the soft reset package pin will be able to reset this unit. Active high.  Synchronization Reset Enable for Core 1.  When enabled, the soft reset package pin will be able to reset this unit. Active high.  Synchronization Reset Enable for Core 0.  When enabled, the soft reset package pin will be able to reset this unit. Active high.  Reset for L2 1.  Direct SW method for resetting this unit. Active high.  Reset for L2 0.  Direct SW method for resetting this unit. Active high.  Reset for Core 1.  Direct SW method for resetting this unit. Active high.  Reset for Core 0.  Direct SW method for resetting this unit. | Tile Frequency Setting. These bits determine the tile frequency for pre-defined router and memory clocks.  Synchronization Reset Enable for L2 0.  When enabled, the soft reset package pin will be able to reset this unit. Active high.  Synchronization Reset Enable for L2 1.  When enabled, the soft reset package pin will be able to reset this unit. Active high.  Synchronization Reset Enable for Core 1.  When enabled, the soft reset package pin will be able to reset this unit. Active high.  Synchronization Reset Enable for Core 0.  When enabled, the soft reset package pin will be able to reset this unit. Active high.  Reset for L2 1.  Direct SW method for resetting this unit. Active high.  Reset for Core 1.  Direct SW method for resetting this unit. Active high.  Reset for Core 1.  Direct SW method for resetting this unit. Active high.  Reset for Core 0.  Direct SW method for resetting this unit. |

Table 3. Global Clock Unit (GCU) Configuration Register

The router clock is set at either 800MHz or 1.6GHz. When the router clock is 800MHz, the memory clock is also at 800MHz. When the router clock is 1.6GHz, the memory clock is either 800MHz or 1066MHz.

When the router frequency is 800MHz, the default tile frequency is 533MHz. When the router frequency is 1.6GHz, the default tile frequency is 800MHz.

By writing bits 25:08 of the GCU, you can change the tile frequency. Table 4 lists the possible

tile frequencies when the router clock is 800MHz. <u>Table 5</u> lists the possible tile frequencies when the router clock is 1.6GHz.

Bits 11:08 are the tile divider setting. The tile frequency in both tables is 1.6GHz divided by the tile divider +1. Bits 25:19 are the router clock ratio setting, and bits 18:12 are the tile clock ratio setting. They control correct synchronous operation of both router and tile clocks. The router clock ratio setting and the tile clock ratio setting are not accessible via a register; they are accessible from the JTAG interface.

| Tile Frequency (MHz) | GCU Config Setting [25:08] |

|----------------------|----------------------------|

| 800                  | 00 0111 0000 1110 0001     |

| 533                  | 00 1010 1000 1110 0010     |

| 400                  | 00 1110 0000 1110 0011     |

| 320                  | 01 0001 1000 1110 0100     |

| 266                  | 01 0101 0000 1110 0101     |

| 228                  | 01 10001 000 1110 0110     |

| 200                  | 01 11000 000 1110 0111     |

| 178                  | 01 11111 000 1110 1000     |

| 160                  | 10 00110 000 1110 1001     |

| 145                  | 10 01101 000 1110 1010     |

| 133                  | 10 10100 000 1110 1011     |

| 123                  | 10 11011 000 1110 1100     |

| 114                  | 11 00010 000 1110 1101     |

| 106                  | 11 01001 000 1110 1110     |