Volume 09

Published, November 9, 2005

005 ISSN 1535-864X

DOI: 10.1535/itj.0904

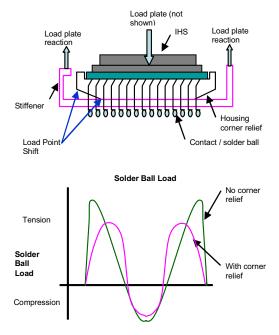

Issue 04

# Intel® Technology Journal

### Electronic Package Technology Development

Electronic package technology has advanced rapidly over the past two decades to meet the demands of faster and more powerful microprocessors with hundred of millions of transistors. This issue of Intel Technology Journal (Volume 9, Issue 4) focuses on Intel's challenges in the area of package technology development.

| Advanced Package Technologies Materials Technologies for Thermomec<br>for High-Performance Systems Management of Organic Package                                        |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                         |    |

| Power Delivery for High-<br>Performance Microprocessors<br>Performance Microprocessors<br>Performance Microprocessors<br>Challenges and Future Trends                   | ıe |

| Nano and Micro Technology-Based<br>Next-Generation Package-Level<br>Cooling Solutions<br>Advanced Fault Isolation and Failure A<br>Techniques for Future Package Techno | -  |

| Finding Solutions to the Challenges in Future Package Technologies fo<br>Package Interconnect Reliability Wireless Communication System                                 |    |

More information, including current and past issues of Intel Technology Journal, can be found at: http://developer.intel.com/technology/itj/index.htm Volume 09

Published, November 9, 2005

05 ISSN 1535-864X

4X DOI: 10.1535/itj.0904

Issue 04

# Intel® Technology Journal

Electronic Package Technology Development

### **Articles**

| Preface                                                                                                  | iii |

|----------------------------------------------------------------------------------------------------------|-----|

| Foreword                                                                                                 | v   |

| Technical Reviewers                                                                                      | vii |

| Advanced Package Technologies for High-Performance Systems                                               | 259 |

| Power Delivery for High-Performance Microprocessors                                                      | 273 |

| Nano and Micro Technology-Based Next-Generation Package-Level<br>Cooling Solutions                       | 285 |

| Finding Solutions to the Challenges in Package Interconnect Reliability                                  | 297 |

| Materials Technologies for Thermomechanical Management<br>of Organic Packages                            | 309 |

| Pentium <sup>®</sup> 4 Processor High-Volume Land-Grid-Array Technology:<br>Challenges and Future Trends | 325 |

| Advanced Fault Isolation and Failure Analysis Techniques<br>for Future Package Technologies              | 337 |

| Future Package Technologies for Wireless Communication Systems                                           | 353 |

### THIS PAGE INTENTIONALLY LEFT BLANK

### Preface

### Electronic Package Technology Development By Lin Chao Publisher, *Intel Technology Journal*

Today's broad spectrum of electronic products such as microprocessors, chipsets, flash memories, wireless radios, and embedded logic all require cost-effective electronic packages. The electronic package is a space transformer between chips and low-cost motherboards.

Electronic package technology has advanced rapidly over the past two decades to meet the demands of faster and more powerful microprocessors with hundred of millions of transistors. The newest microprocessor products are dual core, providing two execution cores in one physical microprocessor. Multi-cores will continue as a trend from dual cores and will require highly advanced electronic package technology. Thermal-heat dissipation, signal interconnects, and higher densities have also necessitated many changes. Significant advances have been made in the areas of mechanical integrity, new materials, signal integrity, power delivery, power dissipation, and thermal sciences.

The eight papers in this Intel Technology Journal (Volume 9, Issue 4) present an in-depth discussion on Intel's latest electronic package technologies. They highlight the technical challenges engineers face now and in the future, and address the many hurdles faced by the semiconductor industry to achieve the next level of performance along the curve of Moore's Law.

The first paper provides an overview of advanced package technologies for today's highperformance computers. The next four papers look at electrical, thermal, mechanical, and new materials advances. The challenge of supplying the appropriate power at the right time, in a costeffective and efficient method, is discussed in the second paper on power delivery. Then there is the need to cool the package and dissipate this power. The third paper on thermal technologies outlines some novel nano and micro technologies currently being investigated at Intel to mitigate the impact of power and power-density distribution across the chip. The component typically undergoes different levels of static and dynamic thermal and mechanical loads. The fourth paper on interconnect reliability provides an insight into the mechanical response and integrity of the silicon, package, and board. The fifth paper follows with a description of package materials technologies to address increasingly demanding thermo-mechanical conditions.

The next three papers look at present and future package technologies. In the sixth paper, the Pentium<sup>®</sup> 4 Processor's Land-Grid-Array (LGA) package technology is discussed. The seventh paper looks at some of the metrologies, tools, and techniques to better quantify the mechanical response for fault isolation and failure analysis in current and future package technologies. Finally, in the eighth paper, new concepts in package technologies for wireless and RF are described.

<sup>&</sup>lt;sup>®</sup>Pentium is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

### THIS PAGE INTENTIONALLY LEFT BLANK

### Foreword

### **Challenges and Opportunities in Electronic Package Technology Development**

By Nasser Grayeli Vice President, Technology and Manufacturing Group Director, Assembly Technology Development Intel Corporation

In this issue of Intel Technology Journal (Volume 9, Issue 4) we focus on challenges in the area of package technology development.

Historically, the primary function of electronic packages has been to facilitate the electrical connectivity of silicon chips to a printed circuit board, while at the same time providing mechanical protection to the chip from environmental conditions. For several decades, Intel's microprocessor technology and performance has followed Moore's Law. Microelectronic package technology has facilitated this evolution by providing the required technology solutions that support the overall microprocessor performance treadmill.

Electronic products are pervasive in multiple consumer and business markets such as traditional PCs, enterprise servers, and communication devices. These markets require technical solutions that are extremely diverse as they support different products such as CPUs, chipsets, radios, flash memories, and embedded logic. Microelectronic packages have adapted to meet the diverse needs of these markets.

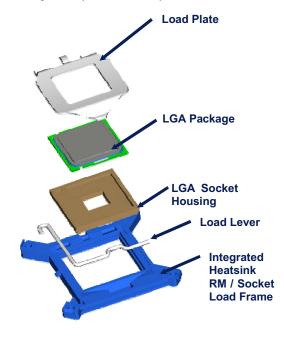

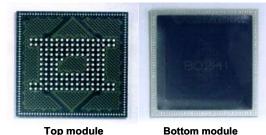

The advances in manufacturing of semiconductor devices and packages over the past few decades have resulted in faster, more powerful, and cheaper computing devices containing hundreds of millions of transistors. Cost pressures, increasing functionality, and market competitive pressures demand continuous innovation in package technology. Packages for current Intel products include innovative and advanced technology solutions such as the world's first high-volume land grid array (LGA) socket for organic substrates, ultra slim packages utilizing thinned Si chips, package-on-package stacking, novel power delivery, and advance heat dissipation architectures. Intel's development methodology focuses on the global optimization of the overall interconnect hierarchy including the silicon, package, socket, and board, rather than the local optimization of individual components of the platform. This methodology has allowed Intel's package solutions for microelectronic devices to lead the industry.

This November 2005 issue of Intel Technology Journal provides a broad perspective of the challenges and opportunities facing engineers working on microelectronic packages as they strive to offer cost-effective solutions for Intel products. Recent advances and future challenges will be discussed with reference to opportunities in electronic materials, polymer science, interfacial mechanics and fracture, computational and experimental methods, power delivery, signal integrity, and thermal sciences. Some of the papers will provide insight into recent technical advances in support of microelectronic packages at Intel, while others will focus more on anticipated future trends.

While one issue of a journal cannot cover all of the individual and cross-disciplinary areas of broad technologies like microelectronic packages, the intent of this issue is to provide some basic insights into Intel's solutions in this area. I hope the reader will enjoy and benefit from the exciting content of this issue!

### **Technical Reviewers**

Pardeep Bhatti, Technology and Manufacturing Group Ted Burton, Digital Enterprise Group Chia-Pin Chiu, Technology and Manufacturing Group Luiz Franca-Neto, Mobility Group Zezhong Fu, Technology and Manufacturing Group Paul J. Gwin, Channel Platforms Group Tanay Karnik, Corporate Technology Group Frank Liang, Technology and Manufacturing Group Ravi Mahajan, Technology and Manufacturing Group Bob Sankman, Technology and Manufacturing Group Ward Scott, Technology and Manufacturing Group David W. Song, Technology and Manufacturing Group Ram Viswanath, Technology and Manufacturing Group Quat Vu, Technology and Manufacturing Group

### THIS PAGE INTENTIONALLY LEFT BLANK

### Advanced Package Technologies for High-Performance Systems

Debendra Mallik, Technology and Manufacturing Group, Intel Corporation Kaladhar Radhakrishnan, Technology and Manufacturing Group, Intel Corporation Jiangqi He, Technology and Manufacturing Group, Intel Corporation Chia-Pin Chiu, Technology and Manufacturing Group, Intel Corporation Telesphor Kamgaing, Technology and Manufacturing Group, Intel Corporation Damion Searls, Technology and Manufacturing Group, Intel Corporation James D. Jackson, Technology and Manufacturing Group, Intel Corporation

Index words: package, power delivery, signal integrity, thermal management, RF package

### ABSTRACT

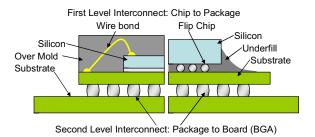

Microelectronic packages continue to undergo significant changes to keep pace with the demands of highperformance silicon. From the traditional role of space transformation and mechanical protection, packages have evolved to be a means to cost-effectively manage the increasing demands of power delivery, signal distribution, and heat removal. In the last decade or so, increasing frequency and power levels coupled with lower product costs have been driving new package technologies. Some examples of this are the migration from wirebond to flip chip interconnect and ceramic to organic package substrates.

Recently, architectural changes like the introduction of multicore processors, material changes such as the low-K dielectrics on the silicon, and lead-free second-level interconnects have introduced a new set of challenges that require innovative package technology solutions. As we look forward, increased levels of current, increased power density, and high-bandwidth signaling are expected to create challenges in all disciplines within the package field. In addition to these technical challenges, market forces such as declining computer prices, increased user experience through miniaturized devices, wireless connectivity, and longer battery life would make these challenges even more complex.

In this paper we provide an overview of trends and challenges in the areas of power delivery, signal transfer, thermal management, miniaturization, and wireless package technologies. We also examine some of the potential solutions that are being developed to meet these challenges.

### **INTRODUCTION**

Forty years of improvements in electronic components driven by Moore's Law has made almost all electronic systems relatively high performance when compared to the systems of a few years past. Even many low-cost children's toys today have computing power that exceeds the power of the earliest Personal Computers (PCs). In this paper, however, we limit the scope of our discussion to advanced package technologies used in consumer and business computing devices such as mobile and desktop PCs as well as workstations and servers. Some of the key components in such systems that drive the use of state-ofthe-art package technologies are the microprocessors, chipsets, and WLAN components.

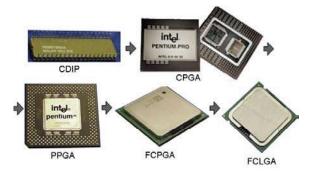

The evolution of packages for the desktop PC is shown in Figure 1. In the early 1980s, the 8086 microprocessor chip was housed in a Ceramic Dual In-line Package (CDIP). It used wirebonds to interconnect the silicon chip to the conducting leads on the ceramic package. This 800 mm<sup>2</sup> package had 40 leads placed along its two long sides. With an operating frequency of only a few MHz, fewer than ten percent of the leads were needed to supply power to the chip allowing the majority of the leads to do the useful function of signal transfer in and out of the microprocessors. The primary function of this package was to provide space transformation and environmental protection. By 1994, the Pentium<sup>®</sup> Pro processor used a 3000mm<sup>2</sup> Ceramic Pin Grid Array (CPGA) package with

<sup>&</sup>lt;sup>®</sup> Pentium is a registered trademark of Intel Corporation and its subsidiaries in the United States and other countries.

387 pins, a large copper-tungsten heat slug and two chipsthe CPU chip and a separate large SRAM cache chip. Over 40% of the pins were dedicated to deliver power to the chips. By the mid-1990s, cost and conductor resistance of the ceramic packages drove another shift in package technology. CPU packages for desktop PCs migrated to Plastic Pin Grid Array (PPGA) that changed the substrate material but continued to use wire bonding for the firstlevel interconnection. The wire inductance, and the need to have the interconnect pads near the periphery of the chip, significantly degraded the quality of power delivery and limited the chip size shrink. By 1997, advanced processors such as the Pentium<sup>®</sup> III processor migrated to flip chip BGA and PGA packages. In 2004, the Flip Chip Land Grid Array (FCLGA) package was introduced to eliminate the fragile package pins and enable the secondlevel interconnect pitch shrink for socketed components.

Figure 1: Evolution of Desktop PC package

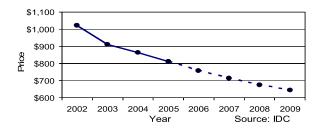

All of these package changes occurred in an environment of shrinking computer costs (Figure 2). The cost, performance, and form-factor optimizations for different market segments that drove the evolution of package technologies described here also drove many other technologies that are not covered here due to space limitations. Examples of such packages are Single Edge Contact Cartridges (SECC), Organic BGA on socket mountable interposer packages, Tape Carrier Packages (TCP), single- and multi-layer Quad Flat Pack (QFP) packages, etc.

Figure 2: Desktop PC selling price [1]

Package technology continues to evolve to meet changing technical and business challenges. In this paper we explore some of the key issues facing future package technologies and how they are being addressed.

### PACKAGE TECHNOLOGY DRIVERS

The traditional microprocessor technology drivers are power delivery, high-speed signal transfer, and heat dissipation. These continue to drive new technologies in advanced packages at every new generation of silicon and product technologies. The recent introduction of multicore CPU architectures has enhanced computing performance without increasing total power. However, lower voltages and some architectural changes drive increases in total current and power density. In addition, for some high-end product segments, higher total power may be necessary to provide significantly higher performance. These require improvements to package power delivery schemes to provide lower noise in power supply.

The increased computing performance requires the signal transfer rate in and out of the processor to increase. In addition, some of the new workloads demand highbandwidth data transfer between memory and the processor. This leads to higher speed signals on each data line as well as an increase in the number of data lines. However, the relatively slow rate of improvement in motherboard features, such as line width, space and via sizes, makes it difficult to increase the IO count. As a result there has been an emphasis on driving innovation in the area of component-to-component interconnects.

From a thermal management perspective, the benefits of improved performance per watt of multicore technology is somewhat offset by the need for power density increases when one or few of the cores need to consume significantly higher power than the average power per core. With increased current and current densities, the self heating of the package substrate and socket can be as high as many watts even with a large amount of copper in the package and with more than half of the socket pins allocated to power delivery.

In addition to these traditional drivers, there are few new drivers for advanced package technology solutions. One

<sup>&</sup>lt;sup>®</sup> Pentium is a registered trademark of Intel Corporation and its subsidiaries in the United States and other countries.

of the key drivers is the need for lower K dielectrics inside the silicon. These dielectrics, in general, are mechanically weaker requiring the package technologies to manage the stresses on the die.

In order to make the electronic components more environmentally friendly, package materials are being changed to eliminate chemicals like lead and halogen. These changes affect the material properties and processing conditions that need to be managed through proper choice of package technologies.

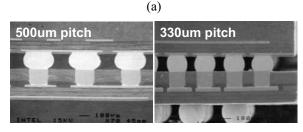

Platform miniaturization is an important industry trend in mobile platforms. Users are increasingly switching to small computers that are still expected to have robust performance [2]. Overall platform miniaturization requires not only one or two components to be tweaked, but a comprehensive platform approach. As a result, Intel is developing new package designs to take greater advantage of system-level technologies common in the hand-held computing space. For example, in hand-held devices, high density board technology is very common. This type of board technology, often referred to as Type II board technology, removes board routing bottlenecks near the package and thus enables smaller, tighter pitch BGA packages. Such finer pitch packages drive the need for elimination of traditional Plated Through-Holes (PTH) within the package substrates. Furthermore, focusing on the platform solution, Type II board technology allows a reduction in overall platform size by enabling denser component interconnects.

The wireless technologies within the PCs drive a different set of package technologies compared to microprocessor packages. More on each of these is discussed in the following sections.

# TECHNOLOGY TRENDS AND CHALLENGES

### **Power Delivery**

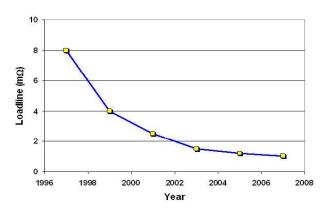

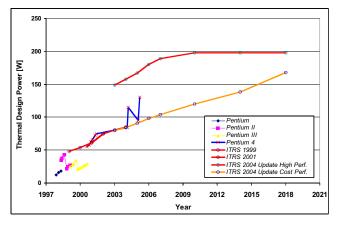

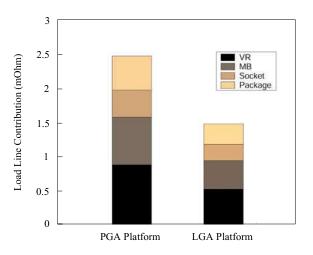

As the transistor count and core frequency increase with everv new microprocessor generation, current consumption has been growing at an exponential rate. In addition, as the device features get smaller to accommodate the increasing density, the die voltage has been scaling down to satisfy the oxide reliability conditions. This trend dictates a reduction in the impedance of the power delivery network which is proportional to the ratio of the voltage over current. If power levels continue to grow at the same pace, we will soon be faced with a sub-milliohm impedance target over a broad frequency range from DC up to several hundred MHz. Figure 3 plots the impedance target (loadline) as a function of time.

Figure 3: Power-delivery target impedance (loadline) trend

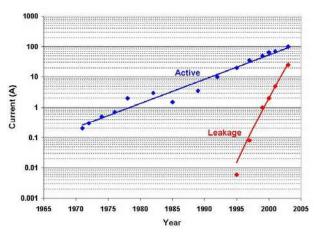

In order to keep up with Moore's Law, the number of transistors on a chip approximately doubles every generation resulting in improved performance. In order to double the device density, key silicon feature sizes are scaled by a factor of 0.7 with each new technology. However, there is a fundamental limit to how fine the features can be. Today's transistor gate oxide layers are literally only a few atoms in thickness. Even good insulators like the gate oxide layers will start leaking current at these dimensions. The leakage power levels in today's microprocessors are an appreciable percentage of the overall power budget. The leakage power issue is typically addressed through a combination of processlevel and architectural fixes. Process-level fixes like the use of thicker high k gate dielectrics are usually transparent to microelectronic packages. However, architectural changes like the use of sleep transistors or the switch to multicore processors do have a significant impact on the package solution.

Figure 4: Growth rate of leakage compared to active power

Until recently, the traditional approach to microprocessor design involved shrinking the device features to enable faster switching and higher core frequency. Unfortunately, this tends to increase leakage power, which degrades the processor performance-to-power consumption ratio. A better alternative is to de-emphasize frequency and get better performance by alternate means. De-emphasizing frequency allows the designer to limit the threshold voltage scaling, which keeps the leakage power in check. Performance improvement can still be realized by adding additional cores. For example, by adding an additional core and keeping the frequency flat, it will be possible to get a much higher performance-to-power ratio. One issue with adding additional cores is the impact on the package decoupling solution. Intel processors have traditionally used package land-side capacitors in the socket cavity directly under the core of the processor. However, with multicore processors, some of these cores may overlap the package pin-field resulting in a high-inductance path to the package capacitors.

### **High-Speed Signaling**

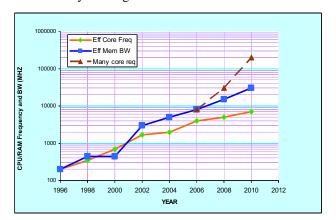

With the increase in the processing power of the CPU, the CPU-MCH (Memory Controller Hub), MCH-memory and/or CPU-memory interconnect links need to have exponentially higher bandwidth in order to fully utilize this computing power. Multiple high-resolution media streams in and out in real time also drive high-bandwidth requirements on the graphics side. Figure 5 shows Intel's CPU core frequency, traditional bandwidth, and "scaled" multicore bandwidth requirements. Well-known means to achieve increased bandwidth include increased data rate, increased IO count, and moving the chips closer to each other. High-bandwidth data transfer would drive the CPU Front Side Bus (FSB) to a series differential bus for its higher data rate and flexibility in scaling bus width. The package and socket technology as well as the designs need special attention to take full advantage of the technology.

Enabling a high data rate brings big challenges to package and socket analysis, characterization, and technology development. It is well known that at low frequencies, the package and socket can be treated as R, L, and C elements because their electrical length is much shorter than a wavelength. When a signal moves faster, the package and socket behave as long interconnects and therefore a full wave analysis is needed. For example, we need to treat package horizontal routing as transmission line and via, PTH and socket pins as arbitrary shaped 3D objects for full wave characterizations and designs. Manufacturing tolerance, which can be ignored at low frequency data rates, becomes important at high frequencies and therefore special attention must be paid to this. Moreover, high density and small form-factor requirements push packagelevel transmission lines to a very small cross section and

the insertion loss becomes a dominant part of the whole system loss budget.

High loss package transmission lines and long motherboard transmission lines at high frequencies eventually restrict high data rates. In these cases, it might be necessary to move chips closer together. For instance, moving the Random Access Memory (RAM) chips closer to the CPU benefits RAM performance, such as fully buffered DIMM (FBD) technology. However, the data rate or performance improvement resulting from this move may still not meet the bandwidth requirement, which is increasing exponentially. Thus, more IO interfaces or IO counts are necessary to leverage the flexibility provided by the series signal interface. With the assumption of lowcost infrastructure, increasing the IO count leads primarily to a shrinking interconnect conductor cross section and signal-to-signal pitch for package horizontal transmission lines, micro-vias, PTHs, and socket pin or BGA balls. While via and PTH geometry and cross-section shrinks have only a minimal impact on signal integrity due to their short length, transmission lines and high socket pin counts impact signal performance significantly. Nevertheless, there is a net bandwidth benefit in increasing the number of IOs. However, limitations on the number of secondlevel interconnects, i.e., socket pins or BGA balls due to cost and size, can cause bottlenecks in the overall system bandwidth by limiting IO counts.

Figure 5: CPU core frequency and bandwidth trend

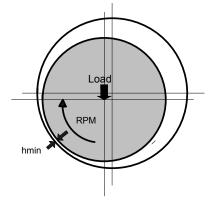

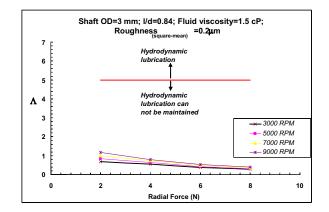

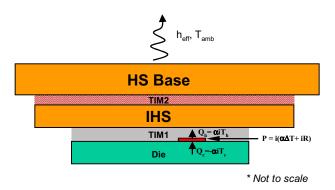

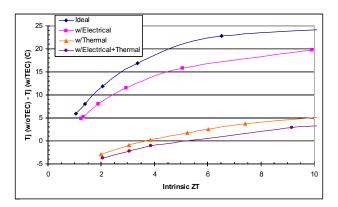

#### **Thermal Management**

We discussed earlier that even at constant power, the power density and electrical current is expected to increase. As current levels continue to rise, Joule heating, i.e., heat generated when current passes through a resistor, along the power delivery path becomes significant. Since it is not uncommon for today's high-end microprocessor to draw currents in excess of 100A, even a resistance of  $0.5m\Omega$  along the path will result in a power dissipation of 5W. Thus it will be increasingly critical to do the thermal management of the on-chip hotspots as well as the package and socket Joule heating.

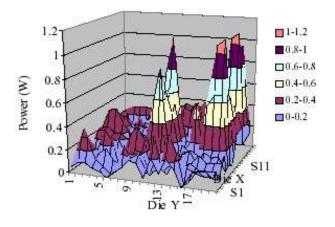

#### **Power Density**

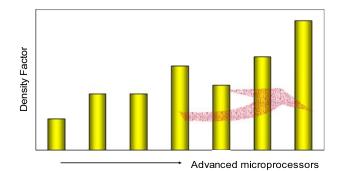

Thermal designers need to account for thermal nonuniformity (typically referred to as hotspots, where power densities of  $300+W/cm^2$  are possible) caused by nonuniform distribution of power on the die. To help quantify the non-uniform power effects, a Density Factor (DF) that is independent of the power profile on the die has been proposed [3]. The DF is simply the ratio of the actual package thermal resistance at the hottest spot to the diearea-normalized uniform power resistance or thermal impedance, and has the units of inverse area (A<sup>-1</sup>). DF can be used to quantify the impact of nonuniform die heating on thermal management. Equation (1) shows the relationship of package junction-to-case thermal resistance ( $\psi$ jc) to the package thermal interface material technology (Rjc).

$$\psi jc = R jc * DF \tag{1}$$

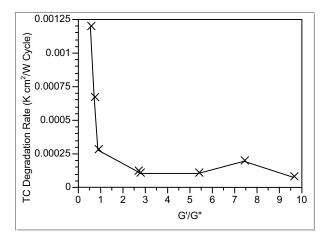

It can be seen that for the same package thermal interface material technology being used (i.e., the same Rjc value), the power maps with a higher DF will result in a higher package thermal resistance, which in turn requires more advanced cooling solutions. Figure 6 shows the increasing trend of DF for desktop microprocessors due to the increasing local power density at the hotspots.

#### **Joule Heating**

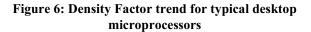

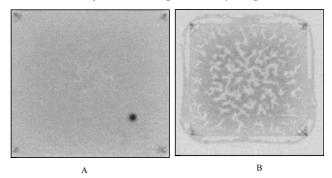

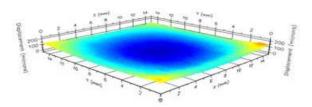

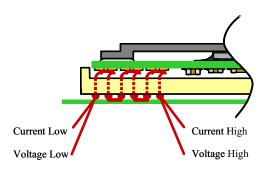

Higher current combined with the need to reduce the package size, i.e., thinner and narrower conductors and/or finer pitch power delivery interconnects, would lead to a high amount of heat generated within the package and socket. This would require thermal management of the entire interconnect which includes the flip chip joints, the substrate, the socket and the solder balls. Figure 7 shows an example of a temperature map of the metal contacts in the socket due to Joule heating. The lighter color here indicates higher temperatures.

### Figure 7: Example of Joule heating of socket contact pins

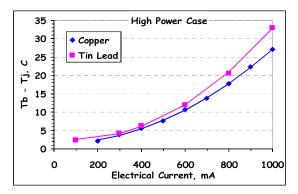

One key area of challenge is the increasing temperature of the flip-chip die bumps. As the electrical current through the flip-chip die bumps and the substrate traces increases, Joule heating increases the bump temperature (Tb) when compared to the transistor junction temperature (Tj) as shown in Figure 8. Without proper attention to package design, the bump temperature could be significantly higher than the Tj causing bump electro-migration problems. The socket and substrate temperatures can also rise due to Joule heating.

Figure 8: Temperature difference between die bump (Tb) and die (Tj) for two different bump materials

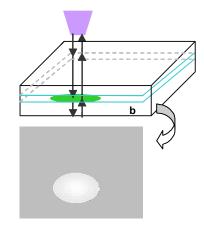

#### **Die Stacking**

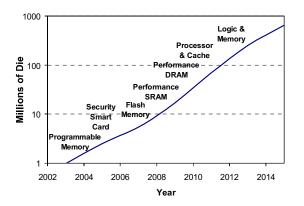

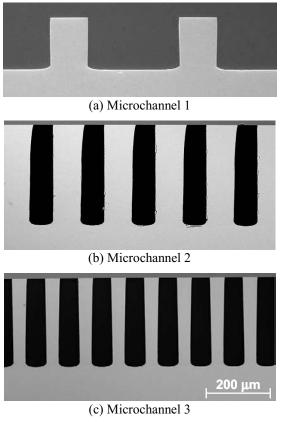

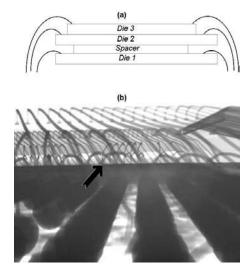

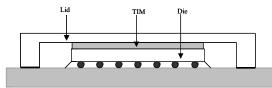

Stacked die packages are a recent trend for memory chips for handheld devices and possibly could be used in conjunction with CPU or chipsets in the future (Figure 9). The thermal challenge of stacked die packages is largely due to higher power dissipation and higher thermal resistance between dies.

Figure 9: 3D Die stacking trend (source: Prismark)

#### Miniaturization

Mobile computing has been one of the world's fastest growing PC market segments [1], and Intel is delivering many products to meet the needs of mobile computing. For example, to enable wireless communications on mobile computing platforms, Intel<sup>®</sup> Centrino<sup>®</sup> mobile Moving technology was developed. forward, miniaturization with increased functionality continues to be an important trend in mobile computing. An example of the miniaturization trend is also seen in the ever improving functionality of mobile handsets. Over the last five or so years, 2D games, and now more demanding 3D games, have become available in these devices. Also, within the last year or so, handset and content providers have teamed up to bring video content to the newest handsets. As more and more functionality is driven into smaller platforms, there will be an ever increasing pressure on component and platform-level solutions to provide smaller packages and denser interconnect solutions.

#### **Packages for Wireless Devices**

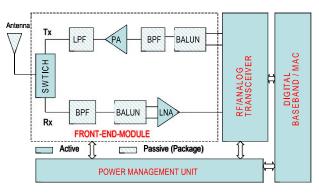

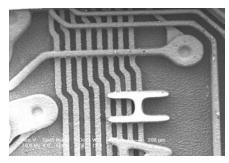

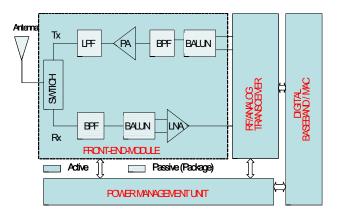

Traditionally, wireless communication devices as illustrated in the block diagram of Figure 10 have consisted of a mixture of several active devices from different semiconductor technologies such as silicon CMOS, silicon BiCMOS, GaAs, and SiGe, all of which are mounted on a PCB substrate and supported by numerous passive components. Each die is typically packaged in a Quad Flat No-lead (QFN) package using low-cost wirebond technology.

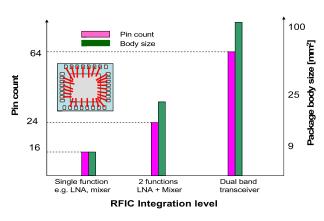

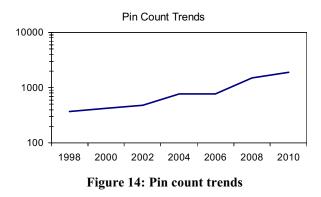

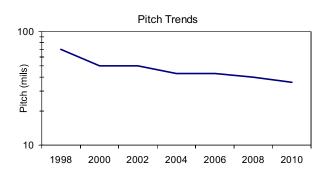

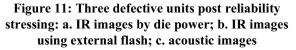

Figure 10: Block diagram illustration of a single band wireless communication device

With the improved maturity of CMOS technologies, the bulk of wireless communication devices is expected to evolve in the short term to a two-chip solution, where one chip is dedicated to RF/analog (radio) and the other chip is dedicated to the digital (baseband/MAC). Over the long term, however, it is expected that the maturity of CMOS technology and improved signal isolation techniques will enable a single-chip solution, where baseband, radio, and even the power amplifier, typically found on the frontend-module, are all integrated on the same silicon substrate. The increased level of integration is expected to require larger package pin counts and possibly larger package sizes, as illustrated in Figure 11. The evolution of wireless devices to multimode, multiband devices that can operate worldwide and provide functionalities such as GSM, PCS, UWB, Wi-Fi\*, WiMax, and GPS requires that future devices be implemented as multiband radios. As the frequency of operation increases, improvement in channel capacity and recovery of signal attenuation associated with interconnect losses require that multiple inputs and multiple output (MIMO) radio architectures be adopted. The addition of each frequency band for multiband radios or an additional transmission path for MIMO has a direct implication on the number of IOs needed by the first-level package. As the total pin count exceeds 70, the traditional single-row QFN would face significant challenges driven by the leadframe metal pitch constraints and the required RF signal isolation between adjacent signal lines.

<sup>&</sup>lt;sup>®</sup> Intel and Centrino are registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

<sup>\*</sup> Other brands and names are the property of their respective owners.

Figure 11: Package pin count and body size requirements for integrated wireless solutions

The increased functionality (music, video, gaming, etc.) integration with each handheld product generation adds to the complexity of the baseband and power management units, which in turn requires more passive components (especially resistors and capacitors) for baseband power supply and management. For example, the number of passive components in a typical cellular phone has more than tripled over the last few years. This increase in passive counts leads to increased assembly costs and reliability issues.

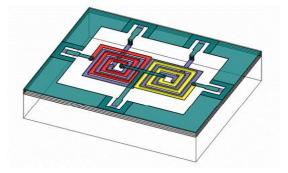

The second level of wireless package is at the module level and includes critical building blocks such as filters, diplexers, baluns, and matching networks found in the RF Front-End Module (FEM). As illustrated in Figure 10, for each frequency band, complete transmission and receive paths are needed. For both multiband and MIMO radios, this implies a significant increase in the overall real estate of the FEM and the wireless device in general. Despite the increase in the number of frequency bands and the implementation of MIMO radios, the size of the package at the module level is expected to continue to decrease as a result of the requirements of portability and power consumption. This would require, for example, that stringent isolation techniques be used at the package level for proper signal isolation between the different transmission paths of the MIMO radios. At the same time, innovative substrate solutions have to be developed to deliver small form-factor filters, diplexers, baluns, and matching networks.

#### POTENTIAL SOLUTIONS

#### **Power Delivery**

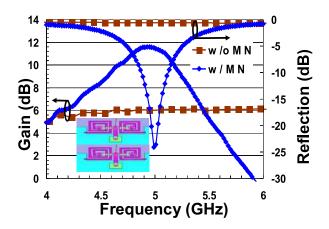

Meeting sub-milliohm power delivery impedance targets and containing leakage power are two major challenges that influence the design of the power delivery solution in today's microprocessors. Since the spectral content of the current drawn by the processor is fairly broad-band, it is important to have a low impedance path from the power supply to the microprocessor across a wide range of frequencies from DC up to several hundred MHz. In order to manage the high-frequency noise, Intel microprocessors have been steadily migrating to better performance package capacitors. Starting with the first Pentium® processor and up until the Pentium III processor, 2terminal capacitors were used for package decoupling. Starting with the Pentium<sup>®</sup> 4 processor, package decoupling needs were addressed using Inter-Digitated Capacitors (IDC). These capacitors have eight alternating power and ground terminals that help reduce the effective inductance, thereby reducing the high-frequency noise seen by the processor. As the power supply demand goes up, even the performance afforded by the IDC capacitor will become inadequate. There are more advanced capacitors such as array capacitors that are currently being investigated as a potential decoupling option for future processors. Array capacitors tend to have a large number of power and ground terminals that make their effective inductance vanishingly small. Figure 12 shows a picture of the different capacitors that are discussed here.

Figure 12: Evolution of package capacitors

As the improvement in capacitor technology drives down the effective inductance of the capacitors, the inductance of the package interconnect becomes the performance bottleneck. This is especially true in the case of multicore processors with one or more cores overlapping the package pin-field. In such cases, the best option would be to use embedded capacitors placed inside the package directly under the cores.

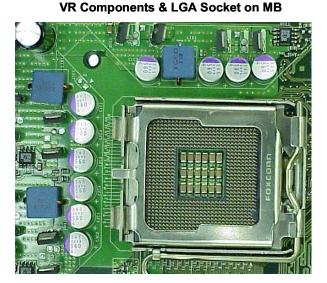

The advanced capacitor solutions limit the high-frequency noise but have little impact on the low-frequency noise seen by the microprocessor. One way to limit the lowfrequency noise is to reduce the resistance in the path from the VR to the die. The DC resistance is typically managed by adding more power and ground pins and increasing the copper thickness in the package power and ground layers. Figure 13 shows a picture of the different types of sockets that have been used over the past few years. As shown in the pictures, the number of pins in the

<sup>&</sup>lt;sup>®</sup> Pentium is a registered trademark of Intel Corporation and its subsidiaries in the United States and other countries.

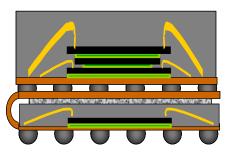

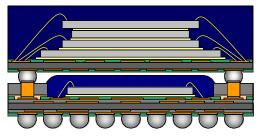

socket has gone up each time we transition to a new socket. At the same time the socket pin pitch has been scaling down, which allows us to increase the pin count without driving up the package body size. Another option to minimize the resistance in the path involves moving the Voltage Regulator (VR) closer to the die. One such topology moves the VR components from the motherboard to a custom VR board that is sandwiched between the package and the heatsink. The power flows from the VR board to the package through an LGA connector. Apart from moving the VR closer to the die, this concept also frees up the P/G pins in the socket which can now be used to address signaling needs. While moving the VR closer to the die provides incremental performance benefits, the ultimate power delivery solution would be to integrate the VR components on the load die or to attach the VR die directly on the top or bottom of the load die.

Figure 13: Evolution of socket technology

### **High-Speed Signaling**

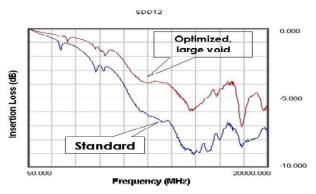

Increasing the data rate is generally the first choice to enable a high-bandwidth system. Typically, two approaches are taken to enhance data speed, namely, loss management and impedance control. While package transmission line loss is mainly due to conductor loss, the copper conductors being used in the organic packages today already provide excellent conductivity. There is not much room for further optimization due to physical limitations. Focus is then shifted to impedance control. Although signal integrity engineers already noticed that packages typically behave as a capacitor such that their impedance is lower than the overall interconnect, and designers already decreased the system impedance target from 100ohm to 90ohm and are now targeting 85ohm, specific package treatments are still necessary to achieve high bandwidth. A key optimization approach is to reduce signal path capacitance so that the "characteristic" impedance can be moved up to match system impedance, resulting in a smaller return loss and a higher insertion loss. Figure 14 shows FCLGA package insertion loss with reduced capacitance between bottom layer pads to the upper layer ground plane. Other approaches to reduce

capacitance include smaller socket pad size or locating a spiral inductor to balance capacitive effects.

Figure 14: Optimization of package interconnect design for high-speed signaling

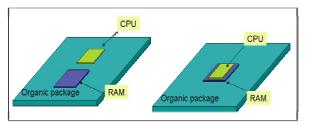

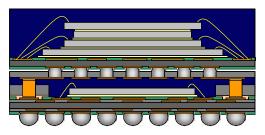

Bandwidth increases from optimization of current interconnect paths or from positioning CPU, chipset and RAM packages closer may not be enough to meet the demands of high-performance computing and multi-media applications. Increasing the IO count also has issues with second-level interconnect density, package sizes, and cost. As a result, revolutionary solutions are needed. Here we show two approaches: one uses an MCP configuration, i.e., putting CPU and RAM side by side (2D configuration) on a single package, and the other uses a 3D stacking approach, i.e., mounting the CPU on a RAM that has through silicon vias in the RAM. Figure 15 shows the basic idea of these two approaches. 2D MCP can provide a few hundred GB/s bandwidth based on projected RAM performance around 2010. However, in order to achieve an order of magnitude higher bandwidth. 3D stacking of the chips would be needed. The 3D stacking not only provides very high interconnect density, but also delivers bandwidth efficiency through higher data rate and improved power consumption.

Figure 15: MCP and 3D die stacking approaches for high-bandwidth system

#### **Thermal Management**

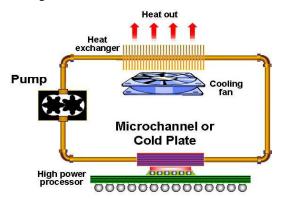

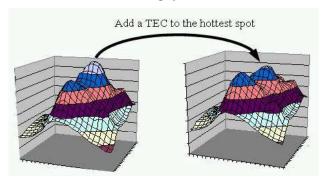

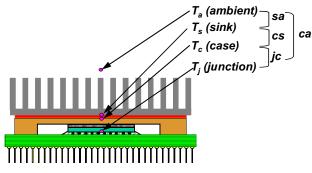

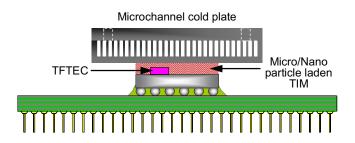

Quite a few technologies are under evaluation by industrial and academic researchers. One area of research is to enhance convection cooling by improving the heat transfer coefficient through extended heat sink surfaces and high airflow fans with the built-in feature for acoustic noise cancellation. Attention has also been paid to the development of heat spreader material such as carbon fiber, graphite, thermal-conductive composites, vapor chambers, heat pipes, and nano-materials. The researchers are aggressively seeking solutions beyond air cooling. For example, a closed-loop liquid cooling system, as shown in Figure 16, is under development. This system implements cold plates or micro-channels with either single-phase or two-phase liquid cooling. In addition, refrigeration to achieve "negative" thermal resistance is being developed with the focus on reducing the size and cost of the compressor and the heat exchanger. Recently, researchers also have investigated solid-state refrigeration (or thermoelectric coolers) for "hotspot" cooling of devices with highly non-uniform power dissipation (Figure 17) or full-chip cooling in conjunction with vapor chamber heat sinks. This type of technology can actively cool the electronic device temperature with no moving parts and potentially provide "negative" thermal resistance similar to traditional refrigeration. Emerging nano-materials hold promise of providing highly conductive Thermal Interface Materials (nano-TIMs) and reducing interconnect Joule heating.

Figure 16: A schematic for a typical closed-loop liquid cooling system

Figure 17: Example of hotspot suppression by applying a TEC to the hottest spot

The Joule heating of the interconnects on the package and socket can be effectively managed through careful design and analysis. This involves minimizing current concentration and spreading heat away through design and material choices.

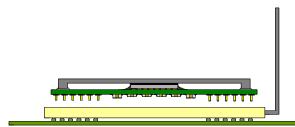

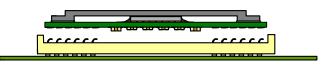

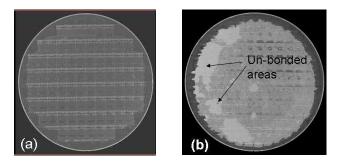

### Miniaturization

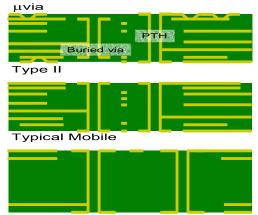

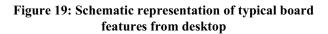

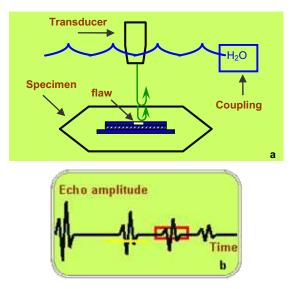

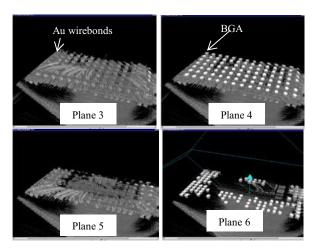

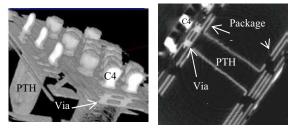

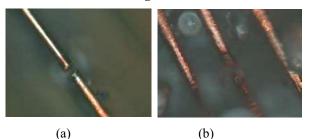

While it can be a challenge to deliver greater functionality in dramatically smaller packages, mobile and small formfactor platforms also offer opportunities for package designers. One example is Type II board technology (Figures 18, 19). Such a board employs buried vias and "micro vias" (µvias) as well as smaller feature sizes. In contrast, mobile PC boards may often have only PTHs and larger feature sizes. A typical desktop board often has even larger PTHs and feature sizes and it has fewer layers than mobile boards. The features of the Type II board technology help in breaking signals out of the package and in delivering power to the package. Figure 20 illustrates this point. The first example used mobile board features. Here the package ball pitch reduction is limited by the need to fit board PTHs in between the BGA pads. Larger board feature sizes, such as signal trace width, further impede package miniaturization. This can result in a package BGA pitch reduction limit of around 0.8mm. On the other hand, Type II board features can result in a package breakout similar to that shown in the second example of Figure 20. Here the package BGA pitch has been reduced to around 0.6mm. This results in significant increase in BGA density and a reduction in package size.

Buried via

Figure 18: Typical Type II board stackup

Typical Desktop

### Figure 20: Illustration of routing fan-out differences between typical mobile (top) & Type II (bottom) board

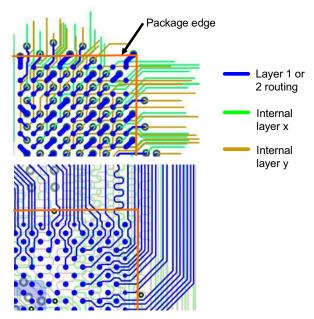

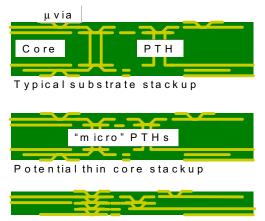

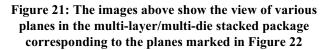

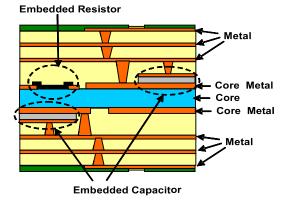

As board routing capabilities increase, the large size and pitch of the package PTHs can constrain the BGA ball pitch shrink. The solution is to use smaller size PTHs with thinner core package substrates or to eliminate PTHs through the use of coreless packages. Figure 21 illustrates potential density improvements for typical thin core and coreless cases. Similarly, innovations in robust power delivery decoupling solutions are being researched. This includes eliminating the decoupling capacitors or minimizing their size and quantity, or cost-effectively embedding the capacitors in the substrate.

Potential coreless stackup

### Figure 21: Schematic of typical, thin core, and coreless package stackups

### Wireless Packages

#### High-pin Count Package Solutions

The problem of limited pin counts associated with QFN packages for highly integrated wireless systems is addressed by using dual-row QFN packages [4] instead of the traditional QFN packages in which two rows of surface mount pads are placed at the periphery of the package. Both rows can then be connected to the die using wirebonds. This technology, as illustrated in Figure 22, can provide about 150 IOs for a package with a body size of 12mm x 12mm, which is sufficient for a dual-band MIMO GSM or WLAN radio.

Figure 22: Dual-row QFN for wireless chip

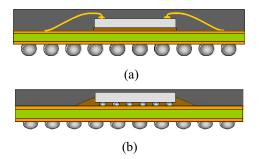

As the RF/analog and digital ICs are combined on a single silicon die and the number of IOs goes beyond 170, the package options available are traditional MMAP (Figure 23), carrier tape-based leadframe packages, or a simple extension of QFN technology.

Figure 23: MMAP package technologies for high pincount wireless chips in (a) wirebond and (b) flip-chip configurations

### Embedded Passives for Baseband Power Management and Miniaturized Front-end Modules

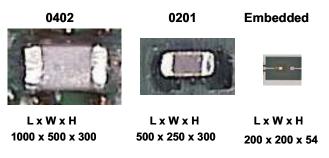

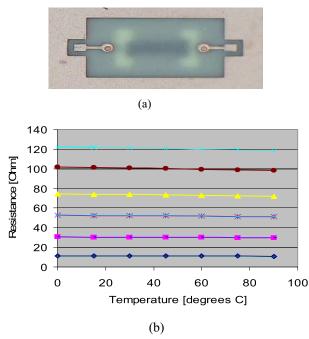

At the board level, most passives (mainly resistors and capacitors) used for the baseband power supply are experiencing a gradual size reduction from today's standard 0603 to smaller 0201 to meet the stringent formfactor requirements. In parallel, embedded passives technologies, where all resistors and capacitors are fabricated as part of the package substrate, are gaining more importance, not only because this technology reduces space, but also because it has the opportunity to enhance product reliability by reducing or eliminating the solder joints. Figure 24 shows a size comparison between typical surface mount and embedded capacitors. Due to the wide capacitance range and tight tolerance demands on these passives, significant innovation is required in integrating the high-K dielectrics to fully utilize the benefits of embedded passives technology.

#### **RF Front-end Module Solutions**

In the RF FEM, the development of low-temperature cofired ceramic and multilayer organic substrates to include high-performance inductors and capacitors has paved the way to integrate filters, diplexers, and LC-based matching networks with much smaller form factors. At the same time GaAs and silicon-based integrated passives have shown good electrical performance for RF FEM applications. The extremely good quality factor of package-embedded inductors will enable future WiFi/WiMax radios to have FEM, where all filtering functions are based exclusively on capacitors and inductors embedded in the package substrate, leaving the surface for the active dies. A detailed discussion of embedded passives for miniaturized front-end-modules can be found in "Future Package Solutions for Wireless Communication Systems" in this issue of the Intel Technology Journal [5].

Figure 24: SMT and embedded capacitor size comparison. All dimension (W,L,H) are in µm

#### SUMMARY

An overview of the key challenges and potential solutions was presented for advanced microelectronic packages in the computing systems commonly used by today's consumers and businesses. Higher performance levels of the key ICs in these systems demand reduced noise in the power supply path from the VR to the transistors on the silicon. Similarly, higher signal transfer bandwidths between different components are needed to feed the data to the high-performance computing engines. Package technology has cost-effectively come up with solutions without significant system architectural changes. In many cases, the VR and the memory components are brought electrically closer to the load die such as the microprocessor, but are still kept off the load die package. The tricks used to achieve these are providing diminishing returns. The trend to reduce the electrical distance to the VR and the RAM would eventually lead to these components being physically brought onto the package in the form of a multi-chip package solution. This will lead to physical space contentions on the small package. Such multi-chip packages are expected to solve these issues for a few more generations but will add complexity to package technology. A further drive to bring the components closer would require the different dies to be vertically stacked and interconnected through features like through-silicon vias. This will create significant challenges not only to many aspects of package technology but also to silicon technology, product architecture, and IC design technology.

Handheld market segments offer an intriguing motivation and opportunity for IC package and platform miniaturization. Platform technologies more common in this segment, e.g., Type II board technology, enables sub-0.8mm BGA pitch for microprocessors and chipsets. Advances in package technology such as thin-core and coreless substrates may push the miniaturization envelope even further by reducing or eliminating the package PTH bottleneck. At this point, a blurring of the traditional role between package and board may emerge allowing for even smaller platform form factors. The form factor and cost demands of the wireless products drive the need to manage the passive components within the package effectively.

### ACKNOWLEDGEMENTS

We acknowledge the contributions of our colleagues in Intel, particularly in the Assembly Technology Development Group, on whose work many of the concepts discussed here are built.

### REFERENCES

- [1] D. Daoud and L Loverde, "Market Analysis: Worldwide PC 2005-2009," *IDC*, June 2005.

- [2] Mikako Kitagawa et al., "Market Trends: Preliminary PC Market Results, Worldwide, 2Q05," *Gartner-Dataquest*, July 25, 2005.

- [3] J. Torresola, C. Chiu, G. Chrysler, D. Grannes, R. Mahajan, R. Prasher, and A. Watwe, "Density factor approach impact on die power maps on thermal management," *IEEE Trans on Advanced Packaging*, in press.

- [4] Ming Ying, Seng Guan Chow, J.D. Punzalan, R. Emigh, K. Ramakrishna, "Design Considerations on Solder Joint Reliability of dual row quad flat no-lead packages," in *Proceedings of 6<sup>th</sup> Electronics Packaging Technology Conference*, EPTC 2004, pp. 308-312.

- [5] T. Kamgaing et al., "Future Package Solutions for Wireless Communication Systems," *Intel Technology Journal*, Volume 9, Issue 4, 2005.

### **AUTHORS' BIOGRAPHIES**

**Debendra Mallik** joined Intel in 1983. He is a principal engineer in the Assembly Technology Development (ATD) Group. His responsibilities include technology definition for next-generation packages. He received his B.S. and M.S. degrees in Mechanical Engineering from the Indian Institute of Technology, Kharagpur and Iowa State University, respectively. He holds over 20 patents in the field of advanced package solutions. His e-mail is debendra.mallik at intel.com.

Kaladhar Radhakrishnan joined Intel in 2000 soon after receiving his Ph.D. degree in Electrical Engineering from the University of Illinois at Urbana-Champaign. He currently manages the Power Delivery Core Competency team within the ATD group. His e-mail is kaladhar.radhakrishnan at intel.com.

**Jiangqi He** received his Ph.D. degree in EE from Duke University, Durham, NC, in 2000 in the field of Computational Electromagnetics. He has been with the electrical core competency team in the ATD group since that time. He has worked on power delivery and highspeed signaling for computer systems focusing on package and socket-level interconnect technologies. Currently he is managing the high-speed IO core competency team in ATD and his main interest is on high-speed interconnect technologies for series differential signaling, including modeling, simulation, validation, and new technology development. He holds 12 US patents and has published more than 30 technical papers. His e-mail is jiangqi.he at intel.com.

**Chia-Pin Chiu** is manager of the Thermal Core Competency group at Intel Corporation in Chandler, Arizona, where he is responsible for thermal technology development and product thermal management. His major research included thermal interface materials, thermal characterization metrology, and the development of new cooling solutions. Chiu received his M.S. and Ph.D. degrees in Mechanical Engineering from the University of Minnesota in 1992. After graduation, he joined the ATD group of Intel and accomplished thermal designs for various Pentium processors. Chiu holds 24 US patents, 17 pending patent applications, and has published 35 technical papers. He is a member of ASME, IEEE, and the JEDEC JC15 committee. His e-mail is chia-pin.chiu at intel.com.

**Telesphor Kamgaing** received his M.S. and Ph.D. degrees in Electrical Engineering from the University of Maryland, College Park, both in 2003. From 1999 to 2004 he held research positions with NIST and Digital DNA Laboratories of Motorola Inc. In 2004, he joined Intel Corporation in Chandler, Arizona as a senior electrical packaging engineer and is currently focusing on RF and non-RF packages aspects of wireless communication systems. He is an IEEE senior member and has published more than 25 technical papers in refereed international journals and conference proceedings. His e-mail is telesphor.kamgaing at intel.com.

**Damion Searls** received his B.S. degree in Nuclear Engineering in 1995 and his M.S. degree in Mechanical Engineering in 1997, both from the University of Maryland. At Intel, he has worked in quality and reliability, boards, and package solutions. Damion's current work is centered on platform optimization and miniaturization. He holds 27 US patents and can be reached by e-mail at damion.searls at intel.com.

**James D. Jackson** received his B.S. degree in Chemical Engineering from the University of Texas at Austin in 1986, and his M.S. degree in Chemical Engineering from the University of Washington in 1989. He has worked at Intel in a variety of positions in fab, package, and board/system technology. Currently, he is working on platform miniaturization. He holds 9 US patents and can be reached by e-mail at james.d.jackson at intel.com.

Copyright © Intel Corporation 2005. This publication was downloaded from <u>http://developer.intel.com/</u>.

Legal notices at <a href="http://www.intel.com/sites/corporate/tradmarx.htm">http://www.intel.com/sites/corporate/tradmarx.htm</a>

THIS PAGE INTENTIONALLY LEFT BLANK

### Power Delivery for High-Performance Microprocessors

Kemal Aygün, Technology and Manufacturing Group, Intel Corporation Michael J. Hill, Technology and Manufacturing Group, Intel Corporation Kimberly Eilert, Technology and Manufacturing Group, Intel Corporation Kaladhar Radhakrishnan, Technology and Manufacturing Group, Intel Corporation Alex Levin, Digital Enterprise Group, Intel Corporation

Index words: power delivery, decoupling capacitors, Fmax, impedance profile

### ABSTRACT

This paper provides an overview of the trends, challenges, and solutions associated with delivering power to highperformance microprocessors. Due to the large power levels in today's microprocessors, it is not uncommon to design a Power Delivery Network (PDN) with a submilliohm impedance target. Apart from the obvious design challenges, there are measurement challenges associated with characterizing these low-impedance power delivery networks. By using a combination of active and passive measurement techniques, it is possible to successfully characterize the power delivery performance of the system. Since most of the pre-silicon power delivery design decisions are made based on modeling data, it is important to have accurate, fully calibrated simulation models. The simulation models used to analyze the PDN for the Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor are shown to have good correlation with the measurement results. While the importance of the ability to measure and model the PDN cannot be understated, it is equally important to fully comprehend the impact of power delivery noise on the overall system performance. This allows the system designer to make the right tradeoffs in maximizing performance without exceeding the cost budget.

### INTRODUCTION

The number of transistors in a microprocessor chip has been growing exponentially in accordance with Moore's Law. Microprocessor current levels have been increasing rapidly as transistors get smaller and faster. Due to the large current levels in today's microprocessors, it is imperative to have a low-impedance path from the power supply to the die. Failure to do so can result in excessive noise that can impact performance by limiting the maximum operable frequency [1].

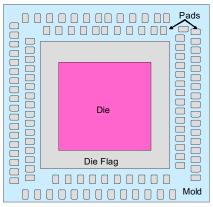

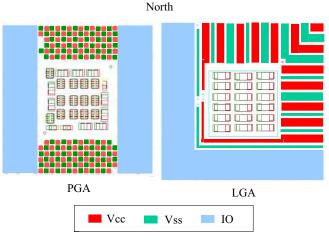

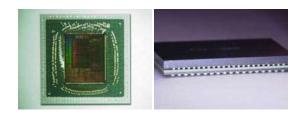

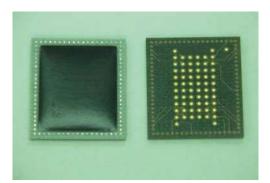

Package – Top View

Package – Bottom View

Figure 1: Power delivery solution for the Pentium<sup>®</sup>4 processor

Since the current drawn by the processor can change suddenly, the impedance target needs to be met across a wide range of frequencies. This is typically accomplished by using a multi-stage decoupling solution with different types of capacitors. Figure 1 is a picture of the power

<sup>&</sup>lt;sup>®</sup>Pentium is a registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

delivery solution for the Pentium 4 microprocessor on an LGA775 system. The high-frequency capacitors are placed on the land-side of the package. Ceramic capacitors are used for mid-frequency decoupling and are placed on the motherboard inside the socket cavity. Bulk capacitors are placed on the motherboard at the output of the voltage regulator to address the low frequency decoupling needs. These decoupling stages along with the voltage regulator and the on-die capacitance constitute the Power Delivery Network (PDN) of the microprocessor.

The primary objective of the power delivery designer is to pick the right type and location for these components in a way that will allow him or her to meet the impedance target. A majority of the power delivery design decisions such as the number of power and ground layers and the location of the capacitors is made prior to the availability of the first silicon. For this reason, these decisions have to be made based on data from the simulation models. Due to the sheer volume in the microprocessor market, the decision to add or remove a single capacitor can have a significant financial impact. As a result, it is important to have fully calibrated, reliable simulation models. Calibration of the simulation model is accomplished by measurement data from the previous collecting microprocessor. power generation's Traditionally, delivery validation was carried out in the time domain by monitoring the noise on the die sense lines while a high activity program is run on the processor. However, it is not convenient to use the time domain measurement data to calibrate the simulation models, due to the uncertainty associated with the die excitation model. In order to circumvent this issue, a frequency domain scheme is used to measure the impedance profile of the power delivery network as a function of frequency. This provides a metric that is independent of the die excitation and allows for direct correlation with the simulation model. In addition to the active measurements on a functional processor, passive characterizations on the individual components are often required to enhance the accuracy of the simulation models. For instance, the capacitance value specified by the vendor is often higher than the effective capacitance of the component under typical use conditions. A measurement scheme for measuring the effective capacitance as a function of temperature, DC bias, and AC signal level is described.

So far we have provided an overview of the power delivery problem for microprocessors. In the next section, we go over some of the power delivery trends that are seen in Intel microprocessors. We look at current and voltage trends as a function of time. We also cover some of the leakage power issues and discuss how they are driving the switch to multi-core processors. In section 3 we describe in detail the active and passive power delivery metrologies that are used to characterize the system power delivery performance. In section 4 we describe the construction of the simulation model and also include some model correlation results. Finally, in section 5 we focus on the impact of the power delivery noise on system performance.

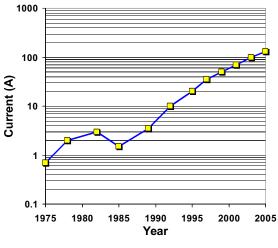

### POWER DELIVERY TRENDS

The number of transistors on a microprocessor chip has been increasing at an exponential rate. At the same time, these transistors have been switching faster to improve performance. These two trends combine to drive up the current consumed by microprocessors. Even though a part of this increase is offset by the reduction in the voltage levels and the transistor size, microprocessor current consumption has still been increasing at an exponential rate over the last two decades as shown in Figure 2. The brief respite in the current scaling in the mid-80s can be attributed to the switch from NMOS to CMOS technology.

Figure 1: Microprocessor current trends in Intel microprocessors

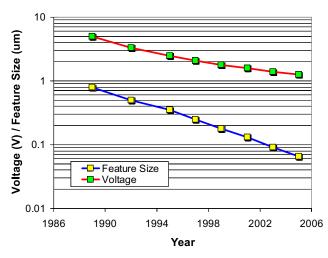

As the dimensions on die get smaller to accommodate the increasing device density, the die voltage levels have been scaling down to meet oxide reliability constraints. Figure 3 shows the silicon feature size as a function of time. From the figure, we can see that the feature size has been scaling by a factor of  $\sim 0.7$  x every two years. This corresponds to a doubling of the device density during the same period in accordance with Moore's Law. As the device dimensions continue to get smaller, the gate oxide thickness has gone from about 100nm back in the 1970s to about 1nm in today's process. In order to comply with the oxide reliability requirements, the die voltage has been scaling down as well as shown in Figure 3. The lowered operating voltage drives a lowered noise requirement. This trend coupled with the increasing current yields a

power delivery impedance target that is fast approaching sub-milliohm levels.

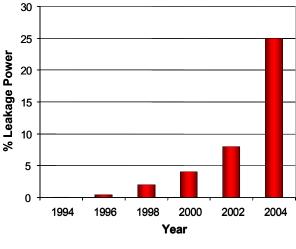

Figure 3: Leakage power growth

### Figure 2: Microprocessor voltage and gate length trends

An unfortunate by-product of the reduction in the device dimensions is the increase in leakage power. Today's transistors start conducting current even when they are turned off and this current is referred to as leakage current. Figure 4 shows the growth in leakage power as a percentage of the total power supplied to the processor. From the figure, it is clear that the leakage power has grown from being negligibly small to being an appreciable percentage of the total power in a short period of time. If left unchecked, leakage power would soon exceed the active power consumption. One way to combat the leakage power issue is by slowing the frequency growth. With a reduced emphasis on the processor frequency, the process parameters can be tweaked to reduce leakage current at the expense of transistor switching speed.

With frequency no longer being the primary knob for improving the processor performance, system architects have turned to other avenues in an effort to improve the overall performance. One example of this is the switch to multiple cores. By adding an extra logic core and reducing the switching frequency, the processor can get a performance boost without a significant power penalty.

### **POWER DELIVERY METROLOGIES**

The power delivery demands of today's microprocessors drive us towards bigger packages with more layers and better decoupling capacitors. The decision to add or remove a single component in a high-volume product can have a significant financial impact. As a result, it is important to have accurate methods to assess and quantify the impact of any changes made to the PDN.

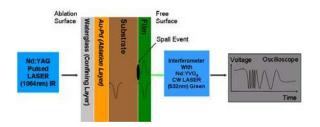

### **Active Power Delivery Measurements**

Traditionally active measurements for power delivery have often been performed in terms of voltage "droop" recordings [2]. In a droop measurement, the processor is periodically driven from a low-power consumption state to a high-power consumption state. This is also referred to as a large "dI/dt" event to emphasize the large instantaneous change in the amount of current drawn by the die. Then, the voltage at the die power rails, v(t), is measured as a function of time during this transition. Given two different PDN solutions, the one with better performance will respond to the large dI/dt event better and this will be reflected in the amount of undershoot (i.e., droop) and overshoot in v(t). The fundamental problem with this method is that it is usually very difficult to determine or measure the exact current drawn by the die, i(t), during a typical droop measurement. Since v(t) is a strong function of i(t), this essentially makes it considerably difficult to interpret and compare the droop waveforms obtained under different test conditions and for different processors.

A more direct assessment of the performance of the PDN can be achieved by measuring its impedance as a function of frequency. In order to measure the impedance profile of the PDN, we utilized the method described in [3], which is also similar to the method presented in [4]. In this method, the clock tree of a microprocessor is directly pumped by an external clock signal. At the same time, the processor is held in a reset state to ensure that the processor's only toggling gates are those in the clock tree. This provides a current draw that can be directly controlled by the injected clock signal [3]. The procedure for measuring the transient die voltage and the transient die current for our particular implementation of this metrology has been detailed in [5]. Once v(t) and i(t) are measured, the impedance of the PDN as seen by the die can be computed as

$$Z(f) = V(f)/I(f), \qquad (1)$$

where V(f) and I(f) denote the Fourier transforms of v(t) and i(t), respectively. For the stimulus used in this measurement it can be shown that i(t) is square pulse train, the frequency of which is equal to the frequency of the envelope of the injected clock signal [3]. Let this frequency be denoted by  $f_T$ . Then I(f) can be represented as

$$I(f) = \sum_{k=-\infty}^{\infty} a_k \delta(f - kf_T) = \sum_{k=-\infty}^{\infty} I_k(f) , \qquad (2)$$

where  $\delta(\cdot)$  is the Dirac delta function,  $a_0$  is the DC value of i(t),  $a_k = 0$  for even k,  $a_k = -jI_{pp}/(k\pi)$  for odd k, and  $I_{pp}$  is the peak-to-peak magnitude of i(t). Consequently, V(f) can be expressed as

$$V(f) = \sum_{k=-\infty}^{\infty} Z(kf_T) I_k(f) = \sum_{k=-\infty}^{\infty} V_k(f).$$

(3)

The impedance value at frequency  $kf_T$  can then be computed as

$$Z(kf_T) = V_k(f) / I_k(f).$$

(4)

Based on equations 1-4, the impedance "extraction" algorithm at a given  $f_T$  can be summarized as:

- 1. Measure (or in this case compute [5])  $I_k(f)$  for k = 1, ..., n.

- 2. Measure  $V_k(f)$  for k = 1, ..., n.

- 3. Compute  $Z_k(kf_T)$  for k = 1, ..., n.

Here, *n* is the actual number of harmonics used in the measurement with the assumption that there is a measurable amount of energy in  $V_n(f)$ . Once  $Z_k(f_T)$  for k = 1, ..., n is extracted, the value of  $f_T$  can be changed and the procedure can be repeated at this new frequency. By varying the value of  $f_T$ ,  $Z_k(f_T)$  can be extracted over a broad range of frequencies. Note that based on the choice of  $f_T$  values and *n*, some of the  $kf_T$  values for different  $f_T$  will be the same. This forms a self-consistency check for the measurement. If the PDN to be characterized is linear, then the impedance values extracted using these different harmonics will be identical.

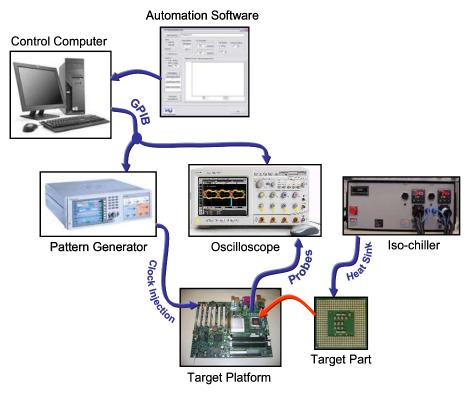

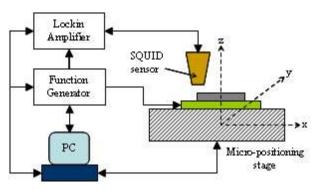

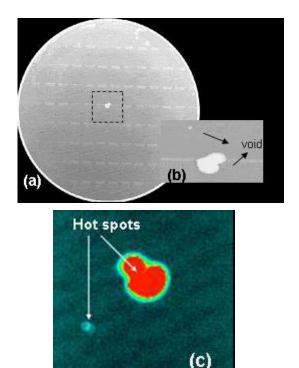

Figure 4: Equipment setup for impedance measurement

The equipment set up for the impedance measurement is illustrated in Figure 5. The injected clock signal is provided via a pattern generator. A high-bandwidth high-speed oscilloscope is used to measure v(t) and i(t). The results in this paper were obtained using an Agilent AG31104<sup>\*</sup> pattern generator and an Agilent AG54855A<sup>\*</sup> oscilloscope with 1134A high-impedance probes [6]. Both the magnitude and phase of  $V_k(f)$  were measured using the fast Fourier transform function of the oscilloscope. The measurements were performed under temperature controlled conditions using an USTC<sup>\*</sup> isochiller.

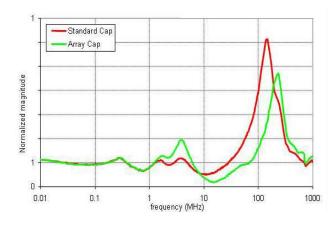

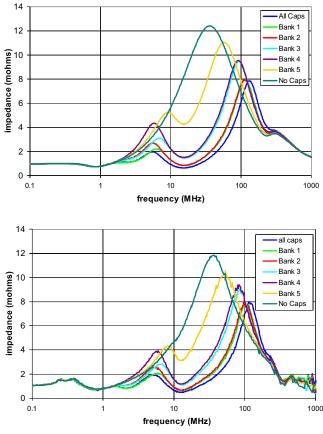

There are two main challenges in measuring the impedance as described above. The first one is to devise a method to cleanly inject a high-frequency clock signal into the processor clock tree from an external pattern generator. The clock frequencies utilized in this measurement are on the order of a GHz and injecting them through motherboard and package into the silicon requires special care. A special test motherboard was designed for this purpose where the traces for clock injection were routed using the shortest possible path through the motherboard. Similar care was applied to the design of the sense lines where the v(t) (or  $V_k(f)$ ) values were measured. The second challenge involves the labor associated with the measurement. Setting up the pattern generator and the oscilloscope manually at each frequency of the measurement to generate and measure the necessary waveforms is a very timeconsuming task. To resolve this issue an automation tool was developed using Visual Basic\*. At each frequency the measurement the automation software of communicates with the pattern generator and the oscilloscope through the General-Purpose-Interface-Bus (GPIB) and performs the necessary operations to compute the impedance. As a result of this automation the impedance profile of a typical PDN can be measured from Hz to hundreds of MHz in a matter of minutes. The impedance measurement technique was used to characterize the performance of various advanced decoupling solutions such as array capacitors [7]. One particular result from [7], which compares the performance of a package with an array capacitor to that of a package with standard package capacitors, is shown in Figure 6. As demonstrated by this figure the results obtained by this method unveil information regarding all the decoupling stages in the PDN in a very transparent way. This makes it very easy to compare different technologies in terms of their impact on the overall power delivery performance.

Figure 5: Measured impedance profiles for two packages with different capacitor solutions

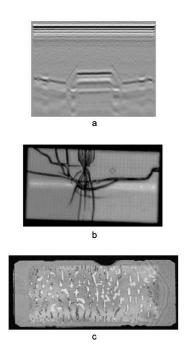

#### **Passive Power Delivery Measurements**

Although characterization of the impedance profile of a functional microprocessor PDN provides a good picture of the performance of the complete PDN system, it is off n desirable or necessary to examine individual components of a PDN outside of a functional system. Typically these passive measurements are helpful when there is a miscorrelation between measurement and modeling of the complete PDN, or when one desires to examine a new PDN component for use in the design of a system that is not yet available for active testing. In many of these cases the PDN component of interest is a high-performance decoupling capacitor. Typically these capacitors have ultra-low Equivalent Series Inductance (ESL) and Resistance (ESR), while maintaining high levels of capacitance. The space allotted to the PDN requires that the components have small form factors, and to achieve the desired high capacitance values, the internal spacing of the capacitor plates continues to decrease. Meanwhile the permittivity of the capacitor materials is also being driven higher. These two factors result in many of today's common PDN capacitors exhibiting non-linear behavior. Although non-linear capacitor behavior can be very complicated, to a first order approximation, the effective capacitance of a capacitor can be found by linearizing the capacitance around an operating point. Specifically, by measuring the capacitor's performance at different temperatures, DC biases, and AC signal levels, an effective value can be determined for a given use condition. This value can then be used in place of the manufacturer's specified value for modeling and for comparison of different capacitor solutions. This "use condition" value thus provides results that more closely resemble the real system performance because in a typical microprocessor system, the actual use condition is very much different from the conditions the capacitor experiences when the

<sup>\*</sup> Other brands and names are the property of their respective owners.

industry-standard measurement techniques are used. Generally these industry-standard techniques involve capacitor measurement at room temperature with no DC bias, and they utilize an AC test signal that may be 1 volt or more. This is in stark contrast to the typical conditions seen in a CPU PDN. Most of today's CPU decoupling capacitors will experience temperatures that may exceed 50°C, with 1 to 2 V DC bias, and will never see AC signals above 100mV or so.

From a practical viewpoint, it is difficult to decide on one correct use condition that is appropriate for all microprocessors. Thus, simply changing the industrystandard measurement to a different set of conditions does not universally solve this problem. Additionally, in many situations multiple products are supported by a given package and decoupling technology generation. In these cases there may be many different use conditions for a given type of decoupling capacitor.

To enable practical use condition measurements an automated system is used to collect capacitor performance data at a large number of varying use conditions. In a typical case the system may examine the effective capacitance provided by a device as the temperature, DC bias, and AC signal levels are swept from 0°C - 100°C, 0VDC - 3VDC, and 5mVrms -100mVrms, respectively. These data are then least squares fit to an 11-term, second-order polynomial in three variables (T, VDC, VAC), allowing for a compact representation of the large data set. This method was selected after studying the measured data for a number of different capacitor types, and it has been shown to be able to reproduce the original measured data with reasonable accuracy. End users of this information can simply load the coefficients describing the capacitor's performance into a custom calculator tool, or can manually calculate a result, to determine an appropriate effective capacitance for their application.

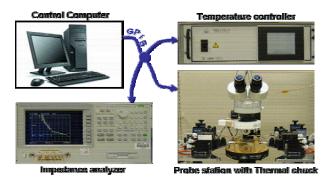

One system that utilizes this technique to characterize package and motherboard decoupling capacitors is shown in Figure 7. This system utilizes a GPIB instrumentation bus to link a control computer to an Agilent 4294A<sup>\*</sup> impedance analyzer, a Trio-Tech TC1000<sup>\*</sup> thermal control chuck, and a Stanford Research SR630<sup>\*</sup> thermocouple reader. A custom software package has been developed to allow convenient adjustment of the sweep parameters and to perform the least squares fitting of the measured data.

Figure 6: System for characterizing use condition capacitance

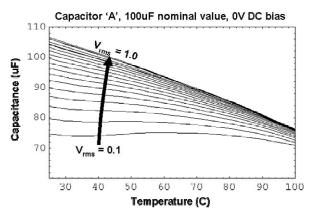

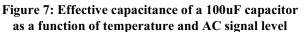

Figure 8 shows an example of a measurement performed on a sample capacitor. In this case the manufacturer, using the industry-standard measurement technique, has specified this capacitor as a 100uF device. The data shown in Figure 8 demonstrate that this capacitor achieves an effective capacitance of 100uF only at high AC test signal levels, and at moderate temperatures with no bias. At conditions more relevant to a microprocessor PDN, the effective capacitance is in the 80uF range or less.

With the significant variation in effective capacitance due to use condition parameters, it is important that PDN modeling activities utilize the use condition effective capacitance values; otherwise, the correlation between modeled and measured results will be poor.

# MODELING THE POWER DELIVERY NETWORK

Since most design decisions are made prior to the availability of first silicon, and therefore a functional test system, it is important to have a good power delivery simulation model to assist with these decisions. In the past, simple lumped element models have been used to model the power delivery network. However, more

<sup>\*</sup> Other brands and names are the property of their respective owners.

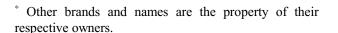

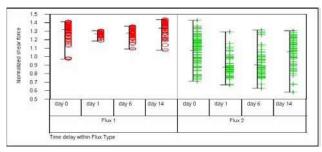

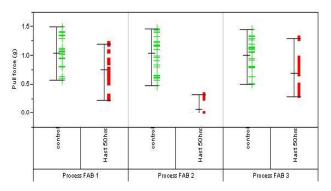

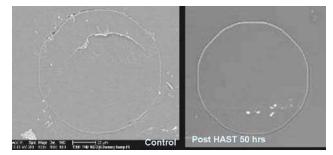

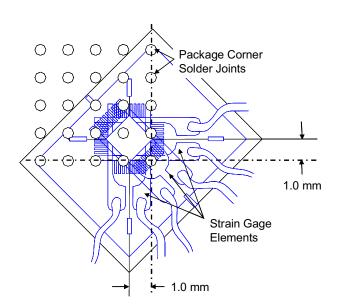

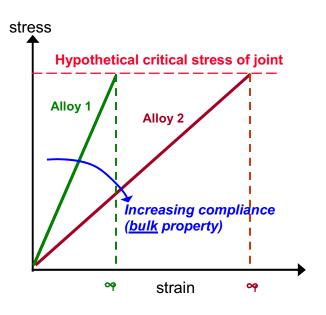

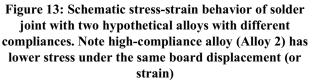

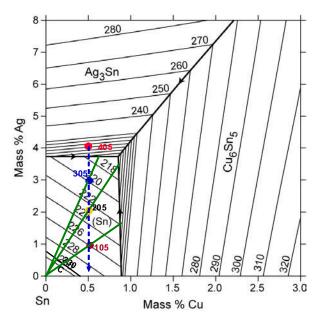

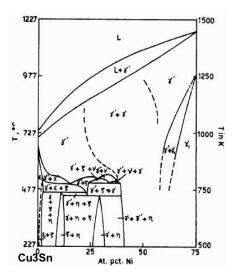

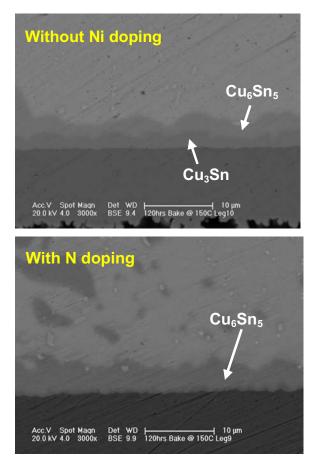

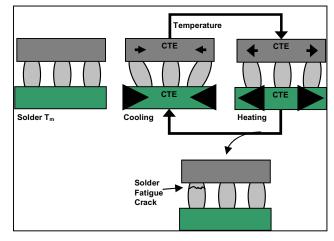

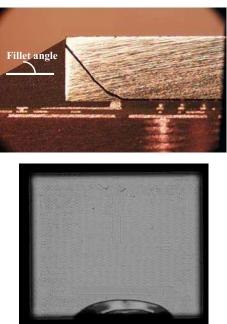

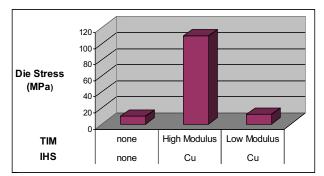

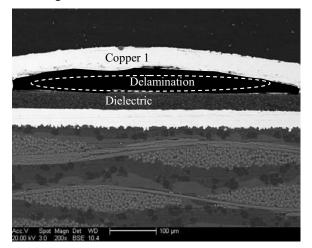

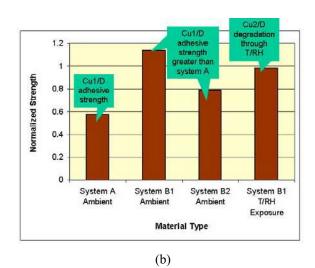

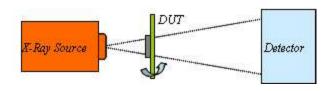

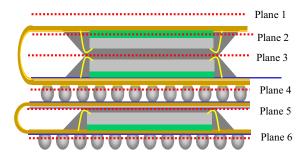

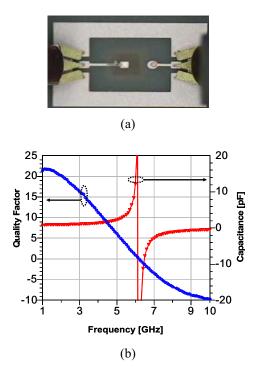

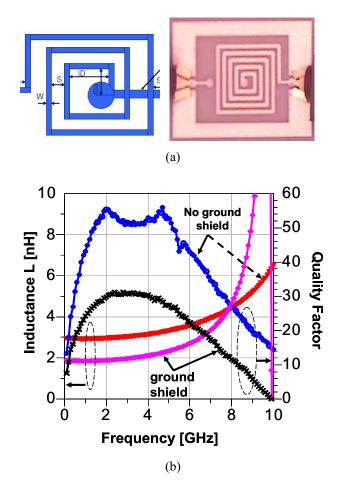

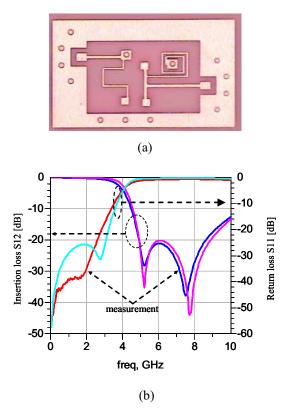

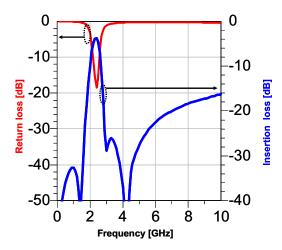

recently with the shrinking power delivery impedance targets, it becomes more important to include additional details that capture the non-uniform loading of the die and the spatial location of the power delivery components. For this reason, detailed distributed models of the package and the motherboard have replaced the traditional lumped element model for power delivery analysis.