# Intel<sup>®</sup> Ethernet Adaptive Virtual Function (AVF) Hardware Architecture Specification (HAS)

**Networking Division**

336311-002 Revision: 1.0 February 2018

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

The products and services described may contain defects or errors which may cause deviations from published specifications. Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting <a href="https://www.intel.com/design/literature.htm">www.intel.com/design/literature.htm</a>.

$Intel\ and\ the\ Intel\ logo\ are\ trademarks\ of\ Intel\ Corporation\ in\ the\ U.S.\ and/or\ other\ countries.$

$\ensuremath{^{*}}$  Other names and brands may be claimed as the property of others.

Copyright © 2018, Intel Corporation. All Rights Reserved.

# **Revisions**

| Revision | Date           | Notes                             |                                                               |

|----------|----------------|-----------------------------------|---------------------------------------------------------------|

| 0.4      | September 2017 | 7 • First Release (Intel Public). |                                                               |

| 1.0      | February 2018  | •                                 | Updated section 2.0 (LAN Queue Interface; descriptor tables). |

# **Content**

| 1.0            |                     | ion                                                                        |             |

|----------------|---------------------|----------------------------------------------------------------------------|-------------|

| 1.1            |                     |                                                                            |             |

|                | 1.1.1               | Mailbox                                                                    | 7           |

|                | 1.1.2               | Queue Pairs                                                                | 7           |

|                | 1.1.3               | Interrupts                                                                 | 8           |

|                | 1.1.4<br>1.1.5      | Tx Offloads                                                                | ŏ           |

| 1.2            |                     | Software Flows                                                             | o           |

| 1.2            | 1.2.1               | Driver Identification                                                      | 8           |

|                | 1.2.2               | Feature Query                                                              | 9           |

|                | 1.2.3               | Device Configuration                                                       | 9           |

| 1.3            | Supported           | Hardware                                                                   | 9           |

| 2.0            |                     | e Interface                                                                |             |

| 2.1            | Receive Ou          | leues                                                                      | 11          |

| 2.1            | 2.1.1               | Receive Oueue Ring                                                         | .11         |

|                | 2.1.2               | Receive Queue Descriptor                                                   | .12         |

|                | 2.1.2.1             | Receive Descriptor - Read Format                                           | .12         |

|                | 2.1.2.2             | Receive Descriptor (Write Back Format)                                     | .13         |

|                | 2.1.3               | Dummy Receive Descriptors                                                  |             |

|                | 2.1.4               | Receive_Init_Flows                                                         | .16         |

|                | 2.1.5               | Packet Receive Flow                                                        | .1/         |

|                | 2.1.5.1<br>2.1.5.2  | Receive Descriptors Preparation and Tall Bump                              | . 1 /       |

|                | 2.1.5.2<br>2.1.6    | Descriptor Write Back Basic Receive Offloads                               | 10          |

|                | 2.1.6.1             | Strip Ethernet CRC Bytes                                                   | 12          |

|                | 2.1.6.2             | VI AN Extraction                                                           | 1Ω          |

|                | 2.1.6.3             | Receive L3 and L4 Integrity Check Offload                                  | .18         |

|                | 2.1.6.4             | RSS Support                                                                | . 19        |

| 2.2            | Transmit Q          | ueues                                                                      | .20         |

|                | 2.2.1               | Transmit Oueue Ring                                                        | .20         |

|                | 2.2.2               | Transmit Queue Descriptor                                                  | .21         |

|                | 2.2.2.1             | General Descriptors                                                        | .21         |

|                | 2.2.2.2             | Transmit Data Descriptor                                                   | . 22        |

|                | 2.2.2.3             | LAN Transmit Context Descriptors                                           | . 25        |

|                | 2.2.3<br>2.2.4      | Transmit init Flows                                                        | . 20        |

|                | 2.2.5               | Stateless Transmit Offloads                                                | 26          |

|                | 2.2.5.1             | L2 Offloads                                                                | 26          |

|                | 2.2.5.2             | VLAN Insertion                                                             | .26         |

|                | 2.2.5.3             | Transmit L3 and L4 Integrity Offload                                       | .27         |

|                | 2.2.5.4             | Transmit Segmentation Offload (TSO or LSO)                                 | .29         |

| 3.0            | Interrupts          | S                                                                          | 33          |

| 3.1            | MSI-X Vect          | ors                                                                        | 33          |

| 0.2            | 3.1.1               | Interrupt Enable Procedure                                                 | .33         |

|                | 3.1.2               | Pending Bit Array (PBA)                                                    | .33         |

|                | 3.1.3               | Interrupt Sequence                                                         | .34         |

|                | 3.1.3.1             | MSI-X Interrupts While Interrupts are Disabled by the Operating System     | . 34        |

| 3.2            | Interrupt C         | auses                                                                      | . 34        |

|                | 3.2.1               | LAN Transmit Queues                                                        | . 35        |

|                | 3.2.2<br>3.2.3      | LAN Receive Queues                                                         | . 33        |

|                | 3.2.3<br>3.2.4      | Other Interrupt Causes                                                     | . 35        |

|                | 3.2.5               | Software Initiated Interrupt                                               | 36          |

| 3.3            |                     | foderation and Link List                                                   |             |

| 3.3            | 3.3.1               | Interrupt Throttling (ITR)                                                 | .36         |

| 4.0            |                     |                                                                            |             |

| <b>4.0</b> 4.1 | Mailbox Do          | gisters and Command Format                                                 | . <b>3/</b> |

| 4.1            | 4.1.1               | Mailbox Oueue CSRs                                                         |             |

|                | 4.1.2               | Error Codes                                                                |             |

|                | 4.1.2.1             | Critical Error Indication                                                  |             |

|                | 4.1.3               | Commands Description                                                       | .40         |

|                | 4.1.3.1             | Direct Command.                                                            | .40         |

|                | 4.1.3.2             | Indirect Command                                                           | .42         |

| 4.2            | Command             | opcodes                                                                    | .43         |

| 4.3            | Mailbox Ini         | tialization Flow<br>Receive Queue Element Initialization by the AVF Driver | .44         |

|                |                     | Receive Queue Element Initialization by the AVF Driver                     | . 44        |

| 4.4            | 4.3.2               | Driver Unload and Queue Shutdown                                           | .45         |

| 4.4            | Mailbox Co<br>4.4.1 | mmands                                                                     |             |

|                | 7.7.1               | JUNE PICARUC LU I I CUITITIBILE III III III III III III III III III        | . +.)       |

|                   | 4.4.2<br>4.4.3                          | Incoming Message From PF MailboxQueue Shutdown Command                                                                                                                                                                                                                                                                                                               | 46<br>47   |

|-------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.0               |                                         | lity Features                                                                                                                                                                                                                                                                                                                                                        | 40         |

| 5.1               | Advanced                                | Rx Offloads                                                                                                                                                                                                                                                                                                                                                          | 49         |

| 5.2               |                                         |                                                                                                                                                                                                                                                                                                                                                                      |            |

| 6.0               |                                         | Flows                                                                                                                                                                                                                                                                                                                                                                |            |

| 6.1               |                                         | DEVEO 125 E 1                                                                                                                                                                                                                                                                                                                                                        | 51         |

|                   | 6.1.1<br>6.1.2                          | PF-VF Capability Exchange<br>Tx and Rx Initialization                                                                                                                                                                                                                                                                                                                | 52         |

| 6.2               |                                         | r PF-VF Software Protocol.                                                                                                                                                                                                                                                                                                                                           | 53         |

| 0.2               | 6.2.1                                   | Software Protocol                                                                                                                                                                                                                                                                                                                                                    | 53         |

|                   | 6.2.1.1                                 | Software Opcodes                                                                                                                                                                                                                                                                                                                                                     |            |

|                   | 6.2.1.2<br>6.2.1.3                      | Error Codes                                                                                                                                                                                                                                                                                                                                                          | 55         |

|                   | 6.2.1.4                                 | Adding New Offloads/Capabilities                                                                                                                                                                                                                                                                                                                                     | 55<br>55   |

|                   | 6.2.2                                   | Event Handling                                                                                                                                                                                                                                                                                                                                                       | 56         |

| 6.3               |                                         | r for AVF                                                                                                                                                                                                                                                                                                                                                            |            |

|                   | 6.3.1<br>6.3.1.1                        | Initialization/Pre-configure FlowPF-VF Capability Exchange                                                                                                                                                                                                                                                                                                           | 56         |

|                   | 6.3.2                                   | Tx and Rx Initialization                                                                                                                                                                                                                                                                                                                                             | 57         |

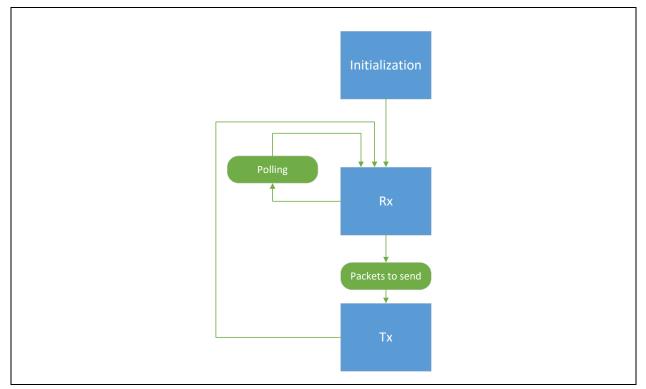

|                   | 6.3.3                                   | Receive and Transmit Flows                                                                                                                                                                                                                                                                                                                                           | 57         |

|                   | 6.3.3.1                                 | Receive Burst                                                                                                                                                                                                                                                                                                                                                        |            |

|                   | 6.3.3.2<br>6.3.4                        | Transmit Burst Flow DPDK Forwarding Application Example                                                                                                                                                                                                                                                                                                              | 59<br>59   |

| 7.0               |                                         | egisters - VF                                                                                                                                                                                                                                                                                                                                                        |            |

| <b>7.0</b><br>7.1 | BARO Regi                               | isters Summary                                                                                                                                                                                                                                                                                                                                                       | <b>61</b>  |

| 7.2               | Detailed R                              | egister Description - VF BAR0                                                                                                                                                                                                                                                                                                                                        | 62         |

|                   | 7.2.1                                   | VF - General Registers<br>VF Reset Status - VFGEN_RSTAT (0x00008800; RW)                                                                                                                                                                                                                                                                                             | 62         |

|                   | 7.2.1.1<br>7.2.2                        | VF Reset Status - VFGEN_RSTAT (0x00008800; RW)VF - Interrupts                                                                                                                                                                                                                                                                                                        | 62         |

|                   | 7.2.2.1                                 | VF Interrupt Dynamic Control Zero - VEINT DYN CTI 0 (0x00005C00: RW)                                                                                                                                                                                                                                                                                                 | 62         |

|                   | 7.2.2.2                                 | VF Interrupt Dynamic Control Zero - VFINT_DYN_CTL0 (0x00005C00; RW)VF Interrupt Dynamic Control N - VFINT_DYN_CTLN[n] (0x00003800 + 0x4*n, n=063;                                                                                                                                                                                                                    | RW)        |

|                   | 7.2.2.3                                 | 63                                                                                                                                                                                                                                                                                                                                                                   | <i>C</i> 1 |

|                   | 7.2.2.3<br>7.2.2.4                      | VF Interrupt Throttling Zero - VFINT_ITR0[n] (0x00004C00 + 0x4*n, n=02; RW) VF Interrupt Throttling N - VFINT_ITRN[n,m] (0x00002800 + 0x4*n + 0xC*m, n=02, m=063; RW)                                                                                                                                                                                                | 04         |

|                   | , , , , , , , , , , , , , , , , , , , , | m=063; RW)                                                                                                                                                                                                                                                                                                                                                           | 64         |

|                   | 7.2.3                                   | VE - CONTROL CHARGE                                                                                                                                                                                                                                                                                                                                                  | 64         |

|                   | 7.2.3.1<br>7.2.3.2                      | VF MailBox Transmit Queue Base Address Low - VF_ATQBAL (0x00007C00; RW)VF MailBox Transmit Queue Base Address High - VF_ATQBAH (0x00007800; RW)                                                                                                                                                                                                                      | 64         |

|                   | 7.2.3.2                                 | VF MailBox Transmit Queue base Address High - VF_ATQBAH (0X0007600, KW)                                                                                                                                                                                                                                                                                              | 65         |

|                   | 7.2.3.4                                 | VF MailBox Transmit Queue Length - VF_ATQLEN (0x00006800; RW)                                                                                                                                                                                                                                                                                                        | 65         |

|                   | 7.2.3.5                                 | VF MailBox Transmit Tail - VF_ATQT (0x00008400; RW)                                                                                                                                                                                                                                                                                                                  | 65         |

|                   | 7.2.3.6<br>7.2.3.7                      | VF MailBox Receive Queue Base Address Low - VF_ARQBAL (UXUUUU6CUU; RW)                                                                                                                                                                                                                                                                                               | 65         |

|                   | 7.2.3.8                                 | VF MailBox Receive Queue Length - VF AROLEN (0x00008000: RW)                                                                                                                                                                                                                                                                                                         | 66         |

|                   | 7.2.3.9                                 | VF MailBox Transmit Tail - VF_ATQT (0x00008400; RW)                                                                                                                                                                                                                                                                                                                  | 66         |

|                   | 7.2.3.10                                | VF MailBox Receive Tail - VF_ARQT (0x00007000; RW)                                                                                                                                                                                                                                                                                                                   | 66         |

|                   | 7.2.4<br>7.2.4.1                        | VF - LAN Transmit and receive registers                                                                                                                                                                                                                                                                                                                              | 67         |

|                   | 7.2.4.2                                 | Transmit Queue Tail - QTX_TAIL[QTX] (0x00000000 + 0x4*QTX, QTX=0255; RW)  Receive Queue Tail - QRX_TAIL[QRX] (0x00002000 + 0x4*QRX, QRX=0255; RW)                                                                                                                                                                                                                    | 67         |

| 7.3               | BAR3 Regi                               | isters Summary                                                                                                                                                                                                                                                                                                                                                       | 6/         |

| 7.4               | Detailed R<br>7.4.1                     | egister Description - VF BAR3MSI-X Table Registers                                                                                                                                                                                                                                                                                                                   | 67         |

|                   | 7.4.1<br>7.4.1.1                        | MSI-X Habile Registers - 1 ow - MSIX TADD[n] (0x000000000 + 0x10*n n=0 64 RW)                                                                                                                                                                                                                                                                                        | 67<br>68   |

|                   | 7.4.1.2                                 | MSI-X Message Address High - MSIX TUADD[n] (0x00000004 + 0x10*n, n=064; RW)                                                                                                                                                                                                                                                                                          | 68         |

|                   | 7.4.1.3                                 | MSI-X Message Data - MSIX_TMSG[n] (0x00000008 + 0x10*n, n=064; RW)                                                                                                                                                                                                                                                                                                   | 68         |

|                   | 7.4.1.4<br>7.4.1.5                      | MSI-X Message Address Low - MSIX_TADD[n] (0x00000000 + 0x10*n, n=064; RW)  MSI-X Message Address High - MSIX_TUADD[n] (0x00000004 + 0x10*n, n=064; RW)  MSI-X Message Data - MSIX_TMSG[n] (0x00000008 + 0x10*n, n=064; RW)  MSI-X Vector Control - MSIX_TVCTRL[n] (0x0000000C + 0x10*n, n=064; RW)  MSI-X PBA Structure - MSIX_PBA[n] (0x00008000 + 0x4*n, n=02; RO) | 68         |

| 7.5               | Register S                              | ubset for Modified Driver                                                                                                                                                                                                                                                                                                                                            | 69         |

|                   |                                         |                                                                                                                                                                                                                                                                                                                                                                      |            |

| adde              | :IIUIX AVIIT                            | ual Channel Protocol                                                                                                                                                                                                                                                                                                                                                 | /1         |

# 1.0 Introduction

This document describes the hardware interface of a Single Root I/O Virtualization (SR-IOV) Virtual Function (VF) that is compatible with the AVF driver. It also describes the interface between the AVF driver and a compliant Physical Function (PF) driver used to negotiate the capabilities of the VF driver/hardware/PF combination.

The Intel® Ethernet 700 Series supports an AVF compliant interface.

## 1.1 Features

The following minimal features are supported by the AVF driver:

- 1. A mailbox to the PF driver

- 2. 4 Rx and Tx queue pairs

- 3. 5 MSI-X interrupts

- 4. Per vector interrupt moderation

- 5. An RSS table of 64 entries that can point to up to 4 queues

- 6. Basic Rx and Tx offloads (checksum and TSO for non-tunneled packets).

The following features are optional and might be exposed by the hardware:

- 1. More queues or more interrupts.

- 2. Extension of the RSS table so that it can point to a larger number of queues/use more entries

- 3. RDMA support

- 4. VF VLAN trunking

- 5. VF promiscuous

- 6. Negotiate header-split

- 7. Negotiate Tx checksum/TSO for tunneled packets

# 1.1.1 Mailbox

The mailbox described in Section 4.0 is a descriptor ring initiated by the AVF driver and can be used for communication with the PF driver for capabilities guery and for configurations.

# 1.1.2 Queue Pairs

The AVF driver exposes at least four Tx and Rx queues. Each queue is initialized by the PF driver upon a request from the AVF driver. The AVF driver then manages the descriptor ring independently. Receive queues are described in Section 2.1 and transmit queues in Section 2.2.

# 1.1.3 Interrupts

The AVF driver exposes at least five MSI-X vectors mapped in BAR3 of the config space. These vectors can be associated with queue write-back events, or with control events using registers accessible by the AVF driver. The interrupts can also be directly moderated using registers accessible by the AVF driver. The interrupt mechanism is described in Section 3.0.

Note:

While MSI-X vectors are provided by the hardware and the AVF kernel drivers uses these interrupts, a poll mode driver might be implemented on an AVF compliant hardware. Refer to Appendix A for details of a polling mode driver operation.

### 1.1.4 Rx Offloads

The AVF driver exposes a set of receive offloads. Namely, it supports RSS, receive CRC and checksum, and VLAN extraction to the receive descriptor as described in Section 2.1.6.

### 1.1.5 Tx Offloads

The AVF driver exposes a set of stateless transmit offloads. Namely, it supports LSO, transmit checksum, VLAN insertion from the transmit descriptor as described in Section 2.2.5.

# 1.2 AVF Driver Software Flows

The AVF driver software flows (init and run time) are described in Section 6.0.

## 1.2.1 Driver Identification

The AVF driver recognizes devices according to the following identification strings.

**Note:** The following driver identification string device IDs can be used for all Intel devices that support AVF.

### **Table 1-1.** Driver Identification Strings

| Vendor ID | Device ID | Sub Vendor<br>ID | Sub Device ID Code Name |                                                        | Branding String                                       |

|-----------|-----------|------------------|-------------------------|--------------------------------------------------------|-------------------------------------------------------|

| 0x8086    | 0x1889    | *                | *                       | Virtualization AVF device for non-Windows* hypervisors | Intel <sup>®</sup> Ethernet Adaptive Virtual Function |

| 0x8086    | 0x1889    | 0x8086           | 0x0001                  | Virtualization AVF device for Windows HyperV           | Intel <sup>®</sup> Ethernet Adaptive Virtual Function |

# **1.2.2** Feature Query

The AVF driver can discover which features are available in hardware as described in Section 6.1.

# **1.2.3** Device Configuration

The AVF driver can request from the PF configurations required for its operation like queue init or new filters as described in Section 6.2.

# 1.3 Supported Hardware

The following devices are compatible with AVF drivers:

- Intel® Ethernet Controller X710, XL710, and XXV710

- Intel® Ethernet Connection X722

Other products will be added in the future.

NOTE: This page has been intentionally left blank.

# 2.0 LAN Queue Interface

# 2.1 Receive Queues

This section includes the following topics:

- Storage of receive packets in system memory.

- Receive descriptor queues description (such as descriptor rings).

- Ring management Indication of free descriptors to the hardware and indication of completed descriptors back to the software.

# 2.1.1 Receive Queue Ring

Received packets are posted to host memory through a set of queues. Each queue is a cyclic ring made of a sequence of receive descriptors in contiguous memory. These queues are also called descriptor rings. The AVF driver supports up to four receive queues allocated to the VF. Receive queues are defined by a set of parameters called the queue context. The queue context is managed by the PF driver and it is out of the scope of this document. Only the tail registers (needed at run time) are accessible to the AVF driver. Part of these context parameters are kept in hardware (like the tail register, queue enable / disable flags and interrupt related context).

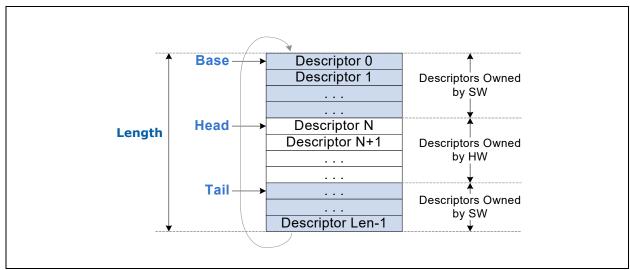

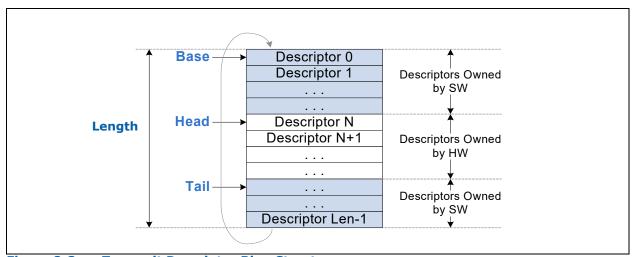

Figure 2-1. Receive Descriptor Ring Structure

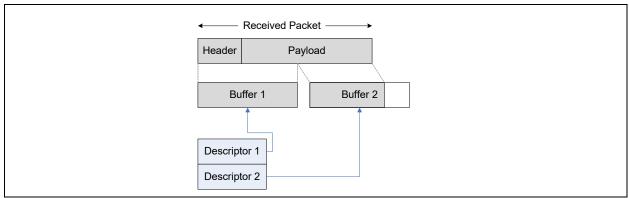

Receive buffers prepared in the system (host) memory buffers are indicated to hardware by descriptors in the ring. There are several types of descriptors detailed in Section 2.1.2. These include pointers to the data buffers and status indications of the received packets. Figure 2-2 shows two examples of receive packets in host memory composed of two buffers (indicated by two matched descriptors).

A few rules related to receive packet posting to host memory are:

- Receive packets might span one to five buffers (descriptors).

- Receive packets shorter than 64 bytes are never posted to host memory.

Figure 2-2. Receive Packet in System Memory

# 2.1.2 Receive Queue Descriptor

### 2.1.2.1 Receive Descriptor - Read Format

### 2.1.2.1.1 16-byte Receive Descriptors Read Format

Following is the 16-byte receive descriptor read format prepared by software.

**Table 2-1. 16-byte Receive Descriptors Read Format**

| Quad<br>Word | 63                    |

|--------------|-----------------------|

| 0            | Packet Buffer Address |

| 1            | Reserved (0x0)        |

|              | 63 0                  |

### **Packet Buffer Address (64)**

The physical address of the packet buffer defined in byte units. The packet buffer size is defined by the DBUFF parameter in the receive queue context.

## 2.1.2.1.2 32-byte Receive Descriptors Read Format

Following is the 32-byte receive descriptor read format prepared by software.

Table 2-2. 32-byte Receive Descriptors Read Format

| Quad<br>Word | 63                    | כ |

|--------------|-----------------------|---|

| 0            | Packet Buffer Address |   |

| 1            | Reserved (0x0)        |   |

| 2            | Reserved (0x0)        |   |

| 3            | Reserved (0x0)        |   |

|              | 63                    | 5 |

The fields in first 16 bytes are identical to the 16-byte descriptors described in Section 2.1.2.1.1.

# **2.1.2.2** Receive Descriptor (Write Back Format)

The following subsections describe the fields of the Receive Descriptor as written back by hardware when using 16-byte and 32-byte descriptors. In both cases, a single packet might span on a single buffer or multiple buffers as reported by their matched descriptors. If a packet is described by a single descriptor then all the fields are valid. Following are some rules that apply for a packet that is described by multiple descriptors:

- The following fields are valid in all descriptors of a packet: DD flag (Done); EOP flag (End of Packet) and PKTL field (Packet content length).

- All other fields are valid only in the last descriptor of a packet.

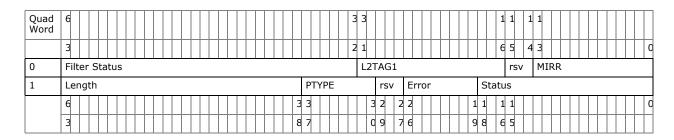

# 2.1.2.2.1 16-byte Legacy Receive Descriptors WB Format

Following is the 16-byte receive descriptor Write Back (WB) format.

Reserved/RSV (Quad Word 1, 3 bits, Quad Word 0, 2 bits)

Reserved.

Status Field (Quad Word 1, 19 bits)

| Bits  | Name      | Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     | DD        | Descriptor done indication flag.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 1     | EOP       | End of packet flag is set to 1b indicating that this descriptor is the last one of a packet.                                                                                                                                                                                                                                                                                                                                                                     |  |

| 2     | L2TAG1P   | VLAN presence indication while the VLAN tag is stripped from the packet and reported in the L2TAG1 field in the descriptor.                                                                                                                                                                                                                                                                                                                                      |  |

| 3     | L3L4P     | For IP packets, this flag indicates that detectable L3 and L4 integrity check is processed by hardware. See Section 2.1.6.3 for details on which headers are processed and how.                                                                                                                                                                                                                                                                                  |  |

| 4     | CRCP      | CRCP indicates that the Ethernet CRC is posted with data to the host buffer. Note that strip CRC is enabled by the VIRTCHNL_VF_OFFLOAD_L2 capability.  If the RXE error flag is set, the CRC bytes are not stripped regardless of the CRCStrip flag in the queue context. Loop back packets originated by another local VSI for which the hardware computes the CRC are never posted with the CRC bytes regardless of the CRCStrip setting in the queue context. |  |

| 8:5   | Reserved  | Reserved. Set to 0x0 by hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 9:10  | UMBCAST   | Destination address can be one of the following:  • 00b = Unicast  • 01b =- Multicast  • 10b = Broadcast  • 11b = Reserved  Non-parsed packets are indicated by PTYPE equals to PAYLOAD (non identified MAC header).                                                                                                                                                                                                                                             |  |

| 11    | Reserved  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 12:13 | FLTSTAT   | The FLTSTAT indicates the reported content in the <i>Filter Status</i> field.  00b = Reserved.  10b = Reserved.  11b = Hash filter signature (RSS).                                                                                                                                                                                                                                                                                                              |  |

| 14    | LPBK      | Loop back indication meaning that the packet is originated from this system rather than the network.                                                                                                                                                                                                                                                                                                                                                             |  |

| 15    | IPV6EXADD | Set when an IPv6 packet contains a Destination Options Header or a Routing Header. If the packet contains two IPv6 headers (tunneling), the IPv6EXADD is a logic 'OR' function of the two IP headers.                                                                                                                                                                                                                                                            |  |

| 16:17 | Reserved  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 18    | INT_UDP_0 | This flag is set for received UDP packets on which the UDP checksum word equals to zero.  Note that UDP checksum zero is an indication that there is no checksum. This option is valid only for IPv4 packets and considered an exception error for IPv6 packets (reported to the stack by the driver).                                                                                                                                                           |  |

### **Error Field (Quad Word 1, 8 bits)**

### Table 2-3. Error Bits

| Bits | Name     | Functionality                                                                                                                                                                                                                                                                                                                                                           |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:0  | RSV      | Reserved                                                                                                                                                                                                                                                                                                                                                                |

| 3:5  | L3L4E    | For IP packets processed by hardware, the L3L4E flag has the following encoding:  Bit 3 = IPE: IP checksum error indication.  Bit 4 = L4E: L4 integrity error indication.  Bit 5 = Reserved for the purpose of these bits, a tunneled packet is a packet with an inner IP header. For example, a VXLAN packet without an inner IP is not considered as a tunnel packet. |

| 6    | OVERSIZE | Oversize packet error indicates that the packet is larger than five descriptors. In this case the portions of the packet that exceeds the permitted number of descriptor(s) is not posted to host memory.                                                                                                                                                               |

| 7    | RSV      | Reserved                                                                                                                                                                                                                                                                                                                                                                |

### L2TAG1 (Quad Word 0, 16 bits)

Stripped L2 VLAN Tag from the receive packet. This field is valid if the L2TAG1P flag in this descriptor is set (see additional description of the L2TAG1P flag). The L2TAG1 includes the VLAN tag if enabled via VIRTCHNL\_VF\_OFFLOAD\_VLAN capability.

### Filter Status (Quad Word 0, 32 bits)

- If the packet matches the Hash filter, then FLTSTAT equals 11b and this field contains the hash signature (RSS).

- Else, FLTSTAT equals 00b and this field is set to zero.

### Length (Quad Word 1, 26 bits)

| Bits  | Name     | Functionality                                                     |  |

|-------|----------|-------------------------------------------------------------------|--|

| 0:13  | PKTL     | Packet content length in the packet buffer defined in byte units. |  |

| 14:25 | Reserved | Reserved                                                          |  |

### PTYPE (Quad Word 1, 8 bits)

Packet Type field encodes supported packet types as listed in Table 2-4.

### **Table 2-4.** Packet Types

PTYPES that are preserved for base-mode support.

| PTYPE     | Description     | PTYPE | Description            |  |  |

|-----------|-----------------|-------|------------------------|--|--|

| L2 Packet | L2 Packet Types |       |                        |  |  |

| 0         | Reserved        | 11    | MAC, ARP               |  |  |

| 1         | MAC, PAY2       | 12    | MAC, PAY3 <sup>1</sup> |  |  |

<sup>1.</sup> PTYPE 12 should be ignored.

| PTYPE    | Description           | PTYPE             | Description              |

|----------|-----------------------|-------------------|--------------------------|

| Non-tunn | eled IPv4             | Non-tunneled IPv6 |                          |

| 22       | MAC, IPvV4FRAG, PAY3  | 88                | MAC, IPv6+IPv6FRAG, PAY3 |

| 23       | MAC, IPv4, PAY3       | 89                | MAC, IPv6, PAY3          |

| 24       | MAC, IPv4, UDP, PAY4  | 90                | MAC, IPv6, UDP, PAY4     |

| 25       | Reserved              | 91                | Reserved                 |

| 26       | MAC, IPv4, TCP, PAY4  | 92                | MAC, IPv6, TCP, PAY4     |

| 27       | MAC, IPv4, SCTP, PAY4 | 93                | MAC, IPv6, SCTP, PAY4    |

| 28       | MAC, IPv4, ICMP, PAY4 | 94                | MAC, IPv6, ICMP, PAY4    |

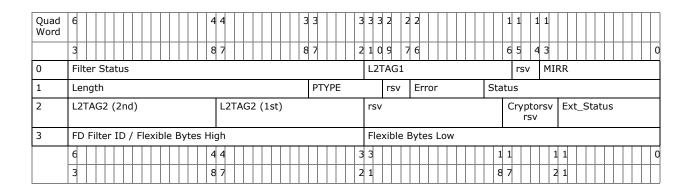

### 2.1.2.2.2 32-byte Receive Descriptors Write Back Format

The 32-byte descriptor is composed of four quad words. The first two Qwords are identical to the 16-byte descriptor write back.

# 2.1.3 Dummy Receive Descriptors

In some cases, hardware might reserve one more descriptor than needed for a given packet. In this case, this dummy descriptor is written back as the last descriptor of the packet with a data length field == 0. For this packet, the dummy descriptor carries all the flags that are normally written at the last descriptor of a multi-descriptors packets. A dummy descriptor might occur in both 16- and 32-byte formats.

# 2.1.4 Receive Init Flows

The receive init flow is described in Section 6.1.2.

### 2.1.5 Packet Receive Flow

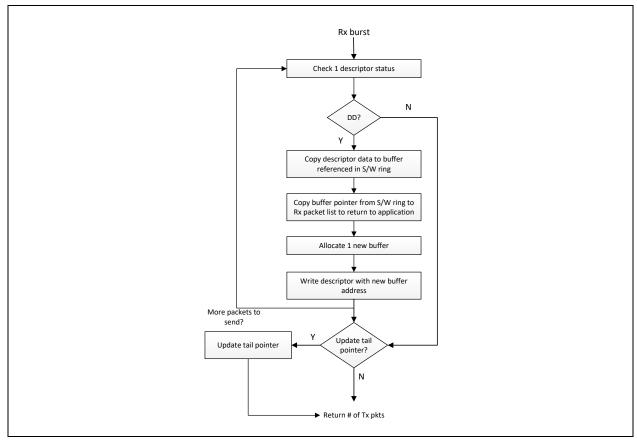

## 2.1.5.1 Receive Descriptors Preparation and Tail Bump

During normal operation, the AVF driver accesses hardware directly using the following flow:

- Prepare receive descriptors by clearing the *DD* bit and setting the buffer pointer(s). Start at the descriptor indicated by the TAIL pointer in the relevant QRX\_TAIL register (Section 7.2.4.2).

- Software should never set the TAIL to a value above the descriptors owned by hardware minus 1. The descriptors considered as owned by hardware are those ones already indicated to hardware but not yet reported as completed.

- Bump the TAIL to the last prepared descriptor plus one.

# 2.1.5.2 Descriptor Write Back

Hardware reports a completion of receive packet in host memory by status indication in the receive descriptor(s) of the packet (descriptor write back). Hardware writes back completed descriptor status in one of the following cases:

- Entire lines of descriptors (4 x 32-byte descriptors or 8 x 16-byte descriptors) are completed.

- In systems that supports a cache based queue context, all completed descriptors of a queue evicted from the internal cache

- Upon assertion of the interrupt associated with the queue.

- If the queue is configured for No Expire then every completed descriptor is written back immediately.

**Note:** If the number of free descriptors available to hardware is lower than a threshold set by the PF driver, then an immediate interrupt is triggered.

In some systems, while in polling mode, the write backs might not fit into any of the previously mentioned categories and the AVF driver might detect that there are a few descriptor write backs (less than a cache line) pending for longer than expected. As a result, the AVF driver triggers a software interrupt to force a write back.

Most applications use interrupts to invoke the AVF driver. Before initiating the interrupt, hardware posts all completed descriptors of the queue that might be kept in the device caches. Following an interrupt assertion, the device masks any further interrupts preventing interrupt nesting. When the interrupts are re-enabled (by software), additional interrupts that trigger additional write-back of completed descriptors can be initiated.

In some applications, the AVF driver works in polling mode (with no interrupts). Configuring this option is done by asking for the VIRTCHNL\_VF\_OFFLOAD\_RX\_POLLING AVF capability.

### 2.1.6 Basic Receive Offloads

### 2.1.6.1 Strip Ethernet CRC Bytes

The AVF driver checks the integrity of the Ethernet CRC and possibly strips it from packets that are posted to LAN queues. This capability is exposed in the capability exchange as VIRTCHNL\_VF\_OFFLOAD\_L2.

### 2.1.6.2 VLAN Extraction

Before a packet is stored in host memory, the VLAN tag might be stripped and optionally stored in the receive descriptor. The action done is defined by the PF. This capability is exposed in the capability exchange as VIRTCHNL\_VF\_OFFLOAD\_VLAN.

### 2.1.6.3 Receive L3 and L4 Integrity Check Offload

The AVF driver compliant hardware offloads the following L3 and L4 integrity checks: IPv4 header(s) checksum, UDP checksum, and SCTP CRC integrity. Hardware identifies the packet type and then checks the matched integrity scheme. The identified packet type is reported in the *PTYPE* field in the receive descriptor. Processing indication of the L3 and L4 headers is reported on the L3L4P flag in the receive descriptor. Potential IPv4 checksum error, L4 integrity error and outer IPv4/UDP checksum error are reported by the IPE, L4E and the EIPE error flags in the legacy receive descriptor respectively. In the advanced receive descriptor it is reported in the flexible error flags.

Some rules for integrity check offload are listed in the text that follows. If the following rules are not met, integrity offload is not provided and the L3L4P is not set.

- IPv4 header is assumed to be at least 20 bytes long (the length of the basic header).

- IPv4 headers might have any IP option headers that fit within the maximum header size (60 bytes).

- IPv6 support: The pseudo header for the L4 checksum takes into account the addresses in the IPv6 header ignoring the optional extension headers. Packets with Routing Header type 2 and Destination Options Header with Home Address option contain an alternative IP address in the extension header. Therefore, checksum calculation for such packets most probably results in erroneous value. The AVF driver indicates the existence of a Destination Options Header or a Routing Header in the IPV6EXADD bit of the RX descriptor. Software can then do one of the following:

- Ignore the checksum done by the device.

- Parse the extension header and identifying if it contains an IP address. Then ignore the checksum done by the device only in this case.

- Fragmented packets the AVF driver parses fragmented receive packets up to including the IP header (for IPv4) or up to including the fragmentation extension header (for IPv6):

- L4 checksum offload is not supported for IPv6 fragmented packets and the L3L4P flag in the receive descriptor is not set.

- Fragmented IPv4 packet is offloaded up to including the IP header.

- TCP header is assumed to be at least 20 bytes long (the length of the basic header).

- The TCP header might have any option headers that fit within the maximum header size (60 bytes).

VM-to-VM loopback traffic is processed by the hardware for L3/L4 integrity check as any other packet received from the network.

Table 2-5 lists all supported packet formats and the processed integrity. The table uses the following notations:

- IP is a generic term for IPv4 header or IPv6 header. The IPv4 header can have IP option headers and the IPv6 header can have IPv6 extension headers.

- L4 is a generic term for UDP, TCP or SCTP headers.

- IP checksum is meaningful only for IPv4.

- Checksum is a generic term for UDP and TCP checksum as well as SCTP CRC integrity.

- Zero UDP checksum: Zero UDP checksum for IPv4 packet is treated as no checksum and is reported by the hardware as no error and done. Zero UDP checksum for IPv6 packet is illegal and is reported by the hardware as L4 checksum error.

**Table 2-5.** Integrity Offload Check for Receive Packet Types

| Packet Type                                                               | Supported Integrity Offload                | Reported L3L4P                              |

|---------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------|

| IP -> [data / Unknown / fragmented]                                       | IP checksum offload                        | 1 (for IPv4/0 (for IPv6)                    |

| IP -> L4                                                                  | IP and L4 checksum offload                 | 1                                           |

| IP -> IP -> [data / Unknown / fragmented]                                 | 2 x IP checksum offload                    | 1 if at least one of the IP headers is IPv4 |

| IP -> IP -> L4                                                            | IP and L4 checksum offload                 | 1                                           |

| IP -> [tunnel header] -> IP -> data /<br>Unknown / fragmented             | Only IP checksum offload                   | 1 if at least one of the IP headers is IPv4 |

| IP -> [tunnel header] -> IP -> L4                                         | 1. IP and L4 checksum offload <sup>1</sup> | 1                                           |

| IP -> [tunnel header] -> data and<br>IP -> [tunnel header] -> MAC -> data | IP checksum offload                        | 1 (for IPv4/0 (for IPv6)                    |

| IP -> [tunnel header] -> MAC -> IP -> data                                | IP checksum (relevant only for IPv4)       | 1 if at least one of the IP headers is IPv4 |

| IP -> [tunnel header] -> MAC -> IP -> L4                                  | IP and L4 checksum offload <sup>1</sup>    | 1                                           |

<sup>1.</sup> The L4 checksum offload relates to the inner header:

## **2.1.6.4** RSS Support

The AVF driver supports by default an RSS table of 64 entries pointing to 4 queues. This capability is exposed in the capability exchange as VIRTCHNL VF OFFLOAD RSS PF.

The configurations of the table and the key are done through the PF mailbox using the VIRTCHNL OP CONFIG RSS KEY and VIRTCHNL OP CONFIG RSS LUT respectively.

The RSS hash value of the receive packet is exposed in the receive descriptor write back in the *Filter Status* field as described in Section 2.1.2.2.

<sup>-</sup> For UDP or TCP protocols, the hardware calculates the expected checksum including the pseudo IP header.

<sup>-</sup> For SCTP protocol, the hardware calculates the expected SCTP CRC.

<sup>2.</sup> Tunneling headers can be one of the following: GRE, Teredo, VXLAN UDP header.

# 2.2 Transmit Queues

# 2.2.1 Transmit Queue Ring

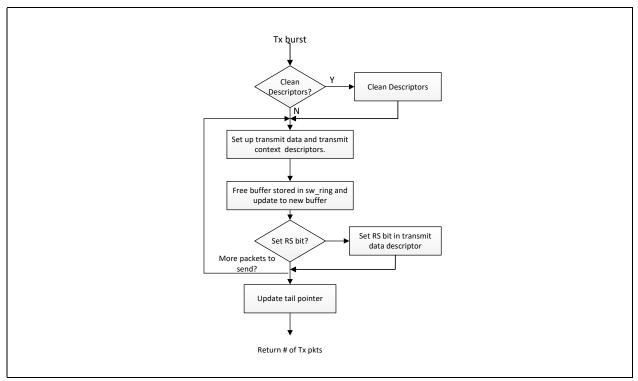

Software prepares structures for transmission in system memory indicated to hardware by a list of consecutive descriptors. These descriptors are organized in a contiguous memory handled as a cyclic queue which is also called a Transmit Descriptor Ring (TDR). Descriptors are initialized by software, and posted to hardware for processing via a write to a doorbell register. The AVF driver supports up to four transmit queues allocated to the VFs.

Transmit queue state and behavior is initialized by PF software, which programs a set of parameters collectively called the queue context. The main parameters are the queue pointers shown in Figure 2-3. The software interface to the queue for initialization, normal operation, and queue disable is described in Section 2.2.3.

Figure 2-3. Transmit Descriptor Ring Structure

When software posts a packet for transmission it can add some specific rules and commands per the transmitted packet. This is done by adding extra descriptors on top of the Data descriptors which point to the transmitted packet. The following sections describes the various descriptor types.

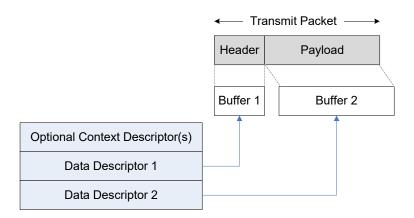

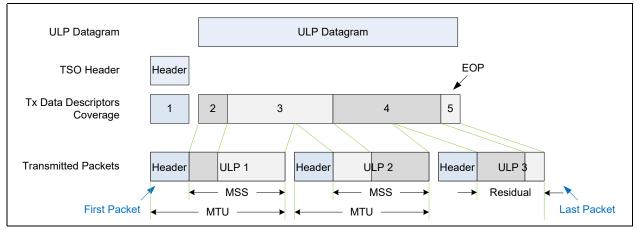

Transmit packets are stored in single or multiple non-contiguous buffers in host memory. The location of these buffers is provided by software to hardware for transmission using descriptors (16-byte structures described in Section 2.1.2.2). These descriptors include pointer and length pairs to the data buffers as well as control fields for the transmit data processing. In some cases additional control parameters that cannot fit within the data descriptors are needed to process the packet(s). In this case, an additional context descriptor (16-byte structures described in Section 2.2.2.3) is posted by software to hardware prior to posting the data descriptors. Figure 2-4 shows an example of a transmit packet in host memory composed of 2 buffers (header buffer and payload buffer), indicated by 2 matched data descriptors and an optional context descriptor.

A few rules related to the transmit packet in host memory are:

• The total size of a single packet in host memory must be at least 17 bytes and up to the Max Frame Size of the port as configured by the PF.

- Packets outside this range are considered malicious. The respective queue is stopped and an interrupt is issued to the PF.

- This rule applies for single packet send as well as any packet within a transmit segmentation (TSO).

- A single transmit packet may span up to 8 buffers (up to 8 data descriptors per packet including both the header and payload buffers).

- When a packet span on multiple buffers, all the descriptor of that packet must be filled similarly.

- The total number of data descriptors for the whole TSO (explained later on in this chapter) is considered unlimited (Limited only by TX queue length) as long as each segment within the TSO obeys the previous rule (up to 8 data descriptors per segment for both the TSO header and the segment payload buffers).

- If a packet or TSO spans on multiple transmit data descriptors, the fields in all the data descriptors must be valid.

- The TSO message header should not span on more than three buffers (Max 3 Descriptors).

Figure 2-4. Transmit Packet in System Memory (Example Using 2 Buffers)

# **2.2.2** Transmit Queue Descriptor

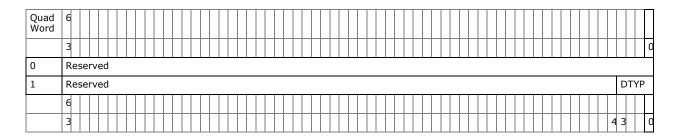

# 2.2.2.1 General Descriptors

Table 2-6. LAN Descriptor Types

| Туре                     | DTYP value | Description                                       | Reference |

|--------------------------|------------|---------------------------------------------------|-----------|

| Transmit Data Descriptor | 0x0        | Regular data descriptor used to send LAN packets. | Section   |

**Note:** For all descriptors: fields indicated as RSV (reserved) should be set to zero by software at programming time.

# **2.2.2.2 Transmit Data Descriptor**

| Quad<br>Word | 6 |    |    |     |    |    |     |      |    |    |    |   |   |   |   |     |    |     |    |    |    |   |   |   |  |   |   |     |    |               |               |               |   |   |   |   |   |   |   |    |    |  |  |   |   |   |   |   |    |    |   |

|--------------|---|----|----|-----|----|----|-----|------|----|----|----|---|---|---|---|-----|----|-----|----|----|----|---|---|---|--|---|---|-----|----|---------------|---------------|---------------|---|---|---|---|---|---|---|----|----|--|--|---|---|---|---|---|----|----|---|

|              | 3 |    |    | T   |    |    |     |      | T  | T  | T  |   | Γ |   |   |     |    | 1   |    | T  | T  | T | T | T |  |   |   |     | T  |               |               |               | П | 1 | T | T | Г | П |   | T  | T  |  |  | T | T | T | Τ |   |    | T  | ō |

| 0            | Т | χl | Pa | cke | et | Bu | ffe | er / | ٩d | dr | es | S |   |   |   |     |    |     |    |    |    |   |   |   |  |   |   |     |    |               |               |               |   |   |   |   |   |   |   |    |    |  |  |   |   |   |   |   |    |    | Ī |

| 1            | L | .2 | Га | g 1 |    |    |     |      |    |    |    |   |   |   | Т | x E | 3u | ffe | er | Si | ze | : |   |   |  |   | 0 | ffs | et |               |               |               |   |   |   |   |   |   |   | C١ | 1D |  |  |   |   |   |   | D | ΤY | ′P | Ī |

|              | 6 |    |    |     |    |    |     |      |    |    |    |   |   | 4 | 4 |     |    |     |    |    |    |   |   |   |  | 3 | 3 |     |    |               |               |               |   |   |   |   |   |   | 1 | 1  |    |  |  |   |   |   |   |   |    |    | 1 |

|              |   |    |    |     |    |    |     |      |    |    |    |   |   |   |   |     |    |     |    |    |    |   |   |   |  |   |   |     |    | $\overline{}$ | $\overline{}$ | $\overline{}$ |   |   |   |   |   |   |   |    |    |  |  |   |   |   |   |   |    |    | _ |

### **Descriptor Type - DTYP (Quad Word 1, bits 0:3)**

0x0 stands for a Transmit Data Descriptor

### Command Field - CMD (Quad Word 1, bits 4:15) as detailed in the following table.

| Bits | Name    | Functionality                                                                                                                                                                                                                                                                                                                              |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | EOP     | End Of Packet. The EOP flag is set in the last descriptor of a packet or TSO.                                                                                                                                                                                                                                                              |

| 1    | RS      | Report Status. When set, the hardware reports the DMA completion of the transmit descriptor and its data buffer. When it is reported by descriptor Write Back, the DTYP field is set to 0xF and the RS flag is set.  The RS flag can be set only on a last Transmit Data Descriptor of a packet or last Transmit Data Descriptor of a TSO. |

| 2    | RSV     | Reserved, must be set to 1b.                                                                                                                                                                                                                                                                                                               |

| 3    | IL2TAG1 | Insert a VLAN tag from the L2TAG1 field in this descriptor. The capability to add a tag is exposed through the VIRTCHNL_VF_OFFLOAD_VLAN capability.                                                                                                                                                                                        |

| 4    | DUMMY   | When the Dummy flag is set, the packet is not transmitted (internal and external). Note that when using the Dummy option, the packet does not have to have a correct checksum. Software should set all the fields in the data descriptor and context descriptors describing the packet structure as it does for nominal packets.           |

| 5:6  | IIPT    | The IP header type and its offload.  00b = Non-IP packet or packet type is not defined by software.  01b = IPv6 packet.  10b = IPv4 packet with no IP checksum offload.  11b = IPv4 packet with IP checksum offload.  For an IPv4 TSO message, this field must be set to 11b.                                                              |

| Bits  | Name     | Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 8:9   | L4T      | L4T is the L4 packet type:  00b = Unknown / fragmented packet.  01b = TCP.  10b = SCTP.  11b = UDP.  When the L4T is set to other values than 00b, the L4LEN must be defined as well. When set to UDP or TCP, the hardware inserts the L4 checksum and when set to SCTP the hardware inserts the L4 CRC Requesting SCTP CRC / TCP or UDP offload for a packet which was padded by software results in wrong SCTP CRC.  EOFT is the EOF Tag to be used:  00b = EOFn.  01b - EOFt.  10b = EOFni.  11b = EOFa. |

| 10:11 | RSV      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

### **Header Offset Parameters - OFFSET (Quad Word 1, bits 16:33)**

| Bits  | Name               | Functionality                                                                                                                                                                                                                                                                           |

|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

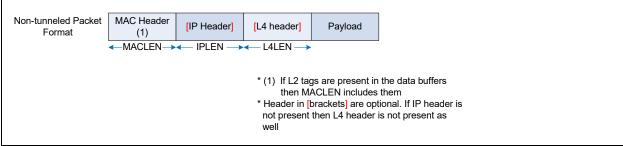

| 0:6   | MACLEN             | MAC Header Length defined in Words.  MACLEN defines the L2 header length up to including the Ethertype. If L2 tag(s) are provided in the data buffers, then they are included in MACLEN.                                                                                                |

| 7:13  | IPLEN /<br>FCoELEN | IP header length (including IP optional/extended headers) in the Tx buffer defined in Dwords                                                                                                                                                                                            |

| 14:17 | L4LEN /<br>FCLEN   | L4LEN is the L4 header length in the Tx buffer defined in Dwords. L4LEN should obey the following rules:  When the L4T field is set to 00b, L4LEN must be set to zero. Otherwise, it should be set to 8 / 12 for UDP / SCTP respectively and should be equal or larger than 20 for TCP. |

### L2 Tag 1 - L2TAG1 (Quad Word 1, 48:63)

A 16-bit VLAN Tag to be inserted into the packet if the IL2TAG1 flag is set. If IL2TAG1 is cleared, L2TAG1 should be set by software to zero. Valid only if VIRTCHNL\_VF\_OFFLOAD\_VLAN capability is exposed.

Transmit Buffer Description - BUFF (Quad Word 0, bits 0:63; Quad Word 1, bits 34:47)

### **Table 2-7.** Transmit Buffer

| Bits  | Name  | Functionality                                            |

|-------|-------|----------------------------------------------------------|

| 34:47 | BSIZE | Buffer size in byte units from 1 byte up to 16KB minus 1 |

| 0:63  | BADDR | Buffer address in byte granularity                       |

### **2.2.2.2.1** Transmit Descriptors Write Back Format

### **Descriptor Type - DTYP (Quad Word 1, bits 0:3)**

Hardware indicates a completed descriptor by setting the DTYP field to a value of 0xF.

Hardware reports this status in the following two cases:

- For descriptors with the RS bit set (Report Status).

- For the last descriptor of a command that was executed before an interrupt of the queue is initiated.

### Completion Flags RS (Quad Word 1, bit 5)

• RS bit is set if it was active by software.

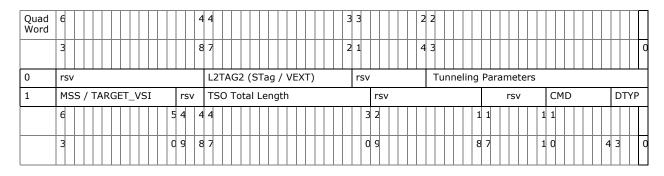

# **2.2.2.3 LAN Transmit Context Descriptors**

A context descriptor might contain some additional setting options for a single packet or TSO defined by the Data descriptor(s) that follows. Following the transmission of the packet or TSO, the context provided by this descriptor is expired.

**Descriptor Type - DTYP (Quad Word 1, bits 0:3)**

0x1 stands for a LAN Context Descriptor.

Command Field - CMD (Quad Word 1, bits 4:10)

| Bits | Name | Functionality                              |

|------|------|--------------------------------------------|

| 0    | TS0  | TSO is activated when the TSO flag is set. |

| 6:1  | RSV  | Reserved                                   |

### Segmentation Parameters / Switching Parameter (Quad Word 1, bits 30:47; bits 50:63)