# INTEL® Fully Buffered DIMM SPECIFICATION ADDENDUM

Rev. 0.9 March 21, 2006 Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation www.intel.com or call 1-800-548-4725

\*Other names and brands may be claimed as the property of others.

Copyright© 2005, Intel Corporation

3/21/2006 2 Intel Confidential

# **TABLE OF CONTENTS**

| 1  | Do         | OCUMENT ORGANIZATION                                                        | 4   |

|----|------------|-----------------------------------------------------------------------------|-----|

|    | 1.1        | Revision History                                                            | 4   |

|    | 1.2        | Related Documents                                                           | 4   |

|    | 1.3        | Objective                                                                   | 4   |

| 2  | A]         | MB Air Flow Resistance                                                      | 5   |

|    | 2.1        | Introduction                                                                | 5   |

|    | 2.2        | Airflow Supply and Measurement                                              |     |

|    | 2.3        | Test Fixture                                                                |     |

|    | 2.4        | Impedance Measurement                                                       | 8   |

| 3  | FF         | B-DIMM AND AMB LATENCY RANGE                                                |     |

|    | 3.1        | FB-DIMM Latency Range                                                       | 9   |

|    | 3.2        | AMB Latency Range                                                           | 11  |

|    | 3.3        | AMB CMD2DATANXT Utilization for Merge Data Training                         | 12  |

| 4  | A]         | MB Power Measurement and Power Specification                                | 13  |

| 5  | S3         | 3 CURRENT SPECIFICATION                                                     | 16  |

| 6  | D)         | IMM HEAT SPREADER MECHANICAL REQUIREMENTS                                   | 17  |

|    | 6.1        | Shock Testing of a Unpackaged Board with FB DIMMs                           | 17  |

|    | <b>6.2</b> | Vibration Testing of a Unpackaged Board with FB DIMMs                       | 18  |

|    | 6.3        | Shock Testing of a FB DIMM in its free state                                |     |

| 7  | D)         | IMM THERMAL RESISTANCE                                                      |     |

|    | 7.1        | DIMM Thermal Characterization                                               | 20  |

|    | 7.2        | SPD Definitions for Thermal Resistance                                      | 20  |

|    | 7.3        | Thermal Resistance Values for DIMM                                          | 21  |

|    | <b>7.4</b> | Default Thermal Resistance Values Implementation                            | 21  |

|    | 7.5        | Terminology                                                                 | 22  |

|    | <b>7.6</b> | Appendix A                                                                  | 23  |

| 8  | D          | DR2 DIMM Product Label                                                      | 24  |

| 9  | D          | DR2 DRAM TEMPERATURE REQUIREMENT FOR FB-DIMM                                | 27  |

| 10 | )          | DUAL DIFFERENTIAL SIGNALS STRIP-LINE SPACING REQUIREMENT FOR FB-DIMM DESIGN | 27  |

| 1  | l          | AMB SPEC AMBIGUITIES CLARIFICATION                                          | 29  |

| 12 | )          | FB-DIMM SPD PROGRAMMING CLARIFICATION AND RECOMMENDATION                    | 31  |

|    | _          | TE ENGLISHED TROOMERING CERTAIN TO CERTAIN THE THEORY IN STREET             | 0 1 |

# 1 Document Organization

# 1.1 Revision History

| <b>Revision Info</b> | Page of  | Description of Change                                                                                               |

|----------------------|----------|---------------------------------------------------------------------------------------------------------------------|

|                      | Revision |                                                                                                                     |

| 0.85                 |          | First revision of this document                                                                                     |

| 0.90                 | 9        | Update latency definitions to reflect that they are DIMM specifications.                                            |

|                      | 10       | Update "AMB Latency Range Table" with DIMM flight times that need to be deducted from the DIMM measurement numbers. |

|                      | 11       | Add CMD2DATANXT requirements                                                                                        |

|                      | 19       | Change from "Utilize service condition A" to "Utilize service condition B"                                          |

|                      | 21       | Remove original section 7.4, 7.5, and 7.6                                                                           |

|                      | 24       | Update 7.6 Appendix A "Thermal Resistance" Table values Update note 2 and 3 of the table                            |

|                      | 30       | Update Byte 17 and 18 SPD available values per JEDEC update                                                         |

|                      | 33       | Update Byte 99 suggested program value table                                                                        |

|                      | 34       | Add Section 13 "OVERTEMP Function of the AMB"                                                                       |

|                      |          |                                                                                                                     |

### 1.2 Related Documents

| Document                        | Revision | Description                                           |

|---------------------------------|----------|-------------------------------------------------------|

| FB-DIMM Architecture & Protocol |          | Architecture and protocol specification for FB-DIMM   |

| Specification                   |          | channel.                                              |

| FB-DIMM Link Signaling          |          | FB-DIMM Electrical Specification. PTP Link            |

| Specification                   |          | parameters: signaling, I/O, and AC and DC Parameters. |

| FB-DIMM AMB Specification       |          | AMB Characteristics: pinout, package type,            |

|                                 |          | mechanical outline, footprint, AC/DC specs,           |

|                                 |          | power/thermal requirements, buffer TPT, special       |

|                                 |          | feature requirements, and basics DFT.                 |

| FB-DIMM Design Specification    |          | FB-DIMM MIMM module parameters, multiple raw          |

|                                 |          | card designs, block diagrams, net topologies, routing |

|                                 |          | details, timing budget, pinout, mechanical outline,   |

|                                 |          | stack up and SPD requirements.                        |

| DDR2 JEDEC Component Spec       |          | JEDEC DDR2 SDRAM Data Sheet ####                      |

| FB-DIMM SPD Specification       |          | Serial Presence Detect (SPD) values for FB-DIMMs.     |

# 1.3 Objective

This Specification addendum includes additional FBD and AMB specification information beyond the JEDEC standard. The intent of this document is to clarify and detail specifications so as to create a more robust, cost effective, compatible, and interoperable solution for Fully Buffered DIMMs (FBD).

The spec addendum represents Intel desired one voice data that is required for Intel products, which will be driven in the industry for acceptance.

3/21/2006 4 Intel Confidential

### 2 AMB Air Flow Resistance

### 2.1 Introduction

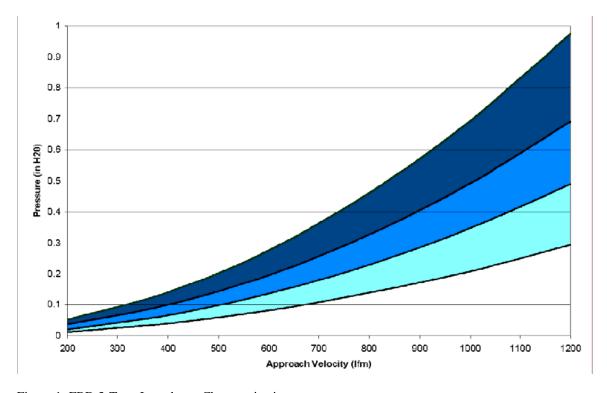

Due to the variety of AMB thermal solutions currently in development, the system designers need to account for varying airflow requirements while developing systems to support Fully Buffered DIMMs (FBD). Of concern is the varying airflow impedance of the thermal solutions, which drive significantly different airflow delivery requirements of the system. There are 3-Type categorizations of DIMM Impedance which can help system designers more discretely identify the airflow requirements of a particular DIMM. The impedance values will be based on measurements conducted with a memory fixed approach velocity of 600lfm as given below:

- Type 1: 0.08 0.13 in H2O

- Type 2: 0.13 0.20 in H2O

- Type 3: 0.20 0.28 in H2O

See Figure 1 for impedance curves of the 3 DIMM types.

Figure 1: FBD 3-Type Impedance Characterization

Implementation of this strategy requires standardization of the airflow measurement technique. This spec addendum describes a process for airflow impedance characterization of a DIMM array using an airflow bench for air delivery, flow measurement, and impedance measurement.

\* FBD Airflow Impedance compliance testing and characterization is not included in the Intel Validation Suite reference.

# 2.2 Airflow Supply and Measurement

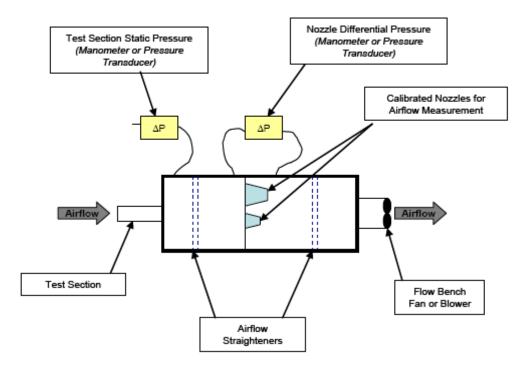

Airflow impedance through an array of Fully Buffered DIMMs in a test fixture can be made using a metered airflow chamber designed in accordance with AMCA 210-99/ASHRAE 51-19 (Figure 2). These airflow chambers, also known as flow-benches, measure pressure drop across a calibrated nozzle to determine volumetric airflow rates. Additionally, they are equipped to measure the impedance across a test section, in this case an array of DIMMs.

Figure 2: AMCA 210-99/ASHRAE 51-19 Airflow Measurement Chamber

Hot wire anemometers in a wind tunnel can also be used to measure velocity and calculate flow rate through a test fixture. If velocity measurements are used to calculate flow rates, airflow should be fully developed and laminar, however using velocity measurements to calculate flow rate is less accurate then using a flow bench.

# 2.3 Test Fixture

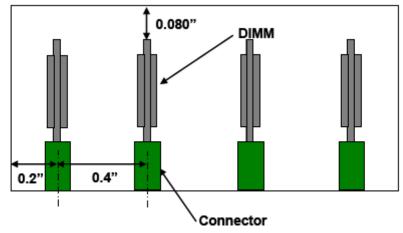

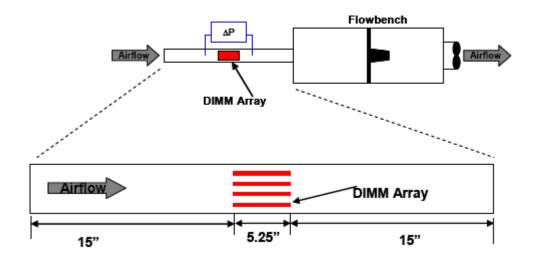

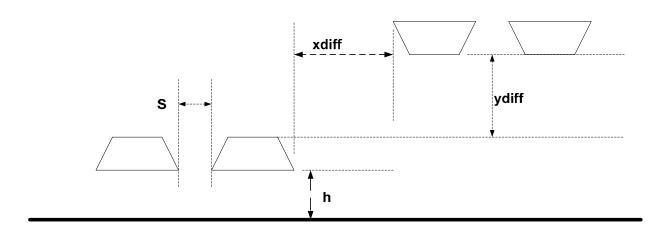

A 4-DIMM array was used for developing the impedance characterization in Figure 1. The DIMMs tested had a 0.400" center-to-center spacing (Figure 3) and this array was centered in a 35.25" long duct, which was fixtured to the end of the flow bench (Figure 4). The flow bench was used to generate the airflow for the characterization testing.

Where:

DIMM Pitch: 0.4"

Distance between Top of the DIMM to the ceiling of the chamber: 0.080"

Distance between the side of the chamber to the center line of the adjacent DIMM: 0.2"

Figure 3: DIMM Array Cross-Section for Flow Bench Impedance Characterization

Figure 4: DIMM Fixture Length

# 2.4 Impedance Measurement

A calibrated pressure transducer or a liquid manometer should be used to take pressure readings for both the nozzle differential pressure to determine airflow rate, as well as to measure the impedance across the DIMM test fixture.

The flow bench described above provides a pressure tap inside of the flow chamber which can be used to determine a pressure difference between the outside air and the air inside the chamber, downstream of the test section. The "Test Section Static Pressure" box in Figure 2 illustrates this.

This measurement captures the pressure drop across the entire test section, but it includes effects of both the test section, and the test duct shown in Figure 4. To isolate the impedance of the DIMM Array from the impedance of the air duct, one can observe that because the air duct impedance is dominated by entrance and exit losses, with minor impacts due to channel length, in this instance:

$$\Delta P_{DIMMs+Duct} = \Delta P_{DIMMS} + \Delta P_{Duct}$$

Simply stated, the impedance of the DIMMs can be found by subtracting the impedance of the empty duct from the impedance of the DIMMs in the duct. For example, consider the sample data in Table 1. The reported value of a DIMM Array's impedance at 600 feet/minute approach air velocity would be 0.11 inches of water, as shown in the right-most column.

Table 1: Sample Impedance Data

| Approach Velocity (LFM) | Impedance of DIMMs in Duct (inches H2O) | Impedance of Empty<br>Duct (inches H2O) | Impedance of DIMMs (inches H2O) |

|-------------------------|-----------------------------------------|-----------------------------------------|---------------------------------|

| 600                     | 0.17                                    | 0.06                                    | 0.11                            |

# 3 FB-DIMM and AMB Latency Range

Refer to JEDEC FB-DIMM AMB spec for tRESAMPLE and tRESYNC definition.

# 3.1 FB-DIMM Latency Range

DIMM latency bounds are critical in order to insure interoperability between different DIMMs and different AMBs. These bounds result in a worst case channel-to-channel skew for lock-stepped channels that does not exceed the host controller's ability to de-skew. DIMM skew is a function of both DIMM channel length and AMB latency, so both are specified.

AMB latency ranges are a function of DIMM latency ranges, when northbound and southbound channel lengths on the DIMMs are known. DIMM latency ranges are specified in the following table. Values for both northbound (NB) and southbound (SB) are listed since DIMM routing varies between NB and SB.

AMB latency ranges are represented as a function of the DIMM latency ranges, and therefore also have both a NB and SB value tabulated.

| Parameter         | Data | Min  | Max  | Units |

|-------------------|------|------|------|-------|

|                   | Rate |      |      |       |

| tC2D_DIMM         | 533  | 20.7 | 25.5 | nS    |

|                   | 667  | 17.5 | 21.5 | nS    |

| tRESAMPLE_DIMM_SB | 533  | 1.4  | 2.7  | nS    |

|                   | 667  | 1.4  | 2.4  | nS    |

| tRESAMPLE_DIMM_NB | 533  | 1.3  | 2.6  | nS    |

|                   | 667  | 1.3  | 2.3  | nS    |

| tRESYNC_DIMM_SB   | 533  | 2.8  | 4.4  | nS    |

|                   | 667  | 2.5  | 3.7  | nS    |

| tRESYNC_DIMM_NB   | 533  | 2.7  | 4.3  | nS    |

|                   | 667  | 2.4  | 3.6  | nS    |

Notes:

**tC2D\_DIMM** = Measured delay at FBDIMM gold finger between the center of the1st UI of command frame on the primary southbound lane 8<sup>1</sup> (connector pins 102 & 103) and the center of the 1st UI of return data on the primary northbound lane 0 (connector pins 22 & 23) – [CL (DRAM CAS latency) value] \* [frame clock period – AL (DRAM additional latency) value \* frame clock period].

**tRESAMPLE\_DIMM\_SB** = Measured delay at FBDIMM gold finger between the center of the 1st UI of a frame on the primary southbound lane 8 (connector pins 102 & 103) and the center of the 1st UI of the same frame on the secondary southbound lane 8 (connector pins 222 & 223).

3/21/2006 9 Intel Confidential

<sup>&</sup>lt;sup>1</sup> This definition assumes that there is no large skew between the arrival times of the SB lanes at the gold finger. If the skew is larger than 150ps (about one inch of micro strip trace), a lane other than SB lane 8 could be the latest arriving lane at the AMB balls, and this lane has to be used for the tC2D\_DIMM measurement instead of lane 8. In order to simplify the measurement, it is required to ensure that no other lane arrives later than 150ps after the SB 8 lane at the gold finger.

Intel Rev. 0.9

**tRESAMPLE\_DIMM\_NB** = Measured delay at FBDIMM gold finger between the center of the 1st UI of a frame on the secondary northbound lane 0 (connector pins 142 & 143) and the center of the 1st UI of the same frame on the primary northbound lane 0 (connector pins 22 & 23).

**tRESYNC\_DIMM\_SB** = Measured delay at FBDIMM gold finger between the center of the 1st UI of a frame on the primary southbound lane 8 (connector pins 102 & 103) and the center of the 1st UI of the same frame on the secondary southbound lane 8 (connector pins 222 & 223).

**tRESYNC\_DIMM\_NB** = Measured delay at FBDIMM gold finger between the center of the 1st UI of a frame on the secondary northbound lane 0 (connector pins 142 & 143) and the center of the 1st UI of the same frame on the primary northbound lane 0 (connector pins 22 & 23).

# 3.2 AMB Latency Range

| Parameter E         |     | Min                                | Max                                | Units |

|---------------------|-----|------------------------------------|------------------------------------|-------|

| tRESAMPLE_AMB_SB    | 533 | tRESAMPLE_DIMM_SB_533 (min) - 0.50 | tRESAMPLE_DIMM_SB_533 (max) - 0.50 | nS    |

| tkesavii le_avib_sb | 667 | tRESAMPLE_DIMM_SB_667 (min) - 0.50 | tRESAMPLE_DIMM_SB_667 (max) - 0.50 | ПЭ    |

| ADECAMBLE AMB ND    | 533 | tRESAMPLE_DIMM_NB_533 (min) - 0.44 | tRESAMPLE_DIMM_NB_533 (max) - 0.44 | nS    |

| tRESAMPLE_AMB_NB    | 667 | tRESAMPLE_DIMM_NB_667 (min) - 0.44 | tRESAMPLE_DIMM_NB_667 (max) - 0.44 | III   |

| tRESYNC AMB SB      | 533 | tRESYNC_DIMM_SB_533 (min) - 0.50   | tRESYNC_DIMM_SB_533 (max) - 0.50   | nS    |

| tkesinc_avib_sb     | 667 | tRESYNC_DIMM_SB_667 (min) - 0.50   | tRESYNC_DIMM_SB_667 (max) - 0.50   | ii.5  |

| tRESYNC_AMB_NB      | 533 | tRESYNC_DIMM_NB_533 (min) - 0.44   | tRESYNC_DIMM_NB_533 (max) - 0.44   | nS    |

| TRESTINC_AVID_ND    | 667 | tRESYNC_DIMM_NB_667 (min) - 0.44   | tRESYNC_DIMM_NB_667 (max) - 0.44   | 11.5  |

### Notes:

**tRESAMPLE\_AMB\_SB** = Measured delay at AMB balls between the center of the 1st UI of a frame on the primary southbound lane 8 (AMB balls U29 & U28) and the center of the 1st UI of the same frame on the secondary southbound lane 8 (AMB balls Y26 & W26).

**tRESAMPLE\_AMB\_NB** = Measured delay at AMB balls between the center of the 1st UI of a frame on the secondary northbound lane 0 (AMB balls V4 & V5) and the center of the 1st UI of the same frame on the primary northbound lane 0 (AMB balls U1 & U2).

**tRESYNC\_AMB\_SB** = Measured delay at AMB balls between the center of the 1st UI of a frame on the primary southbound lane 8 (AMB balls U29 & U28) and the center of the 1st UI of the same frame on the secondary southbound lane 8 (AMB balls Y26 & W26).

**tRESYNC\_AMB\_NB** = Measured delay at AMB balls between the center of the 1st UI of a frame on the secondary northbound lane 0 (AMB balls V4 & V5) and the center of the 1st UI of the same frame on the primary northbound lane 0 (AMB balls U1 & U2).

3/21/2006 11 Intel Confidential

# 3.3 AMB CMD2DATANXT Utilization for Merge Data Training

AMB designs support a limited range of CMD2DATANXT register settings during runtime. (Refer to the JEDEC AMB Component Specification).

In addition, the AMB CMD2DATANXT mechanism will be used temporarily by memory reference code during memory subsystem training to train each memory channel with adequate timing margin to prevent Merge Data errors when mixing different AMB's on a channel. Memory reference code will over ride the SPD CMD2DATANXT value only during Merge Data training, and not while accessing DRAM. Once training completes, the original CMD2DATANXT value will be restored before normal system operation initiates.

AMB designs need to support a range of CMD2DATANXT values for purposes of non-DRAM access, Merge Data training ONLY. The supported range needs to extend at least 16UI higher than the value recommended and specified in the SPD for normal operation.

AMB designs that do not support a particular DLYFRAC value due implementation granularity must functionally round up to the next supported value.

### **CMD2DATANXT Register Definition**

| Function:1<br>Offset:E8h |          |             |                                                                                                                                                                                       |  |  |  |  |  |

|--------------------------|----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit                      | Attr     | Description |                                                                                                                                                                                       |  |  |  |  |  |

| 7:4                      | RWS<br>T | 0h          | DLYFRMS: Number of frames  This specifies full frame delay part of the command to data delay.  0 - 9: Valid delays  10 - 15: Reserved                                                 |  |  |  |  |  |

| 3:0                      | RWS<br>T | 0h          | DLYFRAC: Fractional delay of command to data This specifies fractional frame delay part of the command to data delay. 0 - 11: Specifies the delay in 1UI increments 12 - 15: Reserved |  |  |  |  |  |

# 4 AMB Power Measurement and Power Specification

AMB Power is measured with DIMMs installed in an FBD platform. This provides a real world conditions for the measurement process. The document <u>AMB Current/Power Measurement Procedure: AMB-FBDIMM</u> provides the step by step procedure, as well as all of the hardware and software requirements.

Current and Power Specification for x8 DIMMs.

|               |                                                                               |              | 533        | MHz        | 667          | MHz        | 800        | MHz        |          |

|---------------|-------------------------------------------------------------------------------|--------------|------------|------------|--------------|------------|------------|------------|----------|

| Symbol        | Conditions                                                                    | Power        | Thermal    |            | Thermal      | Max        | Thermal    | Max        | Units    |

|               |                                                                               | Supply       |            | Current    | Design       | Current    | Design     | Current    |          |

| ldd_ldle_0    | Idle Current, single or last DIMM                                             | 1.5V<br>1.8V | 2.1        | 2.2        | 2.4          | 2.6<br>0.7 | TBD<br>TBD | TBD<br>TBD | A        |

|               | L0 state, idle (0 BW)                                                         | Power        | 0.6<br>3.5 | 0.7        | 0.6<br>4.0   | 0.7        | TBD        | עפו        | A<br>W   |

|               | Primary channel enabled,<br>Secondary Channel Disabled                        | 1 Owei       | 3.3        |            | 4.0          |            | 100        |            | VV       |

|               | CKE high.                                                                     |              |            |            |              |            |            |            |          |

|               | Command and address lines stable. DRAM clock active.                          |              |            |            |              |            |            |            |          |

| Idd_Idle_1    | Idle Current, first DIMM                                                      | 1.5V         | 2.7        | 3.0        | 3.1          | 3.4        | TBD        | TBD        | Α        |

|               | L0 state, idle (0 BW)                                                         | 1.8V         | 0.6        | 0.7        | 0.6          | 0.7        | TBD        | TBD        | Α        |

|               | Primary and Secondary channels enabled<br>CKE high. Command and address lines | Power        | 4.6        |            | 5.1          |            | TBD        |            | W        |

|               | stable.                                                                       |              |            |            |              |            |            |            |          |

| Idd TDP 0     | DRAM clock active.  Active Power, TDP BW, Single                              | 1.5V         | 2.4        | 2.6        | 2.8          | 3.0        | TBD        | TBD        | Α        |

| 144_121_0     | or Last DIMM                                                                  | 1.8V         | 1.1        | 1.3        | 1.2          | 1.3        | TBD        | TBD        | Α        |

|               | LO state                                                                      | Power        | 5.2        |            | 5.8          |            | TBD        |            | W        |

|               | TDP Channel BW = 2.0GB/s@533; 2.4GB/<br>s@667; 3.0GB/s@800                    |              |            |            |              |            |            |            |          |

|               | DIMM BW = 2.0GB/s@533; 2.4GB/s@667; 3.0GB/s@800                               |              |            |            |              |            |            |            |          |

|               | 67% read, 33% write.                                                          |              |            |            |              |            |            |            |          |

|               | Primary channel Enabled<br>Secondary channel Disabled                         |              |            |            |              |            |            |            |          |

|               | CKE high. Command and Address                                                 |              |            |            |              |            |            |            |          |

| Idd_TDP_1     | Active Power, TDP BW, First                                                   | 1.5V         | 3.0        | 3.3        | 3.5          | 3.8        | TBD        | TBD        | Α        |

|               | DIMM<br>L0 state                                                              | 1.8V         | 0.9        | 1.0        | 0.9          | 1.0        | TBD        | TBD        | Α        |

|               | TDP Channel BW = 2.0GB/s@533; 2.4GB/                                          | Power        | 5.8        |            | 6.4          |            | TBD        |            | W        |

|               | s@667; 3.0GB/s@800<br>DIMM BW =2/3 Channel BW = 1.3GB/                        |              |            |            |              |            |            |            |          |

|               | s@533; 1.6GB/s@667; 2GB/s@800                                                 |              |            |            |              |            |            |            |          |

|               | 67% read, 33% write.<br>Primary channel Enabled                               |              |            |            |              |            |            |            |          |

|               | Secondary channel Enabled                                                     |              |            |            |              |            |            |            |          |

| Idd Astivo 1  | CKE high. Command and Ad                                                      | 1.5\/        | 2.4        | 2.4        | 2.6          | 2.0        | TBD        | TBD        | _        |

| Idd_Active_1  | Active Power L0 state.                                                        | 1.5V<br>1.8V | 3.1<br>1.2 | 3.4<br>1.3 | 3.6<br>1.2   | 3.9<br>1.3 | TBD        | TBD        | A        |

|               | 50% DRAM BW, 67% read, 33% write.<br>Primary and Secondary channels enabled.  | Power        | 6.4        | 1.5        | 7.1          | 1.5        | TBD        | 100        | W        |

|               | DRAM clock active, CKE high.                                                  |              | 0          |            | '''          |            |            |            |          |

| Idd_Active_2  |                                                                               | 1.5V         | 2.9        | 3.2        | 3.3          | 3.7        | TBD        | TBD        | Α        |

|               | L0 state.<br>50% DRAM BW to downstream DIMM, 67%                              | 1.8V         | 0.6        | 0.7        | 0.6          | 0.7        | TBD        | TBD        | Α        |

|               | read, 33% write.                                                              | Power        | 5.0        |            | 5.6          |            | TBD        |            | W        |

|               | Primary and Secondary channels enabled<br>CKE high. Command and address lines |              |            |            |              |            |            |            |          |

|               | stable.                                                                       |              |            |            |              |            |            |            |          |

| Idd_Training  | DRAM clock active.  Training                                                  | 1.5V         |            | 3.5        |              | 4.0        | TBD        | TBD        | Α        |

| laa_rraiiiiig | Primary and Secondary channels enabled.                                       | 1.8V         |            | 0.7        |              | 0.7        | TBD        | TBD        | A        |

|               | 100% toggle on all channel lanes<br>DRAMs idle. 0 BW.                         |              |            |            |              |            |            |            |          |

|               | CKE high, Command and address lines                                           |              |            |            |              |            |            |            |          |

|               | stable. DRAM clock active.                                                    |              |            |            |              |            |            |            |          |

| Idd_IBIST     | IBIST                                                                         | 1.5V         |            | 3.8        |              | 4.5        | TBD        | TBD        | Α        |

|               | Over all IBIST modes<br>DRAM Idle (0 BW)                                      | 1.8V         |            | 0.7        |              | 0.7        | TBD        | TBD        | Α        |

|               | Primary channel Enabled                                                       |              |            |            |              |            |            |            |          |

|               | Secondary channel Enabled<br>CKE high. Command and Address lines              |              |            |            |              |            |            |            |          |

|               | stable                                                                        |              |            |            |              |            |            |            |          |

| Idd_MEMBI     | DRAM clock active  MemBIST                                                    | 1.5V         | 1          | 3.3        |              | 3.8        | TBD        | TBD        | Α        |

| ST            | Over all MemBIST modes                                                        | 1.8V         | 1          | 2.1        | <del> </del> | 2.1        | TBD        | TBD        | A        |

|               | >50% DRAM BW (as dictated by the AMB)<br>Primary channel Enabled              |              |            |            |              |            | .55        | .55        | <b>[</b> |

|               | Secondary channel Enabled                                                     |              |            |            |              |            |            |            |          |

|               | CKE high. Command and Address lines stable                                    |              |            |            |              |            |            |            |          |

|               | DRAM clock active                                                             |              |            |            |              |            |            |            |          |

| ldd_EI        | Electrical Idle                                                               | 1.5V         |            | 2.0        |              | 2.5        | TBD        | TBD        | Α        |

|               | DRAM Idle (0 BW)<br>Primary channel Disabled                                  | 1.8V         |            | 0.2        |              | 0.2        | TBD        | TBD        | Α        |

|               | Secondary channel Disabled                                                    |              |            |            |              |            |            |            |          |

|               | CKE low. Command and Address lines<br>Floated                                 |              |            |            |              |            |            |            |          |

|               | DRAM clock active, ODT and CKE driven                                         |              |            |            |              |            |            |            |          |

|               | low                                                                           | l .          | I          | i .        | I            | l          | I          | l          | <u> </u> |

Current and Power Specification for x4 DIMMs.

|              |                                                                               |               | 533        | MHz        | 667        | MHz        | 800        | MHz        |        |

|--------------|-------------------------------------------------------------------------------|---------------|------------|------------|------------|------------|------------|------------|--------|

| Symbol       | Conditions                                                                    | Power         | Thermal    |            |            | Max        | Thermal    | Max        | Units  |

|              |                                                                               | Supply        |            | Current    | Design     | Current    | Design     | Current    |        |

| ldd_ldle_0   | Idle Current, single or last                                                  | 1.5V          | 2.1        | 2.2        | 2.4        | 2.6        | TBD        | TBD        | A      |

|              | DIMM<br>L0 state, idle (0 BW)                                                 | 1.8V<br>Power | 0.9<br>3.9 | 0.9        | 0.9<br>4.4 | 0.9        | TBD<br>TBD | TBD        | A<br>W |

|              | Primary channel enabled,                                                      | Fower         | 3.9        |            | 4.4        |            | טפו        |            | VV     |

|              | Secondary Channel Disabled CKE high.                                          |               |            |            |            |            |            |            |        |

|              | Command and address lines stable.                                             |               |            |            |            |            |            |            |        |

| Idd_Idle_1   | DRAM clock active.  Idle Current, first DIMM                                  | 1.5V          | 2.7        | 3.0        | 3.1        | 3.4        | TBD        | TBD        | Α      |

|              | L0 state, idle (0 BW)                                                         | 1.8V          | 0.9        | 0.9        | 0.9        | 0.9        | TBD        | TBD        | Α      |

|              | Primary and Secondary channels enabled<br>CKE high. Command and address lines | Power         | 4.9        |            | 5.5        |            | TBD        |            | W      |

|              | stable.                                                                       |               |            |            |            |            |            |            |        |

| Idd_TDP_0    | DRAM clock active.  Active Power, TDP BW, Single                              | 1.5V          | 2.4        | 2.6        | 2.8        | 3.0        | TBD        | TBD        | Α      |

| 144_121_0    | or Last DIMM                                                                  | 1.8V          | 1.5        | 1.6        | 1.5        | 1.6        | TBD        | TBD        | Α      |

|              | L0 state                                                                      | Power         | 5.9        |            | 6.5        |            | TBD        |            | W      |

|              | TDP Channel BW = 2.0GB/s@533; 2.4GB/<br>s@667; 3.0GB/s@800                    |               |            |            |            |            |            |            |        |

|              | DIMM BW = 2.0GB/s@533; 2.4GB/s@667; 3.0GB/s@800                               |               |            |            |            |            |            |            |        |

|              | 67% read, 33% write.                                                          |               |            |            |            |            |            |            |        |

|              | Primary channel Enabled<br>Secondary channel Disabled                         |               |            |            |            |            |            |            |        |

|              | CKE high. Command and Address                                                 |               |            |            |            |            |            |            |        |

| Idd_TDP_1    | Active Power, TDP BW, First                                                   | 1.5V          | 3.0        | 3.3        | 3.5        | 3.8        | TBD        | TBD        | Α      |

|              | DIMM<br>L0 state                                                              | 1.8V          | 1.3        | 1.4        | 1.3        | 1.4        | TBD        | TBD        | A      |

|              | TDP Channel BW = 2.0GB/s@533; 2.4GB/                                          | Power         | 6.3        |            | 6.9        |            | TBD        |            | W      |

|              | s@667; 3.0GB/s@800<br>DIMM BW =2/3 Channel BW = 1.3GB/                        |               |            |            |            |            |            |            |        |

|              | s@533; 1.6GB/s@667; 2GB/s@800                                                 |               |            |            |            |            |            |            |        |

|              | 67% read, 33% write.<br>Primary channel Enabled                               |               |            |            |            |            |            |            |        |

|              | Secondary channel Enabled                                                     |               |            |            |            |            |            |            |        |

| Idd_Active_1 | CKE high. Command and Ad Active Power                                         | 1.5V          | 3.1        | 3.4        | 3.6        | 3.9        | TBD        | TBD        | Α      |

| Iuu_Active_1 | L0 state.                                                                     | 1.8V          | 1.6        | 1.7        | 1.6        | 1.7        | TBD        | TBD        | A      |

|              | 50% DRAM BW, 67% read, 33% write.<br>Primary and Secondary channels enabled.  | Power         | 6.9        | 1.7        | 7.6        | 1.7        | TBD        | 100        | W      |

|              | DRAM clock active, CKE high.                                                  |               |            |            |            |            |            |            |        |

| Idd_Active_2 | Active Power, data pass through                                               | 1.5V          | 2.9        | 3.2        | 3.3        | 3.7        | TBD        | TBD        | Α      |

|              | L0 state.<br>50% DRAM BW to downstream DIMM, 67%                              | 1.8V          | 0.9        | 0.9        | 0.9        | 0.9        | TBD        | TBD        | A      |

|              | read, 33% write. Primary and Secondary channels enabled                       | Power         | 5.5        |            | 6.1        |            | TBD        |            | W      |

|              | CKE high. Command and address lines                                           |               |            |            |            |            |            |            |        |

|              | stable. DRAM clock active.                                                    |               |            |            |            |            |            |            |        |

| Idd_Training | Training                                                                      | 1.5V          |            | 3.5        |            | 4.0        | TBD        | TBD        | Α      |

| 3            | Primary and Secondary channels enabled.                                       | 1.8V          |            | 0.9        |            | 0.9        | TBD        | TBD        | Α      |

|              | 100% toggle on all channel lanes<br>DRAMs idle. 0 BW.                         |               |            |            |            |            |            |            |        |

|              | CKE high, Command and address lines stable.                                   |               |            |            |            |            |            |            |        |

|              | DRAM clock active.                                                            |               |            |            |            |            |            |            |        |

| Idd_IBIST    | IBIST                                                                         | 1.5V          |            | 3.8        |            | 4.5        | TBD        | TBD        | Α      |

|              | Over all IBIST modes<br>DRAM Idle (0 BW)                                      | 1.8V          |            | 0.9        |            | 0.9        | TBD        | TBD        | Α      |

|              | Primary channel Enabled                                                       |               |            |            |            |            |            |            |        |

|              | Secondary channel Enabled<br>CKE high. Command and Address lines              |               |            |            |            |            |            |            |        |

|              | stable DRAM clock active                                                      |               |            |            |            |            |            |            |        |

| Idd_MEMBI    | MemBIST                                                                       | 1.5V          |            | 3.3        |            | 3.8        | TBD        | TBD        | Α      |

| ST           | Over all MemBIST modes                                                        | 1.8V          |            | 2.4        |            | 2.4        | TBD        | TBD        | Α      |

|              | >50% DRAM BW (as dictated by the AMB)<br>Primary channel Enabled              |               |            |            |            |            |            |            |        |

|              | Secondary channel Enabled<br>CKE high. Command and Address lines              |               |            |            |            |            |            |            |        |

|              | stable                                                                        |               |            |            |            |            |            |            |        |

| Idd El       | DRAM clock active                                                             | 1 5\/         | 1          | 2.0        |            | 2.5        | TBD        | TDD        |        |

| ldd_EI       | Electrical Idle<br>DRAM Idle (0 BW)                                           | 1.5V<br>1.8V  | 1          | 2.0<br>0.2 |            | 2.5<br>0.2 | TBD        | TBD<br>TBD | A      |

|              | Primary channel Disabled                                                      | 1.00          |            | 0.2        |            | 0.2        | 100        | 100        | ^      |

|              | Secondary channel Disabled<br>CKE low. Command and Address lines              |               |            |            |            |            |            |            |        |

|              |                                                                               | 1             | 1          | 1          | I          |            | I          | 1          |        |

|              | Floated DRAM clock active, ODT and CKE driven                                 |               |            |            |            |            |            |            |        |

# 5 S3 current Specification

S3 is an ACPI mode in which the DIMMs are put into a very lower power state, with the DRAMs in self refresh mode. This AMB S3 current specification is required for the sizing of the power supply used for the S3 mode.

In this mode is defined as:

DRAMs in self refresh.

AMB maintaining the DRAMs in self refresh by driving the CKE signals low.

REFCLK not toggling.

VDD = VDDmax (1.9V).

VCC = 0V

VTT = 0V

|        |                                                                                                                                                                   |               | 533     | MHz            | 667     | MHz            | 800     | MHz            |       |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------|----------------|---------|----------------|---------|----------------|-------|

| Symbol | Conditions                                                                                                                                                        | Power Supply  | Nominal | Max<br>Current | Nominal | Max<br>Current | Nominal | Max<br>Current | Units |

| Idd_S3 | S3 current  VDD = 1.9V  VCC = 0V  VTT = 0V  Across process variations  Across the operating TCASE temperature range.  DIMM types: Raw Card A, B, C, D, E, H, & J. | VDD<br>(1.8V) |         | 75             |         | 75             |         | 75             | mA    |

Note that the total DIMM current will include the AMB IDD\_S3 value as well as the self refresh current of all of the DRAMs on the DIMM.

# 6 DIMM Heat Spreader Mechanical Requirements

The objective of defining the mechanical requirements is to ensure that the FB DIMM Heat Spreader are sufficiently robust to withstand shocks when shipped on a board in a system, withstand vibration when mounted in a system which is being shipped and to withstand shock of dropping the DIMM's in their free state onto a floor during handling. The first two cases are performed on a unpackaged board whereas the third case is performed on a FB DIMM in its free state (not attached to a board). Board unpackaged testing does not pre-qualify a board for shipping as a un-mounted unit inside a shipping container.

# 6.1 Shock Testing of a Unpackaged Board with FB DIMMs

The test will be performed on at least 2 FB DIMMs in one Customer Reference Board (CRB) or an equivalent board product. The Board will be configured as in a complete system with all the other memory slots populated, processors installed and where possible, any required support cards will also be installed. The board must be mounted in a rigid fixture that duplicates the support points in the actual application of the board.

# **Test Objective**

Trapezoidal shock  $50 \text{ g} \pm 10\%$

Velocity change 170 inches/sec,  $\pm$  10%

Duration Not Specified

Three drops in each of the six directions are applied to the board sample.

### **Expected Failure Mechanisms**

- 1. Displaced or dislodged FB DIMM from the DIMM connector.

- 2. Displaced or dislodged Heatspreader/Clip from the FB DIMM Raw Cards

### Pass Criteria

- 1. No visible damage

- 2. No displacement of FB DIMM from the connector

- 3. No displacement of heat spreader or clips from the FB DIMM Raw Cards

### **Basis for Profile**

- 1. Specification limits are defined by Intel Corporation

- 2. MIL-STD-810E, Method 516, Transportation and Application Environments was the source of the test profile used here.

- 3. The board shock is more stressful that the system shock to guardband for the amplification that can be generated by a chassis. The board shock defined in this test is similar to shocks measured during system package testing on boards inside a packaged system.

- 4. Mounting a board to a rigid test fixture as defined in this test does not simulate stresses inside a board shipping container

- 5. The recommended filter frequency for response waveform collection is only a suggestion, using a common waveform filter frequency on all tests allows easier comparison of data taken at package, system or board level tests.

- 6. The rigid fixture used to mount the board must not amplify the stress being applied by to the shock table to the board. The fixture usually consists of a 1-inch aluminum plate with standoffs mounted in the proper position to duplicate the support of the chassis.

### Intel Rev. 0.9

- 7. Care should be taken to use only those support points that will actually be used in mounted the board to an actual chassis.

- 8. The testing should be conducted on a programmable shock machine.

- a. Table drop height and programmer pressure is adjusted to produce the desired delta velocity of  $\sim$ 170 inches/sec and  $\sim$ 50 g

- b. Table response used to set the desired input shock is to be filtered using a frequency 20 times the fundamental frequency of the input waveform

Example:  $f = (1/(t \times 2) \times 20)$

- 9. The board is then mounted to the table and dropped. Recommended filter frequency for any response waveform data collection is 225 Hz

- 10. Three drops in each of the six directions are applied to the board sample.

# 6.2 Vibration Testing of a Unpackaged Board with FB DIMMs

The test will be performed on at least 2 FB DIMMs in one Customer Reference Board (CRB) or an equivalent board product. The Board will be configured as in a complete system with all the other memory slots populated, processors installed and where possible, any required support cards will also be installed. The board must be mounted in a rigid fixture that duplicates the support points in the actual application of the board.

# **Test Objective**

Random Profile: 5 Hz @  $0.01 \text{ g}^2/\text{Hz}$  t 20 Hz @  $0.02 \text{ g}^2/\text{Hz}$  (slope up)

20Hz to 500Hz @ 0.02 g<sup>2</sup>/Hz (flat) Input acceleration is 3.13 g RMS 10 minutes per axis for all 3 axes Random control limit tolerance is ± 3 dB

### **Expected Failure Mechanisms**

- 1. Displaced or dislodged FB DIMM from the DIMM connector.

- 2. Displaced or dislodged Heatspreader/Clip from the FB DIMM Raw Cards

- 3. Cracking or breaking of FB DIMM Raw Cards

### Pass Criteria

- 1. No visible damage

- 2. No displacement of FB DIMM from the connector

- 3. No displacement of heat spreader or clips from the FB DIMM Raw Cards

### **Basis for Profile**

- 1. Specification limits are defined by Intel Corporation

- 2. MIL-STD-810E, Method 516, Transportation and Application Environments was the source of the test profile used here.

- 3. The board should be mounted in a rigid fixture that duplicates the support points in the actual application of the board.

- 4. The fixture must not amplify the stress being applied by the table to the board. The fixture usually consists of a 1-inch aluminum plate with standoffs mounted in the proper position to duplicate the support of the chassis.

- Care should be taken to use only those support points that will actually be used in the final product.

- 6. Vibrate per profile in all 3 axes for 10 minutes per axis.

- 7. The FB DIMM module should be inspected for damage after the tests.

# 6.3 Shock Testing of a FB DIMM in its free state

This test will determine the robustness of the modules under mechanical shock in its free state to simulate dropping them for a height. A minimum sample size of 5 modules shall be used.

### **Test Method:**

Reference JESD22-B110 "Subassembly Mechanical Shock". Perform visual inspection and test each module for functionality prior to testing. Utilize service condition B (1500G @ 0.5 ms shock pulse height) or any of the other service conditions listed in the Table 1 in JESD22-B110. Each module shall experience 5 shocks on each direction on each of the three axis of the module.

### **Expected Failure Mechanisms**

1. Visual damage to the modules

### Pass Criteria

- 1. No visible damage

- 2. Modules are functional

### 7 DIMM Thermal Resistance

### 7.1 DIMM Thermal Characterization

System thermal management must match the thermal characteristics of the DIMM with the system cooling capability. The required DIMM thermal characteristics for lower airflow system conditions are the thermal resistances of the devices on the DIMM. These thermal resistance values are included in the JEDEC SPD standard as bytes 94-97. Intel supports the JEDEC specification and definition of these bytes. Before a standard measurement process can be put in place, Intel also supports the specification of 'category' bits, bits [5:0] of SPD byte 99. These 'category' bits are simple physical descriptions of the DIMM such as DRAM and heat spreader types. Intel will use these simple physical descriptions to establish buffer and DRAM thermal resistance values that will be used by systems. Intel will test for compliance to these thermal resistance values, which are listed in Appendix A. This document will outline the following:

- 1. SPD definitions for Thermal Characterization

- 2. Thermal Resistance Values for DIMMs

- 3. Thermal Resistance test Methodology

### 7.2 SPD Definitions for Thermal Resistance

The following are SPD DIMM thermal characterization byte definitions.

Bytes 94-97 are thermal resistance of the AMB and DRAM devices on the FB DIMM. The byte definitions are a JEDEC standard.

| SPD BYTE | BYTE NAME                  | BYTE DEFINTION                  | COMMENT |

|----------|----------------------------|---------------------------------|---------|

| LOCATION |                            |                                 |         |

| Byte 94  | $\Psi_{ m AMB}$            | Thermal Resistance of AMB       |         |

|          |                            | Junction to Ambient             |         |

| Byte 95  | $\Psi_{ m AMB-DRAM}$       | Thermal Resistance of AMB       |         |

|          |                            | Junction to DRAM Case           |         |

| Byte 96  | $\Psi_{DRAM}$              | Thermal Resistance of DRAM      |         |

|          |                            | Case to Ambient                 |         |

| Byte 97  | $\Psi_{ m DRAM	ext{-}AMB}$ | Thermal Resistance of DRAM case |         |

|          |                            | to AMB junction                 |         |

The following DIMM thermal characterization bytes are simple physical descriptions of the DIMMs. These are referred to as 'category' bits. These bits are used to map to thermal resistance values (refer to Section 7.6) measured and tested by Intel in the absence of valid thermal resistance values specified in the SPD.

Byte 99, bits [5:3] are category bits that define the packaging types of the DRAM devices used on the DIMM. The package types used have different thermal resistances.

| SPD BYTE   | VAL | DRAM    | DEFINTION                         | COMMENT                  |

|------------|-----|---------|-----------------------------------|--------------------------|

| LOCATION/B | UE  | TYPE    |                                   |                          |

| ITS        |     |         |                                   |                          |

| Byte 99    | 000 | Unknown | DRAM package type does not match  |                          |

| Bits [5:3] |     |         | the pre-defined type.             |                          |

|            | 001 | Planar  | DRAM package type is a single die | Examples are FB DIMM Raw |

|            |     |         | per package. Does not use package | Cards E and H.           |

|            |     |         | stacking or multi-die package     |                          |

|            |     |         | technology.                       |                          |

| 010  | Dual Die | DRAM package type is two die in a  |                          |

|------|----------|------------------------------------|--------------------------|

|      |          | single DRAM package. Does not use  |                          |

|      |          | package stacking technology.       |                          |

| 011  | Stacked  | DRAM package type is two separate, | Example includes FB DIMM |

|      |          | packaged DRAM devices stacked on   | Raw Card D.              |

|      |          | top of each other.                 |                          |

| 100- | Reserved | Reserved for future definitions.   |                          |

| 111  |          |                                    |                          |

Byte 99, bits [2:0] are category bits that define heat spreader configuration of the DIMM. The heat spreader used impact the thermal resistances and thermal performance of the DIMM.

| SPD BYTE   | VAL  | HS TYPE  | DEFINTION                            | COMMENT                       |

|------------|------|----------|--------------------------------------|-------------------------------|

| LOCATION/B | UE   |          |                                      |                               |

| ITS        |      |          |                                      |                               |

| Byte 99    | 000  | Unknown  | DIMM heat spreader type does not     |                               |

| Bits [2:0] |      |          | match the pre-defined type.          |                               |

|            | 001  | AMB      | Heat spreader for AMB only. Contacts |                               |

|            |      | Only     | AMB only and covers AMB only.        |                               |

|            |      |          | Does not extend over DRAM devices.   |                               |

|            | 010  | Full     | Heat spreader extends the entire     | Heat spreader is assumed to   |

|            |      | DIMM     | length of the DIMM and covers the    | contact DRAM devices for best |

|            |      | Heat     | AMB and the DRAMs. Heat spreader     | thermal performance.          |

|            |      | Spreader | exists for both sides of the DIMM.   |                               |

|            | 011- | Reserved | Reserved for future definitions.     |                               |

|            | 111  |          |                                      |                               |

### 7.3 Thermal Resistance Values for DIMM

Intel will use the Resistance Values as defined in Section 7.6 for the DIMM categories defined above. DIMMs will be tested for thermal performance to meet or exceed the values in the table.

### 7.4 Default Thermal Resistance Values Implementation

Current implementations of the Thermal Resistance Values include default values for two primary DIMM configurations: AMB-only heat spreader and full-DIMM heat spreader (see Section 7.6 for the default values).

An AMB-only heat spreader consists of a highly conductive heat spreader (nominally 25mm square thin copper sheet) mechanically attached to the DIMM with sufficient hold down force for effective thermal conduction across the interface. The larger area will provide a greater surface area for AMB heat removal by convection to the air, but at the expense of additional interface and spreading resistance. An optimal balance needs to be achieved. The heat spreader must be attached with a TIM in between the heat spreader and AMB. The TIM must meet or exceed the performance of Honeywell PCM45.

A full-DIMM heat spreader consists of thin sheets of highly conductive material on both sides of the DIMM. The heat spreader is typically aluminum or copper. These heat spreaders must have a mechanical attach method that allows good contact with ALL DRAM and the AMB. There must also be a TIM between EVERY component and the heat spreader; otherwise the heat spreader will actually reduce thermal performance by blocking airflow to the DRAM without the TIM, essentially acting as an insulator.

When the system sees values of 0 (zero) in the 4 Thermal Resistance Bytes (i.e. Byte 97, 96, 95, and 94), the system will read the Category Byte (i.e. Byte 99, Bit[5:0]), and use the default thermal resistance

Intel Rev. 0.9

values as defined in Appendix A. The implementation of these category Bytes allows the use of FBDs that have not been fully characterized in an airflow/power/temperature test and do not have DIMM specific Thermal Resistance Bytes determined.

Properly implemented heat spreader solutions should not have thermal problems through the use of these default values. DIMMs can be inspected for heat spreader type, connection method, and thermal interface material (TIM) presence. Proper use of these components can also be validated by running the DIMM in the thermal test set-up and verifying the thermal performance is within the default thermal envelope as defined by the default thermal values in Appendix A. Improper installation of thermal hardware or bad thermal design (e.g. no TIM between heat spreader and DRAMs) will cause the part to be rejected as it will not meet the default thermal performance.

# 7.5 Terminology

Case Temperature – The temperature at the external surface of the silicon component

AMB – Advanced Memory Buffer

DRAM - Dynamic Random Access Memory

DIMM – Dual in-line memory module

MRC - Memory Reference Code

TIM - Thermal Interface Material

Junction Temperature – The peak temperature internal to the silicon component

$\Psi_x$  – Thermal resistance (in °C/W) from the component X to the ambient cooling airstream. For the AMB

$\Psi_{xy}$  – Thermal resistance cross terms (in °C/W) with power from the component X through component Y

# 7.6 Appendix A

|                                                                                                                  |                                                                                                                                                                                                                                                                               |                          |                       | Intel Spec Addendum Thermal Resistances |                             |          |          |          |            |          |                          |          |            |                               |          |          |            |          |          |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|-----------------------------------------|-----------------------------|----------|----------|----------|------------|----------|--------------------------|----------|------------|-------------------------------|----------|----------|------------|----------|----------|

| Raw<br>Card                                                                                                      | DRAM<br>Type                                                                                                                                                                                                                                                                  | Heat<br>Spreader<br>Type | Byte 99<br>Bits (5:0) | Max                                     | Max Ramb (degC/W, at X m/s) |          |          |          |            |          | Rdram (degC/W, at X m/s) |          |            | Max Rda (degC/W, at X<br>m/s) |          |          |            |          |          |

|                                                                                                                  |                                                                                                                                                                                                                                                                               |                          |                       | 1<br>m/s                                | 1.5<br>m/s                  | 3<br>m/s | 5<br>m/s | 1<br>m/s | 1.5<br>m/s | 3<br>m/s | 5<br>m/s                 | 1<br>m/s | 1.5<br>m/s | 3<br>m/s                      | 5<br>m/s | 1<br>m/s | 1.5<br>m/s | 3<br>m/s | 5<br>m/s |

| Α                                                                                                                | Planar                                                                                                                                                                                                                                                                        | AMB Only                 | 001001                | 11.6                                    | 9.8                         | 7.1      | 5.3      | 3.9      | 3.0        | 1.8      | 1.1                      | 4.6      | 3.8        | 2.8                           | 2.2      | 5.7      | 4.6        | 3.3      | 2.6      |

| Α                                                                                                                | Planar                                                                                                                                                                                                                                                                        | Full Dimm                | 001010                | 8.0                                     | 7.0                         | 5.5      | 4.5      | 5.7      | 4.5        | 2.9      | 1.9                      | 4.0      | 3.3        | 2.3                           | 1.6      | 4.4      | 3.7        | 2.9      | 2.4      |

| В                                                                                                                | Planar                                                                                                                                                                                                                                                                        | AMB Only                 | 001001                | 11.2                                    | 9.3                         | 6.6      | 4.9      | 5.3      | 4.1        | 2.6      | 1.8                      | 4.9      | 4.0        | 2.7                           | 1.8      | 4.3      | 3.4        | 2.2      | 1.5      |

| В                                                                                                                | Planar                                                                                                                                                                                                                                                                        | Full Dimm                | 001010                | 8.0                                     | 7.0                         | 5.5      | 4.5      | 5.7      | 4.5        | 2.9      | 1.9                      | 4.0      | 3.3        | 2.3                           | 1.6      | 4.4      | 3.7        | 2.9      | 2.4      |

| С                                                                                                                | Planar                                                                                                                                                                                                                                                                        | AMB Only                 | 001001                | 11.2                                    | 9.3                         | 6.6      | 4.9      | 5.3      | 4.1        | 2.6      | 1.8                      | 4.9      | 4.0        | 2.7                           | 1.8      | 4.3      | 3.4        | 2.2      | 1.5      |

| С                                                                                                                | Planar                                                                                                                                                                                                                                                                        | Full Dimm                | 001010                | 8.0                                     | 7.0                         | 5.5      | 4.5      | 5.7      | 4.5        | 2.9      | 1.9                      | 4.0      | 3.3        | 2.3                           | 1.6      | 4.4      | 3.7        | 2.9      | 2.4      |

| D/J                                                                                                              | Stacked                                                                                                                                                                                                                                                                       | AMB Only                 | 011001                | 11.2                                    | 9.3                         | 6.6      | 4.9      | 5.3      | 4.1        | 2.6      | 1.8                      | 4.9      | 4.0        | 2.7                           | 1.8      | 4.3      | 3.4        | 2.2      | 1.5      |

| D/J                                                                                                              | Stacked                                                                                                                                                                                                                                                                       | Full Dimm                | 011010                | 8.0                                     | 7.0                         | 5.5      | 4.5      | 5.7      | 4.5        | 2.9      | 1.9                      | 4.0      | 3.3        | 2.3                           | 1.6      | 4.4      | 3.7        | 2.9      | 2.4      |

| D/J                                                                                                              | Dual die                                                                                                                                                                                                                                                                      | AMB Only                 | 010001                | 11.2                                    | 9.3                         | 6.6      | 4.9      | 5.3      | 4.1        | 2.6      | 1.8                      | 4.9      | 4.0        | 2.7                           | 1.8      | 4.3      | 3.4        | 2.2      | 1.5      |

| D/J                                                                                                              | Dual die                                                                                                                                                                                                                                                                      | Full Dimm                | 010010                | 8.0                                     | 7.0                         | 5.5      | 4.5      | 5.7      | 4.5        | 2.9      | 1.9                      | 4.0      | 3.3        | 2.3                           | 1.6      | 4.4      | 3.7        | 2.9      | 2.4      |

| E/H                                                                                                              | Planar                                                                                                                                                                                                                                                                        | AMB Only                 | 001001                | 11.4                                    | 10.0                        | 8.1      | 6.8      | 4.0      | 3.0        | 1.8      | 1.1                      | 3.1      | 2.5        | 1.8                           | 1.4      | 5.1      | 4.4        | 3.4      | 2.8      |

| E/H                                                                                                              | Planar                                                                                                                                                                                                                                                                        | Full Dimm                | 001010                | 8.0                                     | 7.0                         | 5.5      | 4.5      | 5.7      | 4.5        | 2.9      | 1.9                      | 4.0      | 3.3        | 2.3                           | 1.6      | 4.4      | 3.7        | 2.8      | 2.3      |

|                                                                                                                  | Note 1: These maximum values must be met if SPD bytes 94:97 are zero  Note 2: If SPD bytes 94:97 are programmed, they effectively offset (up or down) the maximum curves by the difference between the byte and the maximum                                                   |                          |                       |                                         |                             |          |          |          |            | num      |                          |          |            |                               |          |          |            |          |          |

|                                                                                                                  |                                                                                                                                                                                                                                                                               | <u> </u>                 | •                     |                                         |                             |          | •        |          |            |          |                          | •        |            |                               |          |          |            |          |          |

|                                                                                                                  | value listed in the 1.5 m/s column. For example, for a R/C A with AMB only, if byte 94 (Ramb) is programmed to 8.8 degC/W, then the curve be lowered by (9.8 – 8.8) = 1.0 degC/W, and the adjusted maximum values would be 10.6, 8.8, 6.1 and 4.3 at the four air velocities. |                          |                       |                                         |                             |          |          |          |            |          |                          |          |            |                               |          |          |            |          |          |