# Intel<sup>®</sup> Xeon<sup>®</sup> Processor 7500 Series

Datasheet, Volume 2

March 2010

Order Number: 323341-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel® 64 architecture 64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel® 64 architecture. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information.

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM) and, for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary depending on hardware and software configurations and may require a BIOS update. Software applications may not be compatible with all operating systems. Please check with your application vendor.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Intel, Xeon, Intel SpeedStep Technology, and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2010, Intel Corporation. All Rights Reserved.

# Contents

| 1 | Intro | duction | 1                                                          | 11 |

|---|-------|---------|------------------------------------------------------------|----|

|   | 1.1   | Key Fea | atures                                                     | 11 |

|   | 1.2   | Termin  | ology and Conventions                                      |    |

|   |       | 1.2.1   | Abbreviations                                              |    |

|   | 1.3   | Notatio | nal Conventions                                            |    |

|   |       | 1.3.1   | Hexadecimal and Binary Numbers                             |    |

|   | 1.4   | Referer | nces                                                       | 15 |

| 2 | Intel | ® Xeon  | Processor 7500 Series Architecture                         | 17 |

|   | 2.1   | Introdu | uction                                                     | 17 |

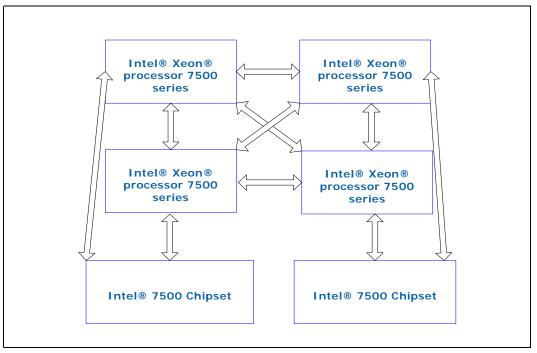

|   |       | 2.1.1   | Intel® Xeon® Processor 7500 Series-based Platform Overview | 18 |

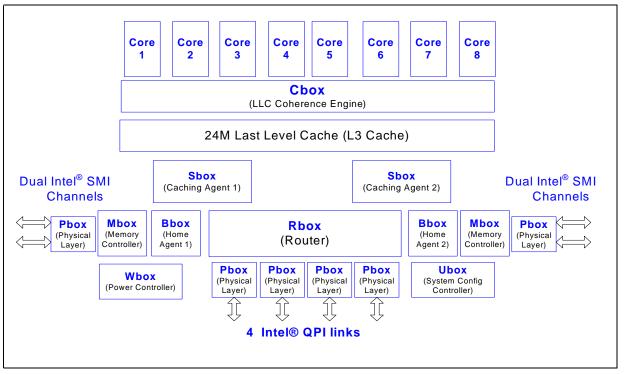

|   | 2.2   | Intel®  | Xeon® Processor 7500 Series Components (Boxes)             |    |

|   |       | 2.2.1   | Intel® Xeon® Processor 7500 Series Core                    |    |

|   |       | 2.2.2   | Intel QuickPath Interconnect                               | 20 |

|   | 2.3   | Cbox: I | Last Level Cache Coherency Engine                          |    |

|   |       | 2.3.1   | Sbox: Intel QuickPath Interconnect Caching Agent Bridge    |    |

|   |       | 2.3.2   | Rbox: Intel QuickPath Interconnect Router                  |    |

|   |       | 2.3.3   | Bbox: Intel QuickPath Interconnect Home Agent              |    |

|   |       | 2.3.4   | Mbox: On-Chip Memory Controller                            |    |

|   |       | 2.3.5   | Ubox: System Configuration Agent                           |    |

|   |       | 2.3.6   | Wbox: Power Controller                                     | 22 |

| 3 | Supp  | orted S | ystem Configurations                                       | 25 |

|   | 3.1   | Introdu | iction                                                     | 25 |

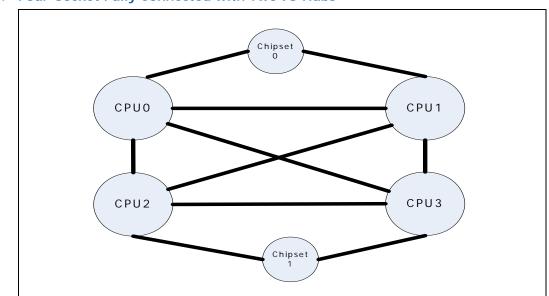

|   |       | 3.1.1   | Four-Socket Processor and Two Intel® 7500 Chipsets         |    |

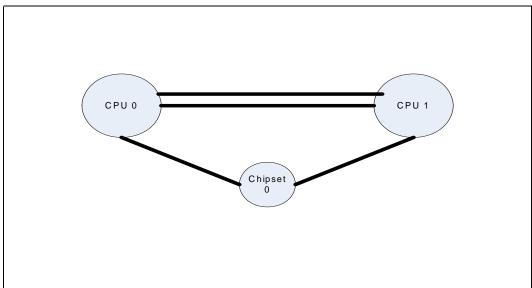

|   |       | 3.1.2   | Two-Socket Processor and One Intel® 7500 Chipset           | 26 |

|   |       | 3.1.3   | Eight-Socket Processor and Four Intel® 7500 Chipsets       |    |

|   |       | 3.1.4   | Scalable Systems, Intel® Xeon® Processor 7500 Series       |    |

|   |       |         | MP, and External Node Controller                           |    |

|   |       | 3.1.5   | Four Sockets and External Node Controller                  |    |

|   | 3.2   | Intel®  | Xeon® Processor 7500 Series – XNC Interface                | 28 |

| 4 | Addro | ess Map | o and Memory Configuration                                 | 29 |

|   | 4.1   | Introdu | uction                                                     | 29 |

|   | 4.2   | Addres  | s Map Regions                                              | 29 |

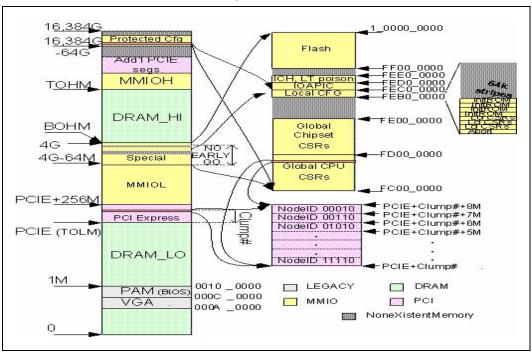

|   |       | 4.2.1   | Legacy Region: 01 M                                        | 30 |

|   |       | 4.2.2   | OS Region 1M4G–64M                                         | 32 |

|   |       | 4.2.3   | Special Region 4G–64M4G                                    | 34 |

|   |       | 4.2.4   | Extended Region                                            | 35 |

|   |       | 4.2.5   | IO Address Regions                                         | 36 |

|   |       | 4.2.6   | IO Decoder Region Summary                                  | 37 |

|   | 4.3   | Configu | uring Regions                                              |    |

|   |       | 4.3.1   | Configuring DRAM                                           |    |

|   |       | 4.3.2   | Configuring MMIOH                                          |    |

|   |       | 4.3.3   | Configuring MMConfig                                       |    |

|   | 4.4   |         | Address Decoder                                            |    |

|   |       | 4.4.1   | Target Address Decoder Configuration                       |    |

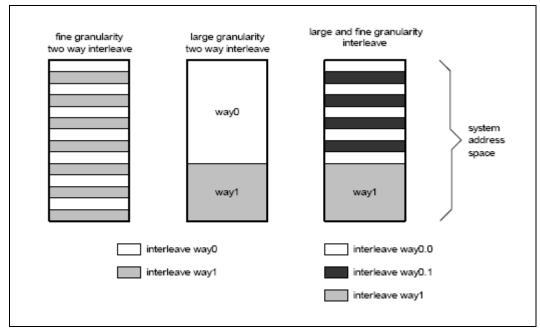

|   | 4.5   |         | s Interleaving                                             |    |

|   |       | 4.5.1   | Overall Structure                                          |    |

|   |       | 4.5.2   | DRAM Decoder                                               |    |

|   |       | 4.5.3   | I/O Decoders                                               |    |

|   |       | 4.5.4   | NodeID Generation                                          | 52 |

| 5 | LLC (                                                                             | Coherence Engine (Cbox) and Caching Agent (Sbox)                                                                                                                                                                                                                                                                                                                                                                                                | 55                                                                                                                                                                               |

|---|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.1                                                                               | Global Cache Coherence                                                                                                                                                                                                                                                                                                                                                                                                                          | 56                                                                                                                                                                               |

|   |                                                                                   | 5.1.1 Last Level Cache                                                                                                                                                                                                                                                                                                                                                                                                                          | 56                                                                                                                                                                               |

|   |                                                                                   | 5.1.2 Coherence                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56                                                                                                                                                                               |

|   | 5.2                                                                               | Performance Monitoring Counting Station (PMCS)                                                                                                                                                                                                                                                                                                                                                                                                  | 57                                                                                                                                                                               |

| 6 | Hom                                                                               | e Agent and Global Coherence Engine (Bbox)                                                                                                                                                                                                                                                                                                                                                                                                      | 59                                                                                                                                                                               |

|   | 6.1                                                                               | Supported Intel QuickPath Interconnect                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                  |

|   |                                                                                   | Transactions by Snoopy Caching Agent                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  |

|   | 6.2                                                                               | Supported Messages from Bbox to CA                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                  |

|   |                                                                                   | 6.2.1 Target Address Decoder                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

|   |                                                                                   | 6.2.2 Tracker Allocation Modes                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                  |

|   | ( )                                                                               | 6.2.3 NonSnoop Message Support                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                  |

|   | 6.3                                                                               | Error Handling                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                  |

|   |                                                                                   | <ul><li>6.3.1 Parity Errors</li><li>6.3.2 Time-outs</li></ul>                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |

|   |                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                  |

| 7 |                                                                                   | QuickPath Interconnect Router (Rbox)                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  |

|   | 7.1                                                                               | Rbox Overview                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                  |

|   |                                                                                   | 7.1.1 Rbox Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |

|   | 7.0                                                                               | 7.1.2 Router Port Connection                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

|   | 7.2                                                                               | Functional Overview                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                  |

|   | 7.3                                                                               | Router Table Addressing                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                  |

|   |                                                                                   | 7.3.2 RTA                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |

|   | 7.4                                                                               | Rbox MC Bank                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

|   | 7.4                                                                               | 7.4.1 BIOS Error CSRs                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                  |

|   |                                                                                   | 7.4.2 Performance Monitor                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |

|   |                                                                                   | 7.4.3 External Reset Inputs                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                  |

|   |                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                  |

| 8 | Syste                                                                             | em Configuration Controller (Ubox)                                                                                                                                                                                                                                                                                                                                                                                                              | 75                                                                                                                                                                               |

| 8 | <b>Syst</b><br>8.1                                                                | em Configuration Controller (Ubox)                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                  |

| 8 | -                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 75                                                                                                                                                                               |

| 8 | -                                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>75                                                                                                                                                                         |

| 8 | -                                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>75<br>76                                                                                                                                                                   |

| 8 | -                                                                                 | Introduction         8.1.1       Feature List         8.1.2       Out-of-Band Requests         8.1.3       Intel® QuickPath Interconnect Port Sharing with Bbox         8.1.4       PECI Interface                                                                                                                                                                                                                                              |                                                                                                                                                                                  |

| 8 | -                                                                                 | Introduction<br>8.1.1 Feature List<br>8.1.2 Out-of-Band Requests<br>8.1.3 Intel® QuickPath Interconnect Port Sharing with Bbox<br>8.1.4 PECI Interface<br>Intel QuickPath Interconnect Transactions                                                                                                                                                                                                                                             | 75<br>76<br>76<br>76<br>76<br>76                                                                                                                                                 |

| 8 | 8.1                                                                               | Introduction<br>8.1.1 Feature List<br>8.1.2 Out-of-Band Requests<br>8.1.3 Intel® QuickPath Interconnect Port Sharing with Bbox<br>8.1.4 PECI Interface<br>Intel QuickPath Interconnect Transactions.<br>8.2.1 Incoming Intel QuickPath Interconnect Requests                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>76<br>77<br>77                                                                                                                                           |

| 8 | 8.1<br>8.2                                                                        | Introduction         8.1.1       Feature List         8.1.2       Out-of-Band Requests         8.1.3       Intel® QuickPath Interconnect Port Sharing with Bbox         8.1.4       PECI Interface         Intel QuickPath Interconnect Transactions         8.2.1       Incoming Intel QuickPath Interconnect Requests         8.2.2       Outgoing Intel QuickPath Interconnect Requests                                                      |                                                                                                                                                                                  |

| 8 | 8.1<br>8.2<br>8.3                                                                 | Introduction         8.1.1       Feature List         8.1.2       Out-of-Band Requests         8.1.3       Intel® QuickPath Interconnect Port Sharing with Bbox         8.1.4       PECI Interface         Intel QuickPath Interconnect Transactions         8.2.1       Incoming Intel QuickPath Interconnect Requests         8.2.2       Outgoing Intel QuickPath Interconnect Requests         Platform Setup for Broadcast Transactions    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>78                                                                                                                                     |

| 8 | 8.1<br>8.2<br>8.3<br>8.4                                                          | Introduction<br>8.1.1 Feature List<br>8.1.2 Out-of-Band Requests<br>8.1.3 Intel® QuickPath Interconnect Port Sharing with Bbox<br>8.1.4 PECI Interface<br>Intel QuickPath Interconnect Transactions<br>8.2.1 Incoming Intel QuickPath Interconnect Requests<br>8.2.2 Outgoing Intel QuickPath Interconnect Requests/Responses<br>Platform Setup for Broadcast Transactions<br>Firmware Region                                                   |                                                                                                                                                                                  |

| 8 | 8.1<br>8.2<br>8.3                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

| 8 | 8.1<br>8.2<br>8.3<br>8.4                                                          | Introduction<br>8.1.1 Feature List<br>8.1.2 Out-of-Band Requests<br>8.1.3 Intel® QuickPath Interconnect Port Sharing with Bbox<br>8.1.4 PECI Interface<br>Intel QuickPath Interconnect Transactions.<br>8.2.1 Incoming Intel QuickPath Interconnect Requests<br>8.2.2 Outgoing Intel QuickPath Interconnect Requests/Responses<br>Platform Setup for Broadcast Transactions<br>Firmware Region<br>Off-Chip ROM Interface.<br>8.5.1 FLASHROM_CFG |                                                                                                                                                                                  |

| 8 | 8.1<br>8.2<br>8.3<br>8.4                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

| 8 | 8.1<br>8.2<br>8.3<br>8.4                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

| 8 | 8.1<br>8.2<br>8.3<br>8.4                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

| 8 | 8.1<br>8.2<br>8.3<br>8.4<br>8.5                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>79<br>80<br>81<br>83<br>83                                                                   |

| 8 | 8.1<br>8.2<br>8.3<br>8.4                                                          | Introduction<br>8.1.1 Feature List<br>8.1.2 Out-of-Band Requests<br>8.1.3 Intel® QuickPath Interconnect Port Sharing with Bbox.<br>8.1.4 PECI Interface.<br>Intel QuickPath Interconnect Transactions.<br>8.2.1 Incoming Intel QuickPath Interconnect Requests.<br>8.2.2 Outgoing Intel QuickPath Interconnect Requests/Responses.<br>Platform Setup for Broadcast Transactions<br>Firmware Region                                              | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>81<br>83<br>83<br>83<br>85                                                                         |

| 8 | 8.1<br>8.2<br>8.3<br>8.4<br>8.5                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>80<br>81<br>83<br>83<br>85<br>85                                                       |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li><li>8.6</li></ul> | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>80<br>81<br>83<br>83<br>83<br>85<br>85                                                 |

| 8 | 8.1<br>8.2<br>8.3<br>8.4<br>8.5                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>79<br>80<br>81<br>83<br>83<br>83<br>85<br>85<br>85<br>86                               |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li><li>8.6</li></ul> | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>79<br>80<br>81<br>83<br>83<br>85<br>85<br>85<br>86<br>86                               |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li><li>8.6</li></ul> | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>79<br>80<br>81<br>83<br>85<br>85<br>85<br>85<br>86<br>86                               |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li><li>8.6</li></ul> | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>79<br>80<br>81<br>83<br>85<br>85<br>85<br>85<br>86<br>86<br>86                         |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li><li>8.6</li></ul> | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>79<br>80<br>81<br>83<br>85<br>85<br>85<br>85<br>86<br>86<br>86             |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li><li>8.5</li><li>8.6</li></ul> | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>76<br>76<br>76<br>77<br>77<br>77<br>77<br>77<br>78<br>78<br>78<br>78<br>78<br>78<br>78<br>79<br>80<br>81<br>83<br>83<br>85<br>85<br>85<br>85<br>86<br>86<br>86<br>86<br>87 |

|    | 8.10 | SysInt Management Utilities                                    |    |

|----|------|----------------------------------------------------------------|----|

| 9  | Memo | ry Controller (Mbox)                                           | 89 |

|    | 9.1  | Memory Controller (Mbox) Support                               |    |

|    |      | 9.1.1 RAS Features                                             |    |

|    |      | 9.1.2 Pin-based Memory Throttle                                |    |

|    |      | 9.1.3 CKE Low Support                                          |    |

|    | 9.2  | Memory Controller (Mbox) Functional Details                    |    |

|    |      | 9.2.1 Memory Address Space                                     |    |

|    |      | 9.2.2 Mapping Criteria                                         |    |

|    |      | 9.2.3 Page Hit Mode                                            | 94 |

|    |      | 9.2.4 Closed Page Mode                                         | 94 |

|    |      | 9.2.5 Other Considerations                                     | 94 |

|    |      | 9.2.6 Device Address Field Variability                         | 94 |

|    |      | 9.2.7 Mapper Operation                                         |    |

|    | 9.3  | Power-Related Features                                         | 97 |

|    |      | 9.3.1 Power-Saving Features Provided to Firmware               | 98 |

|    |      | 9.3.2 Architectural Features to Mitigate High Temperature      | 98 |

|    | 9.4  | RAS Support                                                    |    |

|    |      | 9.4.1 Memory ECC                                               | 99 |

|    |      | 9.4.2 Address Protection                                       |    |

|    |      | 9.4.3 Transient Electrical Intel® SMI Errors                   |    |

|    |      | 9.4.4 Intel® SMI Lane Fail-over                                |    |

|    |      | 9.4.5 Mbox Internal Errors                                     |    |

|    |      | 9.4.6 Scrubbing 1                                              |    |

|    |      | 9.4.7 DIMM Sparing 1                                           |    |

|    | 9.5  | Population Requirements for Memory RAS Modes 1                 | 01 |

|    |      | 9.5.1 Intel <sup>®</sup> SMI Lock Stepped Channels Requirement |    |

|    |      | 9.5.2 Hemisphere Mode Requirement 1                            |    |

|    |      | 9.5.3 Memory Sparing 1                                         |    |

|    |      | 9.5.4 Memory Mirroring 1                                       |    |

|    | 9.6  | Errors 1                                                       |    |

|    |      | 9.6.1 Interrupts                                               |    |

|    |      | 9.6.2 Mbox Parity Error 1                                      |    |

|    |      | 9.6.3 Finite State Machine Error 1                             |    |

|    |      | 9.6.4 Error Flow State Machine Success and Failure             |    |

|    |      | 9.6.5 Intel® SMI Link CRC Error                                |    |

|    |      | 9.6.6 Intel SMI Link Alert Frame Error 1                       |    |

| 10 | Powe | r Management Architecture 1                                    | 07 |

|    |      | -                                                              | 07 |

|    |      | 10.1.1 Overview                                                | 07 |

|    |      | 10.1.2 Frequency/Voltage Target Management1                    |    |

|    | 10.2 | Turbo Mode                                                     |    |

|    |      | 10.2.1 "Legacy" Turbo Mode                                     |    |

|    |      | 10.2.2 Turbo Mode Policies                                     | 11 |

|    |      | 10.2.3 Intel Thermal Monitor                                   | 12 |

|    |      | 10.2.4 External PROCHOT# Pin Assertion                         | 12 |

|    |      | 10.2.5 External ForcePR# Pin Assertion                         | 12 |

|    |      | 10.2.6 Core Clock Modulation 1                                 | 13 |

|    | 10.3 | Thermal Management 1                                           |    |

|    |      | 10.3.1 Overview                                                |    |

|    |      | 10.3.2 Digital Thermal Sensor 1                                |    |

|    | 10.4 | Idle State Power Management 1                                  |    |

|    |      | 10.4.1 Overview                                                |    |

|    |      | 10.4.2 C-State Support 1                                       | 21 |

|    |       | 10.4.3 S-State Support                             | 125   |

|----|-------|----------------------------------------------------|-------|

|    | 10.5  | CPUID                                              | 125   |

| 11 | Douvo | r Controller (Wbox)                                | 107   |

|    |       |                                                    |       |

|    | 11.1  | Intel Thermal Monitor 1 / T-State State Machine    |       |

|    |       | 11.1.1 Requesting T-State Throttling               |       |

|    |       | 11.1.2 Intel Thermal Monitor 1                     |       |

|    |       | 11.1.3 MSR                                         |       |

|    |       | 11.1.4 ICH Emulation                               |       |

|    |       | 11.1.5 Thread C-States                             |       |

|    |       | 11.1.6 Core C-States                               | 129   |

|    |       | 11.1.7 S-States                                    | 129   |

|    |       | 11.1.8 Platform Environment Control Interface      | 129   |

| 10 | Confi | munstion and DAC Fastures                          | 1 2 2 |

| 12 |       | guration and RAS Features                          |       |

|    | 12.1  | CPU NodeID Assignments                             |       |

|    |       | 12.1.1 NodeID Restrictions                         |       |

|    | 12.2  | Credit Configurations                              |       |

|    |       | 12.2.1 Protocol Credits                            | 134   |

|    |       | 12.2.2 Link Credits                                | 136   |

|    | 12.3  | Protocol Configurations                            | 136   |

|    |       | 12.3.1 Snoop Modes                                 | 136   |

|    |       | 12.3.2 Snoopy + IOH Directory                      |       |

|    |       | 12.3.3 Unsupported Modes                           |       |

|    | 12.4  | Routing Configurations                             |       |

|    |       | 12.4.1 Route Table Entries                         |       |

|    |       | 12.4.2 Virtual Networks                            |       |

|    | 12.5  | Physical Layer Configuration.                      |       |

|    | 12.5  | 12.5.1 Intel® QuickPath Interconnect data failover |       |

|    | 12.6  |                                                    |       |

|    |       | Power Configurations                               |       |

|    | 12.7  | Miscellaneous and Special Message Broadcast        |       |

|    | 12.8  | DRAM Configurations.                               |       |

|    |       | 12.8.1 DIMM Configurations                         |       |

|    |       | 12.8.2 DIMM Restrictions                           |       |

|    | 12.9  | Boot Modes                                         |       |

|    |       | 12.9.1 Direct Connect Flash Boot                   |       |

|    |       | 12.9.2 Service Processor Boot                      |       |

|    |       | 12.9.3 Intel® QuickPath Interconnect Link Init     | 142   |

|    |       | 12.9.4 Intel QuickPath Interconnect Link Boot      |       |

|    | 12.10 | Memory Mirroring Configuration and Constraints     | 143   |

|    |       | 12.10.1 Mirroring Configuration                    | 143   |

|    |       | 12.10.2 Mirroring Reconfiguration Flow             | 144   |

|    |       | 12.10.3 Mirroring Constraints                      |       |

|    | 12.11 | Memory Migration                                   |       |

|    |       | 12.11.1 Memory Migration Configuration             |       |

|    |       | 12.11.2 Memory Migration Constraints               |       |

|    | 12 12 | DIMM Sparing Configuration and Constraints         |       |

|    | 12.12 | 12.12.1 DIMM/Rank Sparing Configuration            |       |

|    |       | 12.12.2 DIMM/Rank Sparing Comgutation              |       |

|    |       |                                                    |       |

|    | 10 10 | 12.12.3DIMM/Rank Sparing Constraints               |       |

|    | 12.13 | IOH Directory Configuration and Constraints.       |       |

|    |       | 12.13.110H Directory Configuration                 |       |

|    |       | 12.13.210H Directory Constraints                   |       |

|    |       | 12.13.3 Misc Constraints                           | 147   |

| 13 | Firm  | ware                                                          | 149 |

|----|-------|---------------------------------------------------------------|-----|

|    | 13.1  | General Firmware Architecture                                 | 149 |

|    |       | 13.1.1 Overview of Intel® Xeon® Processor 7500 Uncore Control |     |

|    |       | Register Architecture                                         | 149 |

|    |       | 13.1.2 CPUID Changes on Intel® Xeon® Processor 7500           | 149 |

|    |       | 13.1.3 CPUID.1: Leaf 1                                        | 150 |

|    |       | 13.1.4 CPUID.2: Leaf 2                                        | 150 |

|    |       | 13.1.5 CPUID.4: Leaf 4                                        | 150 |

|    |       | 13.1.6 CPUID.5: Leaf 5                                        | 151 |

|    |       | 13.1.7 CPUID.6: Leaf 6                                        | 151 |

|    |       | 13.1.8 CPUID.A: Leaf 10                                       | 152 |

|    |       | 13.1.9 Memory/Addressing Related Features                     | 153 |

|    |       | 13.1.10 Interrupts                                            |     |

|    |       | 13.1.11 Power Related Features                                | 154 |

|    | 13.2  | Firmware and Reset                                            |     |

|    |       | 13.2.1 Initializing the Intel QuickPath Interconnect Links    | 155 |

|    |       | 13.2.2 Boot Modes                                             | 158 |

|    |       | 13.2.3 Selecting the Package BSP                              | 158 |

| 14 | Intel | Xeon® Processor 7500 Series Errors                            |     |

|    | 14.1  | Error Containment and S/W Error Recovery Overview             |     |

|    | 14.2  | Firmware Support                                              |     |

|    | 14.3  | New Resources                                                 |     |

|    |       | 14.3.1 MCG_CAP[10]: Interrupt on Corrected Error              |     |

|    |       | 14.3.2 New LVT Entry                                          |     |

|    |       | 14.3.3 MCi_STATUS[52:38]: Corrected Error Count               |     |

|    |       | 14.3.4 MCi_MISC_2                                             |     |

|    |       | 14.3.5 Logging MSR Addresses                                  |     |

|    |       | 14.3.6 Core Error Severities                                  |     |

|    |       | 14.3.7 Core Behavior on a Machine Check                       |     |

|    | 14.4  | Uncore Error Severities                                       |     |

|    | 14.5  | Error Signaling                                               |     |

|    | 11.0  | 14.5.1 Signals and Messages                                   |     |

|    |       | 14.5.2 Signaling Behavior.                                    |     |

|    | 14.6  | Data Poison Handling                                          |     |

|    | 11.0  | 14.6.1 Tracking Poisoned Data in Memory                       |     |

|    |       | 14.6.2 Error Recovery                                         |     |

|    |       | 14.6.3 Poison Mode and System Management Interrupt            |     |

|    | 14.7  |                                                               |     |

|    | ,     |                                                               |     |

# **Figures**

| 2-1   | Platform Block Diagram, Four-socket Two-IOH Configuration                       |      |

|-------|---------------------------------------------------------------------------------|------|

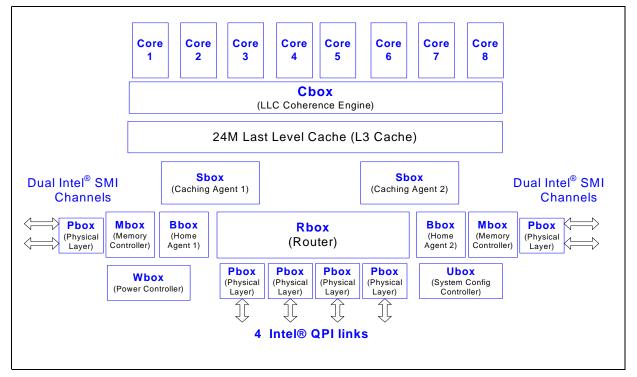

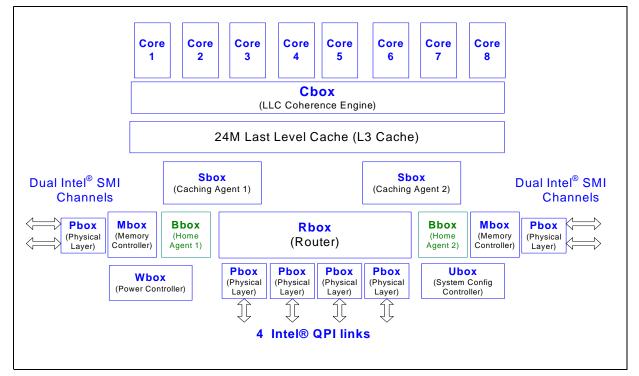

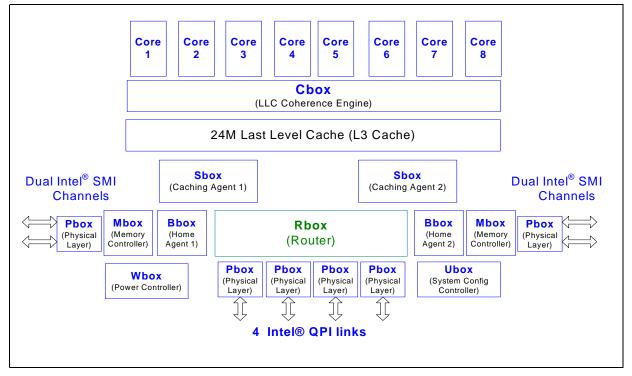

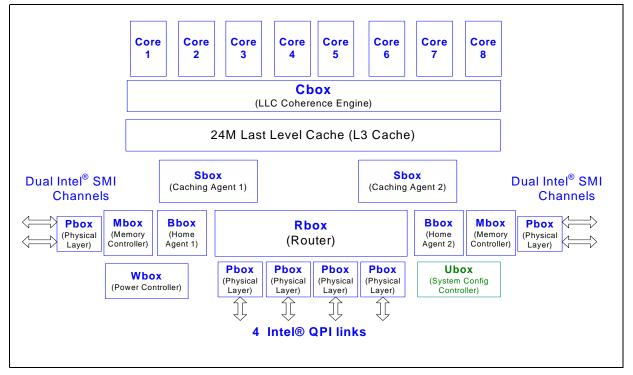

| 2-2   | Intel® Xeon® Processor 7500 Series Block Diagram                                | .19  |

| 3-1   | Four-Socket Fully Connected with Two IO Hubs                                    | 25   |

| 3-2   | Two-Socket Fully Connected with One IO Hub                                      | 26   |

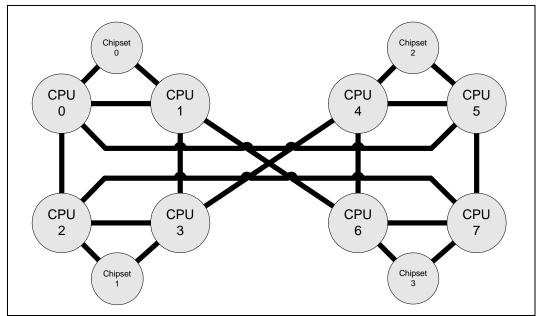

| 3-3   | Eight-Socket Glueless configuration                                             | 27   |

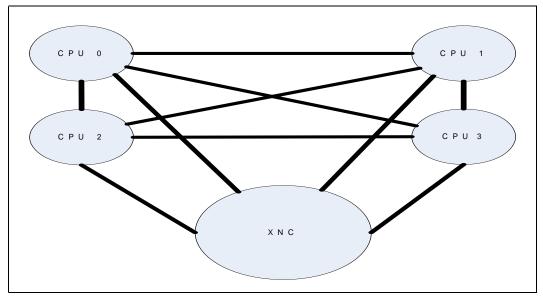

| 3-4   | Scalable MP System, Clumps of Two Intel® Xeon® Processor 7500 Series            |      |

|       | and Two Intel® 7500 Chipsets                                                    | .27  |

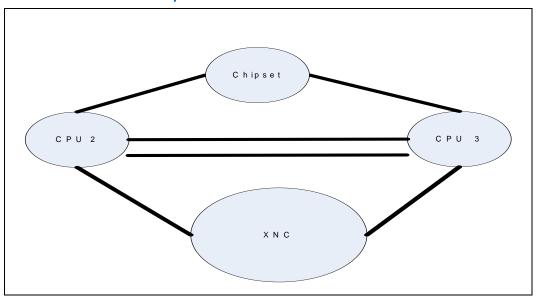

| 3-5   | Scalable Four-Socket Fully Connected Clump with External Node Controllers       |      |

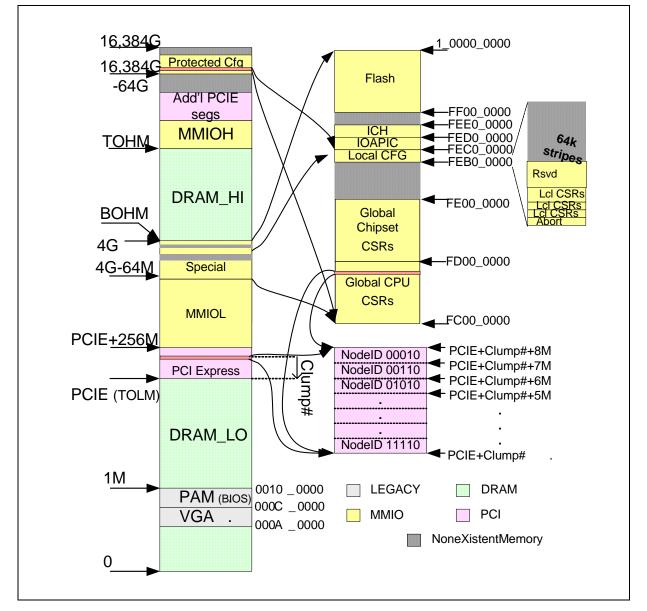

| 4-1   | Intel® Xeon® Processor 7500 Series Address Map                                  | .30  |

| 4-2   | Source Address Decoder Block Diagram                                            | .39  |

| 5-1   | Intel® Xeon® Processor 7500 Block Diagram                                       | .55  |

| 6-1   | Intel® Xeon® Processor 7500 Block Diagram                                       | 59   |

| 6-2   | Fine Granularity and Large Granularity Interleaving of the System Address Space | .61  |

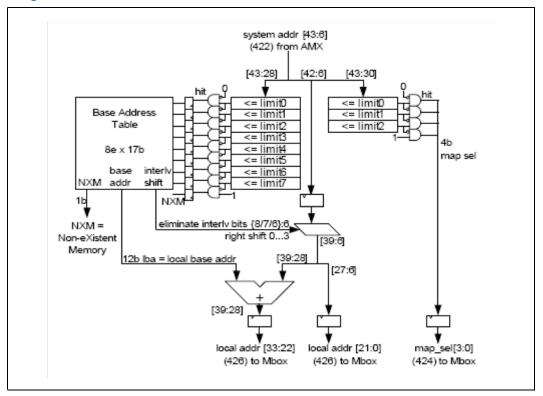

| 6-3   | Target Address Decoder                                                          | .62  |

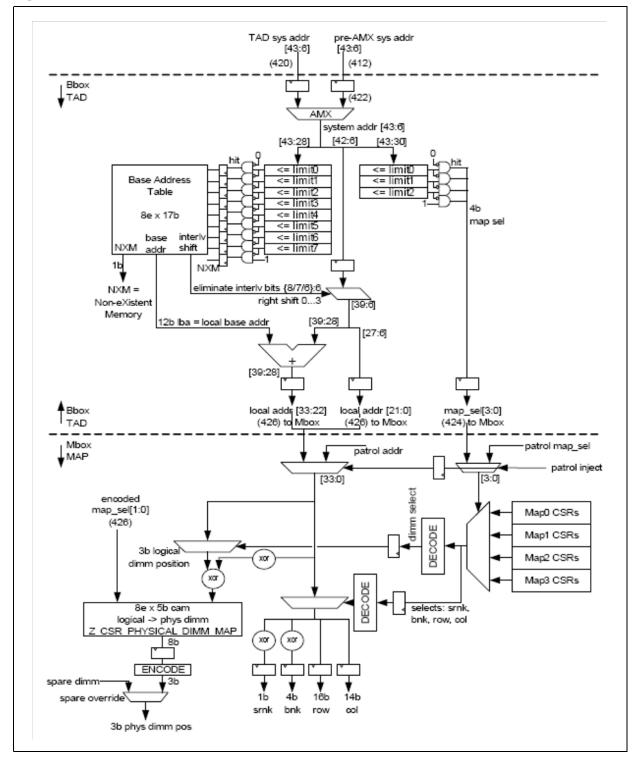

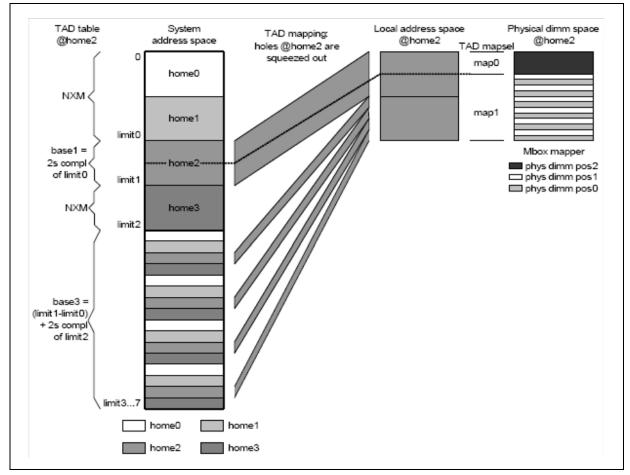

| 6-4   | TAD's Environment                                                               | 63   |

| 6-5   | System Address Space Interleave Example                                         | 64   |

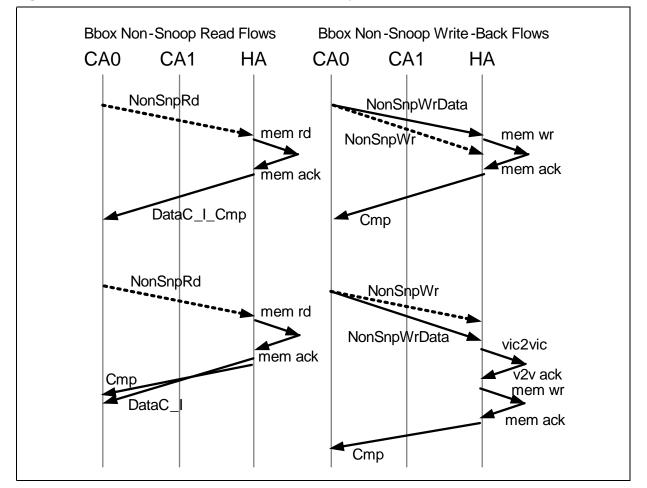

| 6-6   | Intel QuickPath Interconnect NonSnp Flows in Bbox                               | .67  |

| 7-1   | Intel® Xeon® Processor 7500 Block Diagram                                       | 69   |

| 7-2   | Rbox Block Diagram                                                              | 70   |

| 8-1   | Intel® Xeon® Processor 7500 Block Diagram                                       | 75   |

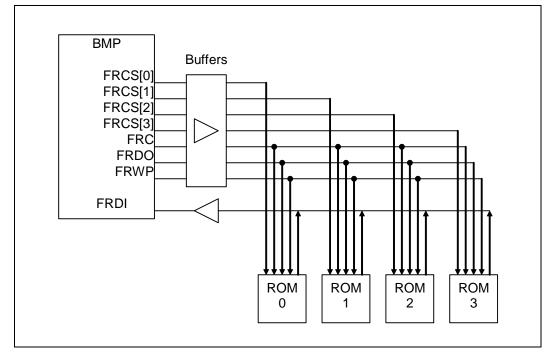

| 8-2   | Flash ROMs Connected to Intel® Xeon® Processor 7500 Series                      | 79   |

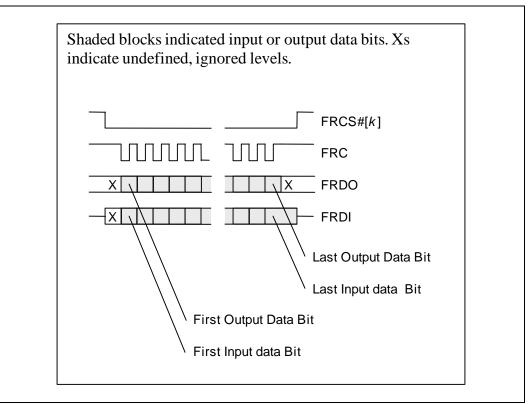

| 8-3   | Generalized Interface Sequence                                                  | . 80 |

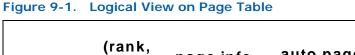

| 9-1   | Logical View on Page Table                                                      | .96  |

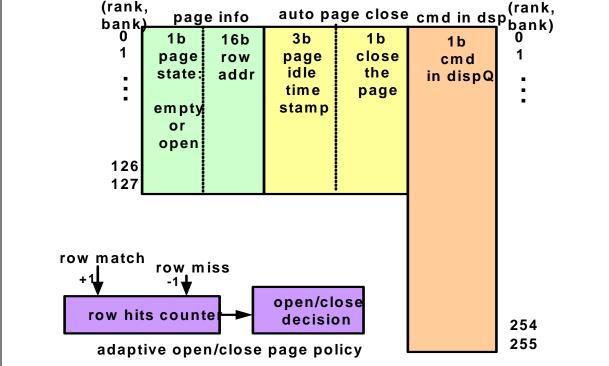

| 9-2   | Intel <sup>®</sup> SMI Channel-Pair Lock-Step Requirement                       | 102  |

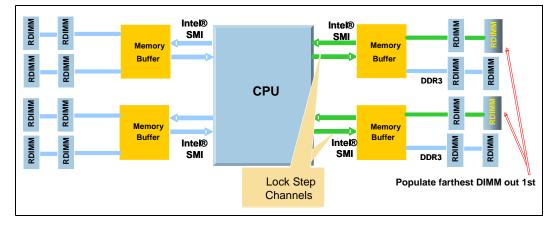

| 9-3   | Hemisphere Mode                                                                 | 103  |

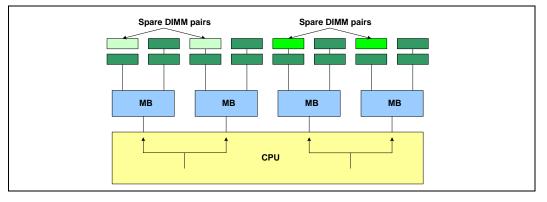

| 9-4   | Memory DIMM and Rank Sparing                                                    | 103  |

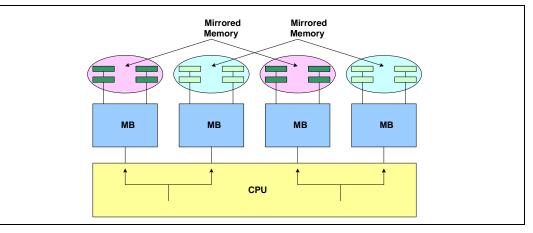

| 9-5   | Memory Mirroring (Intra-Socket)                                                 | 104  |

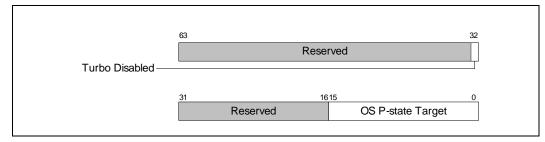

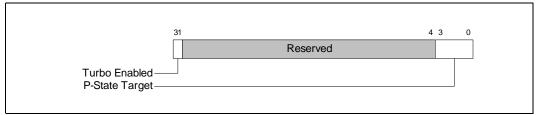

| 10-1  | IA32_PERF_CTRL MSR (0x199)                                                      | 108  |

| 10-2  | P_STATE_Thread                                                                  |      |

| 10-3  | IA32_PERF_STATUS MSR (0x198)                                                    | 109  |

| 10-4  | C_STATE_Thread                                                                  | 109  |

| 10-5  | IA32_CLOCK_MODULATION MSR (0x19A)                                               | 114  |

| 10-6  | ACPI P_CNT I/O Register (Located at P_BLK+0)                                    | 115  |

| 10-7  | PMG_IO_CAPTURE MSR (0x0E4)                                                      | 115  |

| 10-8  | ICH_THROT Control Register                                                      | 115  |

| 10-9  | T-STATE_PERIOD MSR (0x276)                                                      | 116  |

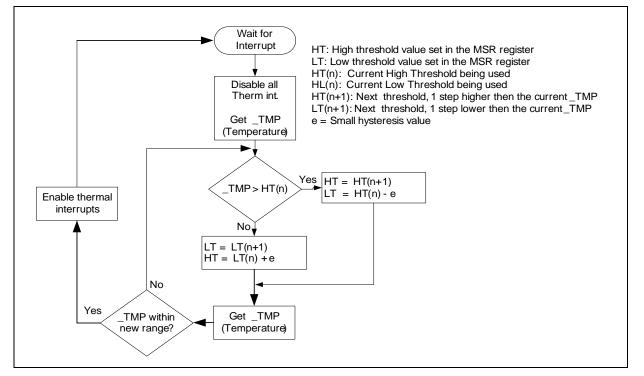

| 10-10 | APCI _TMP Algorithm                                                             | 118  |

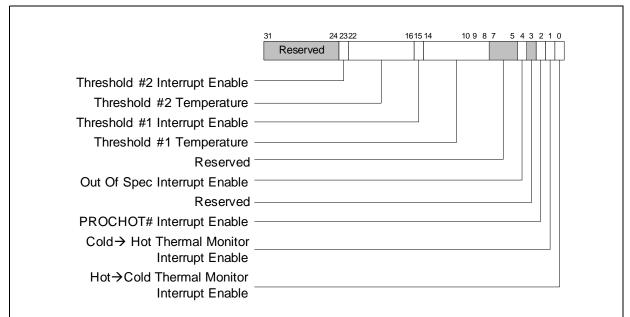

| 10-11 | IA32_THERM_INTERRUPT MSR (0x19B)                                                | 119  |

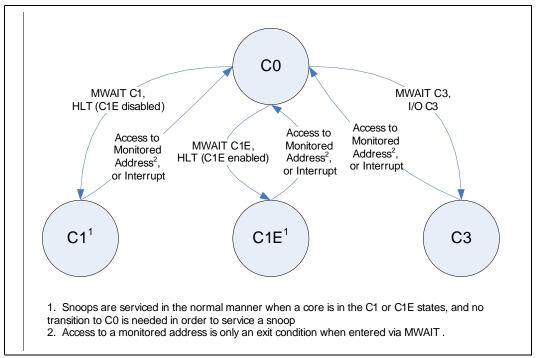

|       | Valid Thread/Core Architectural C-State Transitions                             |      |

|       | CPUID Power Management Leaf                                                     |      |

| 11-1  | T-State Throttling Control Register Format                                      | 128  |

|       |                                                                                 |      |

# Tables

| 1-1  | Abbreviation Summary                                        | 13  |

|------|-------------------------------------------------------------|-----|

| 1-2  | References                                                  | 15  |

| 2-1  | Intel® Xeon® Processor 7500 Series Key Features             |     |

| 2-2  | System Interface Functional Blocks                          |     |

| 4-1  | SMM Control Bits                                            | 31  |

| 4-2  | Truth Table for Mapping Address to PAM Segment              | 32  |

| 4-3  | PAM Region Handling                                         | 32  |

| 4-4  | IO Decoder Regions                                          | 37  |

| 4-5  | DRAM Decoder Fields                                         | 43  |

| 4-6  | Intel® QuickPath Interconnect Memory Attributes             | 43  |

| 4-7  | Example Target Interleaving                                 |     |

| 4-8  | I/O Decoder Entries                                         | 46  |

| 4-9  | I/O Decoder Entries with Target Lists                       |     |

| 4-10 | IOS Decoder Entries                                         | 48  |

| 4-11 | VGA/CSEG                                                    | 50  |

| 4-12 | BIOS Entry Segments                                         | 51  |

| 4-13 | Target List Index                                           | 53  |

| 4-14 | NodeID Formation                                            | 53  |

| 6-1  | Home Channel Requests                                       |     |

| 6-2  | Home Channel Responses                                      | 60  |

| 6-3  | Response Channel Data                                       | 60  |

| 6-4  | Snoop Channel Messages                                      |     |

| 6-5  | Data Response Channel                                       |     |

| 6-6  | Response Channel Non Data (Ordered per Address)             |     |

| 6-7  | Programming of TAD at home2                                 |     |

| 6-8  | TAD Reset Values                                            |     |

| 6-9  | Tracker Allocation Modes                                    |     |

| 6-10 | TID Assignment Restrictions                                 |     |

| 6-11 | Time-out Range and Granularity                              |     |

| 6-12 | Intel® Xeon® Processor 7500 Transaction Time-out Levels     |     |

| 7-1  | Router Table Addressing                                     |     |

| 7-2  | SBU Route Table                                             |     |

| 7-3  | Router Table Entry                                          |     |

| 7-4  | RTA CSR Write Format                                        |     |

| 8-1  | PECI / TAP CSR Rd/Wt Format                                 |     |

| 8-2  | Intel® Xeon® Processor 7500 Series Flash ROM Interface Pins |     |

| 8-3  | Initial Flash ROM Mapping                                   |     |

| 8-4  | Ubox Exceptions                                             | 85  |

| 8-5  | MCI_Summary                                                 |     |

| 9-1  | Supported Bit Combinations for Highest Capacity DRAMs       |     |

| 10-1 | Turbo Mode Policy                                           |     |

| 10-2 | IA32_CLOCK_MODULATION MSR Duty Cycle                        |     |

| 10-3 | Core Clock Modulation Duty Cycle Selection                  |     |

| 10-4 | Core C-State Resolution                                     |     |

| 10-5 | Package C-State Resolution                                  |     |

| 11-1 | Clock Modulation Duty Cycle Encoding                        |     |

| 12-1 | NodeID Usage                                                |     |

| 12-2 | Tracker Modes                                               |     |

| 12-3 | RTID Generation 8 LLC (last level cache) slices             |     |

| 12-4 | RTID Generation 6 LLC (last level cache) slices             | 135 |

| 12-5 | RTID Generation 4 LLC (last level cache) slices             |

|------|-------------------------------------------------------------|

| 13-1 | Intel® Xeon® Processor 7500 LLC SKUs                        |

| 13-2 | Threads Sharing Each Cache Level                            |

| 13-3 | Fields Providing Numbers of C Sub-states                    |

| 13-4 | Intel® Xeon® Processor 7500 Leaf 6 Values                   |

| 13-5 | Intel® Xeon® Processor 7500 Output Values for CPUID Leaf 11 |

# **Revision History**

| Document<br>Number | Revision<br>Number | Description    | Date       |

|--------------------|--------------------|----------------|------------|

| 323341             | 001                | Public release | March 2010 |

§

# **1** Introduction

The Intel® Xeon® Processor 7500 Series (formerly code named Nehalem-EX) is the first-generation chip multiprocessor (CMP) offering Intel® QuickPath Interconnect (Intel<sup>®</sup> QPI) Technology in the Intel<sup>®</sup> Xeon<sup>®</sup> MP processor family of processors. The Intel® Xeon® processor 7500 series implements up to eight multi-threaded (two thread) cores based upon the Intel® Xeon® processor 7500 series core design. A large, up to 24-MB, last-level cache (level 3), has been implemented to be shared across all active cores. The Intel® Xeon® processor 7500 series implements Intel® QuickPath Interconnect Technology to replace the traditionally-implemented front-side bus. The Intel® Xeon® processor 7500 series provides four full width Intel QuickPath Interconnect links, sufficient to implement a glue-less (direct connect) four processor socket and two IOH solutions, as well as scalable solutions based on OEM-developed external node controllers (referred to as XNC). The Intel® Xeon® processor 7500 series also integrates two memory controllers supporting DDR3 memory technology to further enhance memory latency at higher memory capacity. The Intel® Xeon® processor 7500 series will be implemented on Intel 45-nm process technology and will be binary-compatible with applications running on previous members of Intel's IA-32/ IA-64 microprocessors.

*Note:* Unless specifically required for clarity, this document will use 'processor' in place of the specific product name. The component described in this document include Intel® Xeon® processor 7500 series.

## 1.1 Key Features

Some high-level key features of the Intel® Xeon® Processor 7500 Series include:

- Chip multiprocessor architecture with up to eight cores per socket

- · Hyper-threaded cores, two threads

- New low-power, high-performance core architecture

- Supports 48-bit virtual addressing and 44-bit physical addressing

- 32 KB Level 1 instruction cache with single bit error correction, and L1 Data cache: 32-KB Level 1 data cache with parity protection, or 16KB Level 1 with ECC error correction and detection on data and on TAG

- 256 kB L2 instruction/data cache, ECC protected (SECDED)

- 24-MB LLC, instruction/data cache, ECC protected (Double Bit Error Correction, Triple bit Error Detection(DECTED), and SECDEC on TAG)

- High-bandwidth point-to-point Intel QuickPath Interconnect link interface enabling glueless 4-socket MP platforms:

- Four full width Intel QuickPath Interconnect links targeted at 4.8-6.4 GT/s

- Aggregate bandwidth of 25.6 GB/s per Intel QuickPath Interconnect link (at 6.4 GT/s)

- Two on-chip memory controllers provide ample memory bandwidth and memory capacity for demanding enterprise applications:

- Each memory controller manages two Intel® Scalable Memory Interconnect (Intel® SMI) channels, operated in lockstep, and an Intel® 7500 Scalable Memory Buffer, an Intel SMI-DDR3 bridge, on each Intel® SMI channel.

- Total of four Intel SMI channels

- Support for up to 16 DDR3 DIMMs per socket. Four DIMMs per Intel® 7500 Scalable Memory Buffer

- Support for DDR III 800, 978, 1067MHz memory speeds

- Support for 1, 2 and 4 Gigabit DRAM technology

- Support for up to 16 GB Quad Rank DIMM

- Memory RAS features including:

- Memory ECC support including correction of x4 and x8 chip-fail

- Failover mode to operate with a single lane failure per channel per direction

- Support for memory mirroring and resilvering, Demand and Patrol Scrubbing

- Support for memory migration

- Intel QuickPath Interconnect RAS features including:

- Self-healing via link width reduction

- Link-level retry mechanism provides hardware retry on link transmission errors

- 8-bit CRC or 16-bit rolling CRC

- Error reporting mechanisms including Data Poisoning indication and Viral bit

- Support for lane reversal as well as polarity reversal at the Intel QuickPath Interconnect links

- Support for Platform-level RAS features: Hot Add/Remove, dynamic reconfiguration

- High-bandwidth ECC protected Crossbar Router with route-through capability

- New power management technology to best manage power across eight cores, including support for Enhanced Intel SpeedStep<sup>®</sup> Technology, Intel<sup>®</sup> Thermal Monitor, and Intel Thermal Monitor 2

- Dynamic monitoring of die temperature via digital thermal sensors

- · Sideband read/write access to un-core logic via PECI and JTAG

- System management mode (SMM)

- Supports an *SMBus Specification, Revision 2.0* slave interface for server management components, that is, PIROM

- Manageability Components including an EEPROM/Processor Information ROM accessed through SMBus interface

- Machine Check Architecture

- Support for Intel<sup>®</sup> Virtualization Technology (Intel<sup>®</sup> VT) for IA-32 Intel<sup>®</sup> Architecture 2 (Intel<sup>®</sup> VT-x 2)

- Allows a platform to run multiple Operating systems and applications in independent partitions or "containers". One physical compute system can function as multiple "virtual" systems.

- Execute Disable Bit capability

- Direct-attach firmware to processor socket via serial flash interface

- Supports commodity 1-, 4-, 8-MB SPI Flash ROM devices

# 1.2 Terminology and Conventions

This section defines the abbreviations, terminology, and other conventions used throughout this document.

## 1.2.1 Abbreviations

## Table 1-1. Abbreviation Summary (Sheet 1 of 2)

| Term                           | Description                                                                                                                                                                                                    |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <sz></sz>                      | Region Size in System Address Map                                                                                                                                                                              |

| RMW                            | Read Modify Write                                                                                                                                                                                              |

| SIPI                           | Start IPI                                                                                                                                                                                                      |

| IPI                            | Interprocessor Interrupt                                                                                                                                                                                       |

| Intel® 7500 Scalable           | Advanced Memory Buffer                                                                                                                                                                                         |

| Memory Buffer                  |                                                                                                                                                                                                                |

| APIC                           | Advanced Programmable Interrupt Controller                                                                                                                                                                     |

| BBox                           | Home Agent or Global Coherence Engine                                                                                                                                                                          |

| Intel <sup>®</sup> IBIST       | Intel <sup>®</sup> Interconnect Built-In Self Test                                                                                                                                                             |

| BMC                            | Baseboard Management Controller                                                                                                                                                                                |

| BSP/SBSP                       | (System) Boot Strap Processor: A processor responsible for system initialization.                                                                                                                              |

| Clump                          | A collection of processors                                                                                                                                                                                     |

| CMP                            | Chip Multi-Processing                                                                                                                                                                                          |

| СОН                            | Coherent                                                                                                                                                                                                       |

| Core(s)                        | A Processing Unit                                                                                                                                                                                              |

| Core/System Interface/<br>SPIS | Interface Logic block present in processor, for interfacing the processor core clusters with Uncore block.                                                                                                     |

| CRC                            | Cyclic Redundancy Code                                                                                                                                                                                         |

| DC-SFROM                       | Direct Connect Serial Flash ROM                                                                                                                                                                                |

| DDR                            | Double Data Rate                                                                                                                                                                                               |

| DIMM                           | Dual In Line Memory Module. A packaging arrangement of memory devices on a socketable substrate.                                                                                                               |

| ECC                            | Error Correction Code                                                                                                                                                                                          |