# Techniques for Lowering Power Consumption in Design Utilizing the Intel® EP80579 Integrated Processor Product Line

## **Application Note**

| ***February 2010***

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting [Intel's Web Site](#).

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See [http://www.intel.com/products/processor\\_number](http://www.intel.com/products/processor_number) for details.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2010, Intel Corporation. All rights reserved.

## Contents

---

|            |                                                  |    |

|------------|--------------------------------------------------|----|

| <b>1.0</b> | <b>Introduction</b>                              | 5  |

| 1.1        | Related Documents                                | 5  |

| <b>2.0</b> | <b>Overview</b>                                  | 5  |

| <b>3.0</b> | <b>Device Disabling</b>                          | 6  |

| <b>4.0</b> | <b>IA-32 core Throttling</b>                     | 7  |

| 4.1        | IA-32 core Throttling Implementation and Effects | 8  |

| 4.2        | Benefits of Throttling                           | 9  |

| 4.2.1      | Throttling Power Savings                         | 9  |

| <b>5.0</b> | <b>Power Management</b>                          | 11 |

| 5.1        | Supported System Power States                    | 11 |

| 5.2        | BIOS Support for Power Management                | 11 |

| <b>6.0</b> | <b>Conclusions</b>                               | 11 |

## Figures

|   |                                              |   |

|---|----------------------------------------------|---|

| 1 | Clocks Relationship for 50% Throttling Ratio | 8 |

|---|----------------------------------------------|---|

## Tables

|   |                                                               |    |

|---|---------------------------------------------------------------|----|

| 1 | Related Documents                                             | 5  |

| 2 | Configurable Devices That Can be Disabled                     | 6  |

| 3 | Throttling Configuration with FORCE_THLT                      | 7  |

| 4 | Throttling Power Savings (All Interface Device Units Enabled) | 9  |

| 5 | Throttling Power Savings with Devices Enabled/Disabled        | 10 |

## Revision History

---

| Date          | Revision | Description                                                                                       |

|---------------|----------|---------------------------------------------------------------------------------------------------|

| February 2010 | 003      | Updated <a href="#">Table 5</a>                                                                   |

| May 2009      | 002      | Update content in <a href="#">Table 1</a> , <a href="#">Table 4</a> , and <a href="#">Table 5</a> |

| August 2008   | 001      | Initial Release.                                                                                  |

## 1.0 Introduction

This application note discusses techniques that are used to conserve power when using the Intel® EP80579 Integrated Processor Product Line (EP80579) in system platform designs.

### 1.1 Related Documents

**Table 1. Related Documents**

| Document Title                                                                | Document Number                                                                    |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| <i>Intel® EP80579 Integrated Processor Product Line Datasheet</i>             | 320066                                                                             |

| <i>Intel® EP80579 Integrated Processor Product Line Platform Design Guide</i> | 320068                                                                             |

| <i>Intel® EP80579 Integrated Processor Product Line BIOS Writers Guide</i>    | <p><b>Note:</b><br/>Contact your Intel Field Representative to obtain document</p> |

## 2.0 Overview

The EP80579 architecture is comprised of several functional units not all simultaneously utilized in all target applications. This application note describes the power savings achieved by utilizing the clock gating and IA-32 core throttling features designed into the EP80579.

By default, several internal functional units are brought out of reset with their respective clocks enabled. The clocks for these functional units are disabled on a per unit basis under BIOS control, by programming the IO\_DEVICE\_CONFIG register. Refer to the *Intel® EP80579 Integrated Processor Product Line BIOS Writers Guide* for additional details on the IO\_DEVICE\_CONFIG register.

Additionally it is feasible to configure the IA-32 core internal clock to throttle, to lower the aggregate frequency for lower data rate applications. This results in additional power savings for applications that do not require the IA-32 core to operate at the normal internal clock rate.

The power savings that is achieved using these features is presented within this document. These power saving techniques are used, in conjunction with the power management capabilities described in the *Intel® EP80579 Integrated Processor Product Line Datasheet*, to determine the total power consumption for a particular application.

## 3.0 Device Disabling

There are several internal functional units within the EP80579 that come up out of reset with their internal clocks enabled, but BIOS can be used to disable the units that are not utilized in the platform application. This allows applications that do not require the use of all of the hardware interface units to reduce the total platform power consumption. Devices are enabled/disabled by using the IO\_DEVICE\_CONFIG Register. BIOS uses this register to put unused devices into a powered down state. Devices that are disabled do not show up in the PCI configuration space, hence the IO\_DEVICE\_CONFIG Register has to be configured prior to PCI enumeration to avoid potential conflicts.

**Table 2** provides a list of devices that are disabled with BIOS by using the IO\_DEVICE\_CONFIG Register.

*Note:* Consult with your BIOS vendor to configure the IO\_DEVICE\_CONFIG register to disable any unused interface devices in your platform design.

**Table 2. Configurable Devices That Can be Disabled**

| Device | Description                         |

|--------|-------------------------------------|

| PCIE1  | PCI Express Port 1                  |

| PCIE0  | PCI Express Port 0                  |

| SATA1  | Serial ATA Port 1                   |

| SATA0  | Serial ATA Port 0                   |

| GbE2   | Gigabit Ethernet Port 2             |

| GbE1   | Gigabit Ethernet Port 1             |

| GbE0   | Gigabit Ethernet Port 0             |

| USB1   | Universal Serial Bus Port 1         |

| USB0   | Universal Serial Bus Port 0         |

| CAN1   | Controller Area Network Port 1      |

| CAN0   | Controller Area Network Port 0      |

| TDM    | Time Division Multiplex Ports (HSS) |

| SSP    | Synchronous Serial Port             |

## 4.0 IA-32 core Throttling

The EP80579 provides the capability to force the IA-32 core to throttle, as a means to conserve power. The FORCE\_THTL bit in the Processor Control Register (PROC\_CNT) allows the BIOS to force the IA-32 core to throttle, independent of the ACPI software.

When the FORCE\_THTL bit is set in the PROC\_CNT register, the IA-32 core starts throttling, using the throttle ratio defined by the PROCHOT\_DTY field in the PROC\_CNT register. Alternatively, the ACPI software is also used to force throttling by setting both the THTL\_EN and FORCE\_THTL bits in PROC\_CNT register. Under ACPI control, the throttle ratio is defined by the THTL\_DTY field.

The throttling ratios results in stop clock (STOPCLK#) control signal to be set active for a minimum of 12.5% and a maximum of 87.5%. The period is 1024 PCI clocks. Thus, the STOPCLK# signal is active for as little as 128 PCI clocks or as much as 896 PCI clocks depending on the setting of the throttling ratio bits.

**Table 3** shows the throttling control by using FORCE\_THTL bit. Refer to the *Intel® EP80579 Integrated Processor Product Line Datasheet* for additional details on the throttling configuration options.

**Table 3. Throttling Configuration with FORCE\_THTL**

| PROCHOT_DTY Bits[2:0] | Throttle Mode ratio | PCI Clocks (STOPCLK# low) |

|-----------------------|---------------------|---------------------------|

| 000                   | Default (50%)       | 512                       |

| 001                   | 87.5%               | 896                       |

| 010                   | 75.0%               | 768                       |

| 011                   | 62.5%               | 640                       |

| 100                   | 50%                 | 512                       |

| 101                   | 37.5%               | 384                       |

| 110                   | 25%                 | 256                       |

| 111                   | 12.5%               | 128                       |

**Note:** The 3-bit PROCHOT\_DTY field determines the duty cycle of the throttling when the FORCE\_THTL bit is set. The duty cycle indicates the approximate percentage of time the STOPCLK# signal is asserted while in the throttle mode. The STOPCLK# throttle period is 1024 PCICLKs.

Throttling only occurs when the system is in the C0 state. When in the C2, C3, or C4 state, no throttling occurs. Once the PROCHOT\_DTY field is written, subsequent writes have no effect until PLTRST# goes active.

## 4.1

## IA-32 core Throttling Implementation and Effects

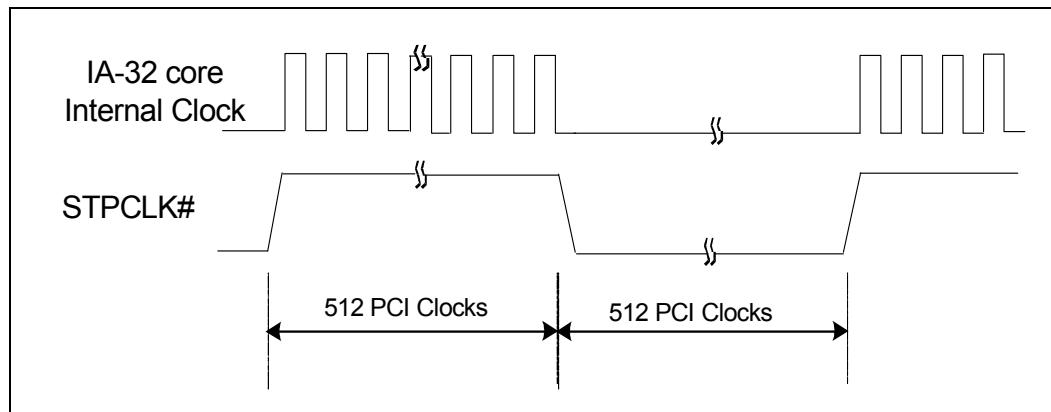

While throttling is enabled, the 'internal stop clock' (STOPCLK#) signal is asserted for some time, and then deasserted for some time. This modulation of the stop clock regulates the aggregate IA-32 core internal clock frequency. The exact times for assertion and deassertion of the internal clock is determined by the Throttle Mode ratios defined in [Table 3](#).

When throttling is forced, the IA-32 core internal clock is limited in the amount of time it runs. For example, by setting the PROCHOT\_DTY bits to '100' (or 50% Duty Cycle), the internal clocks only runs for 50% of the throttling period of 1024 PCI clocks, as shown in [Figure 1](#).

During the time when Stop Clock is asserted (in other words, when the internal clock is not running), there is no code execution. However, interrupts are registered, as is all I/O activity. This is because the interrupt and I/O Controllers are not affected by the assertion of the "Internal Stop Clock".

In the case of an interrupt, this has the effect of extending the time it takes to run the interrupt service routine (ISR). In other words, at 50% throttling it takes an ISR that normally takes 1ms, up to 2ms to execute. These are considerations the developer must take into account when throttling the IA-32 core.

**Figure 1.**

**Clocks Relationship for 50% Throttling Ratio**

## 4.2 Benefits of Throttling

The most significant benefit from throttling is that the overall power consumption of EP80579 is reduced, and thus allows the EP80579 to hit power envelopes that are not achieved otherwise.

### 4.2.1 Throttling Power Savings

[Table 4](#) and [Table 5](#) provide the percentage drop in total power consumption by the EP80579 when throttling is enabled.

[Table 4](#) shows the percentages of total power savings per EP80579 SKU, by throttling the IA-32 core across the throttle ratio spectrum with all interface device units enabled.

[Table 5](#) shows the percentages of total power savings per EP80579 SKU, by throttling the IA-32 core across the throttle ratio spectrum with the various interface units enabled or disabled during the test.

The percentage power savings values in [Table 4](#) and [Table 5](#) are referenced to the Thermal Design Power (TDP) value specifications for the EP80579 SKUs provided in the *Intel® EP80579 Integrated Processor Product Line Datasheet*. The TDP is a system design target associated with the maximum component operating temperature specifications. The TDP values are based on typical DC electrical specification and maximum component temperature for a realistic case application running at maximum utilization.

Both [Table 4](#) and [Table 5](#) indicate that the EP80579 SKU's power saving increases as the throttling ratio increases.

**Note:** It should be noted that the power saving values provided in [Table 4](#) and [Table 5](#) are for informational purposes only. Thermal solutions for EP80579-based platforms must be designed to meet the TDP values specified in the *Intel® EP80579 Integrated Processor Product Line Datasheet* and voltage regulators must be designed to meet specifications in the *Intel® EP80579 Integrated Processor Product Line Platform Design Guide*.

**Table 4. Throttling Power Savings (All Interface Device Units Enabled)**

| EP80579 SKU      |                   | 600 MHz                        | 1066 MHz                       | 1200 MHz                       |

|------------------|-------------------|--------------------------------|--------------------------------|--------------------------------|

| PROCHOT_DTY Bits | Throttle Mode (%) | EP80579 Total Power Saving (%) | EP80579 Total Power Saving (%) | EP80579 Total Power Saving (%) |

| 001              | 87.5              | 21.0                           | 47.6                           | 42.8                           |

| 010              | 75                | 18.8                           | 40.7                           | 37.2                           |

| 011              | 62.5              | 16.3                           | 36.2                           | 32.1                           |

| 100 or 000       | 50                | 13.3                           | 29.4                           | 26.5                           |

| 101              | 37.5              | 9.4                            | 22.8                           | 20.2                           |

| 110              | 25                | 6.7                            | 15.9                           | 15.6                           |

| 111              | 12.5              | 5.0                            | 9.5                            | 9.8                            |

| N/A <sup>1</sup> | 0                 | 0                              | 0                              | 0                              |

1. No throttling active

**Table 5. Throttling Power Savings with Devices Enabled/Disabled**

| EP80579 SKU          |                | 600 MHz SKU           | 1066 MHz SKU                   | 1200 MHz SKU                   |      |

|----------------------|----------------|-----------------------|--------------------------------|--------------------------------|------|

| Device Configuration | PCIE1          | Disabled              |                                |                                |      |

|                      | PCIE0          | Disabled              | <b>Enabled</b>                 |                                |      |

|                      | SATA1          | Disabled <sup>a</sup> |                                |                                |      |

|                      | SATA0          | Disabled              |                                |                                |      |

|                      | GbE2           | Disabled              |                                |                                |      |

|                      | GbE1           | Disabled              | <b>Enabled</b>                 |                                |      |

|                      | GbE0           | <b>Enabled</b>        |                                |                                |      |

|                      | USB1           | <b>Enabled</b>        |                                |                                |      |

|                      | USB0           | <b>Enabled</b>        |                                |                                |      |

|                      | CAN1           | Disabled              |                                |                                |      |

|                      | CAN0           | Disabled              |                                |                                |      |

|                      | TDM            | Disabled              |                                |                                |      |

| SSP                  |                | Disabled              |                                |                                |      |

| PROCHOT_DTY Bits     | FORCE_THTL Bit | Throttle Mode (%)     | EP80579 Total Power Saving (%) | EP80579 Total Power Saving (%) |      |

| 001                  | 1              | 87.5                  | 30.4                           | 53.0                           | 43.8 |

| 010                  | 1              | 75                    | 28.5                           | 46.8                           | 38.3 |

| 011                  | 1              | 62.5                  | 26.3                           | 42.8                           | 33.3 |

| 100 or 000           | 1              | 50                    | 23.7                           | 36.7                           | 27.9 |

| 101                  | 1              | 37.5                  | 20.3                           | 30.8                           | 21.6 |

| 110                  | 1              | 25                    | 17.9                           | 24.7                           | 15.6 |

| 111                  | 1              | 12.5                  | 16.3                           | 18.9                           | 9.8  |

| XXX <sup>1</sup>     | 0 <sup>1</sup> | 0                     | 11.9                           | 10.4                           | 1.8  |

1. The FORCE\_THTL is used to turn on/off throttling. Therefore when FORCE\_THTL is off the PROC\_DTY bits are ignored and throttling is not enabled.

## 5.0 Power Management

The EP80579 is compatible with the [PCI Bus Power Management Interface Specification, Rev. 1.1](#). It is also compatible with [Advanced Configuration and Power Interface \(ACPI\) Specification](#). The EP80579 is designed to operate seamlessly with systems operating under these specifications.

### 5.1 Supported System Power States

The EP80579, like all systems, supports the S0 state. The EP80579 also supports S3 (STR- Suspend to RAM), S4 and S5 (Soft Off).

### 5.2 BIOS Support for Power Management

The EP80579 supports all PCI-to-PMI and PCI Express messaging required to place any subordinate device on any of its PCI Express ports into any of the defined device low power states. Peripherals attached to the PCI segments provided via a PXH component are placed in any of their supported low power states via messaging directed from the EP80579 through the intervening PCI Express hierarchy. BIOS designers for EP80579-based platforms must make allowances to support power-off device states within the PCI Express hierarchy.

## 6.0 Conclusions

The EP80579 architecture provides a flexible mechanism for managing power consumption. Although all the internal units come up enabled out of RESET, the EP80579 component provides BIOS the flexibility to disable those units that are not used by the design.

Additionally, BIOS can be used to configure the IA-32 core to operate at reduced internal clock frequencies for lower data rate applications by utilizing the IA-32 core throttling capability to reduce power consumption.

Finally, BIOS should make provisions to support the power management features provided by the part. All of these features provide the developer with options on how to minimize the overall power consumption of the application.

§ §