# Enabling TMII Hardware on Intel® IXP435 Network Processors

## Application Note

---

*December 2008*

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See [http://www.intel.com/products/processor\\_number](http://www.intel.com/products/processor_number) for details.

The Intel® IXP4XX Product Line of Network Processors may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

This Application Note as well as the software described in it is furnished under license and may only be used or copied in accordance with the terms of the license. The information in this manual is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by Intel Corporation. Intel Corporation assumes no responsibility or liability for any errors or inaccuracies that may appear in this document or any software that may be provided in association with this document.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at <http://www.intel.com>.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino Inside, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, IntelDX2, IntelDX4, IntelSX2, Intel Atom, Intel Atom Inside, Intel Core, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel VliV, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, PDCharm, Pentium, Pentium Inside, skoool, Sound Mark, The Journey Inside, VliV Inside, vPro Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008, Intel Corporation. All Rights Reserved.

## Contents

---

|            |                                           |   |

|------------|-------------------------------------------|---|

| <b>1.0</b> | <b>Introduction</b>                       | 5 |

| 1.1        | Purpose                                   | 5 |

| 1.2        | Intended Audience                         | 5 |

| 1.3        | Acronyms                                  | 5 |

| 1.4        | Related Documents                         | 5 |

| <b>2.0</b> | <b>Flexcomm® CRONUS1000 Block Diagram</b> | 6 |

| <b>3.0</b> | <b>Hardware Reference Block Diagram</b>   | 6 |

| <b>4.0</b> | <b>Software Enabling</b>                  | 7 |

## Figures

|   |                                                                                                    |   |

|---|----------------------------------------------------------------------------------------------------|---|

| 1 | Block Diagram of Flexcomm® CRONUS1000 Hardware Platform                                            | 6 |

| 2 | TMII Connection between the Intel® IXP435 Network Processor and TANTOS-3G® Switch (from Infineon®) | 7 |

## Revision History

---

| Date          | Revision | Description                 |

|---------------|----------|-----------------------------|

| December 2008 | 001      | Initial release of document |

§ §

## 1.0 Introduction

The TMII (Turbo Media Independent Interface) also named as Turbo MII is used to increase the MII clock from 25 MHz to 50 MHz. The purpose of the Turbo MII is to enhance LAN throughput performance by doubling the MII clock rate.

The complete solution has been validated on the hardware platform of Flexcomm\* called as CRONUS1000 using the Intel® IXP435 Network Processor.

### 1.1 Purpose

The objective of this application note is to illustrate the hardware block diagram that has been validated while working on the Flexcomm CRONUS1000 using the Intel® IXP435 Network Processor.

The following sections explain the block diagram of the TMII construction.

*Note:* The Flexcomm CRONUS1000 has been validated using the Intel® IXP400 Software v3.0.1 only. The hardware guide below is based on the TANTOS-3G\* Switch (PSB6973) from Infineon\*.

### 1.2 Intended Audience

This application note is targeted for those who intend to enhance the throughput performance of their system using the TANTOS-3G switch (PSB6973).

### 1.3 Acronyms

| Acronym | Description                                    |

|---------|------------------------------------------------|

| MII     | Media Independent Interface                    |

| TMII    | Turbo MII or Turbo Media Independent Interface |

### 1.4 Related Documents

| Document Title                                                             | Document Number |

|----------------------------------------------------------------------------|-----------------|

| <i>Intel® IXP43X Product Line of Network Processors Developer's Manual</i> | 316843          |

| <i>Intel® IXP400 Software Programmer's Guide v3.0</i>                      | 252539          |

| <i>Intel® IXP400 Software Release 3.0 Software Release Notes</i>           | -               |

| <i>Intel® IXP400 Software Release 3.0.1 Readme</i>                         | -               |

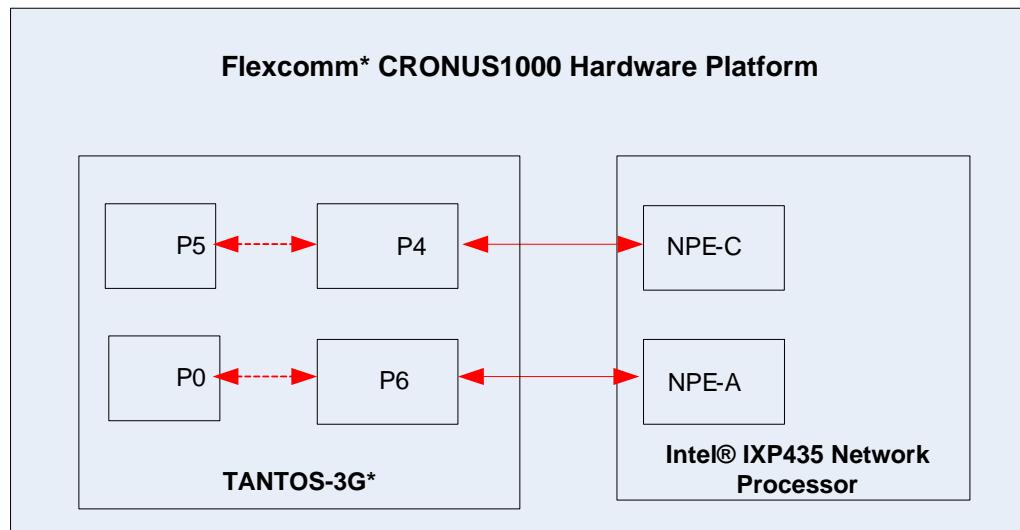

## 2.0 Flexcomm® CRONUS1000 Block Diagram

Figure 1 shows the block diagram of the Flexcomm CRONUS1000.

The solid lines show the connection between the IXP435 network processor and TANTOS-3G switch. The dotted lines show the internal VLAN connection of individual ports in the TANTOS-3G switch. The VLAN connections can be configured by the software.

**Figure 1. Block Diagram of Flexcomm® CRONUS1000 Hardware Platform**

## 3.0 Hardware Reference Block Diagram

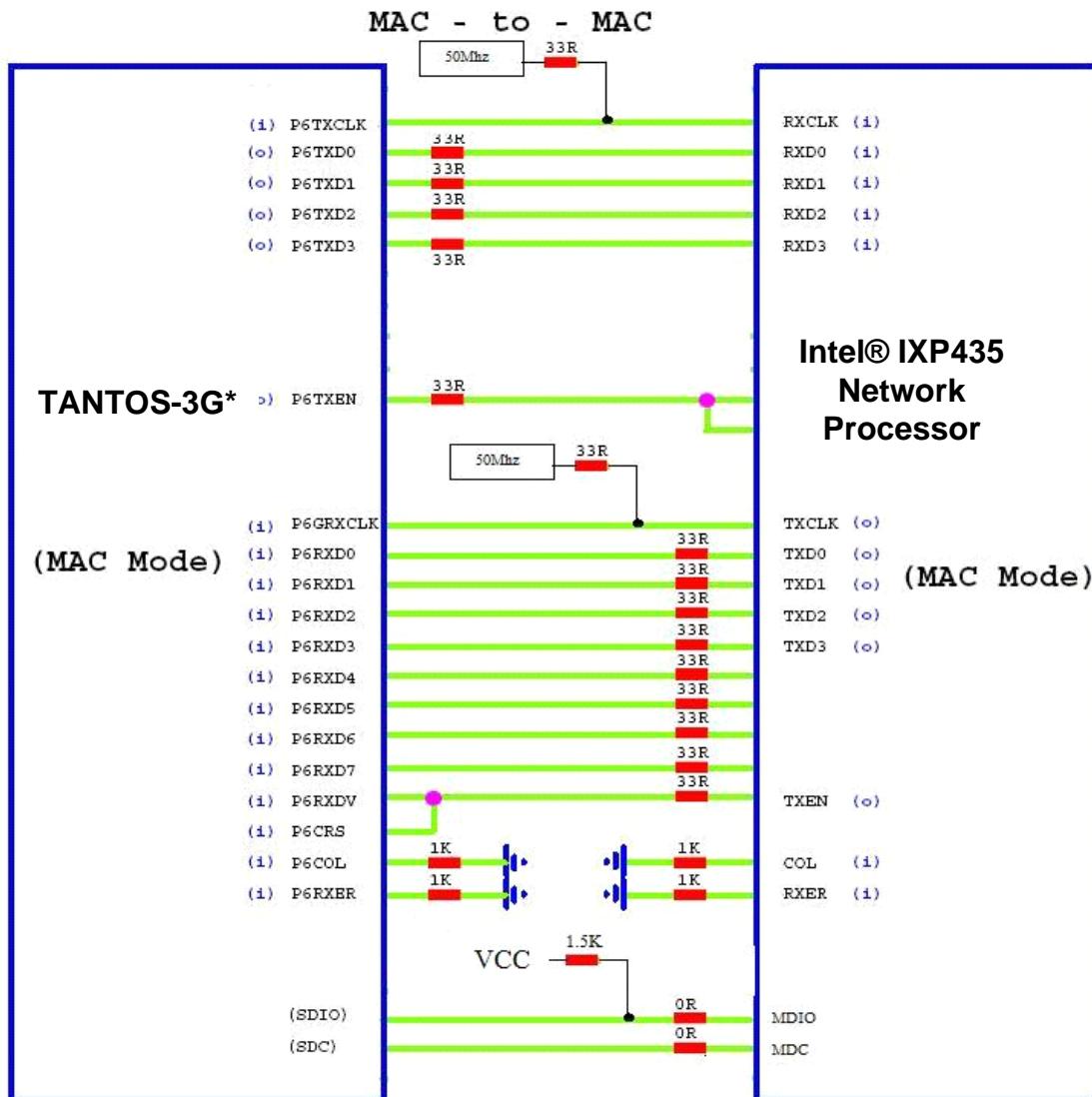

Figure 2 shows the connection between the IXP435 network processor and TANTOS-3G switch.

The data, clock, and control signals should be terminated with a 33 ohm series resistor for drive strength adjustment and must be placed very close to the driver. The Collision signal and RX\_Error signal are not used in the implementation, and therefore should be tied to the ground.

A 50 MHz oscillator with 50 ppm is recommended. It must be placed at the center of the RXCLK / TXCLK trace (in between the IXP435 network processor and TANTOS-3G) to ensure same clock propagation to each device. Place a 33 ohm series resistor close to the oscillator output pin. This value should be adjusted to optimize signal integrity depending on the oscillator drive strength.

It is recommended to length match (ball to ball) the DATA, and TXCLK/RXCLK traces within 400 mils.

If you use a 5 mil trace width, ensure that the trace separation of TX data, RX data, TXCLK, and RXCLK is at least 10 mil. Avoid parallelism on these signal traces. Trace impedance of 50-60 ohm should be used.

The MDIO/MDC management pins on the IXP435 network processor should be connected to the SDIO/SDC pins on the TANTOS-3G switch. A pull up resistor of 1.5 Kohm to VCC (3.3V) is required on the MDIO pin.

**Figure 2. TMII Connection between the Intel® IXP435 Network Processor and TANTOS-3G\* Switch (from Infineon\*)**

## 4.0 Software Enabling

The enabling TMII software for the Flexcomm CRONUS1000 is available on the [Intel Developer web site](#).

The following software packages are needed:

- Intel® IXP400 Software v3.0

- Intel® IXP400 Software v3.0.1 patch

The required software components are:

- Hardware access library

- NPE microcode

- Ethernet Device Driver

Refer to the *Intel® IXP400 Software v3.0.1 Readme* available on the [Intel Developer web site](#) for further information.

§ §