# Simulation Quick-Start for ModelSim\* - Intel® FPGA Edition

Intel® Quartus® Prime Standard Edition

Updated for Intel® Quartus® Prime Design Suite: 18.0

UG-01102 | 2018.05.08 Latest document on the web: PDF | HTML

# **Contents**

| 1.1. Open the Example Design                                 | 4 |

|--------------------------------------------------------------|---|

| 1.2. Specify EDA Tool Settings                               |   |

| 1.3. Launch Simulation from the Intel Quartus Prime Software | 6 |

| 1.4. View Signal Waveforms                                   | 7 |

| 1.5. Add Signals to the Simulation                           |   |

| 1.6. Rerun Simulation                                        | 9 |

| 1.7. Modify the Simulation Testbench                         | 9 |

| 1.8. (Optional) Run Simulation at Command Line               |   |

# 1. Simulation Quick-Start for ModelSim\* - Intel® FPGA Edition (Intel® Quartus® Prime Standard Edition)

This document demonstrates how to simulate an Intel® Quartus® Prime Standard Edition design in the ModelSim\*-Intel FPGA Edition simulator. Design simulation verifies your design before device programming. The Intel Quartus Prime software generates simulation files for supported EDA simulators during design compilation.

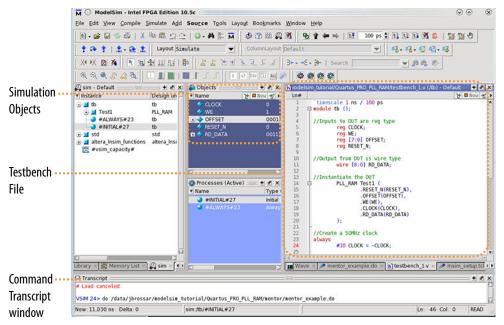

#### Figure 1. ModelSim-Intel FPGA Edition

Design simulation involves generating setup scripts for your simulator, compiling simulation models, running the simulation, and viewing the results. The following steps describe this flow in detail:

- Open the Example Design on page 4

- 2. Specify EDA Tool Settings on page 4

- 3. Launch Simulation from the Intel Quartus Prime Software on page 6

- 4. View Signal Waveforms on page 7

- 5. Add Signals to the Simulation on page 8

- 6. Rerun Simulation on page 9

- 7. Modify the Simulation Testbench on page 9

- 8. (Optional) Run Simulation at Command Line on page 10

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2008 Registered

# 1.1. Open the Example Design

The PLL\_RAM example design includes Intel FPGA IP cores to demonstrate the basic simulation flow. Download the example design files and open the project in the Intel Quartus Prime software.

Note:

This Quick-Start requires a basic understanding of hardware description language syntax and the Intel Quartus Prime design flow, as the Intel Quartus Prime Standard Edition Foundation Online Training describes.

- Download and unzip the Quartus\_STD\_LITE\_PLL\_RAM.zip design example from the Altera wiki.

- 2. Launch the Intel Quartus Prime Standard Edition software.

- To open the example design project, click File ➤ Open Project, select the pll\_ram.qpf project file, and then click OK.

# 1.2. Specify EDA Tool Settings

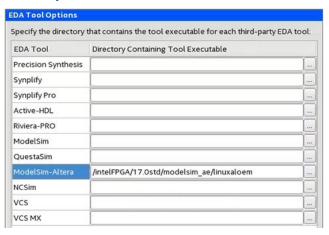

Specify EDA tool settings to generate simulation files for supported simulators.

- 1. In the Intel Quartus Prime software, click **Tools ➤ Options ➤ EDA Tool Options**.

- To specify the location of your simulator for integration with the Intel Quartus Prime software, click Tools ➤ Options ➤ EDA Tool Options.

#### Figure 2. EDA Tool Options

- 3. In **ModelSim-Altera**, enter the ModelSim Intel FPGA Edition executable path. Select the appropriate ModelSim Intel FPGA Edition executable, rather than any other supported ModelSim software.

- /intelFPGA\_lite/<version>/modelsim\_ase/win32aloem (Lite)

- /intelFPGA/<version>/modelsim\_ase/win32aloem (Standard)

- 4. Click Assignments ➤ Settings ➤ EDA Tool Settings ➤ Simulation.

- 5. On the **Simulation** page, specify the following values for the options:

# 1. Simulation Quick-Start for ModelSim\* - Intel® FPGA Edition (Intel® Quartus® Prime Standard Edition)

UG-01102 | 2018.05.08

| Option                                                    | Value            |

|-----------------------------------------------------------|------------------|

| Tool name                                                 | ModelSim-Altera  |

| Run gate-level simulation automatically after compilation | Disable checkbox |

| Format for output netlist                                 | Verilog HDL      |

| Map illegal VHDL characters                               | Disable checkbox |

| Enable glitch filtering                                   | Disable checkbox |

| Generate Value Change Dump (VCD) file script              | Disable checkbox |

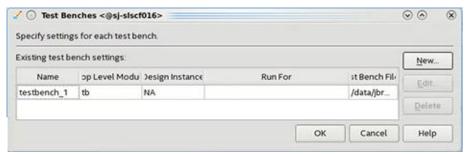

Figure 3. Simulation Options

- 6. Under **NativeLink settings**, select the **Compile test bench** option, and then click the **Test Benches** button.

- Click New. Specify testbench\_1 as the Test bench name, and tb as the Top level module in test bench.

- 8. Under **Test bench and simulation files**, enter or select the testbench\_1.v file, click **Add**, and then click **OK**. The **Test Benches** dialog box displays the properties of the testbenches in your project.

#### Figure 4. Test Benches Dialog Box

9. In the **Test Benches** dialog box, click **OK**. In the **Settings** dialog box, click **OK**.

#### 1.3. Launch Simulation from the Intel Quartus Prime Software

To generate and run the ModelSim-Intel FPGA Edition automation script from within the Intel Quartus Prime software, follow these steps:

- To compile the design and generate the .do file, click Processing ➤ Start Compilation. The Messages window indicates when compilation is complete.

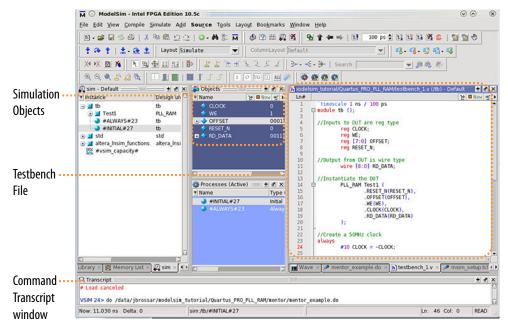

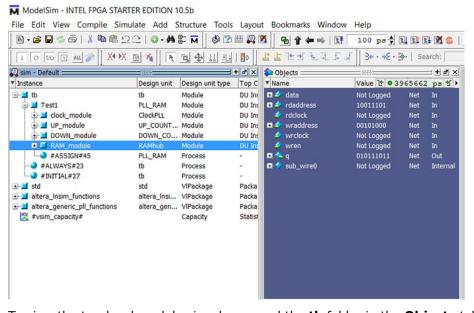

- Click Tools > Run Simulation Tool > RTL Simulation. The Intel Quartus Prime software launches the ModelSim Intel FPGA Edition simulator and simulates the testbench\_1.v file, according to your specifications in the Simulation settings. The ModelSim Intel FPGA Edition GUI organizes the elements of your simulation in separate windows. The right side of the GUI displays the testbench\_1.v file that defines the simulation.

Figure 5. ModelSim - Intel FPGA Edition GUI

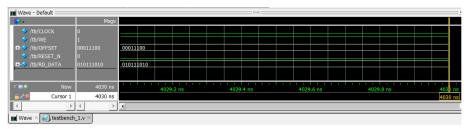

# 1.4. View Signal Waveforms

Follow these steps to view signals in the testbench\_1.v simulation waveform:

Click the Wave window. The simulation waveform ends at 4030 ns, as the testbench specifies. The Wave window lists the CLOCK, WE, OFFSET, RESET\_N, and RD DATA signals.

#### Figure 6. ModelSim - Intel FPGA Edition Wave Window

To view the signals in the top-level pll\_ram.v design, click the Sim tab. The Sim window synchronizes with the Objects window.

#### Figure 7. ModelSim - Intel FPGA Edition Sim and Objects Windows

- To view the top-level module signals, expand the tb folder in the Objects tab.

Similarly, expand the Test1 folder. The Objects window displays the UP\_module,

DOWN\_module, PLL\_module, and RAM\_module signals.

- 4. In the **Sim** window, click a module under **Test1** to display the module's signals in the **Objects** window.

- 5. View the simulation library files in the **Library** window.

Figure 8. ModelSim - Intel FPGA Edition Library Window

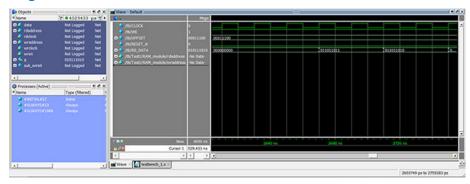

# 1.5. Add Signals to the Simulation

The CLOCK, WE, OFFSET, RESET\_N, and RD\_DATA signals automatically appear in the **Wave** window because the top-level design defines these I/O. In addition, you can optionally add internal signals to the simulation.

- 1. In the **Objects** window, locate the UP\_module, DOWN\_module, PLL\_module, and RAM module modules.

- In the **Objects** window, select **RAM\_module**. The module's inputs and outputs display.

#### Figure 9. Add Signals To Wave Window

- 3. To add the internal signals between the down-counter and dual-port RAM module, right-click **rdaddress** and then click **Add Wave**.

- 4. To add the internal signals between the up-counter and dual-port RAM module, right-click **wraddress** and then click **Add Wave**. Alternatively, you can drag and drop these signals from the **Objects** window to the **Wave** window.

- To generate the waveforms for the new signals you add, click Simulate ➤ Run ➤ Continue.

#### 1.6. Rerun Simulation

You must rerun the simulation if you make changes to the simulation setup, such as adding signals to the **Wave** window, or modifying the  $testbench_1.v$  file. Follow these steps to rerun simulation:

- 1. In the ModelSim Intel FPGA Edition simulator, click **Simulate** ➤ **Restart**. Retain the default options and click **OK**. These options clear the waveforms and restart the simulation time, while retaining the necessary signals and settings.

- 2. Click **Simulate** ➤ **Run** ➤ **Run** -all. The testbench\_1.v file simulates according to the testbench specifications. To continue simulation, click **Simulate** ➤ **Run** ➤ **Continue**. This command continues the simulation until you click the **Stop** button.

# 1.7. Modify the Simulation Testbench

The testbench\_1.v example testbench tests only a specific set of conditions and test cases. You can manually edit the testbench\_1.v file in the ModelSim - Intel FPGA Edition simulator to test other cases and conditions:

- 1. Open the testbench\_1.v file in the ModelSim Intel FPGA Edition simulator.

- 2. Right-click in the testbench\_1.v file to confirm that the file is not set to **Read** Only.

- 3. Enter and save any additional testbench parameters in the testbench\_1.v file.

- To generate the waveforms for a testbench that you modify, click Simulate ➤ Restart.

- 5. Click Simulate ➤ Run ➤ Run -all.

# 1.8. (Optional) Run Simulation at Command Line

Follow these steps to generate a .do file that runs the ModelSim - Intel FPGA Edition simulator from the command line.

- To open the example design project, click File ➤ Open Project, select the pll\_ram.qpf project file, and then click OK. The project opens in the Intel Quartus Prime GUI.

- 2. Click Assignments ➤ Settings ➤ EDA Tool Settings ➤ Simulation ➤ More NativeLink Settings.

- 3. Enable Generate third-party EDA tool command scripts without running the EDA tool, and then click OK. In the Settings dialog box, click OK.

- 4. To compile the design and generate the .do file, click **Processing ➤ Start Compilation**.

- 5. Click Tools ➤ Run Simulation Tool ➤ RTL Simulation. The Intel Quartus Prime software generates the PLL\_RAM\_run\_msim\_rtl\_verilog\_do file that defines the compilation and simulation instructions for the ModelSim Intel FPGA Edition simulator in the /simulation/modelsim/ directory in your project.

- 6. In the ModelSim Intel FPGA Edition software, open the PLL\_RAM\_run\_msim\_rtl\_verilog.do file. This file contains all the commands and library inclusions the simulation requires.

- In the Transcript window (View > Transcript), type the following command and press Enter:

do PLL\_RAM\_run\_msim\_rtl\_verilog\_do

The ModelSim - Intel FPGA Edition simulator runs compilation and simulation, as the .do file specifies.

# 2. Simulation Quick-Start for ModelSim - Intel FPGA Edition (Intel Quartus Prime Standard Edition) Revision History

| Document Version | Intel Quartus<br>Prime Version | Changes                                                                |

|------------------|--------------------------------|------------------------------------------------------------------------|

| 2018.05.07       | 18.0                           | Removed unecessary step from Run Simulation at Command Line procedure. |

| 2017.07.15       | 17.1                           | Initial release.                                                       |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2008 Registered