# Turbo Intel® FPGA IP User Guide

Updated for Intel® Quartus® Prime Design Suite: 20.4

IP Version: 20.4.0

UG-TURBO | 2021.03.28 Latest document on the web: PDF | HTML

# **Contents**

| 1. About the Turbo Intel® FPGA IP                                  | 3  |

|--------------------------------------------------------------------|----|

| 1.1. Turbo Intel FPGA IP Features                                  | 4  |

| 1.2. Turbo Intel FPGA IP Device Family Support                     | 4  |

| 1.3. Turbo IP Core Performance and Resource Utilization            | 6  |

| 1.4. Turbo Code Licensing Disclaimer                               | 7  |

| 1.5. Release Information                                           | 7  |

| 2. Getting Started with the Turbo Intel FPGA IP                    | 9  |

| 2.1. Installing and Licensing Intel FPGA IP Cores                  | g  |

| 2.1.1. Intel FPGA IP Evaluation Mode                               | 9  |

| 2.1.2. Turbo IP Timeout Behavior                                   | 12 |

| 2.2. IP Catalog and Parameter Editor                               | 12 |

| 2.3. Specifying the IP Core Parameters and Options                 |    |

| 2.3.1. IP Core Generation Output (Intel Quartus Prime Pro Edition) |    |

| 2.4. Simulating Intel FPGA IP Cores                                |    |

| 2.5. Simulating the Turbo IP with the RTL Simulator                |    |

| 2.6. Simulating the Turbo IP with the C-Model                      |    |

| 2.6.1. Encoder Simulation                                          |    |

| 2.6.2. Decoder Simulation                                          |    |

| 2.7. Simulating the Turbo IP with MATLAB                           | 20 |

| 3. Parameter Settings                                              | 21 |

| 4. Turbo Intel FPGA IP Functional Description                      | 22 |

| 4.1. Turbo Encoder                                                 | 22 |

| 4.1.1. Turbo Encoder Data Format                                   |    |

| 4.1.2. Turbo Encoder Latency Calculation                           | 24 |

| 4.2. Turbo Decoder                                                 |    |

| 4.2.1. Turbo Decoder Data Format                                   |    |

| 4.2.2. CRC24A or CRC24B Early Termination                          |    |

| 4.2.3. Decoder Latency Calculation                                 |    |

| 4.2.4. Error Correction Performance for the Turbo Decoder          |    |

| 4.3. Turbo IP Core Interfaces and Signals                          |    |

| 4.3.1. Packet Format Errors                                        |    |

| 4.4. Turbo Throughput                                              | 33 |

| A. Turbo IP Core User Guide Document Archives                      | 34 |

| 6. Desument Devision History for Turke Intel EDCA ID Hear Cuide    | 25 |

# 1. About the Turbo Intel® FPGA IP

The Turbo Intel® FPGA IP implements Turbo codes that is compliant with 3rd Generation Partnership Project (3GPP) LTE/LET-A and UMTS specification for integration in your wireless design. Forward-error correction (FEC) channel codes commonly improve the energy efficiency of wireless communication systems.

Turbo codes are suitable for 3G and 4G mobile communications and satellite communications to help transmitting and receiving messages over noisy channels. You can also use Turbo codes in other applications that require reliable information transfer over bandwidth- or latency-constrained communication links in the presence of data corrupting noise.

### **Related Information**

- 3GPP TS 36.212 Version 15.2.1 Release 15

- 3GPP TS 25.212 Version 14.0.0 Release 14

### 1.1. Turbo Intel FPGA IP Features

The Turbo Intel FPGA IP offers the following features:

- General features:

- 3GPP LTE compliant with support for block sizes from 40 to 6,144.

- 3GPP UMTS compliant with support for block sizes from 40 to 5,114.

- C/MATLAB bit-accurate models for performance simulation or RTL test vector generation.

- Decoder features:

- Run time parameters for interleaver size and number of iterations.

- Early termination with cyclical redundancy check (CRC).

- Compile time parameters for the number of parallel engines, input precision.

- Uses MaxLogMAP decoding algorithm.

- Double-buffering for reduced latency real-time applications, which allows the decoder to receive data while processing the previous data block at compile time.

- No external memory required.

- Encoder features:

- Run-time selectable interleaver block sizes.

- Compile time parameters for standard (LTE or UMTS) and parallel encoding engines (1, 4 or 8) for high throughput and low latency.

- Code rate 1/3 only. Use external rate matching for other code rates.

- Double-buffering allows the encoder to receive data while processing the previous data block at compile time.

# 1.2. Turbo Intel FPGA IP Device Family Support

Intel offers the following device support levels for Intel FPGA IP cores:

- Advance support—the IP is available for simulation and compilation for this device family. FPGA programming file (.pof) support is not available for Quartus Prime Pro Stratix 10 Edition Beta software and as such IP timing closure cannot be guaranteed. Timing models include initial engineering estimates of delays based on early post-layout information. The timing models are subject to change as silicon testing improves the correlation between the actual silicon and the timing models. You can use this IP core for system architecture and resource utilization studies, simulation, pinout, system latency assessments, basic timing assessments (pipeline budgeting), and I/O transfer strategy (data-path width, burst depth, I/O standards tradeoffs).

- Preliminary support—Intel verifies the IP with preliminary timing models for this

device family. The IP core meets all functional requirements, but might still be

undergoing timing analysis for the device family. You can use it in production

designs with caution.

- Final support—Intel verifies the IP with final timing models for this device family. The IP core meets all functional and timing requirements for the device family. You can use it in production designs.

# **Table 1.** Turbo IP Device Family Support

| Device Family                  | Support    |

|--------------------------------|------------|

| Intel Agilex <sup>™</sup>      | Advance    |

| Intel Stratix <sup>®</sup> 10  | Final      |

| Intel Arria® 10                | Final      |

| Intel Cyclone® 10              | Final      |

| Stratix V                      | Final      |

| Arria V                        | Final      |

| Cyclone V                      | Final      |

| Stratix IV GT                  | Final      |

| Stratix IV GX/E                | Final      |

| Cyclone IV                     | Final      |

| Arria II GX                    | Final      |

| Arria II GZ                    | Final      |

| Intel MAX <sup>®</sup> 10 FPGA | Final      |

| Other device families          | No support |

### 1.3. Turbo IP Core Performance and Resource Utilization

### **Table 2.** Performance and Resource Utilization

Typical expected performance for a Turbo IP Core using the Quartus Prime software with the Intel Agilex (AGFA014R24A2E2VR0), Intel Stratix 10 (1SG280HU2F50E2VG), and Intel Arria 10 (10AT115S1F45E1SG) devices.

| Device           | Speed<br>Grade |         | Parameters |               | ALM     | Memory |      | fMAX <sup>(1)</sup><br>(MHz) |        |   |     |     |

|------------------|----------------|---------|------------|---------------|---------|--------|------|------------------------------|--------|---|-----|-----|

|                  | Codec<br>Type  |         | Standard   | Input<br>Bits | Engines |        | M20K | M10K                         | (MH2)  |   |     |     |

|                  |                |         |            | -             | 1       | 529    | 8    | -                            | 425    |   |     |     |

|                  |                |         | 1.75       | -             | 4       | 900    | 10   | -                            | 425    |   |     |     |

|                  |                | Encoder | LTE        | -             | 8       | 1.4K   | 19   | -                            | 425    |   |     |     |

|                  |                |         |            | -             | -       | 529    | 8    | -                            | 425    |   |     |     |

|                  |                |         | UMTS       | -             | 1       | 1.1K   | 9    | -                            | 432    |   |     |     |

|                  |                |         |            | 6             | 8       | 12.8K  | 27   | -                            | 414    |   |     |     |

| Intel Agilex     | 2              |         | LTE        | 8             | 8       | 15.2K  | 32   | -                            | 411    |   |     |     |

|                  |                |         | LIL        | 6             | 16      | 23.4K  | 34   | -                            | 383    |   |     |     |

|                  |                | Decoder |            | 8             | 16      | 28K    | 40   | -                            | 365    |   |     |     |

|                  |                | Decoder |            | 6             | 2       | 4.9K   | 80   | -                            | 303    |   |     |     |

|                  |                |         | UMTS       | 8             | 2       | 5.5K   | 90   | -                            | 295    |   |     |     |

|                  |                |         |            | 6             | 4       | 7.2K   | 92   | -                            | 304    |   |     |     |

|                  |                |         |            |               |         | 8      | 4    | 8.1K                         | 97     | - | 286 |     |

|                  |                |         |            |               |         |        | -    | 1                            | 528    | 8 | -   | 405 |

|                  |                |         | LTE        | -             | 4       | 987    | 10   | -                            | 411    |   |     |     |

|                  |                | Encoder |            | -             | 8       | 1.4K   | 19   | -                            | 381    |   |     |     |

|                  |                |         | UMTS       | -             | 1       | 1.1K   | 9    | -                            | 330    |   |     |     |

|                  |                |         | UMIS       | -             | 1       | 1.1K   | 9    | -                            | 315    |   |     |     |

|                  |                |         |            | 6             | 8       | 12.7K  | 27   | -                            | 313    |   |     |     |

| Intel Stratix 10 | 2              |         |            | 8             | 8       | 15.2K  | 32   | -                            | 313    |   |     |     |

|                  |                |         | LTE        | 6             | 16      | 23.2K  | 34   | -                            | 292    |   |     |     |

|                  |                | Decoder |            | 8             | 16      | 27.8K  | 40   | -                            | 271    |   |     |     |

|                  |                | Decoder |            | 6             | 2       | 4.8K   | 80   | -                            | 239    |   |     |     |

|                  |                |         | UMTS       | 8             | 2       | 5.5K   | 90   | -                            | 230    |   |     |     |

|                  |                |         | כוויוט     | 6             | 4       | 7.1K   | 92   | -                            | 239    |   |     |     |

| <u> </u>         |                |         |            | 8             | 4       | 8.1K   | 97   | -                            | 225    |   |     |     |

|                  |                |         |            |               |         |        |      | con                          | tinued |   |     |     |

$<sup>^{(1)}\,</sup>$  The table shows  $f_{MAX}$  frequency reduced by 15%. The actual average is  $f_{MAX}$  x 1.15.

| Device         | Speed                     |               | Paramet  | ers           |         | ALM   | Memory |      | fMAX <sup>(1)</sup> |     |

|----------------|---------------------------|---------------|----------|---------------|---------|-------|--------|------|---------------------|-----|

|                | Grade                     | Codec<br>Type | Standard | Input<br>Bits | Engines |       | M20K   | M10K | (MHz)               |     |

|                |                           |               |          | -             | 1       | 476   | 2      | -    | 425                 |     |

|                |                           |               | LTE      | -             | 4       | 902   | 10     | -    | 371                 |     |

|                | Intel Arria 10 1  Decoder | Encoder       |          | -             | 8       | 1.4K  | 10     | -    | 371                 |     |

|                |                           |               | UMTS     | -             | 1       | 1K    | 4      | -    | 304                 |     |

|                |                           | Decoder —     |          | 6             | 8       | 11K   | 27     | -    | 323                 |     |

| Total Assis 10 |                           |               |          | LTE           | 8       | 8     | 13K    | 32   | -                   | 331 |

| Intel Arria 10 |                           |               |          |               | 6       | 16    | 19.9K  | 34   | -                   | 311 |

|                |                           |               |          | 8             | 16      | 23.8K | 40     | -    | 298                 |     |

|                |                           |               | UMTS     | 6             | 2       | 4.7K  | 71     | -    | 228                 |     |

|                |                           |               |          | 8             | 2       | 5.5K  | 81     | -    | 213                 |     |

|                |                           |               |          | UMIS          | 6       | 4     | 7.4K   | 73   | -                   | 225 |

|                |                           | 8             | 4        | 8.4K          | 78      | -     | 208    |      |                     |     |

# 1.4. Turbo Code Licensing Disclaimer

France Telecommunication, for itself and certain other parties, claims certain intellectual property rights covering Turbo Codes technology, and has decided to license these rights under a licensing program called the Turbo Codes Licensing Program. Supply of this IP core does not convey a license nor imply any right to use any Turbo Codes patents owned by France Telecommunication, TDF or GET. For information about the Turbo Codes Licensing Program, contact France Telecommunication at the following address:

France Telecommunication R&D

VAT/TURBOCODES

38, rue du Général Leclerc

92794 Issy Moulineaux

Cedex 9

France

### 1.5. Release Information

Intel FPGA IP versions match the Intel Quartus® Prime Design Suite software versions until v19.1. Starting in Intel Quartus Prime Design Suite software version 19.2, Intel FPGA IP has a new versioning scheme.

<sup>(1)</sup> The table shows  $f_{MAX}$  frequency reduced by 15%. The actual average is  $f_{MAX}$  x 1.15.

The Intel FPGA IP version (X.Y.Z) number can change with each Intel Quartus Prime software version. A change in:

- X indicates a major revision of the IP. If you update the Intel Quartus Prime software, you must regenerate the IP.

- Y indicates the IP includes new features. Regenerate your IP to include these new features.

- Z indicates the IP includes minor changes. Regenerate your IP to include these changes.

### **Table 3.** Turbo Intel FPGA IP Release Information

| Item                        | Description          |

|-----------------------------|----------------------|

| Intel Quartus Prime Version | 20.4                 |

| IP Version                  | 20.4.0               |

| Release Date                | 2020.12.14           |

| Ordering Code               | IP-TURBO (IPR-TURBO) |

### **Related Information**

- Turbo IP Core Release Notes

- Errata for Turbo IP core in the Knowledge Base

# 2. Getting Started with the Turbo Intel FPGA IP

# 2.1. Installing and Licensing Intel FPGA IP Cores

The Intel Quartus Prime software installation includes the Intel FPGA IP library. This library provides many useful IP cores for your production use without the need for an additional license. Some Intel FPGA IP cores require purchase of a separate license for production use. The Intel FPGA IP Evaluation Mode allows you to evaluate these licensed Intel FPGA IP cores in simulation and hardware, before deciding to purchase a full production IP core license. You only need to purchase a full production license for licensed Intel IP cores after you complete hardware testing and are ready to use the IP in production.

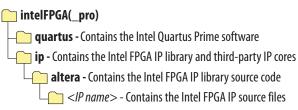

The Intel Quartus Prime software installs IP cores in the following locations by default:

### Figure 1. IP Core Installation Path

### Table 4. IP Core Installation Locations

| Location                                                               | Software                                | Platform |

|------------------------------------------------------------------------|-----------------------------------------|----------|

| <pre><drive>:\intelFPGA_pro\quartus\ip\altera</drive></pre>            | Intel Quartus Prime Pro Edition         | Windows* |

| <pre><drive>:\intelFPGA\quartus\ip\altera</drive></pre>                | Intel Quartus Prime Standard<br>Edition | Windows  |

| <pre><home directory="">:/intelFPGA_pro/quartus/ip/altera</home></pre> | Intel Quartus Prime Pro Edition         | Linux*   |

| <pre><home directory="">:/intelFPGA/quartus/ip/altera</home></pre>     | Intel Quartus Prime Standard<br>Edition | Linux    |

*Note:* The Intel Quartus Prime software does not support spaces in the installation path.

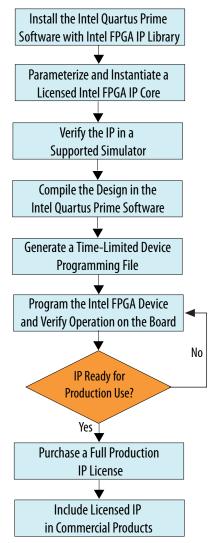

### 2.1.1. Intel FPGA IP Evaluation Mode

The free Intel FPGA IP Evaluation Mode allows you to evaluate licensed Intel FPGA IP cores in simulation and hardware before purchase. Intel FPGA IP Evaluation Mode supports the following evaluations without additional license:

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, eASIC, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

- Simulate the behavior of a licensed Intel FPGA IP core in your system.

- Verify the functionality, size, and speed of the IP core quickly and easily.

- Generate time-limited device programming files for designs that include IP cores.

- Program a device with your IP core and verify your design in hardware.

Intel FPGA IP Evaluation Mode supports the following operation modes:

- **Tethered**—Allows running the design containing the licensed Intel FPGA IP indefinitely with a connection between your board and the host computer. Tethered mode requires a serial joint test action group (JTAG) cable connected between the JTAG port on your board and the host computer, which is running the Intel Quartus Prime Programmer for the duration of the hardware evaluation period. The Programmer only requires a minimum installation of the Intel Quartus Prime software, and requires no Intel Quartus Prime license. The host computer controls the evaluation time by sending a periodic signal to the device via the JTAG port. If all licensed IP cores in the design support tethered mode, the evaluation time runs until any IP core evaluation expires. If all of the IP cores support unlimited evaluation time, the device does not time-out.

- **Untethered**—Allows running the design containing the licensed IP for a limited time. The IP core reverts to untethered mode if the device disconnects from the host computer running the Intel Quartus Prime software. The IP core also reverts to untethered mode if any other licensed IP core in the design does not support tethered mode.

When the evaluation time expires for any licensed Intel FPGA IP in the design, the design stops functioning. All IP cores that use the Intel FPGA IP Evaluation Mode time out simultaneously when any IP core in the design times out. When the evaluation time expires, you must reprogram the FPGA device before continuing hardware verification. To extend use of the IP core for production, purchase a full production license for the IP core.

You must purchase the license and generate a full production license key before you can generate an unrestricted device programming file. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (roject name>\_time\_limited.sof) that expires at the time limit.

Figure 2. Intel FPGA IP Evaluation Mode Flow

Note: Refer to each IP core's user guide for parameterization steps and implementation details.

Intel licenses IP cores on a per-seat, perpetual basis. The license fee includes first-year maintenance and support. You must renew the maintenance contract to receive updates, bug fixes, and technical support beyond the first year. You must purchase a full production license for Intel FPGA IP cores that require a production license, before generating programming files that you may use for an unlimited time. During Intel FPGA IP Evaluation Mode, the Compiler only generates a time-limited device programming file (project name>\_time\_limited.sof) that expires at the time limit. To obtain your production license keys, visit the Self-Service Licensing Center.

The Intel FPGA Software License Agreements govern the installation and use of licensed IP cores, the Intel Quartus Prime design software, and all unlicensed IP cores.

#### **Related Information**

- Intel FPGA Licensing Support Center

- Introduction to Intel FPGA Software Installation and Licensing

### 2.1.2. Turbo IP Timeout Behavior

All IP cores in a device time out simultaneously when the most restrictive evaluation time is reached. If a design has more than one IP core, the time-out behavior of the other IP cores may mask the time-out behavior of a specific IP core.

For IP cores, the untethered time-out is 1 hour; the tethered time-out value is indefinite. Your design stops working after the hardware evaluation time expires. The Quartus Prime software uses Intel FPGA IP Evaluation Mode Files (.ocp) in your project directory to identify your use of the Intel FPGA IP Evaluation Mode evaluation program. After you activate the feature, do not delete these files..When the evaluation time expires, the data output port  $reset_n$  goes low, which keeps the IP core permanently in its reset state.

### **Related Information**

AN 320: OpenCore Plus Evaluation of Megafunctions

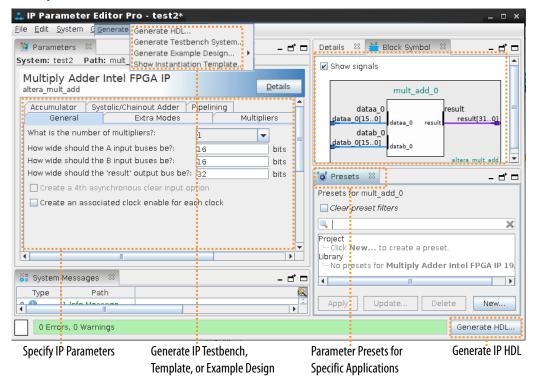

### 2.2. IP Catalog and Parameter Editor

The IP Catalog displays the IP cores available for your project, including Intel FPGA IP and other IP that you add to the IP Catalog search path. Use the following features of the IP Catalog to locate and customize an IP core:

- Filter IP Catalog to Show IP for active device family or Show IP for all device families. If you have no project open, select the Device Family in IP Catalog.

- Type in the Search field to locate any full or partial IP core name in IP Catalog.

- Right-click an IP core name in IP Catalog to display details about supported devices, to open the IP core's installation folder, and for links to IP documentation.

- Click **Search for Partner IP** to access partner IP information on the web.

The parameter editor prompts you to specify an IP variation name, optional ports, and output file generation options. The parameter editor generates a top-level Intel Quartus Prime IP file (.ip) for an IP variation in Intel Quartus Prime Pro Edition projects. This file represents the IP variation in the project, and stores parameterization information.<sup>(2)</sup>

<sup>(2)</sup> The parameter editor generates a top-level Quartus IP file (.qip) for an IP variation in Intel Quartus Prime Standard Edition projects.

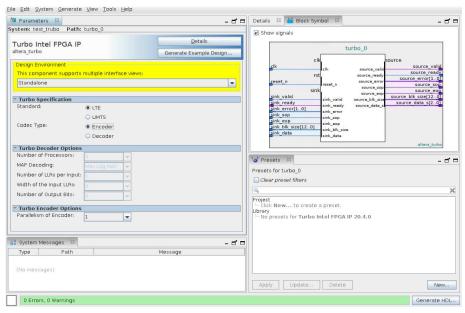

Figure 3. Example IP Parameter Editor

# 2.3. Specifying the IP Core Parameters and Options

Quickly configure Intel FPGA IP cores in the Intel Quartus Prime parameter editor. Double-click any component in the IP Catalog to launch the parameter editor. The parameter editor allows you to define a custom variation of the IP core. The parameter editor generates the IP variation synthesis and optional simulation files, and adds the .ip file representing the variation to your project automatically.

Follow these steps to locate, instantiate, and customize an IP core in the parameter editor:

- Create or open an Intel Quartus Prime project (.qpf) to contain the instantiated IP variation.

- In the IP Catalog (Tools ➤ IP Catalog), locate and double-click the name of the IP core to customize. To locate a specific component, type some or all of the component's name in the IP Catalog search box. The New IP Variation window appears.

- Specify a top-level name for your custom IP variation. Do not include spaces in IP variation names or paths. The parameter editor saves the IP variation settings in a file named <your\_ip>.ip. Click OK. The parameter editor appears.

- 4. Set the parameter values in the parameter editor and view the block diagram for the component. The **System Messages** tab at the bottom displays any errors in IP parameters:

- Optionally, select preset parameter values if provided for your IP core. Presets specify initial parameter values for specific applications.

- Specify parameters defining the IP core functionality, port configurations, and device-specific features.

- Specify options for processing the IP core files in other EDA tools.

*Note:* Refer to your IP core user guide for information about specific IP core parameters.

- 5. Click **Generate HDL**. The **Generation** dialog box appears.

- 6. Specify output file generation options, and then click **Generate**. The synthesis and simulation files generate according to your specifications.

- 7. To generate a simulation testbench, click **Generate ➤ Generate Testbench System**. Specify testbench generation options, and then click **Generate**.

- 8. To generate an HDL instantiation template that you can copy and paste into your text editor, click **Generate** ➤ **Show Instantiation Template**.

- 9. Click **Finish**. Click **Yes** if prompted to add files representing the IP variation to your project.

- 10. After generating and instantiating your IP variation, make appropriate pin assignments to connect ports.

UG-TURBO | 2021.03.28

Note: Some IP cores generate different HDL implementations according to the IP core parameters. The underlying RTL of these IP cores contains a unique hash code that prevents module name collisions between different variations of the IP core. This unique code remains consistent, given the same IP settings and software version during IP generation. This unique code can change if you edit the IP core's parameters or upgrade the IP core version. To avoid dependency on these unique codes in your simulation environment, refer to Generating a Combined Simulator Setup Script.

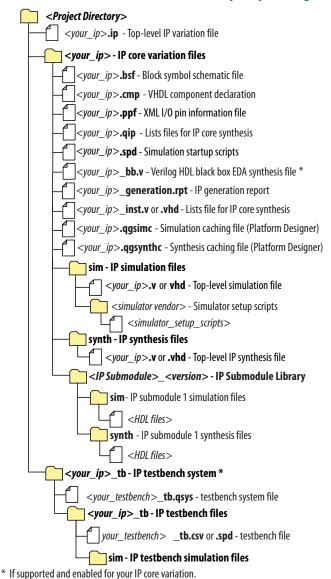

### 2.3.1. IP Core Generation Output (Intel Quartus Prime Pro Edition)

The Intel Quartus Prime software generates the following output file structure for individual IP cores that are not part of a Platform Designer system.

Figure 5. Individual IP Core Generation Output (Intel Quartus Prime Pro Edition)

Send Feedback

Table 5. Output Files of Intel FPGA IP Generation

| File Name                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <your_ip>.ip</your_ip>                                        | Top-level IP variation file that contains the parameterization of an IP core in your project. If the IP variation is part of a Platform Designer system, the parameter editor also generates a .qsys file.                                                                                                                                                                                                                                                                     |

| <pre><your_ip>.cmp</your_ip></pre>                            | The VHDL Component Declaration (.cmp) file is a text file that contains local generic and port definitions that you use in VHDL design files.                                                                                                                                                                                                                                                                                                                                  |

| <pre><your_ip>_generation.rpt</your_ip></pre>                 | IP or Platform Designer generation log file. Displays a summary of the messages during IP generation.                                                                                                                                                                                                                                                                                                                                                                          |

| $<\!your\_ip\!>$ .qgsimc (Platform Designer systems only)     | Simulation caching file that compares the $.qsys$ and $.ip$ files with the current parameterization of the Platform Designer system and IP core. This comparison determines if Platform Designer can skip regeneration of the HDL.                                                                                                                                                                                                                                             |

| $<\!your\_ip\!>$ . $qgsynth$ (Platform Designer systems only) | Synthesis caching file that compares the .qsys and .ip files with the current parameterization of the Platform Designer system and IP core. This comparisor determines if Platform Designer can skip regeneration of the HDL.                                                                                                                                                                                                                                                  |

| <pre><your_ip>.qip</your_ip></pre>                            | Contains all information to integrate and compile the IP component.                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre><your_ip>.csv</your_ip></pre>                            | Contains information about the upgrade status of the IP component.                                                                                                                                                                                                                                                                                                                                                                                                             |

| <pre><your_ip>.bsf</your_ip></pre>                            | A symbol representation of the IP variation for use in Block Diagram Files (.bdf).                                                                                                                                                                                                                                                                                                                                                                                             |

| <pre><your_ip>.spd</your_ip></pre>                            | Input file that ip-make-simscript requires to generate simulation scripts. The .spd file contains a list of files you generate for simulation, along with information about memories that you initialize.                                                                                                                                                                                                                                                                      |

| <pre><your_ip>.ppf</your_ip></pre>                            | The Pin Planner File (.ppf) stores the port and node assignments for IP components you create for use with the Pin Planner.                                                                                                                                                                                                                                                                                                                                                    |

| <pre><your_ip>_bb.v</your_ip></pre>                           | Use the Verilog blackbox (_bb.v) file as an empty module declaration for use as a blackbox.                                                                                                                                                                                                                                                                                                                                                                                    |

| <pre><your_ip>_inst.v or _inst.vhd</your_ip></pre>            | HDL example instantiation template. Copy and paste the contents of this file into your HDL file to instantiate the IP variation.                                                                                                                                                                                                                                                                                                                                               |

| <pre><your_ip>.regmap</your_ip></pre>                         | If the IP contains register information, the Intel Quartus Prime software generates the .regmap file. The .regmap file describes the register map information of master and slave interfaces. This file complements the .sopcinfo file by providing more detailed register information about the system. This file enables register display views and user customizable statistics in System Console.                                                                          |

| <your_ip>.svd</your_ip>                                       | Allows HPS System Debug tools to view the register maps of peripherals that connect to HPS within a Platform Designer system.  During synthesis, the Intel Quartus Prime software stores the .svd files for slave interface visible to the System Console masters in the .sof file in the debug session. System Console reads this section, which Platform Designer queries for register map information. For system slaves, Platform Designer accesses the registers by name. |

| <pre><your_ip>.v <your_ip>.vhd</your_ip></your_ip></pre>      | HDL files that instantiate each submodule or child IP core for synthesis or simulation.                                                                                                                                                                                                                                                                                                                                                                                        |

| mentor/                                                       | Contains a msim_setup.tcl script to set up and run a ModelSim* simulation.                                                                                                                                                                                                                                                                                                                                                                                                     |

| aldec/                                                        | Contains a Riviera-PRO* script rivierapro_setup.tcl to setup and run a simulation.                                                                                                                                                                                                                                                                                                                                                                                             |

| /synopsys/vcs                                                 | Contains a shell script vcs_setup.sh to set up and run a VCS* simulation.                                                                                                                                                                                                                                                                                                                                                                                                      |

| /synopsys/vcsmx                                               | Contains a shell script vcsmx_setup.sh and synopsys_sim.setup file to set up and run a VCS MX simulation.                                                                                                                                                                                                                                                                                                                                                                      |

|                                                               | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| File Name               | Description                                                                                                                   |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| /cadence                | Contains a shell script ncsim_setup.sh and other setup files to set up and run an NCSim simulation.                           |

| /xcelium                | Contains an Xcelium* Parallel simulator shell script xcelium_setup.sh and other setup files to set up and run a simulation.   |

| /submodules             | Contains HDL files for the IP core submodule.                                                                                 |

| <ip submodule="">/</ip> | Platform Designer generates /synth and /sim sub-directories for each IP submodule directory that Platform Designer generates. |

# 2.4. Simulating Intel FPGA IP Cores

The Intel Quartus Prime software supports IP core RTL simulation in specific EDA simulators. IP generation optionally creates simulation files, including the functional simulation model, any testbench (or example design), and vendor-specific simulator setup scripts for each IP core. You can use the functional simulation model and any testbench or example design for simulation. IP generation output may also include scripts to compile and run any testbench. The scripts list all models or libraries you require to simulate your IP core.

The Intel Quartus Prime software provides integration with many simulators and supports multiple simulation flows, including your own scripted and custom simulation flows. Whichever flow you choose, IP core simulation involves the following steps:

- 1. Generate IP HDL, testbench (or example design), and simulator setup script files.

- 2. Set up your simulator environment and any simulation scripts.

- 3. Compile simulation model libraries.

- 4. Run your simulator.

### 2.5. Simulating the Turbo IP with the RTL Simulator

Before simulating, generate the Turbo IP design example from the IP parameter editor.

- To run the simulation with Synopsys VCS simulator:

- 1. Run vcsmx\_setup.sh from <example\_design\_directory> \simulation\_scripts\synopsys\vcsmx\ directory by typing the following commands:

```

>> source vcsmx_setup.sh

>> simv

```

- To run the simulation with Cadence NCSim® simulator:

- 1. Run ncsim\_setup.sh from <example\_design\_directory> \simulation\_scripts\cadence\ directory by typing the following command:

```

sh ./ncsim_setup.sh USER_DEFINED_ELAB_OPTIONS='"-timescale lps/lps"'USER_DEFINED_SIM_OPTIONS='"-input \"@run; exit\""'

```

- To run the simulation with Xcelium simulator:

- Run xcelium\_setup.sh from <example\_design\_directory>

\simulation\_scripts\xcelium\ directory by typing the following command:

```

sh ./xcelium_setup.sh USER_DEFINED_ELAB_OPTIONS='"-timescale 1ps/1ps"'USER_DEFINED_SIM_OPTIONS='"-input \"@run; exit\""'

```

- To run the simulation with ModelSim simulator:

- 1. Run msim\_setup.tcl from <example\_design\_directory>

\simulation\_scripts\mentor\ directory by typing the following commands:

```

do msim_setup.tcl

ld

run -all

```

- To run the simulation with Aldec<sup>®</sup> simulator:

- Run rivierapro\_setup.tcl from <example\_design\_directory>

\simulation\_scripts\aldec\ directory by typing the following

commands:

```

do rivierapro_setup.tcl

ld

run -all

```

# 2.6. Simulating the Turbo IP with the C-Model

Before simulating, generate the Turbo IP design example from the IP parameter editor.

### Table 6. Turbo C-Model versus Turbo IP Related Parameters

| Turbo C-model | Turbo IP                                       | Value  |

|---------------|------------------------------------------------|--------|

| K             | Block size K, supports LTE standard            | -      |

| CW            | sink_data (input codeword Ncb)                 | -      |

| llr_width     | Width of the input LLRs supports 5,6,7,8.      | 8      |

| early_ter     | Early termination, always set to 1.            | 1      |

| crc24b        | CRC_type,                                      | -      |

| max_subiter   | sink_max_iter supports up to 31 (5 bits).      | -      |

| nb_eng        | Number of Processors supports 2, 4, 8, 16, 32. | 16     |

| Iter_used     | source_iter                                    | Output |

| crc_pass      | CRC_pass                                       | Output |

| decoded_bits  | source_data_s                                  | Output |

### 2.6.1. Encoder Simulation

- 1. Go to the <example\_design\_directory>\c\ directory.

- 2. Compile the C code:

For LTE, type the following command:

```

>> gcc -lm main_lte_enc.c -o run_enc

```

For UMTS, type the following command:

```

>> gcc -lm main_umts_enc.c -o run_enc

```

3. Run the executable without arguments.

```

>>./run_enc

```

Note: The executable reads /test\_data/ctc\_encoder\_input.txt and ./

test\_data/ctc\_encoder\_input\_info.txt as inputs. The executable

generates /test\_data/ctc\_encoder\_output\_gold.txt as output. The

RTL simulation uses the same input .txt files. The output .txt file

provides a golden output, which may be used to check the correctness of

the output from RTL simulations.

### 2.6.2. Decoder Simulation

- 1. Go to the <example\_design\_directory>\c\ directory.

- 2. Compile the C code:

For LTE, type the following command:

```

>> gcc -lm main_lte_dec.c -o run_dec

```

For UMTS, type the following command:

```

>> gcc -lm main_umts_dec.c -o run_dec

```

3. Run the executable without arguments.

```

>>./run_dec

```

Note: The executable reads /test\_data/ctc\_input\_data.txt and / test\_data/ctc\_input\_info.txt as inputs. The executable generates / test\_data/ctc\_decoded\_output\_gold.txt and ctc\_output\_et\_info\_gold.txtas output. The RTL simulation uses the same input .txt files. The output .txt file provides a golden output, which may be used to check the correctness of the output from RTL simulations.

### 2.7. Simulating the Turbo IP with MATLAB

Verify that the RTL behaves the same as these models.

Before simulating, generate the Turbo IP design example from the IP parameter editor.

In MATLAB, run MATLAB script from the <example\_design\_directory>

\matlab directory.

### For encoder simulation:

• Run the following script for LTE:

```

main_lte_enc

```

• Run the following script for UMTS:

```

main_umts_enc

```

### For decoder simulation:

• Run the following script for LTE:

```

main_lte_dec

```

Run the following script for UMTS:

```

main_umts_dec

```

Note: MATLAB model reads and generates the same .txt files as C model.

# 3. Parameter Settings

You can customize the Turbo IP by specifying parameters in the IP parameter editor:

**Table 7. Parameters**

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                     | Range                           | Description                                                                                                                                                                                                                                                                                                     |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Turbo Specification                                                                                                                                                                                                                                                                                                                                                                                           |                                 |                                                                                                                                                                                                                                                                                                                 |  |  |

| Standard                                                                                                                                                                                                                                                                                                                                                                                                      | LTE or UMTS Select LTE or UMTS. |                                                                                                                                                                                                                                                                                                                 |  |  |

| Codec Type                                                                                                                                                                                                                                                                                                                                                                                                    | Encoder, Decoder                | Select an encoder or decoder.                                                                                                                                                                                                                                                                                   |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                               | Tur                             | bo Decoder Options                                                                                                                                                                                                                                                                                              |  |  |

| Number of Processors  2, 4, 8, 16, 32  Note: The UMTS supports only 2 and 4, and LTE supports 2, 4, 8, 16, 32.  Select the number of engines (N <sub>dec</sub> ) that the decoder uses. The output width (W <sub>out</sub> ) varies depending on the number of engines:  • 8 bits for 8 engines or less, • 16 bits for 16 engines, • 32 bits for 32 engines  Note: For the UMTS the output width is always 1. |                                 |                                                                                                                                                                                                                                                                                                                 |  |  |

| Number of LLRs<br>per input                                                                                                                                                                                                                                                                                                                                                                                   | 1 or 2                          | The number of data LLR per input symbol ( $N_{\rm LLR}$ ). For two LLR the input symbols are Z'2 Z2 X2 Z'1 Z1 X1  Note: This parameter is not available if you select UMTS standard.                                                                                                                            |  |  |

| Width of the input<br>LLRs                                                                                                                                                                                                                                                                                                                                                                                    | 5, 6, 7, 8                      | The number of input bits (W <sub>LLR</sub> ) to the decoder. Three of the bits are integer bits and the remaining bits are fractional bits:  • 5-bit LLRs have two fractional bits.  • 6-bit LLRs have three fractional bits.  • 7-bit LLRs have four fractional bits.  • 8-bit LLRs have five fractional bits. |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                               | Tur                             | bo Encoder Options                                                                                                                                                                                                                                                                                              |  |  |

| Parallelism of<br>Encoder                                                                                                                                                                                                                                                                                                                                                                                     | 1, 4, 8                         | Selects the number of parallel encoding engines ( $N_{\rm enc}$ ) for LTE turbo encoder only.  For UMTS turbo encoder the value of this parameter ( $N_{\rm enc}$ ) is 1. This parameter is not available in the Intel Quartus Prime Standard Edition software IP variations.                                   |  |  |

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, eASIC, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# 4. Turbo Intel FPGA IP Functional Description

This topic describes the IP core's architecture, interfaces, and signals.

You can parameterize the Turbo IP core as an encoder or a decoder.

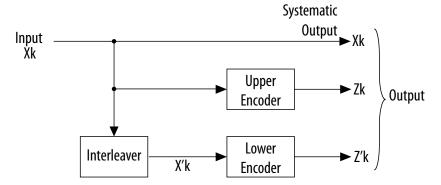

### 4.1. Turbo Encoder

The 3GPP Turbo encoder uses a parallel concatenated convolutional code. A convolutional encoder encodes an information sequence and another convolutional encoder encodes an interleaved version of the information sequence. The Turbo encoder has two 8-state constituent encoders and one Turbo code internal interleaver. The Turbo encoder accepts K bits and outputs 3K+12 bits, having a natural code rate 1/3. The last 12 output bits of every packet are termination bits, which guarantee that the state of the encoder is back to state zero in the end of encoding process.

Figure 6. Turbo Encoder Block Diagram

The output from the turbo coder is:

$$X_0, Z_0, Z'_0, X_1, Z_1, Z'_1, ..., X_{K-1}, Z_{K-1}, Z'_{K-1}$$

### Where:

- Bits  $X_0$ ,  $X_1$ , ...,  $X_{K-1}$  are input to both the first 8-state constituent encoder and the internal interleaver (K is the number of bits).

- Bits  $Z_0$ ,  $Z_1$ , ...,  $Z_{K-1}$  and  $Z'_0$ ,  $Z'_1$ , ...,  $Z'_{K-1}$  are output from the first and second 8-state constituent encoders.

- The bits output from the internal interleaver (and input to the second 8-state constituent encoder) are  $X'_0, X'_1, ..., X'_{K-1}$ .

- Additionally, encoder outputs 12 termination bits,  $X_K$ ,  $X_{K+1}$ ,  $X_{K+2}$ ,  $X'_K$ ,  $X'_{K+1}$ ,  $X'_K$ ,  $X'_{K+1}$ ,  $X'_K$ ,  $X'_{K+1}$ ,  $X'_{K+2}$ ,  $X'_{K+1}$ ,  $X'_{K+2}$ ,  $X'_{K+1}$ ,  $X'_{K+2}$ .

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, eASIC, Intel, the Intel logo, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

### 4.1.1. Turbo Encoder Data Format

The required input data ordering for a block of size K is:  $X_0$ ,  $X_1$ ,  $X_2$ , . . . .  $X_{K-1}$ . The output data is three bits wide.

Table 8. Turbo Encoder Input Data Ordering for a Block of Size K

| Output Data | sink_data                                                  |                                |                       |  |

|-------------|------------------------------------------------------------|--------------------------------|-----------------------|--|

|             | N <sub>enc</sub> = 8                                       | N <sub>enc</sub> = 4           | N <sub>enc</sub> = 1  |  |

| 0           | $X_7X_6X_5X_4X_3X_2X_1X_0$                                 | $X_3X_2X_1X_0$                 | <i>X</i> <sub>0</sub> |  |

| 1           | $X_{15}X_{14}X_{13}X_{12}X_{11}X_{10}X_{9}X_{8}$           | $X_7X_6X_5X_4$                 | X <sub>1</sub>        |  |

|             |                                                            |                                |                       |  |

| K - 1       | -                                                          | -                              | X <sub>K-1</sub>      |  |

| K/4-1       | -                                                          | $X_{K-1}X_{K-2}X_{K-3}X_{K-4}$ | -                     |  |

| K/8-1       | $X_{K-1}X_{K-2}X_{K-3}X_{K-4}X_{K-5}X_{K-6}X_{K-7}X_{K-8}$ | -                              | -                     |  |

Table 9. Turbo Encoder Output Data Ordering for a Block of Size K and Number of Parallel Encoder = 1

| Output Data | source_data          |                   |                       |

|-------------|----------------------|-------------------|-----------------------|

|             | 2                    | 1                 | 0                     |

| 0           | Z ′0                 | $Z_0$             | <i>X</i> <sub>0</sub> |

| 1           | Z '1                 | $Z_1$             | <i>X</i> <sub>1</sub> |

|             |                      |                   |                       |

| K - 1       | Z' <sub>K-1</sub>    | Z <sub>K-1</sub>  | X <sub>K-1</sub>      |

| К           | X <sub>K+1</sub>     | $Z_K$             | X <sub>K</sub>        |

| K + 1       | Z <sub>K + 2</sub>   | X <sub>K+2</sub>  | Z <sub>K+1</sub>      |

| K + 2       | X ' <sub>K + 1</sub> | Z' <sub>K</sub>   | X ' <sub>K</sub>      |

| K + 3       | Z' <sub>K+2</sub>    | X' <sub>K+2</sub> | Z' <sub>K+1</sub>     |

Note: The outputs of the last four clock cycles are corresponding to 12 termination bits.

# Table 10. Turbo Encoder Output Data Ordering for a Block of Size K and $N_{enc} = 4$

Note: Parallelism of encoder is only supported in Intel Arria 10, Intel Stratix 10, and Intel Agilex device variations in Intel Quartus Prime Pro Edition software and not supported for Intel Arria 10 device variation in Intel Quartus Prime Standard Edition software.

| Output Data | source_data                                                                |                                                                     |                                                                     |  |  |

|-------------|----------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|--|--|

|             | 118                                                                        | 74                                                                  | 30                                                                  |  |  |

| 0           | Z '3Z '2Z '1Z'0                                                            | $Z_3Z_2Z_1Z_0$                                                      | $X_3X_2X_1X_0$                                                      |  |  |

| 1           | Z' <sub>7</sub> Z' <sub>6</sub> Z' <sub>5</sub> Z' <sub>4</sub>            | $Z_7Z_6Z_5Z_4$                                                      | X7X <sub>6</sub> X <sub>5</sub> X <sub>4</sub>                      |  |  |

|             |                                                                            |                                                                     |                                                                     |  |  |

| K / 4 - 1   | Z ' <sub>K-1</sub> Z ' <sub>K-2</sub> Z ' <sub>K-3</sub> Z' <sub>K-4</sub> | $Z_{K-1}Z_{K-2}Z_{K-3}Z_{K-4}$                                      | $X_{K-1}X_{K-2}X_{K-3}X_{K-4}$                                      |  |  |

| K / 4       | Z' <sub>K+2</sub> X' <sub>K+1</sub> Z <sub>K+2</sub> X <sub>K+1</sub>      | X ' <sub>K+2</sub> Z ' <sub>K</sub> X <sub>K+2</sub> Z <sub>K</sub> | Z ' <sub>K+1</sub> X ' <sub>K</sub> Z <sub>K+1</sub> X <sub>K</sub> |  |  |

Note: The outputs of the last four clock cycles are corresponding to 12 termination bits.

### Table 11. Turbo Encoder Output Data Ordering for a Block of Size K and $N_{enc} = 8$

Note: The value of  $N_{\rm enc}$  can be 1, 4, or 8 in the Intel Quartus Prime Pro Edition software and the value is 1 in Intel Quartus Prime Standard Edition software .  $N_{\rm enc}$  is only supported in Intel Arria 10, Intel Stratix 10, and Intel Agilex device variations in Intel Quartus Prime Pro Edition software and not supported for Intel Arria 10 device variation in Intel Quartus Prime Standard Edition software.

| Output Data | source_data                                                                                                                                     |                                                                          |                                                                          |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|

|             | 2316                                                                                                                                            | 158                                                                      | 70                                                                       |

| 0           | Z' <sub>7</sub> Z' <sub>6</sub> Z' <sub>5</sub> Z' <sub>4</sub> Z' <sub>3</sub> Z' <sub>2</sub> Z' <sub>1</sub> Z' <sub>0</sub>                 | $Z_7Z_6Z_5Z_4Z_3Z_2Z_1Z_0$                                               | $X_7X_6X_5X_4X_3X_2X_1X_0$                                               |

| 1           | Z' <sub>15</sub> Z' <sub>14</sub> Z' <sub>13</sub> Z' <sub>12</sub> Z' <sub>11</sub> Z' <sub>10</sub> Z' <sub>9</sub> Z' <sub>8</sub>           | $Z_{15}Z_{14}Z_{13}Z_{12}Z_{11}Z_{10}Z_{9}Z_{8}$                         | $X_{15}X_{14}X_{13}X_{12}X_{11}X_{10}X_{9}X_{8}$                         |

| ***         |                                                                                                                                                 |                                                                          |                                                                          |

| K / 8 - 1   | Z' <sub>K-1</sub> Z' <sub>K-2</sub> Z' <sub>K-3</sub> Z' <sub>K-4</sub> Z' <sub>K-5</sub> Z' <sub>K-6</sub> Z' <sub>K-7</sub> Z' <sub>K-8</sub> | $Z_{K-1}Z_{K-2}Z_{K-3}Z_{K-4}Z_{K-5}Z_{K-6}Z_{K-7}Z_{K-8}$               | $X_{K-1}X_{K-2}X_{K-3}X_{K-4}X_{K-5}X_{K-6}X_{K-7}X_{K-8}$               |

| K / 8       | 4'bx Z ' <sub>K+2</sub> X ' <sub>K+1</sub> Z <sub>K+2</sub> X <sub>K+1</sub>                                                                    | 4'bx X ' <sub>K+2</sub> Z ' <sub>K</sub> X <sub>K+2</sub> Z <sub>K</sub> | 4'bx Z ' <sub>K+1</sub> X ' <sub>K</sub> Z <sub>K+1</sub> X <sub>K</sub> |

Note:

The outputs of the last clock cycles are corresponding to 12 termination bits. where output bits 23, 22, 21, 20, 15, 14, 13, 12, 7, 6, 5, 4 in the last clock cycle are unused bits.

### 4.1.2. Turbo Encoder Latency Calculation

The encoding delay D is the number of clock cycles the IP core consumes to encode an entire block of data. If K is the block size,  $D = K/N_{enc} + 14$ , where  $N_{enc}^{(3)}$  is the number of parallel encoder. The encoding delay does not include the loading delay, which requires the same number of clock cycles as the block size K to load the input data to the input buffer.

### For example:

- When K = 6144, and  $N_{enc} = 8$ , D = 6144/8 + 14 = 782

- When K = 40, and  $N_{enc} = 1$ , D = 40 + 14 = 54

You can calculate the encoding latency (the time taken by the encoder to encode an entire block) using the following equation:

L = D/f s

Where f is the system clock speed.

### 4.2. Turbo Decoder

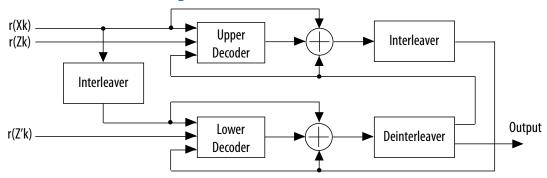

The Turbo decoder consists of two single soft-in soft-out (SISO) decoders, which work iteratively. The output of the first (upper decoder) feeds into the second to form a Turbo decoding iteration. Interleaver and deinterleaver blocks re-order data in this process.

<sup>(3)</sup> The value of 4 or 8 is only available in Intel Arria 10, Intel Stratix 10, and Intel Agilex device variations in Intel Quartus Prime Pro Edition software.

UG-TURBO | 2021.03.28

Figure 7. Turbo Decoder Block Diagram

The Turbo decoder supports the MaxLogMAP decoding algorithm. This algorithm is a simplified version of LogMAP that uses less logic resource and offers slightly reduced BER performance relative to LogMAP.

### 4.2.1. Turbo Decoder Data Format

Table 12. Turbo Decoder Output Data Ordering for a Block of Size K

N is the width of the input LLRs.

| Input Data | sink_data         |                    |                       |  |

|------------|-------------------|--------------------|-----------------------|--|

|            | 3N - 1 down to 2N | 2N - 1 down to N   | N - 1 down to 0       |  |

| 0          | Z ′0              | $Z_0$              | <i>X</i> <sub>0</sub> |  |

| 1          | Z' <sub>1</sub>   | $Z_1$              | <i>X</i> <sub>1</sub> |  |

|            |                   |                    |                       |  |

| K - 1      | Z' <sub>K-1</sub> | Z <sub>K-1</sub>   | X <sub>K-1</sub>      |  |

| К          | X <sub>K+1</sub>  | $Z_K$              | X <sub>K</sub>        |  |

| K + 1      | Z <sub>K+2</sub>  | X <sub>K + 2</sub> | Z <sub>K+1</sub>      |  |

| K + 2      | X' <sub>K+1</sub> | Z' <sub>K</sub>    | X ' <sub>K</sub>      |  |

| K + 3      | Z' <sub>K+2</sub> | X' <sub>K+2</sub>  | Z' <sub>K+1</sub>     |  |

The Turbo decoder requires all data to be in the log-likelihood format. The connected system must provide soft information, including parity 1 and parity 2 bit sequences according to the following equation:

$$L(x) = \log[P(x=1)/(x=0)]$$

The log-likelihood value is the logarithm of the probability that the received bit is a 1, divided by the probability that this bit is a 0. It is represented as a two's complement number. A value of zero indicates equal probability of a 1 and a 0, which you should use for depuncturing. The decoder does not use the most negative two's complement number, which means the representation is balanced.

**Table 13. Four-bit Mapping Input Values**

| Input (3 downto 0) | Value                         |

|--------------------|-------------------------------|

| 0111               | Most likelihood of a 1        |

|                    |                               |

| 0001               | Lowest likelihood of a 1      |

| 0000               | Equal probability of a 0 or 1 |

| 1111               | Lowest likelihood of a 0      |

|                    |                               |

| 1001               | Most likelihood of a 0        |

| 1000               | Not used                      |

### **Output**

The number of output bits can be 1 or 8 bits. For 1 bit, the ordering is:  $X_0$ ,  $X_1$ ,  $X_2$ , . . . .  $X_{K-1}$

Table 14. 8-bit Output Data Ordering

| Output Order | source_data      |                  |                  |                    |                       |                    |                       |                       |

|--------------|------------------|------------------|------------------|--------------------|-----------------------|--------------------|-----------------------|-----------------------|

|              | 7                | 6                | 5                | 4                  | 3                     | 2                  | 1                     | 0                     |

| 1            | X <sub>7</sub>   | X <sub>6</sub>   | X <sub>5</sub>   | X <sub>4</sub>     | <i>X</i> <sub>3</sub> | X <sub>2</sub>     | <i>X</i> <sub>1</sub> | <i>X</i> <sub>0</sub> |

| 2            | X <sub>15</sub>  | X <sub>14</sub>  | X <sub>13</sub>  | X <sub>12</sub>    | X <sub>11</sub>       | X <sub>10</sub>    | X <sub>9</sub>        | X <sub>8</sub>        |

|              |                  |                  |                  |                    |                       |                    |                       |                       |

| K/8          | X <sub>K-1</sub> | X <sub>K-2</sub> | X <sub>K-3</sub> | X <sub>K - 4</sub> | X <sub>K - 5</sub>    | X <sub>K - 6</sub> | X <sub>K - 7</sub>    | X <sub>K - 8</sub>    |

### 4.2.2. CRC24A or CRC24B Early Termination

Early termination reduces power consumption and the overall latency, and increases the throughput significantly. It may also increase BER performance of the decoder.

The IP core checks the CRC checksum that the decoder generates after every iteration. Turbo decoding stops as soon as the CRC is successful. turbo decoding does not continue until the maximum number of iterations specified at the input ports. The gains depend on the signal-to-noise ration (SNR) of the received data block, block size, and the maximum number of iterations you specify.

### 4.2.3. Decoder Latency Calculation

The decoding delay *D* is the number of clock cycles the IP core consumes to decode an entire block of data. *D* depends on the block size, the number of iterations to perform, and the number of engines available in the decoder.

The following calculations assume no early termination for the worst case latency.

You can calculate the decoding delay D using one of the following equations:

- If K < 264:  $D = 26 + (2 \times f(K,N) + 14) \times 2 \times I$

- If K > 264,  $D = 26 + (f(K,N) + 46) \times 2 \times I$

UG-TURBO | 2021.03.28

#### where:

- K is the block size

- *I* is the number of decoding iterations

- N<sub>dec</sub> is the number of engines specified in the decoder

### For LTE,

- $f(K,N_{dec}) = K/N_{dec}$  if K is divisible by  $N_{dec}$ .

- $f(K,N_{dec}) = K/16$  if K is not divisible by  $N_{dec}$ , but it is divisible by 16.

- $f(K,N_{dec}) = K/8$  in all other conditions.

For UMTS,

$$f(K,N_{dec}) = ceil(K/N_{dec})$$

### For example:

- D =  $26 + (6144/8 + 46) \times 2 \times 8 = 13,050$ , if K = 6144, N = 8, I = 8.

- D =  $26 + (2 \times 40/8 + 14) \times 2 \times 8 = 410$ , if K = 40, N = 8, I = 8.

You can calculate the decoding latency (the time the decoder takes to decode an entire block to the decoded data is ready for output) using the following equation:

$$L = D/f s$$

Where f is the system clock speed.

### 4.2.4. Error Correction Performance for the Turbo Decoder

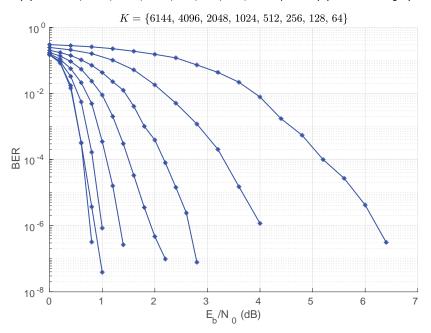

Figure 8. BER (bit error rate) Curve of LTE turbo decoder over AWGN channels, where  $N_{\text{dec}} = 8$ ,  $W_{\text{LLR}} = 6$ , and I = 8

Block sizes (K) are 6144, 4096, 2048, 1024, 512, 256, 128, 64 respectively (from left to right).

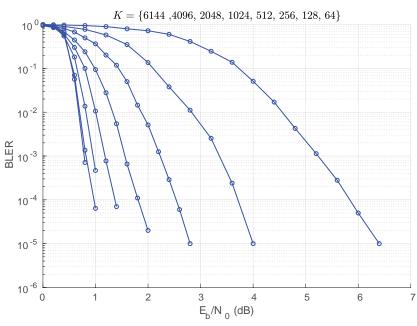

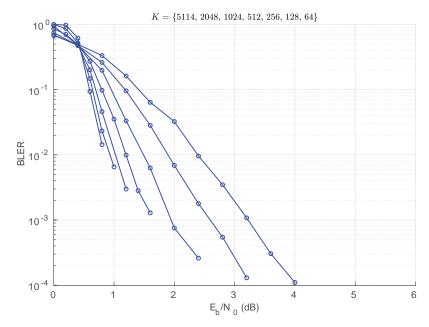

Figure 9. BLER (block error rate) Curve of LTE turbo decoder over AWGN channels, where  $N_{\rm dec}$ = 8,  $W_{\rm LLR}$ = 6, and I= 8

Block sizes (K) are 6144, 4096, 2048, 1024, 512, 256, 128, 64 respectively (from left to right).

Send Feedback

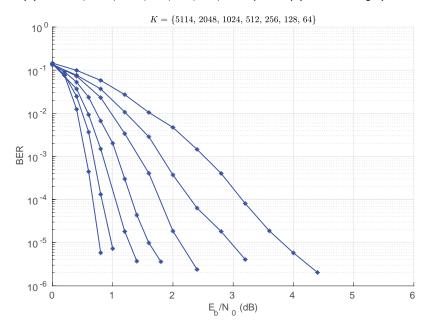

Figure 10. BER Curve of UMTS turbo decoder over AWGN channels, where  $N_{\rm dec}$ = 4,  $W_{\rm LLR}$ = 6, and I= 8

Block sizes (K) are 5144, 2048, 1024, 512, 256, 128, 64 respectively (from left to right).

Figure 11. BLER Curve of UMTS turbo decoder over AWGN channels, where  $N_{\text{dec}}$  = 4,  $W_{\text{LLR}}$  = 6, and I = 8

Block sizes (K) are 5144, 2048, 1024, 512, 256, 128, 64 respectively (from left to right).

# 4.3. Turbo IP Core Interfaces and Signals

Signal names beginning with  $sink_*$  are the input interface to the Turbo IP. Signal names beginning with  $source_*$  are the output interface from the Turbo IP (excluding  $sink_ready$  and  $source_ready$  signals). Both interfaces comply with the Avalon Streaming specification with READY\_LATENCY = 0.

**Table 15.** Turbo Encoder Signals

| Signal          | Direction | Description                                                                                                                                                                                                                       |

|-----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk             | Input     | Clock signal that clocks all internal registers.                                                                                                                                                                                  |

| reset_n         | Input     | Active low reset signal. The IP core must always be reset before receiving data. If the megafunction is not reset, the Turbo encoder may produce unexpected results because of feedback signals.                                  |

| sink_blk_size   | Input     | Specifies the incoming block size. This needs to be held throughout the whole incoming block, from sop to eop.                                                                                                                    |

| sink_data       | Input     | Input data.                                                                                                                                                                                                                       |