# 10. Selectable I/O Standards in Stratix II and Stratix II GX Devices

SII52004-4.6

#### Introduction

This chapter provides guidelines for using industry I/O standards in Stratix<sup>®</sup> II and Stratix II GX devices, including:

- I/O features

- I/O standards

- External memory interfaces

- I/O banks

- Design considerations

# Stratix II and Stratix II GX I/O Features

Stratix II and the Stratix II GX devices contain an abundance of adaptive logic modules (ALMs), embedded memory, high-bandwidth digital signal processing (DSP) blocks, and extensive routing resources, all of which can operate at very high core speed.

Stratix II and Stratix II GX devices I/O structure is designed to ensure that these internal capabilities are fully utilized. There are numerous I/O features to assist in high-speed data transfer into and out of the device including:

- Single-ended, non-voltage-referenced and voltage-referenced I/O standards

- High-speed differential I/O standards featuring serializer/deserializer (SERDES), dynamic phase alignment (DPA), capable of 1 gigabit per second (Gbps) performance for low-voltage differential signaling (LVDS), Hypertransport technology, HSTL, SSTL, and LVPECL

HSTL and SSTL I/O standards are used only for PLL clock inputs and outputs in differential mode. LVPECL is supported on clock input and outputs of the top and bottom I/O banks.

- Double data rate (DDR) I/O pins

- Programmable output drive strength for voltage-referenced and non-voltage-referenced single-ended I/O standards

- Programmable bus-hold

- Programmable pull-up resistor

- Open-drain output

- On-chip series termination

- On-chip parallel termination

- On-chip differential termination

- Peripheral component interconnect (PCI) clamping diode

- Hot socketing

For a detailed description of each I/O feature, refer to the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook* or the *Stratix II GX Architecture* chapter in volume 1 of the *Stratix II GX Device Handbook*.

# Stratix II and Stratix II GX I/O Standards Support

Stratix II and Stratix II GX devices support a wide range of industry I/O standards. Table 10–1 shows which I/O standards Stratix II devices support as well as typical applications.

| Table 10–1. Stratix II and Stratix II GX I/O Standard Applications | (Part 1 |

|--------------------------------------------------------------------|---------|

| of 2)                                                              |         |

| I/O Standard                     | Application               |

|----------------------------------|---------------------------|

| LVTTL                            | General purpose           |

| LVCMOS                           | General purpose           |

| 2.5 V                            | General purpose           |

| 1.8 V                            | General purpose           |

| 1.5 V                            | General purpose           |

| 3.3-V PCI                        | PC and embedded system    |

| 3.3-V PCI-X                      | PC and embedded system    |

| SSTL-2 Class I                   | DDR SDRAM                 |

| SSTL-2 Class II                  | DDR SDRAM                 |

| SSTL-18 Class I                  | DDR2 SDRAM                |

| SSTL-18 Class II                 | DDR2 SDRAM                |

| 1.8-V HSTL Class I               | QDRII SRAM/RLDRAM II/SRAM |

| 1.8-V HSTL Class II              | QDRII SRAM/RLDRAM II/SRAM |

| 1.5-V HSTL Class I               | QDRII SRAM/SRAM           |

| 1.5-V HSTL Class II              | QDRII SRAM/SRAM           |

| 1.2-V HSTL                       | General purpose           |

| Differential SSTL-2 Class I      | DDR SDRAM                 |

| Differential SSTL-2 Class II     | DDR SDRAM                 |

| Differential SSTL-18 Class I     | DDR2 SDRAM                |

| Differential SSTL-18 Class II    | DDR2 SDRAM                |

| 1.8-V differential HSTL Class I  | Clock interfaces          |

| 1.8-V differential HSTL Class II | Clock interfaces          |

| Table 10–1. Stratix II and Stratix II GX I/O Standard Applications (Part 2 of 2) |                                       |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|---------------------------------------|--|--|--|--|--|--|--|

| I/O Standard                                                                     | Application                           |  |  |  |  |  |  |  |

| 1.5-V differential HSTL Class I                                                  | Clock interfaces                      |  |  |  |  |  |  |  |

| 1.5-V differential HSTL Class II                                                 | Clock interfaces                      |  |  |  |  |  |  |  |

| LVDS                                                                             | High-speed communications             |  |  |  |  |  |  |  |

| HyperTransport™ technology                                                       | PCB interfaces                        |  |  |  |  |  |  |  |

| Differential LVPECL                                                              | Video graphics and clock distribution |  |  |  |  |  |  |  |

#### Single-Ended I/O Standards

In non-voltage-referenced single-ended I/O standards, the voltage at the input must be above a set voltage to be considered "on" (high, or logic value 1) or below another voltage to be considered "off" (low, or logic value 0). Voltages between the limits are undefined logically, and may fall into either a logic value 0 or 1. The non-voltage-referenced single-ended I/O standards supported by Stratix II and Stratix II GX devices are:

- Low-voltage transistor-transistor logic (LVTTL)

- Low-voltage complementary metal-oxide semiconductor (LVCMOS)

- 1.5 V

- 1.8 V

- 2.5 V

- 3.3-V PCI

- 3.3-V PCI-X

Voltage-referenced, single-ended I/O standards provide faster data rates. These standards use a constant reference voltage at the input levels. The incoming signals are compared with this constant voltage and the difference between the two defines "on" and "off" states.

Stratix II and Stratix II GX devices support stub series terminated logic (SSTL) and high-speed transceiver logic (HSTL) voltage-referenced I/O standards.

#### LVTTL

The LVTTL standard is formulated under EIA/JEDEC Standard, JESD8-B (Revision of JESD8-A): Interface Standard for Nominal 3-V/3.3-V Supply Digital Integrated Circuits.

The standard defines DC interface parameters for digital circuits operating from a 3.0- or 3.3-V power supply and driving or being driven by LVTTL-compatible devices. The 3.3-V LVTTL standard is a

general-purpose, single-ended standard used for 3.3-V applications. This I/O standard does not require input reference voltages ( $V_{REF}$ ) or termination voltages ( $V_{TT}$ ).

Stratix II and Stratix II GX devices support both input and output levels for 3.3-V LVTTL operation.

Stratix II Stratix II GX devices support a  $V_{\rm CCIO}$  voltage level of 3.3 V  $\pm 5\%$  as specified as the narrow range for the voltage supply by the EIA/JEDEC standard.

#### LVCMOS

The LVCMOS standard is formulated under EIA/JEDEC Standard, JESD8-B (Revision of JESD8-A): Interface Standard for Nominal 3-V/3.3-V Supply Digital Integrated Circuits.

The standard defines DC interface parameters for digital circuits operating from a 3.0- or 3.3-V power supply and driving or being driven by LVCMOS-compatible devices. The 3.3-V LVCMOS I/O standard is a general-purpose, single-ended standard used for 3.3-V applications. While LVCMOS has its own output specification, it specifies the same input voltage requirements as LVTTL. These I/O standards do not require  $V_{RFF}$  or  $V_{TT}$ .

Stratix II and Stratix II GX devices support both input and output levels for 3.3-V LVCMOS operation.

Stratix II and Stratix II GX devices support a  $V_{CCIO}$  voltage level of 3.3 V  $\pm 5\%$  as specified as the narrow range for the voltage supply by the EIA/JEDEC standard.

#### 2.5 V

The 2.5-V I/O standard is formulated under EIA/JEDEC Standard, EIA/JESD8-5: 2.5-V± 0.2-V (Normal Range), and 1.8-V – 2.7-V (Wide Range) Power Supply Voltage and Interface Standard for Non-Terminated Digital Integrated Circuit.

The standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 2.5-V devices. This standard is a general-purpose, single-ended standard used for 2.5-V applications. It does not require the use of a  $\rm V_{REF}$  or a  $\rm V_{TT}$ .

Stratix II and Stratix II GX devices support both input and output levels for 2.5-V operation with  $V_{\rm CCIO}$  voltage level support of 2.5 V ± 5%, which is narrower than defined in the Normal Range of the EIA/JEDEC standard.

#### 1.8 V

The 1.8-V I/O standard is formulated under EIA/JEDEC Standard, EIA/JESD8-7: 1.8-V  $\pm$  0.15-V (Normal Range), and 1.2-V - 1.95-V (Wide Range) Power Supply Voltage and Interface Standard for Non-Terminated Digital Integrated Circuit.

The standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 1.8-V devices. This standard is a general-purpose, single-ended standard used for 1.8-V applications. It does not require the use of a  $V_{\rm REF}$  or a  $V_{\rm TT}$ .

Stratix II and Stratix II GX devices support both input and output levels for 1.8-V operation with  $V_{\rm CCIO}$  voltage level support of 1.8 V ± 5%, which is narrower than defined in the Normal Range of the EIA/JEDEC standard.

#### 1.5 V

The 1.5-V I/O standard is formulated under EIA/JEDEC Standard, JESD8-11:  $1.5\text{-V} \pm 0.1\text{-V}$  (Normal Range) and 0.9-V - 1.6-V (Wide Range) Power Supply Voltage and Interface Standard for Non-Terminated Digital Integrated Circuit.

The standard defines the DC interface parameters for high-speed, low-voltage, non-terminated digital circuits driving or being driven by other 1.5-V devices. This standard is a general-purpose, single-ended standard used for 1.5-V applications. It does not require the use of a  $\rm V_{REF}$  or a  $\rm V_{TT}$ .

Stratix II and Stratix II GX devices support both input and output levels for 1.5-V operation  $V_{\rm CCIO}$  voltage level support of 1.5 V ± 5%, which is narrower than defined in the Normal Range of the EIA/JEDEC standard.

#### 3.3-V PCI

The 3.3-V PCI I/O standard is formulated under PCI Local Bus Specification Revision 2.2 developed by the PCI Special Interest Group (SIG).

The PCI local bus specification is used for applications that interface to the PCI local bus, which provides a processor-independent data path between highly integrated peripheral controller components, peripheral add-in boards, and processor/memory systems. The conventional PCI specification revision 2.2 defines the PCI hardware environment including the protocol, electrical, mechanical, and configuration specifications for the PCI devices and expansion boards. This standard requires 3.3-V  $\rm V_{\rm CCIO.}$  Stratix II and Stratix II GX devices are fully compliant with the 3.3-V PCI Local Bus Specification Revision 2.2 and meet 64-bit/66-MHz operating frequency and timing requirements.

The 3.3-V PCI standard does not require input reference voltages or board terminations. Stratix II and Stratix II GX devices support both input and output levels.

#### 3.3-V PCI-X

The 3.3-V PCI-X I/O standard is formulated under PCI-X Local Bus Specification Revision 1.0a developed by the PCI SIG.

The PCI-X 1.0 standard is used for applications that interface to the PCI local bus. The standard enables the design of systems and devices that operate at clock speeds up to 133 MHz, or 1 Gbps for a 64-bit bus. The PCI-X 1.0 protocol enhancements enable devices to operate much more efficiently, providing more usable bandwidth at any clock frequency. By using the PCI-X 1.0 standard, you can design devices to meet PCI-X 1.0 requirements and operate as conventional 33- and 66-MHz PCI devices when installed in those systems. This standard requires 3.3-V V<sub>CCIO</sub>. Stratix II and Stratix II GX devices are fully compliant with the 3.3-V PCI-X Specification Revision 1.0a and meet the 133-MHz operating frequency and timing requirements. The 3.3-V PCI-X standard does not require input reference voltages or board terminations.

Stratix II and Stratix II GX devices support both input and output levels operation.

#### SSTL-2 Class I and SSTL-2 Class II

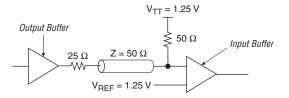

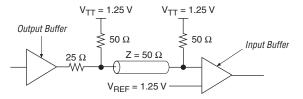

The 2.5-V SSTL-2 standard is formulated under JEDEC Standard, JESD8-9A: Stub Series Terminated Logic for 2.5-V (SSTL\_2).

The SSTL-2 I/O standard is a 2.5-V memory bus standard used for applications such as high-speed DDR SDRAM interfaces. This standard defines the input and output specifications for devices that operate in the SSTL-2 logic switching range of 0.0 to 2.5 V. This standard improves

operation in conditions where a bus must be isolated from large stubs. SSTL-2 requires a 1.25-V  $V_{REF}$  and a 1.25-V  $V_{TT}$  to which the series and termination resistors are connected (Figures 10–1 and 10–2).

Stratix II and Stratix II GX devices support both input and output levels operation.

Figure 10-1. 2.5-V SSTL Class I Termination

Figure 10–2. 2.5-V SSTL Class II Termination

#### SSTL-18 Class I and SSTL-18 Class II

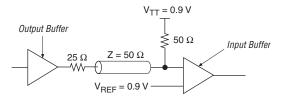

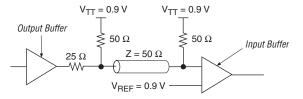

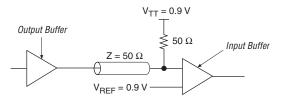

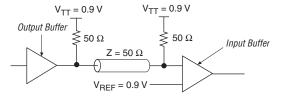

The 1.8-V SSTL-18 standard is formulated under JEDEC Standard, JESD8-15: Stub Series Terminated Logic for 1.8-V (SSTL\_18).

The SSTL-18 I/O standard is a 1.8-V memory bus standard used for applications such as high-speed DDR2 SDRAM interfaces. This standard is similar to SSTL-2 and defines input and output specifications for devices that are designed to operate in the SSTL-18 logic switching range 0.0 to 1.8 V. SSTL-18 requires a 0.9-V  $V_{\rm REF}$  and a 0.9-V  $V_{\rm TT}$  to which the series and termination resistors are connected.

There are no class definitions for the SSTL-18 standard in the JEDEC specification. The specification of this I/O standard is based on an environment that consists of both series and parallel terminating resistors. Altera provides solutions to two derived applications in JEDEC specification, and names them Class I and Class II to be consistent with other SSTL standards. Figures 10–3 and 10–4 show SSTL-18 Class I and II termination, respectively.

Stratix II and Stratix II GX devices support both input and output levels operation.

Figure 10-3. 1.8-V SSTL Class I Termination

Figure 10-4. 1.8-V SSTL Class II Termination

#### 1.8-V HSTL Class I and 1.8-V HSTL Class II

The HSTL standard is a technology-independent I/O standard developed by JEDEC to provide voltage scalability. It is used for applications designed to operate in the 0.0- to 1.8-V HSTL logic switching range such as quad data rate (QDR) memory clock interfaces.

Although JEDEC specifies a maximum  $V_{\rm CCIO}$  value of 1.6 V, there are various memory chip vendors with HSTL standards that require a  $V_{\rm CCIO}$  of 1.8 V. Stratix II and Stratix II GX devices support interfaces to chips with  $V_{\rm CCIO}$  of 1.8 V for HSTL. Figures 10–5 and 10–6 show the nominal  $V_{\rm REF}$  and  $V_{\rm TT}$  required to track the higher value of  $V_{\rm CCIO}$ . The value of  $V_{\rm REF}$  is selected to provide optimum noise margin in the system.

Stratix II and Stratix II GX devices support both input and output levels operation.

Figure 10-5. 1.8-V HSTL Class I Termination

Figure 10-6. 1.8-V HSTL Class II Termination

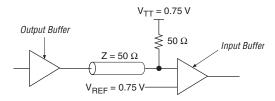

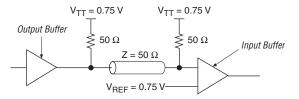

#### 1.5-V HSTL Class I and 1.5-V HSTL Class II

The 1.5-V HSTL standard is formulated under EIA/JEDEC Standard, EIA/JESD8-6: A 1.5-V Output Buffer Supply Voltage Based Interface Standard for Digital Integrated Circuits.

The 1.5-V HSTL I/O standard is used for applications designed to operate in the 0.0- to 1.5-V HSTL logic nominal switching range. This standard defines single-ended input and output specifications for all HSTL-compliant digital integrated circuits. The 1.5-V HSTL I/O standard in Stratix II and Stratix II GX devices are compatible with the 1.8-V HSTL I/O standard in APEX<sup>TM</sup> 20KE, APEX 20KC, and in Stratix II and Stratix II GX devices themselves because the input and output voltage thresholds are compatible (Figures 10–7 and 10–8).

Stratix II and Stratix II GX devices support both input and output levels with  $V_{\text{REF}}$  and  $V_{\text{TT}}\!.$

Figure 10-7. 1.5-V HSTL Class I Termination

Figure 10-8. 1.5-V HSTL Class II Termination

#### 1.2-V HSTL

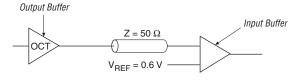

Although there is no EIA/JEDEC standard available for the 1.2-V HSTL standard, Altera supports it for applications that operate in the 0.0 to 1.2-V HSTL logic nominal switching range. 1.2-V HSTL can be terminated through series or parallel on-chip termination (OCT). Figure 10–9 shows the termination scheme.

Figure 10-9. 1.2-V HSTL Termination

#### Differential I/O Standards

Differential I/O standards are used to achieve even faster data rates with higher noise immunity. Apart from LVDS, LVPECL, and HyperTransport technology, Stratix II and Stratix II GX devices also support differential versions of SSTL and HSTL standards.

For detailed information on differential I/O standards, refer to the High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II Device Handbook or High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook.

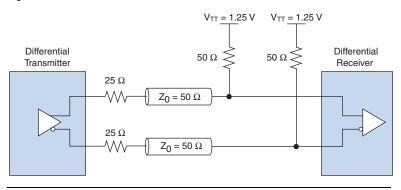

#### Differential SSTL-2 Class I and Differential SSTL-2 Class II

The 2.5-V differential SSTL-2 standard is formulated under JEDEC Standard, JESD8-9A: Stub Series Terminated Logic for 2.5-V (SSTL\_2).

This I/O standard is a 2.5-V standard used for applications such as high-speed DDR SDRAM clock interfaces. This standard supports differential signals in systems using the SSTL-2 standard and supplements the SSTL-2 standard for differential clocks. Stratix II and Stratix II GX devices support both input and output levels. Figures 10–10 and 10–11 shows details on differential SSTL-2 termination.

Stratix II and Stratix II GX devices support differential SSTL-2 I/O standards in pseudo-differential mode, which is implemented by using two SSTL-2 single-ended buffers.

The Quartus II software only supports pseudo-differential standards on the INCLK, FBIN and EXTCLK ports of enhanced PLL, as well as on DQS pins when DQS megafunction (ALTDQS, Bidirectional Data Strobe) is used. Two single-ended output buffers are automatically programmed to have opposite polarity so as to implement a pseudo-differential output. A proper  $V_{\rm REF}$  voltage is required for the two single-ended input buffers to implement a pseudo-differential input. In this case, only the positive polarity input is used in the speed path while the negative input is not connected internally. In other words, only the non-inverted pin is required to be specified in your design, while the Quartus II software automatically generates the inverted pin for you.

Although the Quartus II software does not support pseudo-differential SSTL-2 I/O standards on the left and right I/O banks, you can implement these standards at these banks. You need to create two pins in the designs and configure the pins with single-ended SSTL-2 standards. However, this is limited only to pins that support the differential pin-pair I/O function and is dependent on the single-ended SSTL-2 standards support at these banks.

Figure 10-10. Differential SSTL-2 Class I Termination

Figure 10-11. Differential SSTL-2 Class II Termination

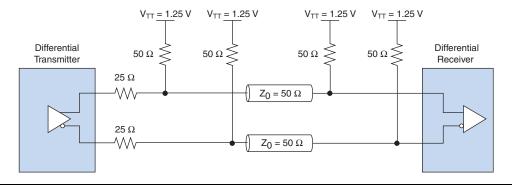

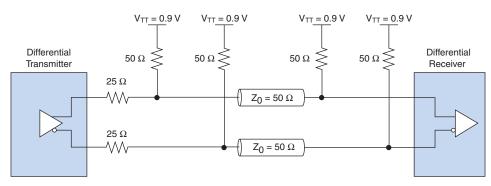

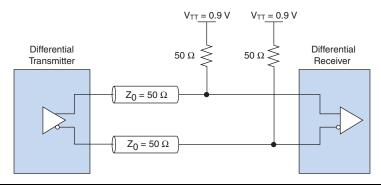

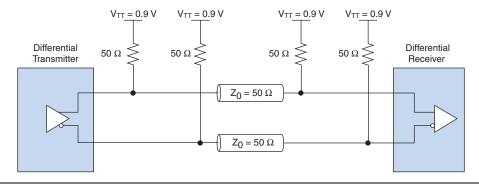

#### Differential SSTL-18 Class I and Differential SSTL-18 Class II

The 1.8-V differential SSTL-18 standard is formulated under JEDEC Standard, JESD8-15: Stub Series Terminated Logic for 1.8-V (SSTL 18).

The differential SSTL-18 I/O standard is a 1.8-V standard used for applications such as high-speed DDR2 SDRAM interfaces. This standard supports differential signals in systems using the SSTL-18 standard and supplements the SSTL-18 standard for differential clocks.

Stratix II and Stratix II GX devices support both input and output levels operation.

Figures 10–12 and 10–13 shows details on differential SSTL-18 termination. Stratix II and Stratix II GX devices support differential SSTL-18 I/O standards in pseudo-differential mode, which is implemented by using two SSTL-18 single-ended buffers.

The Quartus II software only supports pseudo-differential standards on the INCLK, FBIN and EXTCLK ports of enhanced PLL, as well as on DQS pins when DQS megafunction (ALTDQS, Bidirectional Data Strobe) is used. Two single-ended output buffers are automatically programmed to have opposite polarity so as to implement a pseudo-differential output. A proper  $V_{REF}$  voltage is required for the two single-ended input buffers to implement a pseudo-differential input. In this case, only the positive polarity input is used in the speed path while the negative input is not connected internally. In other words, only the non-inverted pin is required to be specified in your design, while the Quartus II software automatically generates the inverted pin for you.

Although the Quartus II software does not support pseudo-differential SSTL-18 I/O standards on the left and right I/O banks, you can implement these standards at these banks. You need to create two pins in the designs and configure the pins with single-ended SSTL-18 standards. However, this is limited only to pins that support the differential pin-pair I/O function and is dependent on the single-ended SSTL-18 standards support at these banks.

Differential Transmitter  $\begin{array}{c} V_{TT}=0.9\,V \\ 50\,\Omega \end{array} \begin{array}{c} Differential \\ Receiver \end{array}$

Figure 10-12. Differential SSTL-18 Class I Termination

Figure 10-13. Differential SSTL-18 Class II Termination

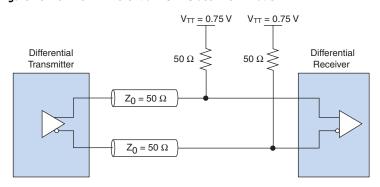

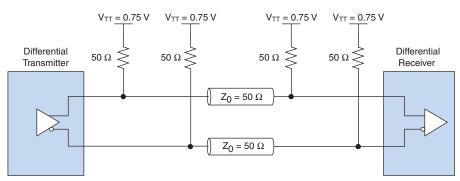

#### 1.8-V Differential HSTL Class I and 1.8-V Differential HSTL Class II

The 1.8-V differential HSTL specification is the same as the 1.8-V single-ended HSTL specification. It is used for applications designed to operate in the 0.0- to 1.8-V HSTL logic switching range such as QDR memory clock interfaces. Stratix II and Stratix II GX devices support both input and output levels operation. Figures 10–14 and 10–15 show details on 1.8-V differential HSTL termination.

Stratix II and Stratix II GX devices support 1.8-V differential HSTL I/O standards in pseudo-differential mode, which is implemented by using two 1.8-V HSTL single-ended buffers.

The Quartus II software only supports pseudo-differential standards on the INCLK, FBIN and EXTCLK ports of enhanced PLL, as well as on DQS pins when DQS megafunction (ALTDQS, Bidirectional Data Strobe) is used. Two single-ended output buffers are automatically programmed to have opposite polarity so as to implement a pseudo-differential output. A proper  $V_{\rm REF}$  voltage is required for the two single-ended input buffers to implement a pseudo-differential input. In this case, only the positive polarity input is used in the speed path while the negative input is not connected internally. In other words, only the non-inverted pin is required to be specified in your design, while the Quartus II software automatically generates the inverted pin for you.

Although the Quartus II software does not support 1.8-V pseudo-differential HSTL I/O standards on left/right I/O banks, you can implement these standards at these banks. You need to create two pins in the designs and configure the pins with single-ended 1.8-V HSTL standards. However, this is limited only to pins that support the differential pin-pair I/O function and is dependent on the single-ended 1.8-V HSTL standards support at these banks.

Figure 10-14. 1.8-V Differential HSTL Class I Termination

Figure 10–15. 1.8-V Differential HSTL Class II Termination

#### 1.5-V Differential HSTL Class I and 1.5-V Differential HSTL Class II

The 1.5-V differential HSTL standard is formulated under EIA/JEDEC Standard, EIA/JESD8-6: A 1.5-V Output Buffer Supply Voltage Based Interface Standard for Digital Integrated Circuits.

The 1.5-V differential HSTL specification is the same as the 1.5-V single-ended HSTL specification. It is used for applications designed to operate in the 0.0- to 1.5-V HSTL logic switching range, such as QDR memory clock interfaces. Stratix II and Stratix II GX devices support both input and output levels operation. Figures 10–16 and 10–17 show details on the 1.5-V differential HSTL termination.

Stratix II and Stratix II GX devices support 1.5-V differential HSTL I/O standards in pseudo-differential mode, which is implemented by using two 1.5-V HSTL single-ended buffers.

The Quartus II software only supports pseudo-differential standards on the INCLK, FBIN and EXTCLK ports of enhanced PLL, as well as on DQS pins when DQS megafunction (ALTDQS, Bidirectional Data Strobe) is used. Two single-ended output buffers are automatically programmed to have opposite polarity so as to implement a pseudo-differential output. A proper  $V_{\rm REF}$  voltage is required for the two single-ended input buffers to implement a pseudo-differential input. In this case, only the positive polarity input is used in the speed path while the negative input is not connected internally. In other words, only the non-inverted pin is required to be specified in your design, while the Quartus II software automatically generates the inverted pin for you.

Although the Quartus II software does not support 1.5-V pseudo-differential HSTL I/O standards on left/right I/O banks, you can implement these standards at these banks. You need to create two pins in the designs and configure the pins with single-ended 1.5-V HSTL standards. However, this is limited only to pins that support the differential pin-pair I/O function and is dependent on the single-ended 1.8-V HSTL standards support at these banks.

Figure 10-16. 1.5-V Differential HSTL Class I Termination

Figure 10–17. 1.5-V Differential HSTL Class II Termination

#### LVDS

The LVDS standard is formulated under ANSI/TIA/EIA Standard, ANSI/TIA/EIA-644: Electrical Characteristics of Low Voltage Differential Signaling Interface Circuits.

The LVDS I/O standard is a differential high-speed, low-voltage swing, low-power, general-purpose I/O interface standard. In Stratix II devices, the LVDS I/O standard requires a 2.5-V  $V_{CCIO}$  level for the side I/O pins in banks 1, 2, 5, and 6. The top and bottom banks have different  $V_{CCIO}$ requirements for the LVDS I/O standard. The LVDS clock I/O pins in banks 9 through 12 require a 3.3-V V<sub>CCIO</sub> level. Within these banks, the PLL [5,6,11,12] OUT [1,2] pins support output only LVDS operations. The PLL [5, 6, 11, 12] FB/OUT2 pins support LVDS input or output operations but cannot be configured for bidirectional LVDS operations. The LVDS clock input pins in banks 4, 5, 7, and 8 use V<sub>CCINT</sub> and have no dependency on the  $V_{CCIO}$  voltage level. This standard is used in applications requiring high-bandwidth data transfer, backplane drivers, and clock distribution. The ANSI/TIA/EIA-644 standard specifies LVDS transmitters and receivers capable of operating at recommended maximum data signaling rates of 655 megabit per second (Mbps). However, devices can operate at slower speeds if needed, and there is a theoretical maximum of 1.923 Gbps. Stratix II and Stratix II GX devices are capable of running at a maximum data rate of 1 Gbps and still meet the ANSI/TIA/EIA-644 standard.

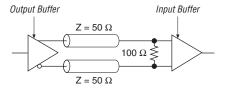

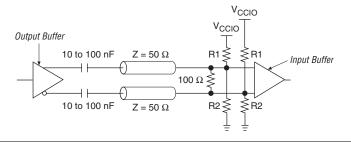

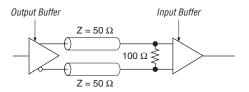

Because of the low-voltage swing of the LVDS I/O standard, the electromagnetic interference (EMI) effects are much smaller than complementary metal-oxide semiconductor (CMOS), transistor-to-transistor logic (TTL), and positive (or psuedo) emitter coupled logic (PECL). This low EMI makes LVDS ideal for applications

with low EMI requirements or noise immunity requirements. The LVDS standard does not require an input reference voltage. However, it does require a  $100\text{-}\Omega$  termination resistor between the two signals at the input buffer. Stratix II and Stratix II GX devices provide an optional  $100\text{-}\Omega$  differential LVDS termination resistor in the device using on-chip differential termination. Stratix II and Stratix II GX devices support both input and output levels operation.

#### Differential I VPFCI

The low-voltage positive (or pseudo) emitter coupled logic (LVPECL) standard is a differential interface standard requiring a 3.3-V  $\rm V_{CCIO}$ . The standard is used in applications involving video graphics, telecommunications, data communications, and clock distribution. The high-speed, low-voltage swing LVPECL I/O standard uses a positive power supply and is similar to LVDS. However, LVPECL has a larger differential output voltage swing than LVDS. The LVPECL standard does not require an input reference voltage, but it does require a  $100\text{-}\Omega$  termination resistor between the two signals at the input buffer. Figures 10--18 and 10--19 show two alternate termination schemes for LVPECL.

Stratix II and Stratix II GX devices support both input and output levels operation.

Figure 10–18. LVPECL DC Coupled Termination

Figure 10–19. LVPECL AC Coupled Termination

#### HyperTransport Technology

The HyperTransport standard is formulated by the HyperTransport Consortium.

The HyperTransport I/O standard is a differential high-speed, high-performance I/O interface standard requiring a 2.5- or 3.3-V  $V_{\rm CCIO}$ . This standard is used in applications such as high-performance networking, telecommunications, embedded systems, consumer electronics, and Internet connectivity devices. The HyperTransport I/O standard is a point-to-point standard in which each HyperTransport bus consists of two point-to-point unidirectional links. Each link is 2 to 32 bits.

The HyperTransport standard does not require an input reference voltage. However, it does require a  $100\text{-}\Omega$  termination resistor between the two signals at the input buffer. Figure 10--20 shows HyperTransport termination. Stratix II and Stratix II GX devices include an optional  $100\text{-}\Omega$  differential HyperTransport termination resistor in the device using on-chip differential termination.

Stratix II and Stratix II GX devices support both input and output levels operation.

Figure 10-20. HyperTransport Termination

# Stratix II and Stratix II GX External Memory Interface

The increasing demand for higher-performance data processing systems often requires memory-intensive applications. Stratix II and Stratix II GX devices can interface with many types of external memory.

Refer to the *External Memory Interfaces in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *External Memory Interfaces in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook* for more information on the external memory interface support in Stratix II or Stratix II GX devices.

# Stratix II and Stratix II GX I/O Banks

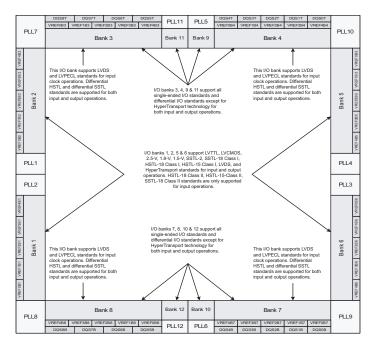

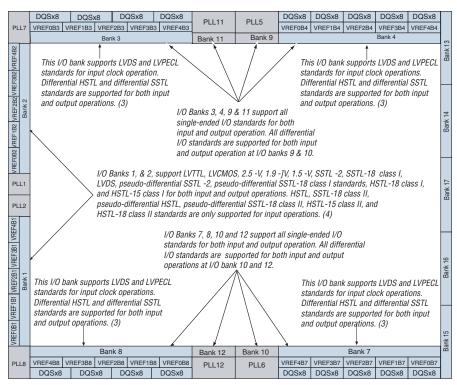

Stratix II devices have eight general I/O banks and four enhanced phase-locked loop (PLL) external clock output banks (Figure 10–21). I/O banks 1, 2, 5, and 6 are on the left or right sides of the device and I/O banks 3, 4, and 7 through 12 are at the top or bottom of the device.

**Figure 10–21. Stratix II I/O Banks** Notes (1), (2), (3), (4), (5), (6), (7)

#### Notes to Figure 10-21:

- (1) Figure 10–21 is a top view of the silicon die that corresponds to a reverse view for flip-chip packages. It is a graphical representation only. Refer to the pin list and Quartus II software for exact locations.

- Depending on the size of the device, different device members have different numbers of V<sub>REF</sub> groups.

- (3) Banks 9 through 12 are enhanced PLL external clock output banks. These PLL banks utilize the adjacent  $V_{REF}$  group when voltage-referenced standards are implemented. For example, if an SSTL input is implemented in PLL bank 10, the voltage level at VREFB7 is the reference voltage level for the SSTL input.

- (4) Differential HSTL and differential SSTL standards are available for bidirectional operations on DQS pin and input-only operations on PLL clock input pins; LVDS, LVPECL, and HyperTransport standards are available for input-only operations on PLL clock input pins. Refer to the "Differential I/O Standards" on page 10–10 for more details.

- (5) Quartus II software does not support differential SSTL and differential HSTL standards at left/right I/O banks. Refer to the "Differential I/O Standards" on page 10–10 if you need to implement these standards at these I/O banks.

- (6) Banks 11 and 12 are available only in EP2S60, EP2S90, EP2S130, and EP2S180 devices.

- (7) PLLs 7, 8, 9 10, 11, and 12 are available only in EP2S60, EP2S90, EP2S130, and EP2S180 devices.

Stratix II GX devices have 6 general I/O banks and 4 enhanced phase-locked loop (PLL) external clock output banks (Figure 10–22). I/O banks 9 through 12 are enhanced PLL external clock output banks located on the top and bottom of the device.

Figure 10-22. Stratix II GX I/O Banks Notes (1), (2), (3), (4)

#### *Notes to Figure 10–22:*

- (1) Figure 10–22 is a top view of the silicon die which corresponds to a reverse view for flip-chip packages. It is a graphical representation only.

- (2) Depending on size of the device, different device members have different number of  $V_{REF}$  groups. Refer to the pin list and the Quartus II software for exact locations.

- (3) Banks 9 through 12 are enhanced PLL external clock output banks.

- (4) Horizontal I/O banks feature transceiver and DPA circuitry for high speed differential I/O standards. Refer to the High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook, or the Stratix II GX Transceiver User Guide (volume 1) of the Stratix II GX Device Handbook for more information on differential I/O standards.

- (5) Quartus II software does not support differential SSTL and differential HSTL standards at left/right I/O banks. Refer to the "Differential I/O Standards" on page 10–10 if you need to implement these standards at these I/O banks.

- (6) Banks 11 and 12 are available only in EP2SGX60C/D/E, EP2SGX90E/F, and EP2SGX130G.

- (7) PLLs 7,8,11, and 12 are available only in EP2SGX60C/D/E, EP2SGXE/F, and EP2SGX130G.

#### Programmable I/O Standards

Stratix II and Stratix II GX device programmable I/O standards deliver high-speed and high-performance solutions in many complex design systems. This section discusses the I/O standard support in the I/O banks of Stratix II and Stratix II GX devices.

#### Regular I/O Pins

Most Stratix II and Stratix II GX device pins are multi-function pins. These pins support regular inputs and outputs as their primary function, and offer an optional function such as DQS, differential pin-pair, or PLL external clock outputs. For example, you can configure a multi-function pin in the enhanced PLL external clock output bank as a PLL external clock output when it is not used as a regular I/O pin.

I/O pins that reside in PLL banks 9 through 12 are powered by the VCC\_PLL<5, 6, 11, or 12>\_OUT pins, respectively. The EP2S60F484, EP2S60F780, EP2S90H484, EP2S90F780, and EP2S130F780 devices do not support PLLs 11 and 12. Therefore, any I/O pins that reside in bank 11 are powered by the VCCIO3 pin, and any I/O pins that reside in bank 12 are powered by the VCCIO8 pin.

Table 10–2 shows the I/O standards supported when a pin is used as a regular I/O pin in the I/O banks of Stratix II and Stratix II GX devices.

| I/O Standard    |          | General I/O Bank |          |          |              |          |          |          |          | Enhanced PLL External<br>Clock Output Bank (2) |          |          |  |

|-----------------|----------|------------------|----------|----------|--------------|----------|----------|----------|----------|------------------------------------------------|----------|----------|--|

|                 | 1        | 2                | 3        | 4        | <b>5</b> (1) | 6(1)     | 7        | 8        | 9        | 10                                             | 11       | 12       |  |

| LVTTL           | <b>✓</b> | <b>✓</b>         | <b>✓</b> | <b>✓</b> | <b>✓</b>     | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> |  |

| LVCMOS          | ~        | <b>✓</b>         | <b>✓</b> | <b>✓</b> | <b>✓</b>     | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> |  |

| 2.5 V           | <b>✓</b> | <b>✓</b>         | <b>✓</b> | <b>✓</b> | <b>✓</b>     | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>\</b>                                       | <b>✓</b> | <b>✓</b> |  |

| 1.8 V           | <b>✓</b> | ~                | <b>~</b> | <b>✓</b> | <b>✓</b>     | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>\</b>                                       | <b>✓</b> | <b>✓</b> |  |

| 1.5 V           | <b>✓</b> | ~                | <b>~</b> | <b>✓</b> | <b>✓</b>     | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>\</b>                                       | <b>✓</b> | <b>✓</b> |  |

| 3.3-V PCI       |          |                  | <b>✓</b> | ~        |              |          | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> |  |

| 3.3-V PCI-X     |          |                  | ~        | <b>✓</b> |              |          | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>\</b>                                       | ~        | <b>~</b> |  |

| SSTL-2 Class I  | ~        | <b>✓</b>         | <b>✓</b> | <b>✓</b> | <b>✓</b>     | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> |  |

| SSTL-2 Class II | <b>✓</b> | <b>✓</b>         | <b>✓</b> | <b>✓</b> | <b>✓</b>     | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> |  |

| Table 10–2. Stratix II and Stratix II GX Regular I/O Standards Support (Part 2 of 2) |                  |          |          |          |          |          |          |          |                                                |          |          |          |

|--------------------------------------------------------------------------------------|------------------|----------|----------|----------|----------|----------|----------|----------|------------------------------------------------|----------|----------|----------|

| I/O Standard                                                                         | General I/O Bank |          |          |          |          |          |          |          | Enhanced PLL External<br>Clock Output Bank (2) |          |          |          |

|                                                                                      | 1                | 2        | 3        | 4        | 5(1)     | 6(1)     | 7        | 8        | 9                                              | 10       | 11       | 12       |

| SSTL-18 Class I                                                                      | <b>✓</b>         | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| SSTL-18 Class II                                                                     | (3)              | (3)      | <b>✓</b> | <b>✓</b> | (3)      | (3)      | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| 1.8-V HSTL Class I                                                                   | <b>✓</b>         | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| 1.8-V HSTL Class II                                                                  | (3)              | (3)      | <b>✓</b> | <b>✓</b> | (3)      | (3)      | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| 1.5-V HSTL Class I                                                                   | <b>✓</b>         | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| 1.5-V HSTL Class II                                                                  | (3)              | (3)      | <b>✓</b> | <b>✓</b> | (3)      | (3)      | <b>✓</b> | <b>✓</b> | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| 1.2-V HSTL                                                                           |                  |          |          | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |                                                |          |          |          |

| Differential SSTL-2 Class I                                                          | (4)              | (4)      | (5)      | (5)      | (4)      | (4)      | (5)      | (5)      |                                                |          |          |          |

| Differential SSTL-2 Class II                                                         | (4)              | (4)      | (5)      | (5)      | (4)      | (4)      | (5)      | (5)      |                                                |          |          |          |

| Differential SSTL-18 Class I                                                         | (4)              | (4)      | (5)      | (5)      | (4)      | (4)      | (5)      | (5)      |                                                |          |          |          |

| Differential SSTL-18 Class II                                                        | (4)              | (4)      | (5)      | (5)      | (4)      | (4)      | (5)      | (5)      |                                                |          |          |          |

| 1.8-V differential HSTL Class I                                                      | (4)              | (4)      | (5)      | (5)      | (4)      | (4)      | (5)      | (5)      |                                                |          |          |          |

| 1.8-V differential HSTL Class II                                                     | (4)              | (4)      | (5)      | (5)      | (4)      | (4)      | (5)      | (5)      |                                                |          |          |          |

| 1.5-V differential HSTL Class I                                                      | (4)              | (4)      | (5)      | (5)      | (4)      | (4)      | (5)      | (5)      |                                                |          |          |          |

| 1.5-V differential HSTL Class II                                                     | (4)              | (4)      | (5)      | (5)      | (4)      | (4)      | (5)      | (5)      |                                                |          |          |          |

| LVDS                                                                                 | <b>✓</b>         | <b>✓</b> | (6)      | (6)      | <b>✓</b> | <b>✓</b> | (6)      | (6)      | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| HyperTransport technology                                                            | <b>✓</b>         | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |                                                |          |          |          |

| Differential LVPECL                                                                  |                  |          | (6)      | (6)      |          |          | (6)      | (6)      | <b>✓</b>                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |

#### *Notes to Table 10–2:*

- (1) This bank is not available in Stratix II GX Devices.

- (2) A mixture of single-ended and differential I/O standards is not allowed in enhanced PLL external clock output bank.

- (3) This I/O standard is only supported for the input operation in this I/O bank.

- (4) Although the Quartus II software does not support pseudo-differential SSTL/HSTL I/O standards on the left and right I/O banks, you can implement these standards at these banks. Refer to the "Differential I/O Standards" on page 10–10 for details.

- (5) This I/O standard is supported for both input and output operations for pins that support the DQS function. Refer to the "Differential I/O Standards" on page 10–10 for details.

- (6) This I/O standard is only supported for the input operation for pins that support PLL INCLK function in this I/O bank.

#### Clock I/O Pins

The PLL clock I/O pins consist of clock inputs (INCLK), external feedback inputs (FBIN), and external clock outputs (EXTCLK). Clock inputs are located at the left and right I/O banks (banks 1, 2, 5, and 6) to support fast PLLs, and at the top and bottom I/O banks (banks 3, 4, 7, and 8) to support enhanced PLLs. Both external clock outputs and external feedback inputs are located at enhanced PLL external clock output banks (banks 9, 10, 11, and 12) to support enhanced PLLs. Table 10–3 shows the PLL clock I/O support in the I/O banks of Stratix II and Stratix II GX devices.

|                               |          | Enhanced PLL (1) |          |          |  |  |  |

|-------------------------------|----------|------------------|----------|----------|--|--|--|

| I/O Standard (2)              | Ir       | ıput             | Output   | Input    |  |  |  |

|                               | INCLK    | FBIN             | EXTCLK   | INCLK    |  |  |  |

| LVTTL                         | <b>✓</b> | ✓                | ✓        | <b>✓</b> |  |  |  |

| LVCMOS                        | ✓        | <b>✓</b>         | ✓        | <b>✓</b> |  |  |  |

| 2.5 V                         | ✓        | <b>✓</b>         | ✓        | <b>✓</b> |  |  |  |

| 1.8 V                         | ✓        | <b>✓</b>         | ✓        | <b>✓</b> |  |  |  |

| 1.5 V                         | ✓        | <b>✓</b>         | ✓        | <b>✓</b> |  |  |  |

| 3.3-V PCI                     | ✓        | <b>✓</b>         | ✓        |          |  |  |  |

| 3.3-V PCI-X                   | ✓        | ✓                | ✓        |          |  |  |  |

| SSTL-2 Class I                | ✓        | <b>✓</b>         | ✓        | <b>✓</b> |  |  |  |

| SSTL-2 Class II               | ✓        | <b>✓</b>         | ✓        | <b>✓</b> |  |  |  |

| SSTL-18 Class I               | ✓        | ✓                | ✓        | ✓        |  |  |  |

| SSTL-18 Class II              | ✓        | ✓                | ✓        | ✓        |  |  |  |

| 1.8-V HSTL Class I            | ✓        | <b>✓</b>         | ✓        | <b>✓</b> |  |  |  |

| 1.8-V HSTL Class II           | ✓        | ✓                | ✓        | ✓        |  |  |  |

| 1.5-V HSTL Class I            | ✓        | <b>✓</b>         | ✓        | <b>✓</b> |  |  |  |

| 1.5-V HSTL Class II           | <b>✓</b> | <b>✓</b>         | ✓        | <b>✓</b> |  |  |  |

| Differential SSTL-2 Class I   | <b>✓</b> | <b>✓</b>         | ✓        |          |  |  |  |

| Differential SSTL-2 Class II  | ✓        | <b>✓</b>         | ✓        |          |  |  |  |

| Differential SSTL-18 Class I  | <b>✓</b> | <b>✓</b>         | ✓        |          |  |  |  |

| Differential SSTL-18 Class II | <b>✓</b> | <b>✓</b>         | <b>✓</b> |          |  |  |  |

|                                  | I        | Enhanced PLL ( | 1)       | Fast PLL |  |

|----------------------------------|----------|----------------|----------|----------|--|

| I/O Standard (2)                 | In       | put            | Output   | Input    |  |

|                                  | INCLK    | FBIN           | EXTCLK   | INCLK    |  |

| 1.8-V differential HSTL Class I  | <b>✓</b> | ✓              | ✓        |          |  |

| 1.8-V differential HSTL Class II | ✓        | ✓              | ✓        |          |  |

| 1.5-V differential HSTL Class I  | ✓        | ✓              | ✓        |          |  |

| 1.5-V differential HSTL Class II | ✓        | ✓              | ✓        |          |  |

| LVDS                             | <b>✓</b> | ✓              | ✓        | <b>✓</b> |  |

| HyperTransport technology        |          |                |          | <b>✓</b> |  |

| Differential LVPECL              | <b>✓</b> | <b>✓</b>       | <b>✓</b> |          |  |

#### Note to Table 10-3:

- The enhanced PLL external clock output bank does not allow a mixture of both single-ended and differential I/O standards.

- (2) Altera does not support 1.2-V HSTL for PLL input pins on column I/O pins.

For more information, refer to the *PLLs in Stratix II & Stratix II GX*Devices chapter in volume 2 of the *Stratix II Device Handbook* or the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II GX Device Handbook*.

#### Voltage Levels

Stratix II device specify a range of allowed voltage levels for supported I/O standards. Table 10–4 shows only typical values for input and output  $V_{\rm CCIO}$ ,  $V_{\rm REF}$ , as well as the board  $V_{\rm TT}$ .

| Table 10–4. Stratix II and Stratix II GX I/O Standards and Voltage Levels (Part 1 of 3) Note (1) |                                |                                    |                                |                                   |       |             |  |  |  |  |

|--------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------|--------------------------------|-----------------------------------|-------|-------------|--|--|--|--|

|                                                                                                  | Stratix II and Stratix II GX   |                                    |                                |                                   |       |             |  |  |  |  |

|                                                                                                  |                                | V <sub>cci</sub>                   | V <sub>REF</sub> (V)           | V <sub>TT</sub> (V)               |       |             |  |  |  |  |

| I/O Standard                                                                                     | Input Op                       | eration                            | Output O                       | peration                          |       |             |  |  |  |  |

|                                                                                                  | Top and<br>Bottom I/O<br>Banks | Left and<br>Right I/O<br>Banks (3) | Top and<br>Bottom I/O<br>Banks | Left and<br>Right I/O<br>Banks(3) | Input | Termination |  |  |  |  |

| LVTTL                                                                                            | 3.3/2.5                        | 3.3/2.5                            | 3.3                            | 3.3                               | NA    | NA          |  |  |  |  |

| LVCMOS                                                                                           | 3.3/2.5                        | 3.3/2.5                            | 3.3                            | 3.3                               | NA    | NA          |  |  |  |  |

|                                         | Stratix II and Stratix II GX   |                                    |                                |                                   |       |             |  |  |  |  |

|-----------------------------------------|--------------------------------|------------------------------------|--------------------------------|-----------------------------------|-------|-------------|--|--|--|--|

|                                         |                                | V <sub>REF</sub> (V)               | V <sub>TT</sub> (V)            |                                   |       |             |  |  |  |  |

| I/O Standard                            | Input Op                       | eration                            | Output O                       | peration                          |       |             |  |  |  |  |

| , , , , , , , , , , , , , , , , , , , , | Top and<br>Bottom I/O<br>Banks | Left and<br>Right I/O<br>Banks (3) | Top and<br>Bottom I/O<br>Banks | Left and<br>Right I/O<br>Banks(3) | Input | Termination |  |  |  |  |

| 2.5 V                                   | 3.3/2.5                        | 3.3/2.5                            | 2.5                            | 2.5                               | NA    | NA          |  |  |  |  |

| 1.8 V                                   | 1.8/1.5                        | 1.8/1.5                            | 1.8                            | 1.8                               | NA    | NA          |  |  |  |  |

| 1.5 V                                   | 1.8/1.5                        | 1.8/1.5                            | 1.5                            | 1.5                               | NA    | NA          |  |  |  |  |

| 3.3-V PCI                               | 3.3                            | NA                                 | 3.3                            | NA                                | NA    | NA          |  |  |  |  |

| 3.3-V PCI-X                             | 3.3                            | NA                                 | 3.3                            | NA                                | NA    | NA          |  |  |  |  |

| SSTL-2 Class I                          | 2.5                            | 2.5                                | 2.5                            | 2.5                               | 1.25  | 1.25        |  |  |  |  |

| SSTL-2 Class II                         | 2.5                            | 2.5                                | 2.5                            | 2.5                               | 1.25  | 1.25        |  |  |  |  |

| SSTL-18 Class I                         | 1.8                            | 1.8                                | 1.8                            | 1.8                               | 0.90  | 0.90        |  |  |  |  |

| SSTL-18 Class II                        | 1.8                            | 1.8                                | 1.8                            | NA                                | 0.90  | 0.90        |  |  |  |  |

| 1.8-V HSTL Class I                      | 1.8                            | 1.8                                | 1.8                            | 1.8                               | 0.90  | 0.90        |  |  |  |  |

| 1.8-V HSTL Class II                     | 1.8                            | 1.8                                | 1.8                            | NA                                | 0.90  | 0.90        |  |  |  |  |

| 1.5-V HSTL Class I                      | 1.5                            | 1.5                                | 1.5                            | 1.5                               | 0.75  | 0.75        |  |  |  |  |

| 1.5-V HSTL Class II                     | 1.5                            | 1.5                                | 1.5                            | NA                                | 0.75  | 0.75        |  |  |  |  |

| 1.2-V HSTL(4)                           | 1.2                            | NA                                 | 1.2                            | NA                                | 0.6   | NA          |  |  |  |  |

| Differential SSTL-2<br>Class I          | 2.5                            | 2.5                                | 2.5                            | 2.5                               | 1.25  | 1.25        |  |  |  |  |

| Differential SSTL-2<br>Class II         | 2.5                            | 2.5                                | 2.5                            | 2.5                               | 1.25  | 1.25        |  |  |  |  |

| Differential SSTL-18<br>Class I         | 1.8                            | 1.8                                | 1.8                            | 1.8                               | 0.90  | 0.90        |  |  |  |  |

| Differential SSTL-18<br>Class II        | 1.8                            | 1.8                                | 1.8                            | NA                                | 0.90  | 0.90        |  |  |  |  |

| 1.8-V differential<br>HSTL Class I      | 1.8                            | 1.8                                | 1.8                            | NA                                | 0.90  | 0.90        |  |  |  |  |

| 1.8-V differential<br>HSTL Class II     | 1.8                            | 1.8                                | 1.8                            | NA                                | 0.90  | 0.90        |  |  |  |  |

| 1.5-V differential<br>HSTL Class I      | 1.5                            | 1.5                                | 1.5                            | NA                                | 0.75  | 0.75        |  |  |  |  |

| 1.5-V differential<br>HSTL Class II     | 1.5                            | 1.5                                | 1.5                            | NA                                | 0.75  | 0.75        |  |  |  |  |

| LVDS (2)                                | 3.3/2.5/1.8/1.5                | 2.5                                | 3.3                            | 2.5                               | NA    | NA          |  |  |  |  |

| Table 10–4. Stratix       | II and Stratix II G            | GX I/O Standar                     | ds and Voltage                 | Levels (Part 3                    | of 3) Note | (1)         |  |

|---------------------------|--------------------------------|------------------------------------|--------------------------------|-----------------------------------|------------|-------------|--|

|                           |                                |                                    | Stratix II and S               | tratix II GX                      |            |             |  |

|                           |                                | V <sub>CCIO</sub>                  | V <sub>REF</sub> (V)           | V <sub>TT</sub> (V)               |            |             |  |

| I/O Standard              | Input Ope                      | eration                            | Output O                       | peration                          |            |             |  |

|                           | Top and<br>Bottom I/O<br>Banks | Left and<br>Right I/O<br>Banks (3) | Top and<br>Bottom I/O<br>Banks | Left and<br>Right I/O<br>Banks(3) | Input      | Termination |  |

| HyperTransport technology | NA                             | 2.5                                | NA                             | 2.5                               | NA         | NA          |  |

| Differential LVPECL (2)   | 3.3/2.5/1.8/1.5                | NA                                 | 3.3                            | NA                                | NA         | NA          |  |

#### Notes to Table 10-4:

- (1) Any input pins with PCI-clamping diode will clamp the  $V_{CCIO}$  to 3.3 V.

- (2) LVDS and LVPECL output operation in the top and bottom banks is only supported in PLL banks 9-12. The  $V_{\rm CCIO}$  level for differential output operation in the PLL banks is 3.3 V. The  $V_{\rm CCIO}$  level for output operation in the left and right I/O banks is 2.5 V.

- (3) The right I/O bank does not apply to the Stratix II GX. The right I/O Bank on Stratix II GX devices consists of transceivers.

- (4) 1.2-V HSTL is only supported in I/O banks 4,7, and 8.

Refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook* or the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook* for detailed electrical characteristics of each I/O standard.

## On-Chip Termination

Stratix II and Stratix II GX devices feature on-chip termination to provide I/O impedance matching and termination capabilities. Apart from maintaining signal integrity, this feature also minimizes the need for external resistor networks, thereby saving board space and reducing costs.

Stratix II and Stratix II GX devices support on-chip series ( $R_S$ ) and parallel ( $R_T$ ) termination for single-ended I/O standards and on-chip differential termination ( $R_D$ ) for differential I/O standards. This section discusses the on-chip series termination support.

For more information on differential on-chip termination, Refer to the High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II Device Handbook or the High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices chapter in volume 2 of the Stratix II GX Device Handbook.

The Stratix II and Stratix II GX devices supports I/O driver on-chip series  $(R_S)$  and parallel  $(R_T)$  termination through drive strength control for single-ended I/Os. There are three ways to implement the  $R_S$  and  $(R_T)$  in Stratix II and Stratix II GX devices:

- R<sub>S</sub> without calibration for both row I/Os and column I/Os

- $\blacksquare$  R<sub>S</sub> with calibration only for column I/Os

- $\blacksquare$  R<sub>T</sub> with calibration only for column I/Os

#### **On-Chip Series Termination without Calibration**

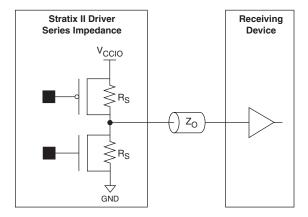

Stratix II and Stratix II GX devices support driver impedance matching to provide the I/O driver with controlled output impedance that closely matches the impedance of the transmission line. As a result, reflections can be significantly reduced. Stratix II and Stratix II GX devices support on-chip series termination for single-ended I/O standards (see Figure 10–23). The  $R_{\rm S}$  shown in Figure 10–23 is the intrinsic impedance of transistors. The typical  $R_{\rm S}$  values are  $25\Omega$  and  $50\Omega$  Once matching impedance is selected, current drive strength is no longer selectable.

On-chip series termination without calibration is supported on output pins or on the output function of bidirectional pins.

Figure 10–23. Stratix II and Stratix II GX On-Chip Series Termination without Calibration

Table 10–5 shows the list of output standards that support on-chip series termination without calibration.

| I/O Ctondord        | On-chip Series Termination Setting |            |      |  |  |  |  |

|---------------------|------------------------------------|------------|------|--|--|--|--|

| I/O Standard        | Row I/O                            | Column I/O | Unit |  |  |  |  |

| 3.3-V LVTTL         | 50                                 | 50         | Ω    |  |  |  |  |

|                     | 25                                 | 25         | Ω    |  |  |  |  |

| 3.3-V LVCMOS        | 50                                 | 50         | Ω    |  |  |  |  |

|                     | 25                                 | 25         | Ω    |  |  |  |  |

| 2.5-V LVTTL         | 50                                 | 50         | Ω    |  |  |  |  |

|                     | 25                                 | 25         | Ω    |  |  |  |  |

| 2.5-V LVCMOS        | 50                                 | 50         | Ω    |  |  |  |  |

|                     | 25                                 | 25         | Ω    |  |  |  |  |

| 1.8-V LVTTL         | 50                                 | 50         | Ω    |  |  |  |  |

|                     |                                    | 25         | Ω    |  |  |  |  |

| 1.8-V LVCMOS        | 50                                 | 50         | Ω    |  |  |  |  |

|                     |                                    | 25         | Ω    |  |  |  |  |

| 1.5-V LVTTL         | 50                                 | 50         | Ω    |  |  |  |  |

| 1.5-V LVCMOS        | 50                                 | 50         | Ω    |  |  |  |  |

| SSTL-2 Class I      | 50                                 | 50         | Ω    |  |  |  |  |

| SSTL-2 Class II     | 25                                 | 25         | Ω    |  |  |  |  |

| SSTL-18 Class I     | 50                                 | 50         | Ω    |  |  |  |  |

| SSTL-18 Class II    |                                    | 25         | Ω    |  |  |  |  |

| 1.8-V HSTL Class I  | 50                                 | 50         | Ω    |  |  |  |  |

| 1.8-V HSTL Class II |                                    | 25         | Ω    |  |  |  |  |

| 1.5-V HSTL Class I  | 50                                 | 50         | Ω    |  |  |  |  |

| 1.2-V HSTL (1)      |                                    | 50         | Ω    |  |  |  |  |

|                     |                                    |            |      |  |  |  |  |

Note to Table 10-5:

To use on-chip termination for the SSTL Class I standard, users should select the  $50\text{-}\Omega$  on-chip series termination setting for replacing the external 25- $\Omega$  Rs (to match the  $50\text{-}\Omega$  transmission line). For the SSTL Class II standard, users should select the 25- $\Omega$  on-chip series termination setting (to match the  $50\text{-}\Omega$  transmission line and the near end  $50\text{-}\Omega$  pull-up to  $V_{TT}$ ).

<sup>(1) 1.2-</sup>V HSTL is only supported in I/O banks 4,7, and 8.

For more information on tolerance specifications for on-chip termination without calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook* or the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

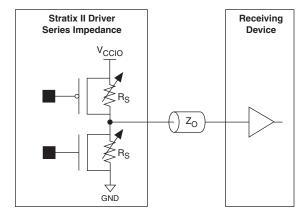

#### **On-Chip Series Termination with Calibration**

Stratix II and Stratix II GX devices support on-chip series termination with calibration in column I/Os in top and bottom banks. Every column I/O buffer consists of a group of transistors in parallel. Each transistor can be individually enabled or disabled. The on-chip series termination calibration circuit compares the total impedance of the transistor group to the external 25- $\Omega$ or 50- $\Omega$ resistors connected to the RUP and RDN pins, and dynamically enables or disables the transistors until they match (as shown in Figure 10–24). The R<sub>S</sub> shown in Figure 10–24 is the intrinsic impedance of transistors. Calibration happens at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

On-chip series termination with calibration is supported on output pins or on the output function of bidirectional pins.

Figure 10–24. Stratix II and Stratix II GX On-Chip Series Termination with Calibration

Table 10–6 shows the list of output standards that support on-chip series termination with calibration.

| Table 10–6. Selectable I/O Drivers with On-Chip Series Termination with Calibration |                                                    |      |  |  |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------------|------|--|--|--|--|--|

| I/O Standard                                                                        | On-Chip Series Termination Setting<br>(Column I/O) | Unit |  |  |  |  |  |

| 3.3-V LVTTL                                                                         | 50                                                 | Ω    |  |  |  |  |  |

|                                                                                     | 25                                                 | Ω    |  |  |  |  |  |

| 3.3-V LVCMOS                                                                        | 50                                                 | Ω    |  |  |  |  |  |

|                                                                                     | 25                                                 | Ω    |  |  |  |  |  |

| 2.5-V LVTTL                                                                         | 50                                                 | Ω    |  |  |  |  |  |

|                                                                                     | 25                                                 | Ω    |  |  |  |  |  |

| 2.5-V LVCMOS                                                                        | 50                                                 | Ω    |  |  |  |  |  |

|                                                                                     | 25                                                 | Ω    |  |  |  |  |  |

| 1.8-V LVTTL                                                                         | 50                                                 | Ω    |  |  |  |  |  |

|                                                                                     | 25                                                 | Ω    |  |  |  |  |  |

| 1.8-V LVCMOS                                                                        | 50                                                 | Ω    |  |  |  |  |  |

|                                                                                     | 25                                                 | Ω    |  |  |  |  |  |

| 1.5 LVTTL                                                                           | 50                                                 | Ω    |  |  |  |  |  |

| 1.5 LVCMOS                                                                          | 50                                                 | Ω    |  |  |  |  |  |

| SSTL-2 Class I                                                                      | 50                                                 | Ω    |  |  |  |  |  |

| SSTL-2 Class II                                                                     | 25                                                 | Ω    |  |  |  |  |  |

| SSTL-18 Class I                                                                     | 50                                                 | Ω    |  |  |  |  |  |

| SSTL-18 Class II                                                                    | 25                                                 | Ω    |  |  |  |  |  |

| 1.8-V HSTL Class I                                                                  | 50                                                 | Ω    |  |  |  |  |  |

| 1.8-V HSTL Class II                                                                 | 25                                                 | Ω    |  |  |  |  |  |

| 1.5-V HSTL Class I                                                                  | 50                                                 | Ω    |  |  |  |  |  |

| 1.2-V HSTL (1)                                                                      | 50                                                 | Ω    |  |  |  |  |  |

Note to Table 10-6:

### **On-Chip Parallel Termination with Calibration**

Stratix II and Stratix II GX devices support on-chip parallel termination with calibration in column I/Os in top and bottom banks. Every column I/O buffer consists of a group of transistors in parallel. Each transistor can be individually enabled or disabled. The on-chip parallel termination calibration circuit compares the total impedance of the transistor group to

<sup>(1) 1.2-</sup>V HSTL is only supported in I/O banks 4,7, and 8.

the external 50- $\Omega$  resistors connected to the RUP and RDN pins and dynamically enables or disables the transistors until they match. Calibration happens at the end of the device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

| Table 10–7. Selectable I/O Drivers with On-Chip Parallel Termination with Calibration |                                                      |      |  |

|---------------------------------------------------------------------------------------|------------------------------------------------------|------|--|

| I/O Standard                                                                          | On-Chip Parallel Termination Setting<br>(Column I/O) | Unit |  |

| SSTL-2 Class I                                                                        | 50                                                   | Ω    |  |

| SSTL-2 Class II                                                                       | 50                                                   | Ω    |  |

| SSTL-18 Class I                                                                       | 50                                                   | Ω    |  |

| SSTL-18 Class II                                                                      | 50                                                   | Ω    |  |

| 1.8-V HSTL Class I                                                                    | 50                                                   | Ω    |  |

| 1.8-V HSTL Class II                                                                   | 50                                                   | Ω    |  |

| 1.5-V HSTL Class I                                                                    | 50                                                   | Ω    |  |

| 1.5-V HSTL Class II                                                                   | 50                                                   | Ω    |  |

| 1.2-V HSTL (1)                                                                        | 50                                                   | Ω    |  |

*Note to Table 10–7:*

(1) 1.2-V HSTL is only supported in I/O banks 4,7, and 8.

There are two separate sets of calibration circuits in the Stratix II and Stratix II GX devices:

- One calibration circuit for top banks 3 and 4

- One calibration circuit for bottom banks 7 and 8

Calibration circuits rely on the external pull-up reference resistor ( $R_{UP}$ ) and pull-down reference resistor ( $R_{DN}$ ) to achieve accurate on-chip series and parallel termination. There is one pair of RUP and RDN pins in bank 4 for the calibration circuit for top I/O banks 3 and 4. Similarly, there is one pair of RUP and RDN pins in bank 7 for the calibration circuit for bottom I/O banks 7 and 8. Two banks share the same calibration circuitry, so they must have the same  $V_{\rm CCIO}$  voltage if both banks enable on-chip series or parallel termination with calibration. If banks 3 and 4 have different  $V_{\rm CCIO}$  voltages, only bank 4 can enable on-chip series or parallel termination with calibration because the RUP and RDN pins are located in bank 4. Bank 3 still can use on-chip series termination, but without calibration. The same rule applies to banks 7 and 8.

On-chip parallel termination with calibration is only supported for input pins. Pins configured as bidirectional do not support on-chip parallel termination.

The RUP and RDN pins are dual-purpose I/Os, which means they can be used as regular I/Os if the calibration circuit is not used. When used for calibration, the RUP pin is connected to  $V_{\rm CCIO}$  through an external 25- $\Omega$  or 50- $\Omega$  resistor for an on-chip series termination value of 25  $\Omega$  or 50  $\Omega$  respectively. The RDN pin is connected to GND through an external 25- $\Omega$  or 50- $\Omega$  resistor for an on-chip series termination value of 25  $\Omega$  or 50  $\Omega$  respectively. For on-chip parallel termination, the RUP pin is connected to  $V_{\rm CCIO}$  through an external 50- $\Omega$  resistor, and RDN is connected to GND through an external 50- $\Omega$  resistor.

For more information on tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook* or the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II GX Device Handbook*.

### Design Considerations

While Stratix II and Stratix II GX devices feature various I/O capabilities for high-performance and high-speed system designs, there are several other considerations that require attention to ensure the success of those designs.

#### I/O Termination

I/O termination requirements for single-ended and differential I/O standards are discussed in this section.

#### Single-Ended I/O Standards

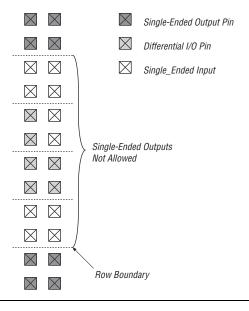

Although single-ended, non-voltage-referenced I/O standards do not require termination, impedance matching is necessary to reduce reflections and improve signal integrity.

Voltage-referenced I/O standards require both an input reference voltage,  $V_{REF}$ , and a termination voltage,  $V_{TT}$ . The reference voltage of the receiving device tracks the termination voltage of the transmitting device. Each voltage-referenced I/O standard requires a unique termination setup. For example, a proper resistive signal termination scheme is critical in SSTL standards to produce a reliable DDR memory system with superior noise margin.

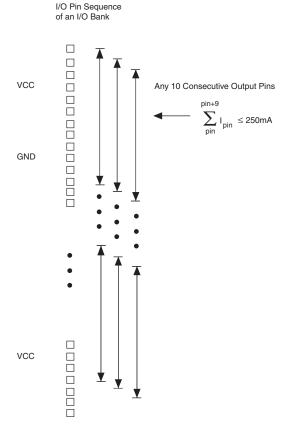

Stratix II and Stratix II GX on-chip series and parallel termination provides the convenience of no external components. External pull-up resistors can be used to terminate the voltage-referenced I/O standards such as SSTL-2 and HSTL.