# **Intel® FPGA SDK for OpenCL™**

Stratix® V Network Reference Platform Porting Guide

Updated for Intel® Quartus® Prime Design Suite: 17.1

UG-OCL008 | 2017.11.06 Latest document on the web: PDF | HTML

# **Contents**

| 1 Inte | el® FPGA SDK for OpenCL™ Stratix® V Network Reference Platform Porting Guide | . 4 |

|--------|------------------------------------------------------------------------------|-----|

|        | 1.1 Stratix V Network Reference Platform: Prerequisites                      |     |

|        | 1.1.1 Legacy Board Support                                                   |     |

|        | 1.2 Features of the Stratix V Network Reference Platform                     |     |

|        | 1.3 Contents of the Stratix V Network Reference Platform                     | 6   |

| 2 Dev  | veloping Your Custom Platform                                                | . 7 |

|        | 2.1 Initializing Your Custom Platform                                        | . 7 |

|        | 2.2 Removing Unused Hardware                                                 |     |

|        | 2.3 Integrating Your Custom Platform with the Intel FPGA SDK for OpenCL      |     |

|        | 2.4 Setting up the Software Development Environment                          |     |

|        | 2.4.1 Setting Up Software Development Environment for Windows                |     |

|        | 2.4.2 Setting Up the Software Development Environment for Linux              |     |

|        | 2.5 Building the Software in Your Custom Platform                            |     |

|        | 2.6 Establishing Host Communication                                          |     |

|        | 2.7 Connecting the Memory         2.8 Integrating an OpenCL Kernel           |     |

|        | 2.9 Programming Your FPGA Quickly Using CvP                                  | 1/  |

|        | 2.10 Guaranteeing Timing Closure                                             |     |

|        | 2.11 Troubleshooting                                                         |     |

|        |                                                                              |     |

| 3 Stra | atix V Network Reference Platform Design Architecture                        |     |

|        | 3.1 Host-FPGA Communication over PCIe                                        |     |

|        | 3.1.1 Parameter Settings for PCIe Instantiation                              |     |

|        | 3.1.2 PCIe Device Identification Registers                                   |     |

|        | 3.1.4 Definitions of Hardware Constants in Software Header Files             |     |

|        | 3.1.5 PCIe Kernel Driver                                                     |     |

|        | 3.1.6 SG-DMA                                                                 |     |

|        | 3.2 DDR3 as Global Memory for OpenCL Applications                            |     |

|        | 3.2.1 DDR3 IP Instantiation                                                  |     |

|        | 3.2.2 DDR3 Connection to PCIe Host                                           | 22  |

|        | 3.2.3 DDR3 Connection to OpenCL Kernel                                       | 23  |

|        | 3.3 QDRII as Heterogeneous Memory for OpenCL Applications                    |     |

|        | 3.4 Host Connection to OpenCL Kernels                                        |     |

|        | 3.5 Implementation of UDP Cores as OpenCL Channels                           |     |

|        | 3.5.1 QuickUDP IP Instantiation                                              |     |

|        | 3.5.2 QuickUDP Configuration via PCIe-Based Host                             |     |

|        | 3.5.3 QuickUDP Connection to OpenCL Kernel                                   |     |

|        | 3.6 FPGA System Design                                                       |     |

|        | 3.6.2 Resets                                                                 |     |

|        | 3.6.3 Floorplan                                                              |     |

|        | 3.6.4 Global Routing                                                         |     |

|        | 3.6.5 Pipelining                                                             |     |

|        | 3.6.6 Encrypted IPs                                                          |     |

|        | 3.7 Guaranteed Timing Closure                                                |     |

|        | 3.7.1 Supply the Kernel Clock                                                |     |

|        |                                                                              |     |

### Contents

| 3.7.2 Guarantee Kernel Clock Timing                                     | 32 |

|-------------------------------------------------------------------------|----|

| 3.7.3 Provide a Timing-Closed Post-Fit Netlist                          |    |

| 3.8 Addition of Timing Constraints                                      |    |

| 3.9 Connection to the Intel FPGA SDK for OpenCL                         | 34 |

| 3.9.1 Describe s5_net to the Intel FPGA SDK for OpenCL                  | 34 |

| 3.9.2 Describe the s5_net Hardware to the Intel FPGA SDK for OpenCL     |    |

| 3.10 FPGA Programming Flow                                              |    |

| 3.10.1 CvP                                                              |    |

| 3.10.2 Flash                                                            | 40 |

| 3.10.3 Defining the Contents of the fpga.bin File                       | 43 |

| 3.11 Host-to-Device MMD Software Implementation                         |    |

| 3.12 OpenCL Utilities Implementation                                    | 45 |

| 3.12.1 aocl install                                                     | 45 |

| 3.12.2 aocl uninstall                                                   |    |

| 3.12.3 aocl program                                                     |    |

| 3.12.4 aocl flash                                                       |    |

| 3.12.5 aocl diagnose                                                    |    |

| 3.12.6 aocl list-devices                                                | 47 |

| 3.13 Stratix V Network Reference Platform Implementation Considerations | 47 |

| A Document Revision History                                             | 49 |

# **1 Intel<sup>®</sup> FPGA SDK for OpenCL<sup>™</sup> Stratix<sup>®</sup> V Network Reference Platform Porting Guide**

The  $Intel^{\circledR}$  FPGA SDK for  $OpenCL^{\intercal}$  Stratix $^{\circledR}$  V Network Reference Platform Porting Guide describes the procedures and design considerations you can implement to modify the Stratix V Network Reference Platform (s5\_net) into your own Custom Platform for use with the Intel FPGA Software Development Kit (SDK) for  $OpenCL^{(1)(2)}$ . This document also contains reference information on the design decisions for s5\_net, which makes use of features such as heterogeneous memory buffers and I/O channels to maximize hardware usage on a computing card designed for networking.

# 1.1 Stratix V Network Reference Platform: Prerequisites

The Stratix V Network Reference Platform Porting Guide assumes that you are an experienced FPGA designer who is familiar with Intel's FPGA design tools and concepts.

These design tools and concepts include:

- FPGA architecture, including clocking, global routing and I/Os

- High-speed design

- Timing analysis

- Intel Quartus® Prime software

- Platform Designer (Standard) design and Avalon<sup>®</sup> interfaces

- · Tcl scripting

- · Designing with Logic Lock regions

- PCI Express\* (PCIe\*)

- DDR3 external memory

### 1.1.1 Legacy Board Support

The Intel FPGA SDK for OpenCL attempts to automigrate your existing Custom Platform to the most recent Intel Quartus Prime Design Suite version.

<sup>(1)</sup> OpenCL and the OpenCL logo are trademarks of Apple Inc. used by permission of the Khronos Group™.

<sup>(2)</sup> The Intel FPGA SDK for OpenCL is based on a published Khronos Specification, and has passed the Khronos Conformance Testing Process. Current conformance status can be found at www.khronos.org/conformance.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Refer to the *Custom Platform Automigration for Forward Compatibility* section in the *Intel FPGA SDK for OpenCL Custom Platform Toolkit User Guide* for more information and instructions.

The Custom Platform Toolkit is available in the SDK's board directory (that is, INTELFPGAOCLSDKROOT/board/custom platform toolkit).

#### Caution:

The Stratix V Network Reference Platform and the *Stratix V Network Reference Platform Porting Guide* are not compatible with Custom Platforms created prior to Altera SDK for OpenCL version 14.0.

#### **Related Links**

Custom Platform Automigration for Forward Compatibility

### 1.2 Features of the Stratix V Network Reference Platform

Prior to designing an Intel FPGA SDK for OpenCL Custom Platform, decide on design considerations that allow you to fully utilize the available hardware on your computing card.

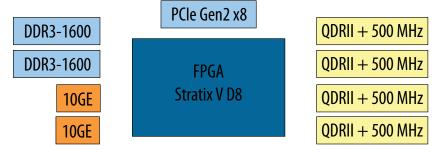

Figure 1. Hardware Features on a Hypothetical Stratix V Network Reference Platform Computing Card

### Features of s5\_net:

1. OpenCL Host

A PCIe-based host that connects to the Stratix V PCIe Gen2 x8 hard intellectual property (IP) core.

### 2. OpenCL Global Memory

The hardware provides two separate 4-gigabyte (GB) DDR3 memory buffers. S5\_net uses both banks together to create 8 GB of global memory.

### 3. Heterogeneous Memory

S5\_net uses the four on-board quad data rate II (QDRII) memory interfaces to implement a total of 64 megabytes (MB) of heterogeneous memory for the Intel FPGA SDK for OpenCL Offline Compiler. By default, the host application allocates memory into the OpenCL global memory (that is, DDR3) when an OpenCL kernel program loads into the OpenCL runtime. However, based on the kernel arguments, the host might relocate memory to other buffers available on the computing card (that is, QDRII). Accesses to heterogeneous memory buffers are advantageous for network applications because they require the fast random access bandwidth that QDR provides.

### 4. OpenCL I/O Channels

The two 10 Gbps Ethernet (10 GbE) I/Os connect to a full user datagram protocol (UDP) stack that provides an Avalon Streaming (Avalon-ST) interface for direct connection to OpenCL kernels.

### 5. FPGA Programming

The computing card uses the Configuration via Protocol (CvP)-capable PCIe hard IP. S5\_net uses Intel FPGA CvP feature for implementing fast reprogramming over PCIe.

### 6. Guaranteed Timing

Guaranteed timing closure is achievable via the Intel Quartus Prime compilation flow for CvP. S5\_net delivers a precompiled netlist in a .personax file that the offline compiler imports into each kernel compilation.

### 1.3 Contents of the Stratix V Network Reference Platform

The Stratix V Network Reference Platform is available for download on the Intel FPGA SDK for OpenCL FPGA Platforms page on the Altera website. Click **Custom** to reveal the download link.

Table 1. Highlights of the Contents of s5\_net

| Windows File or<br>Folder | Linux File or Directory | Description                                                                                                                                                                                                                                        |

|---------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| board_env.xml             | board_env.xml           | eXtensible Markup Language (XML) file that describes s5_net to the SDK.                                                                                                                                                                            |

| windows64                 | linux64                 | Contains memory-mapped device (MMD) library, kernel mode driver, and executables for the SDK utilities (that is, install, flash, program, diagnose, and uninstall) for your 64-bit operating system.                                               |

| hardware                  | hardware                | Contains the Intel Quartus Prime project template into which the Intel FPGA SDK for OpenCL Offline Compiler integrates kernels. The offline compiler then synthesizes the Intel Quartus Prime project files that implement the hardware of s5_net. |

| source                    | source                  | Contains source codes for the MMD library and SDK utilities in the linux64 and windows64 directories.                                                                                                                                              |

| include                   | include                 | Contains header files necessary for compiling an OpenCL host application and accessing board-specific application programming interface (API) calls. For s5_net, these files are necessary for UDP initialization.                                 |

### **Related Links**

Intel FPGA SDK for OpenCL FPGA Platforms page

# 2 Developing Your Custom Platform

Use the tools available in the Stratix V Network Reference Platform and the Intel FPGA SDK for OpenCL Custom Platform Toolkit together to create your own Custom Platform.

Developing your Custom Platform requires in-depth knowledge of the contents in the following documents and tools:

- 1. Intel FPGA SDK for OpenCL Custom Platform User Guide

- 2. Contents of the Custom Platform Toolkit

- 3. Stratix V Network Reference Platform Porting Guide

- 4. Documentation for all the Intel FPGA IP in your Custom Platform

- 5. Intel FPGA SDK for OpenCL Getting Started Guide

- 6. Intel FPGA SDK for OpenCL Programming Guide

In addition, you must independently verify all the hard IPs on your computing card (for example, PCIe controllers, DDR3 external memory, and Ethernet).

#### **Related Links**

- Intel FPGA SDK for OpenCL Custom Platform Toolkit User Guide

- Intel FPGA SDK for OpenCL Getting Started Guide

- Intel FPGA SDK for OpenCL Programming Guide

# **2.1 Initializing Your Custom Platform**

To initialize your Intel FPGA SDK for OpenCL Custom Platform, copy the Stratix V Network Reference Platform to another directory and rename it.

- 1. Download s5\_net from the Intel FPGA SDK for OpenCL FPGA Platforms page on the Altera website. Click **Custom** to reveal to download link.

- 2. Store the s5\_net directory into a directory that you own (that is, not a system directory) and then rename it (<your\_custom\_platform\_name>).

- 3. Remove the <your\_custom\_platform\_name>/hardware/s5\_net/persona

directory.

- 4. Rename the <your\_custom\_platform\_name>/hardware/s5\_net directory to

match the name of your FPGA board (<board name>).

- 5. Modify the name attribute of the board XML element in the board\_spec.xml file with <board\_name>.

- 6. Modify the board\_env.xml file so that the name and default fields match the changes you made in 4 on page 7 and 5 on page 8.

- 7. In the SDK, invoke the command aoc -list-boards to confirm that the Intel FPGA SDK for OpenCL Offline Compiler displays the board name in your Custom Platform.

### **Related Links**

- Intel FPGA SDK for OpenCL FPGA Platforms page

- Listing the Available FPGA Boards in Your Custom Platform (-list-boards)

# 2.2 Removing Unused Hardware

After you store the Stratix V Network Reference Platform to your own directory and perform some preliminary modifications, modify the Intel Quartus Prime design files.

- 1. Instantiate your PCIe controller.

- For detailed instructions on instantiating your PCIe controller, refer to the *Getting Started with the Avalon-MM Stratix V Hard IP for PCI Express* section of the *Stratix V Avalon-MM Interface for PCIe Solutions User Guide*.

- For information on the design parameters for instantiating the PCIe controller in s5\_net, refer to *Host-FPGA Communication over PCIe*, and the *Parameter Settings* section of the *Stratix V Avalon-MM Interface for PCIe Solutions User Guide*.

- 2. In Platform Designer (Standard), open the <your\_custom\_platform\_name>/

hardware/<board\_name>/board.qsys Platform Designer (Standard) system

file. Remove the following components by selecting their names and then clicking

Remove from the right-click menu:

- a. cpld\_bridge\_0

- b. qdr\_0

- c. DDR3 memory controllers

- Because several components use the clock that ddr3a generates, it might be easier to remove only the second DDR3 controller (ddr3b) and reparameterize ddr3a to match your memory.

- 3. Remove the cpld.sdc file from the <your\_custom\_platform\_name>/ hardware/<board name> directory.

- 4. In Platform Designer (Standard), open the <your\_custom\_platform\_name>/

hardware/<board\_name>/system.qsys file. Remove the udp\_0 component.

- 5. In the Platform Designer (Standard) **System** menu, click **Remove Dangling Connections** to remove invalid connection points between system.qsys and board.qys.

- 6. Modify both Intel Quartus Prime settings files (.qsf) to use only the pin-outs and settings for your system. Ensure that the only differences between the base.qsf and top.qsf files are in the settings in the Revision Specific Settings section of the files.

### **Related Links**

- Getting Started with the Avalon-MM Hard IP for PCI Express

- Host-FPGA Communication over PCIe on page 17

- Parameter Settings

# 2.3 Integrating Your Custom Platform with the Intel FPGA SDK for OpenCL

After you modify your Intel Quartus Prime design files, integrate your Custom Platform with the Intel FPGA SDK for OpenCL.

Update the <your\_custom\_platform\_name>/hardware/<board\_name>/

board\_spec.xml file by removing the QDR and Ethernet channels from it.

Ensure that there is at least one global memory interface, and all the global

memory interfaces correspond to the exported interfaces from the board.qsys

Platform Designer (Standard) system file.

QDR section of the Stratix V Network Reference Platform's board\_spec.xml file:

```

<!-- QDRII -->

<global_mem name="QDR" max_bandwidth="17600" interleaved_bytes="8"</pre>

config addr="0x100">

<interface name="board" type="slave" width="64" maxburst="1"</pre>

address="0x200000000" size="0x1000000" latency="150" addpipe="1">

<port name="kernel_qdr0_r" direction="r"/>

<port name="kernel_qdr0_w" direction="w"/>

</interface>

<interface name="board" type="slave" width="64" maxburst="1"</pre>

address="0x201000000" size="0x1000000" latency="150" addpipe="1">

<port name="kernel_qdrl_r" direction="r"/>

<port name="kernel_qdr1_w" direction="w"/>

</interface>

<interface name="board" type="slave" width="64" maxburst="1"</pre>

address="0x202000000" size="0x1000000" latency="150" addpipe="1">

<port name="kernel_qdr2_r" direction="r"/>

<port name="kernel_qdr2_w" direction="w"/>

</interface>

<interface name="board" type="slave" width="64" maxburst="1"</pre>

address="0x203000000" size="0x1000000" latency="150" addpipe="1">

<port name="kernel_qdr3_r" direction="r"/>

<port name="kernel_qdr3_w" direction="w"/>

</interface>

</global_mem>

```

Ethernet channels section of the s5\_net board\_spec.xml file:

2. In the <your\_custom\_platform\_name>/hardware/<board\_name>/scripts

directory, modify the post\_flow.tcl file to not call the create\_fpga\_bin.tcl

file. You can do so by commenting out the line of code containing the command

call script as function scripts/create fpga bin.tcl.

3. Set the environment variable ACL\_QSH\_COMPILE\_CMD to quartus\_sh --flow compile top -c base.

Setting this environment variable instructs the SDK to compile the base revision corresponding to the base.qsf file in the <your\_custom\_platform\_name>/

hardware/<boxed name> directory of your Custom Platform.

4. Perform the steps outlined in the <code>INTELFPGAOCLSDKROOT/board/custom\_platform\_toolkit/tests/README.txt</code> file to compile the <code>INTELFPGAOCLSDKROOT/board/custom\_platform\_toolkit/tests/boardtest/boardtest.cl OpenCL kernel source</code> file.

The environment variable *INTELFPGAOCLSDKROOT* points to the location of the SDK installation.

The hardware compilation stage will fail because of the absence of the fpga.bin file. However, the Intel Quartus Prime compilation should complete successfully and produce a boardtest.aoco Intel FPGA SDK for OpenCL Offline Compiler object file.

5. If compilation fails because of timing failures, fix the errors, or compile INTELFPGAOCLSDKROOT/board/custom\_platform\_toolkit/tests/

boardtest.cl with different seeds by including the -seed=<N> option in the aoc command (for example, aoc -seed=2 boardtest.cl).

# 2.4 Setting up the Software Development Environment

Prior to building the software layer for your Intel FPGA SDK for OpenCL Custom Platform, you must set up the software development environment.

### 2.4.1 Setting Up Software Development Environment for Windows

1. Install the GNU make utility on your Windows development machine.

Note: Intel used the GNU make utility version 3.81a to build the software in the Stratix V Network Reference Platform.

2. Install Microsoft Visual Studio.

Note: Microsoft Visual Studio 2008 (9.0) was used to build the software in s5\_net.

- 3. Set up the software development environment so that the Intel FPGA SDK for OpenCL user can invoke SDK commands and utilities at a command prompt.

- 4. Modify the <your\_custom\_platform\_name>/source/Makefile.common file

so that TOP\_DEST\_DIR points to the top-level directory of your Custom Platform.

- In the Makefile.common file, set the JUNGO\_LICENSE variable to your Jungo WinDriver license.

- For information on how to acquire a Jungo Windriver license, visit the Jungo Connectivity Ltd. website.

- 6. To check that you have set up the software development environment properly, invoke the gmake or gmake clean command.

### **Related Links**

Jungo Connectivity Ltd. website

# 2.4.2 Setting Up the Software Development Environment for Linux

- 1. Ensure that you use a Linux distribution that Intel supports.

- Note: Intel used the GNU Compiler Collection (GCC) version 4.2.3 to build the software in the Stratix V Network Reference Platform.

- 2. Modify the <your\_custom\_platform>/source/Makefile.common file so that

TOP\_DEST\_DIR points to the top-level directory of your Custom Platform.

- To check that you have set up the software environment properly, invoke the make or make clean command.

# 2.5 Building the Software in Your Custom Platform

You can build the software in your custom platform by modifying the library, driver, and source files provided in the Stratix V Network Reference Platform. To brand your custom platform, you must modify the MMD library, driver, and utilities provided in s5\_net to include information specific to your board design.

- 1. In the software available with s5\_net, ensure that you replace all references to s5 net to your Custom Platform.

- 2. Modify the linklib element in <your\_custom\_platform\_name>/

board env.xml XML file to your custom MMD library name.

- 3. Modify the PACKAGE\_NAME and MMD\_LIB\_NAME fields in the <your\_custom\_platform\_name>/source/Makefile.common file.

- 4. Modify the following files to include information of your Custom Platform:

- For Windows, <your\_custom\_platform\_name>\source\include

\hw\_pcie\_constants.h

- For Linux, <your\_custom\_platform\_name>/linux64/driver/ hw\_pcie\_constants.h

Update the following lines of code with information of your Custom Platform:

```

#define ACL_PCI_SUBSYSTEM_VENDOR_ID 0x1172

#define ACL_PCI_SUBSYSTEM_DEVICE_ID 0x0005

#define ACL_BOARD_PKG_NAME "s5_net"

#define ACL_VENDOR_NAME "Intel(R) Corporation"

#define ACL_BOARD_NAME "Network Reference Platform"

```

Note: The IDs must match the parameters in the PCIe controller hardware. For more information, refer to PCIe Device Identification Registers.

- 5. For Windows systems, update the DeviceList field in the <your\_custom\_platform\_name>\windows64\driver\acl\_boards.inf Setup Information file.

- 6. Run make in the<your\_custom\_platform\_name>/source directory to generate

the MMD library, driver, and utilities.

#### **Related Links**

PCIe Device Identification Registers on page 17

# 2.6 Establishing Host Communication

After you modify and rebrand the Stratix V Network Reference Platform to your own Custom Platform, use the tools and utilities in the Custom Platform to establish communication between your FPGA accelerator board and your host application.

- 1. Program your FPGA device with the <your\_custom\_platform\_name>/

hardware/<board\_name>/base.aocx hardware configuration file and reboot

your system.

- Confirm that your operating system recognizes a PCIe device with your vendor and device IDs.

- For Windows, open the **Device Manager**

- For Linux, invoke the lspci command

- 3. Run the aocl install <path\_to\_customplatform> utility command to install the kernel driver on your machine.

- 4. Ensure that you properly set the *LD\_LIBRARY\_PATH* environment variable on Linux or the *PATH* environment variable on Windows.

- For more information about the settings for *LD\_LIBRARY\_PATH* or *PATH*, refer to the *Setting the Intel FPGA SDK for OpenCL User Environment Variables* section of the *Intel FPGA SDK for OpenCL Getting Started Guide*.

- 5. To instruct the MMD software not to use CvP or flash memory to program the FPGA, perform one of the following tasks :

- To force the MMD to program via the quartus\_pgm executable, set the environment variable ACL PCIE FORCE USB PROGRAMMING to a value of 1.

- To force the MMD to program via your custom programming method, modify the <your\_custom\_platform\_name>/source/host/mmd/

acl\_pcie\_device.cpp file. Trace the appearance of the environment variable ACL\_PCIE\_FORCE\_USB\_PROGRAMMING in the source code, and replace the existing instruction with your custom programming method.

- 6. Modify the version\_id\_test function in the MMD source code in the <your\_custom\_platform\_name>/source/host/mmd/

acl\_pcie\_device.cpp file to exit after reading from the version ID register.

- 7. Remake the MMD software.

- 8. Run the aocl diagnose utility command and confirm the version ID register reads back the ID successfully. You may set the environment variables ACL\_HAL\_DEBUG and ACL\_PCIE\_DEBUG to a value of 1 to visualize the result of the diagnostic test on your terminal.

### **Related Links**

- Host-FPGA Communication over PCIe on page 17

- Setting the Intel FPGA SDK for OpenCL User Environment Variables (Windows)

- Setting the Intel FPGA SDK for OpenCL User Environment Variables (Linux)

- Querying the Device Name of Your FPGA Board (diagnose)

# 2.7 Connecting the Memory

Calibrate the external memory IP and controllers in your Custom Platform, and connect them to the host.

- 1. In your Custom Platform, instantiate your external memory IP based on the information in the *DDR3* as *Global Memory for OpenCL Applications* section.

- 2. Update the <your\_custom\_platform\_name>/hardware/<board\_name>/

board\_spec.xml file to reflect the modifications.

- 3. Remove the boardtest hardware configuration file that you created during the integration of your Custom Platform with the Intel FPGA SDK for OpenCL.

- 4. Recompile the INTELFPGAOCLSDKROOT/board/custom\_platform\_toolkit/tests/boardtest/boardtest.cl kernel source file.

- The environment variable *INTELFPGAOCLSDKROOT* points to the location of the SDK installation.

- 5. Reprogram the FPGA with the new boardtest hardware configuration file and then reboot your machine.

- 6. Modify the MMD source code to exit after checking the UniPHY status register in the function wait\_for\_uniphy. Rebuild the MMD software.

- 7. Run the aocl diagnose utility command and confirm that the host reads back both the version ID and the value 0 from the uniphy\_status component.

The utility should return the message Uniphy are calibrated.

- 8. Consider using the Signal Tap logic analyzer to confirm the successful calibration of all memory controllers.

### **Related Links**

DDR3 as Global Memory for OpenCL Applications on page 21

# 2.8 Integrating an OpenCL Kernel

After you establish host communication and connect the external memory, test the FPGA programming process from kernel creation to program execution.

- Perform the steps outlined in INTELFPGAOCLSDKROOT/board/ custom\_platform\_toolkit/tests/README.txt file to build the hardware configuration file from the INTELFPGAOCLSDKROOT/board/ custom\_platform\_toolkit/tests/boardtest/boardtest.cl kernel source file.

- The environment variable *INTELFPGAOCLSDKROOT* points to the location of the Intel FPGA SDK for OpenCL installation.

- 2. Program your FPGA device with the boardtest.aocx Intel FPGA SDK for OpenCL Offline Compiler executable file and reboot your machine.

- 3. Remove the early-exit modification in the version\_id\_test function in the <your\_custom\_platform\_name>/source/host/mmd/

acl\_pcie\_device.cpp file that you implemented when you established communication between the board and the host interface.

- 4. Invoke the aocl diagnose <device\_name> command, where <device\_name> is the string you define in your Custom Platform to identify each board.

- By default, <device\_name> is the acl number (for example, acl0 to acl31) that corresponds to your FPGA device. In this case, invoke the aocl diagnose acl0 command.

- 5. Build the boardtest host application. The .sln file for Windows and the Makefile for Linux are available in the <code>INTELFPGAOCLSDKROOT/board/custom\_platform\_toolkit/tests/boardtest directory.</code>

- **Attention:** You must modify the .sln file to link it against the MMD library in your Custom Platform.

- 6. Set the environment variable *CL\_CONTEXT\_COMPILER\_MODE\_INTELFPGA* to a value of 3.

For more information on this environment variable, refer to *Troubleshooting*.

### **Related Links**

Troubleshooting on page 16

# 2.9 Programming Your FPGA Quickly Using CvP

After you verify that the host can program you FPGA device successfully, establish the CvP programming capability of your Custom Platform.

1. Invoke the following command to generate the CvP files:

quartus\_cpf -c --cvp <revision\_name>.sof <revision\_name>.rbf

You may include this command in the <your\_custom\_platform\_name>/

hardware/<board\_name>/scripts/post\_flow.tcl file so that it generates

the CvP files automatically after each compilation.

Your Intel Quartus Prime compilation directory should contain the files <revision\_name>.sof, <revision\_name>.periph.rbf, and <revision\_name>.core.rbf files.

- 2. Program the base.sof file and then reboot your machine.

- 3. (Optional) You may use the Intel Quartus Prime Programmer to verify basic CvP functionality. Invoke the quartus\_cvp command to program the base.core.rbf file.

- 4. Define the contents of your fpga.bin file by adding Tcl code to the <your\_custom\_platform\_name>/hardware/<board\_name>/scripts/

post\_flow.tcl file that generates the fpga.bin file. Then, modify the MMD source code and the program utility so that you can use the file.

- You may use the existing format if you remove the proprietary host-to-flash programming over the cpld\_bridge component from both the hardware and software.

- 5. If you set the environment ACL\_PCIE\_FORCE\_USB\_PROGRAMMING earlier, unset it. Then, set the environment variable ACL\_PCIE\_FORCE\_PERIPH\_REPLACE\_USB to a value of 1. Alternatively, modify the <your\_custom\_platform\_name>/

source/host/mmd/acl\_pcie\_device.cpp file to use CvP but not flash memory for reprogramming periphery changes. Flash programming is unavailable because of the removal of the cpld\_bridge component.

- 6. Navigate to the directory containing the boardtest.aocx file. Invoke the command aocl program <device\_name> boardtest.aocx to reprogram the device. Confirm that the message Program succeed appears.

Note: By default, <device\_name> is the acl number. If you have retained the default naming convention, invoke the aocl program command using acl0 as <device\_name>. Alternatively, if you use another naming convention for <device\_name>, use that in your aocl utility command.

### **Related Links**

Programming the FPGA Offline or without a Host (program <device\_name>)

# 2.10 Guaranteeing Timing Closure

When you modify the Stratix V Network Reference Platform into your own Custom Platform, ensure that guaranteed timing closure holds true for your Custom Platform.

- 1. Establish the floorplan of your design.

- Important: Consider all design criteria outlined in FPGA System Design and the Intel FPGA SDK for OpenCL Custom Platform Toolkit User Guide.

- 2. Compile several seeds of boardtest.cl until you generate a compiled design that achieves timing closure cleanly. Include the -seed=<N> option in your acc command to specify the seed number.

- 3. Copy the <path\_to\_s5\_net>/hardware/s5\_net/persona/

base.root\_partition.personax file into your Custom Platform.

- 4. Copy the boardtest.aocx file from the timing-closed compilation in Step 2 into your Custom Platform. Rename the file base.aocx.

- 5. Derive the top revision top.qsf file from your base.qsf file by including the changes described in the CvP section.

- 6. Remove the ACL\_QSH\_COMPILE\_CMD environment variable.

- 7. Recompile boardtest.cl. In the Fitter Preservation section of the report, confirm that the Top partition is imported.

- The Incremental Compilation Placement Preservation section should show 100% placement for Top. Similarly, the Incremental Compilation Routing Preservation section should show 100% routing for Top.

- 8. Confirm that you can use the .aocx file to reprogram over CvP by invoking the aocl program acl0 boardtest.aocx command.

- 9. Ensure that the environment variable CL\_CONTEXT\_COMPILER\_MODE\_INTELFPGA is not set. Run the boardtest\_host executable.

#### **Related Links**

- Intel FPGA SDK for OpenCL Custom Platform Toolkit User Guide

- CvP on page 36

- FPGA System Design on page 26

# 2.11 Troubleshooting

Set Intel FPGA SDK for OpenCL-specific environment variables to help troubleshoot Custom Platform design problems.

Table 2. Intel FPGA SDK for OpenCL-Specific Environment Variables for Identifying **Custom Platform Design Problems**

| Environment Variable               | Description                                                                                                                                                                                                                                            |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACL_HAL_DEBUG                      | Set this variable to a value of 1 to 5 to enable increasing debug output from the Hardware Abstraction Layer (HAL), which interfaces directly with the MMD layer.                                                                                      |

| ACL_PCIE_DEBUG                     | Set this variable to a value of 1 to 10000 to enable increasing debug output from the MMD. This variable setting is useful for confirming that the version ID register was read correctly and the UniPHY IP cores are calibrated.                      |

| ACL_PCIE_JTAG_CABLE                | Set this variable to override the default quartus_pgm argument that specifies the cable number. The default is cable 1. If there are multiple Intel FPGA Download Cable, you can specify a particular one here.                                        |

| ACL_PCIE_JTAG_DEVICE_INDEX         | Set this variable to override the default quartus_pgm argument that specifies the FPGA device index. By default, this variable has a value of 1. If the FPGA is not the first device in the JTAG chain, you can customize the value.                   |

| CL_CONTEXT_COMPILER_MODE_INTELFPGA | Unset this variable or set it to a value of 3. The OpenCL host runtime reprograms the FPGA as needed, which it does at least once during initialization. To prevent the host application from programming the FPGA, set this variable to a value of 3. |

|                                    | Important: When setting CL_CONTEXT_COMPILER_MODE_INTELFPGA, only use a value of 3.                                                                                                                                                                     |

# 3 Stratix V Network Reference Platform Design Architecture

Intel created the Stratix V Network Reference Platform based on various design considerations. Familiarize yourself with these design considerations. Having a thorough understanding of the design decision-making process might help in the design of your own Intel FPGA SDK for OpenCL Custom Platform.

### 3.1 Host-FPGA Communication over PCIe

To set up the PCIe hard IP that enables communication between the host and the FPGA board, you must configure the IP settings, and set various IDs, constants and parameters.

# 3.1.1 Parameter Settings for PCIe Instantiation

The Stratix V Network Reference Platform instantiates the Stratix V PCIe hard IP to implement a host-to-device connection over PCIe.

### **Dependencies**

- Stratix V hard IP for PCI Express

- For Windows systems, Jungo WinDriver

### Table 3. Highlights of the Stratix V PCIe hard IP Configuration Settings

| Parameter                              | Setting                                                                                                                                                                                                  |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lanes                                  | Lane rate: <b>Gen2 (5.0 Gbps)</b> Number of lanes: <b>x8</b> Note: This setting is the fastest configuration that can support CvP.                                                                       |

| Rx buffer credit allocation            | Low Note: This setting is derived experimentally.                                                                                                                                                        |

| Enable configuration via the PCIe link | On Click the check box to enable the setting.                                                                                                                                                            |

| Base Address Registers (BARs)          | The design uses only a single BAR (BAR 0).                                                                                                                                                               |

| Address Translation Tables             | Number of address pages: 256  Note: This setting is derived experimentally.  Size of address pages: 12 bits  Important: The number and size of the address pages must match the values in the MMD layer. |

## 3.1.2 PCIe Device Identification Registers

To build PCIe hardware, you must set PCIe IDs related to the device hardware.

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2008 Registered

| Table 4. Device Hardware-Related PCIe ID Register | Table 4. | Device | Hardware-Re | elated | PCTe ID | Register |

|---------------------------------------------------|----------|--------|-------------|--------|---------|----------|

|---------------------------------------------------|----------|--------|-------------|--------|---------|----------|

| ID Register Name    | Parameter Name in PCIe IP Core | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vendor ID           | vendor_id_hwtcl                | Identifies the manufacturer of the FPGA device. Always set this register to 0x1172.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Device ID           | device_id_hwtcl                | Identifies the FPGA device. Set the device ID to the device code of the FPGA device on your accelerator board. For the Stratix V Network Reference Platform, this register is set to 0xD800 for the Stratix V D8 FPGA.                                                                                                                                                                                                                                                                                |

| Subsystem Vendor ID | subsystem_vendor_id_hwtcl      | Identifies the manufacturer of the accelerator board. Set this register to the vendor ID of manufacturer of your accelerator board. If you are a board vendor, set this register to your vendor ID.                                                                                                                                                                                                                                                                                                   |

| Subsystem Device ID | subsystem_device_id_hwtcl      | Identifies the accelerator board.  The Intel FPGA SDK for OpenCL uses this ID to identify the board because the software might perform differently on different boards. If you create a Custom Platform that supports multiple boards, use this ID to distinguish between the boards. Alternatively, if you have multiple Custom Platforms, each supporting a single board, you can use this ID to distinguish between the Custom Platforms.  Important: Make this ID unique to your Custom Platform. |

You can find these PCIe ID definitions in the PCIe controller instantiated in the board.gsys system. These IDs are necessary in the driver and the SDK programming flow. The kernel driver uses the Vendor ID, Subsystem Vendor ID and the Subsystem Device ID to identify the boards it supports. The SDK programming flow refers to the Device ID to ensure that it programs a device with a .aocx file targeting that specific device.

### 3.1.3 Version ID

The Stratix V Network Reference Platform instantiates a version id component that connects to the PCIe Avalon master.

Before communicating with any part of the FPGA system, the PCIe first reads from this version id register to confirm the following:

- The PCIe can access the FPGA fabric successfully.

- The address map matches the map in the MMD software.

Update the VERSION ID parameter in the version id component to a new value with every slave addition or removal from the PCIe BAR 0 bus, or whenever the address map changes.

### 3.1.4 Definitions of Hardware Constants in Software Header Files

After you build the PCIe component in your hardware design, you need a software layer to communicate with the board via PCIe. To enable communication between the board and the host interface, define the hardware constants for the software in header files.

The Stratix V Network Reference Platform includes three header files that describe the hardware design to the software. The location of these header files are as follows:

- For Linux systems, the location is path\_to\_s5\_net>/linux64/driver

- For Windows systems, the location is <path\_to\_s5\_net>\source\include

## Table 5. S5\_net Header Files

| Header File Name                                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| hw_pcie_constants.h                                                                                                 | Header file that defines most of the hardware constants for the board design.  Example constants in this file include the IDs described in the <i>PCIe Device Identification Registers</i> section, BAR number, and offset for different components in your design. In addition, this header file also defines the name strings of ACL_BOARD_PKG_NAME, ACL_VENDOR_NAME and ACL_BOARD_NAME.  Keep the information in this file in sync with any changes to the board design. |  |

| hw_pcie_dma.h                                                                                                       | Header file that defines direct memory access (DMA)-related hardware constants. Refer to <i>SG-DMA</i> for more information.                                                                                                                                                                                                                                                                                                                                                |  |

| hw_pcie_cvp_constants.h Header file that defines CvP-related hardware constants. Refer to CvP for more information. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

### **Related Links**

- SG-DMA on page 20

- CvP on page 36

- PCIe Device Identification Registers on page 17

### 3.1.5 PCIe Kernel Driver

A PCIe kernel driver is necessary for the OpenCL runtime library to access your board design via a PCIe bus.

The Stratix V Network Reference Platform PCIe kernel driver is in the following directory:

- For Windows systems, the driver is in the rath\_to\_s5\_net>

\windows64\driver folder

- For Linux systems, the driver is in the <path\_to\_s5\_net>/linux64/driver directory

Use the Intel FPGA SDK for OpenCL install utility to install the kernel driver. Refer to *aocl install* for more information.

For Windows systems, the WinDriver API kernel driver is a third-party driver from Jungo Connectivity Ltd. For more information about the WinDriver, refer to the Jungo Connectivity Ltd. website or contact a Jungo Connectivity representative.

For Linux systems, an open-source, MMD-compatible kernel driver is available with s5 net.

Table 6. Highlight of Files Available in the Linux Kernel Driver Directory

| File Name                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <pre>pcie_linux_driver_exports. h</pre> | Header file defining the special commands that the kernel driver supports. It defines the interface of the kernel driver. The MMD layer uses this header file to communicate with the device.  After you install the kernel driver, it works as a character device. The basic operations to the driver are open(), close(), read(), and write(). To support more complex commands, an acl_cmd struct variable is necessary to pass the command of interest to the kernel driver through the read() or write() operation. To execute a command, perform the following tasks:  1. Create a variable as type acl_cmd_struct.  2. Specify the command you want to execute with the appropriate parameters.  3. Send the command through a read() or write() operation. |  |  |

| aclpci.c                                | File that implements the basic structures and functions that a Linux kernel driver requires (for example, the init and remove functions, probe function, and functions that handle interrupts).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| aclpci_fileio.c                         | File that implements the file I/O operations of the kernel driver. The s5_net Linux kernel driver supports four file I/O operations, namely open(), close(), read() and write(). Implementation of these file I/O operations allows the user application to access the kernel driver via file I/O system calls (open/read/write/close).                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| aclpci_cmd.c                            | File that implements the special commands defined in the pcie_linux_driver_exports.h file. Examples of these special commands include SAVE_PCI_CONTROL_REGS, LOAD_PCI_CONTROL_REGS, DO_CVP, and GET_PCI_SLOT_INFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| aclpci_dma.c                            | File that implements DMA-related routine in the kernel driver.  Refer to SG-DMA for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| aclpci_cvp.c                            | File that implements CvP-related routine in the kernel driver.  Refer to CvP for more information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| aclpci_queue.c                          | File that implements a queue structure for use in the kernel driver. Such a queue structure eases programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

### **Related Links**

- aocl install on page 45

- SG-DMA on page 20

- CvP on page 36

- Jungo Connectivity Ltd. website

### 3.1.6 **SG-DMA**

The acl\_dma\_core.qsys file within the OpenCL SGDMA Controller IP encapsulates and parameterizes the modular scatter-gather SG-DMA hardware. The board.qsys system instantiates the acl\_dma.qsys file within the OpenCL SGDMA Controller IP. For more information on SG-DMA, visit the Modular SG-DMA page on the Altera $^{\circledR}$  Wiki website.

#### **Hardware**

The acl\_dma\_core.qsys file presents slave ports for the control and status registers (dma\_csr) and the descriptors (dma\_descriptors). It also provides separate masters for read and write operations. The acl\_dma.qsys Platform Designer (Standard) System File adds the following features:

- An address span extender for non-DMA memory accesses

- A merged read/write master

The merged read/write master issues constant bursts of size 16, resulting in a 1/16 efficiency degradation from sharing the time interface. However, the bandwidth of this unit exceeds the bandwidth of the PCIe connection by more than this amount. Therefore, there is no observable host-to-memory bandwidth degradation.

#### **Software**

When the MMD receives a request for data transfer, it uses DMA when both of the following conditions are true:

- 1. The transfer size is bigger than 1024 bytes.

- There are 64-byte alignments with the starting addresses for both the host buffer and the device offset.

Perform the following tasks to carry out a DMA transfer:

- 1. Check if there are remaining bytes to be sent.

- 2. Unpin the memory from the previous transfer.

- 3. Pin the memory for the new transfer.

- 4. Set up the Address Translation Tables on the PCIe.

- 5. Create and send the DMA descriptor.

- 6. Wait until the DMA finishes and then repeat Step 1.

### Attention:

For the Stratix V Network Reference Platform, this implementation is in the Linux kernel driver in the  $< path\_to\_s5\_net>/linux64/driver/aclpci\_dma.c$  file. For Windows systems, the implementation is in the  $< path\_to\_s5\_net> \$  \mmd\acl\_pcie\_dma\_windows.cpp file.

### **Related Links**

Modular SG-DMA page on Altera Wiki

# 3.2 DDR3 as Global Memory for OpenCL Applications

The Stratix V Network Reference Platform targets a computing card that has two banks of 4 GB x72 DDR3-160 SDRAM. Completion of the tasks below are necessary to access these banks as global memory for OpenCL applications.

For more information on the DDR3 UniPHY IP, refer to the *DDR2, DDR3, and DDR4 SDRAM Board Design Guidelines* section in Volume 2 of the *External Memory Interface Handbook*.

#### **Related Links**

DDR2, DDR3, and DDR4 SDRAM Board Design Guidelines

### 3.2.1 DDR3 IP Instantiation

The Stratix V Network Reference Platform uses two DDR3 controllers with UniPHY IP to communicate with the physical memories.

Table 7. **DDR3 SDRAM Controller with UniPHY IP Configuration Settings**

| IP Parameter                                                | Configuration Setting                                                                                                                                                                                                                                               |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Timing Parameters                                           | As per the computing card's data specifications.                                                                                                                                                                                                                    |  |

| Phase-locked loop (PLL)/delay-<br>locked loop (DLL) Sharing | s5_net is configured such that both memory controllers can share the same PLL and DLL.                                                                                                                                                                              |  |

| Avalon Width Power of 2                                     | Currently, OpenCL does not support non-power-of-2 bus widths. As a result, s5_net uses the option that forces the DDR3 controller to power of 2. Use the additional pins of this x72 core for error checking between the memory controller and the physical module. |  |

| Byte Enable Support                                         | OpenCL requires byte-level granularity to all memories; therefore, byte-enable support is necessary in the core.                                                                                                                                                    |  |

| Performance                                                 | Enabling reordering and a deeper command queue look-ahead depth might provide increased bandwidth for some OpenCL kernels. For a target application, adjust these and other parameters as necessary.                                                                |  |

| Debug                                                       | Debug is disabled for production.                                                                                                                                                                                                                                   |  |

After you instantiate the UniPHY IP, you typically need to run the <variation\_name>\_pin\_assignments.tcl Tcl script to add additional constraints to the Intel Quartus Prime project. For more information on this process, refer to the Adding Pins and DQ Group Assignments section in Volume 2 of the External Memory Interface Handbook.

### **Related Links**

Adding Pins and DO Group Assignments

# 3.2.2 DDR3 Connection to PCIe Host

Connect all global memory systems to the host via the OpenCL Memory Bank Divider component.

The DDR3 UniPHY IP core has two banks where their width and address configurations match those of the DDR3 SDRAM. Intel tunes the other parameters such as burst size, pending reads, and pipelining. These parameters are customizable for an end application or board design.

The Avalon master interfaces from the bank divider connect to their respective memory controllers. The Avalon slave connects to the PCIe and DMA cores. Implementations of appropriate clock crossing and pipelining are based on the design floorplan and clock domains specific to the computing card. The OpenCL Memory Bank Divider section in the Intel FPGA SDK for OpenCL Custom Platform Toolkit User Guide specifies the connection details of the snoop and memorg ports.

*Important:* Instruct the host to check for the successful calibration of the memory controller.

The board.qsys system uses a custom IP component named UniPHY Status to AVS to aggregate different UniPHY status conduits into a single Avalon slave port named s. This slave connects to the pipe\_stage\_host\_ctrl component so that the PCIe host can access it.

#### **Related Links**

OpenCL Memory Bank Divider

### 3.2.3 DDR3 Connection to OpenCL Kernel

The OpenCL kernel needs to connect directly to the memory controller via a FIFO-based clock crosser.

A clock crosser is necessary because the kernel interface for the compiler must be clocked in the kernel clock domain. In addition, the width, address width, and burst size characteristics of the kernel interface must match those specified in the bank divider connecting to the host. Appropriate pipelining also exists between the clock crosser and the memory controller.

# 3.3 QDRII as Heterogeneous Memory for OpenCL Applications

The OpenCL heterogeneous memory feature allows Intel FPGA SDK for OpenCL users to take advantage of the nonuniform memory architecture in a Custom Platform.

An SDK Custom Platform groups memories with similar characteristics into a single global memory system. Each Custom Platform has a designated default global memory system. In the case of the Stratix V Network Reference Platform, the default global memory system consists of the two DDR3 memory banks. The default global memory system must start at base address 0 from the host's perspective. Both the hardware design and the board\_spec.xml file in the Custom Platform reflect this address assignment. In s5 net, the DDR global memory system is named DDR.

In addition to the DDR global memory system, the computing card that s5\_net targets includes four banks of QDR memory. These four banks belong to a global memory system named *QDR*. SDK users can only allocate memory in the QDR global memory system using an attribute on their global memory buffers. All addressable global memory must be contiguous from the host's perspective; therefore, the QDR memory base address must start where the DDR memory ends.

For more information on the QDR UniPHY IP, refer to the *QDR II and QDR IV SRAM Board Design Guidelines* in Volume 2 of the *External Memory Interface Handbook*.

The procedure for implementing the QDR subsystem is similar to the one outlined in the *Developing Your Custom Platform* section. Below is a list of high-level tasks:

- 1. Instantiate and parameterize the UniPHY memory controllers.

- 2. Connect the UniPHY memory controllers to the host via a new OpenCL Memory Bank Divider instance.

- 3. Connect the UniPHY memory controller to the UniPHY Status to AVS component.

- 4. Export the UniPHY memory controller to the OpenCL kernel via clock-crossing bridges.

Below are special QDR subsystem design considerations for s5 net:

- QDR provides separate read and write ports.

- By default, the OpenCL Memory Bank Divider produces a single bidirectional master for each memory controller. In Platform Designer (Standard), select the **Separate read/write** ports option to support separate read and write masters. With respect to the kernel, instantiate clock crosses and separate read and write interfaces.

- The 275 MHz QDR afi clock and 4-to-1 multiplexing in the bank divider make it difficult to meet timing.

To achieve timing closure robustly, open the qdr.qsys file in Platform Designer (Standard), and select the option to pipeline the outputs in the OpenCL Memory Bank Divider memory bank divider 1. Doing so adds a pipeline stage for each master that the bank divider creates.

### **Related Links**

- Developing Your Custom Platform on page 7

- QDR II and QDR IV SRAM Board Design Guidelines

# 3.4 Host Connection to OpenCL Kernels

The PCIe host needs to pass commands and arguments to the OpenCL kernels via the control register access (CRA) Avalon slave port that each OpenCL kernel generates. The OpenCL Kernel Interface component exports an Avalon master interface (kernel cra) that connects to this slave port. The OpenCL Kernel Interface component also generates the kernel reset (kernel reset) that resets all logic in the kernel clock domain.

The Stratix V Network Reference Platform instantiates the OpenCL Kernel Interface component and sets the **Number of global memory systems** parameter to 2. The parameter setting is 2 because s5 net has DDR and QDR memories. Below is a list of connection settings in s5 net:

- For the default DDR memory, the generated memorg host0x018 conduit must connect to the DDR bank divider (memory bank divider 0).

- For the default DDR memory, the config\_addr attribute in the board spec.xml file must be set to 0x018.

- For the QDR memory, the memorg\_host0x100 conduit must connect to the QDR bank divider (memory bank divider 1).

- For the QDR memory, the config\_addr attribute in the board\_spec.xml file must be set to 0x100.

# 3.5 Implementation of UDP Cores as OpenCL Channels

OpenCL kernels can communicate directly with I/O using the Intel FPGA SDK for OpenCL channels extension.

For the Stratix V Network Reference Platform, Intel uses the PLDA QuickUDP IP to implement a full UDP stack on top of the available 10 GbE channels on the card. OuickUDP provides an Avalon-ST interface that can connect directly to the OpenCL kernel, allowing it to send and receive UDP network traffic without concern for UDP or lower-level protocols.

The UDP Hardware Stack QuickUDP IP is a licensed IP from PLDA. Refer to the PLDA Attention:

website for information on acquiring and installing the appropriate license.

Improper installation of the QuickUDP IP license causes the SDK users to encounter Caution:

the following error message when they compile with a Custom Platform that contains

the QuickUDP IP:

Error (292014): Can't find valid feature line for core PLDA QUICKTCP (73E1\_AE12) in current license.

The error has no actual dependency on the PLDA QuickTCP IP.

**Related Links**

PLDA website

# 3.5.1 QuickUDP IP Instantiation

The Stratix V Network Reference Platform targets a computing card that has two 10 GbE channels. To access these channels, s5\_net instantiates two PLDA QuickUDP IP cores.

The two 10 Gigabit Media Independent Interface (XGMII) interfaces from these cores connect to a single 10GBASE-R PHY with two channels. The Verilog instantiation of the PHY IP core is in the <path\_to\_s5\_net>/hardware/s5\_net/ip/quickudp/ quickudp wrapper.v file. This file contains parameters such as the multitenant unit (MTU) and the number of sessions supported. Most parameters are accessible via QuickUDP's Avalon Memory-Mapped (Avalon-MM) slave interface.

### 3.5.2 QuickUDP Configuration via PCIe-Based Host

The Stratix V Network Reference Platform provides access to the PLDA QuickUDP IP configuration space to the host over PCIe by connecting pipe\_stage\_host\_ctrl to the config udp0 and config udp1 interfaces of the s5 net udp.gsvs subsystem.

Intel FPGA SDK for OpenCL users need to set their own parameters such as media access control (MAC), IP address, ports, and destinations. With the host access to QuickUDP via PCIe, the SDK users can configure the QuickUDP settings in their host software using the API in the <path to s5 net>/include/aocl net.h header file.

# 3.5.3 QuickUDP Connection to OpenCL Kernel

Each PLDA QuickUDP IP core produces a read stream and a write stream, for a total of four Intel FPGA SDK for OpenCL channels available to the kernel. These streams cross into the kernel clk domain and are listed in the board spec.xml file.

Attention: The SDK supports only basic Avalon-ST with no packet support.

QuickUDP provides an Avalon-ST interface with full packet support along with additional metadata about the payload. Because OpenCL does not support the packet extensions, the packetization signals are converted to data, and the OpenCL application must handle all packetization.

QuickUDP also provides additional metadata that the application can use. For a full explanation of these signals, refer to the QuickUDP documentation on the PLDA website. In the Stratix V Network Reference Platform, the payload, packetization signals, and metadata are concatenated into a single 256-bit-wide vector exported as an Intel FPGA SDK for OpenCL channel.

Use the information in the following table to access the desired components of the channel's data:

Table 8. Bit Mapping for the 256-Bit Intel FPGA SDK for OpenCL Channel to QuickUDP

| Bit Range | Name         | Description                                            |

|-----------|--------------|--------------------------------------------------------|

| [0:127]   | payload      | Packet payload                                         |

| [128]     | sop          | Start of packet signal                                 |

| [129]     | eop          | End of packet (EOP) signal                             |

| [130:133] | empty        | On EOP, this field indicates how many bytes are unused |

| [134:149] | payload_size | Size of the packet<br>Set to 0 for outbound packets    |

| [150:181] | rem_ip       | Indicates the remote IP for incoming packets           |

| [182:197] | rem_port     | Indicates the remote port for incoming packets         |

| [198:205] | channel      | Avalon channel                                         |

| [206]     | error        | Avalon error signal                                    |

#### **Related Links**

PLDA website

# 3.6 FPGA System Design

To integrate all components, close timing, and deliver a post-fit netlist that functions in the hardware, you must first address several additional FPGA design complexities. These design complexities include a robust reset sequence, establishment of a design floorplan, global routing management, pipelining, and IP encryption. Optimizations of these design complexities occur in tandem with one another in order to meet timing and board hardware optimization requirements.

### **3.6.1 Clocks**

The following clock domains affect the Platform Designer (Standard) hardware system:

- 250 MHz PCIe clock

- 200 MHz DDR3 clock

- 275 MHz QDR clock

- 156.25 MHz Ethernet clock

- 100 MHz general clock (config\_clk)

- Kernel clock that can take on any clock frequency

With the exception of the kernel clock, the Stratix V Network Reference Platform is responsible for closing timing of these clocks. However, because the board design must clock cross all interfaces in the kernel clock domain, the board design also has logic in this clock domain. It is crucial that this logic is minimal and achieves an Fmax higher than typical kernel performance.

### **Related Links**

Guaranteed Timing Closure on page 31

### **3.6.2 Resets**

The FPGA system design includes the implementation of the following reset drivers:

- 1. The por\_reset\_counter in the board.qsys system implements the power-on-reset. This reset issues a reset for a number of cycles after the FPGA completes configuration. It resets all the hardware on the device.

- 2. The PCIe bus issues a PERST reset that resets all hardware on the device.

- 3. The OpenCL Kernel Interface component issues the kernel\_reset that resets all logic in the kernel clock domain.

The first two resets are combined into a single global\_reset; therefore, there are only two reset sources in the system. However, these resets are explicitly synchronized across the various clock domains, resulting in several reset interfaces.

Important notes regarding resets:

- Synchronizing resets to different clock domains might cause several high fan-out resets.

- Platform Designer (Standard) automatically synchronizes resets to the clock domain of each connected component. In doing so, Platform Designer (Standard) instantiates new reset controllers with derived names that might change when the design changes. This name change makes it difficult to make and maintain global clock assignments to some of the resets. As a result, for each clock domain, there are explicit reset controllers. For example, global\_reset drives reset\_controller\_pcie and reset\_controller\_ddr3a; however, they are synchronized to the PCIe and DDR3 clock domains, respectively. Because both of these resets have high fan-out signals, they are assigned to global routing in the .gsf file.

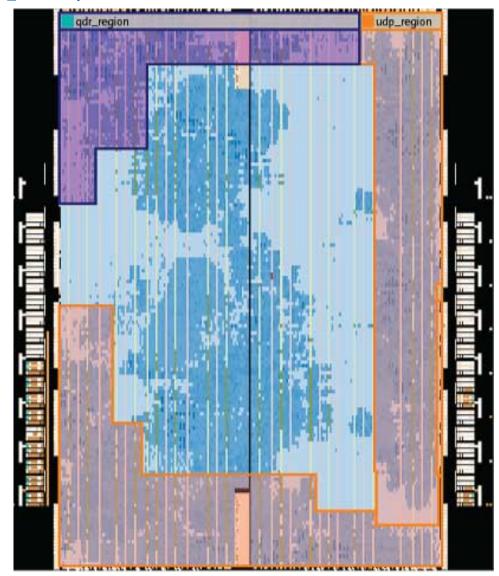

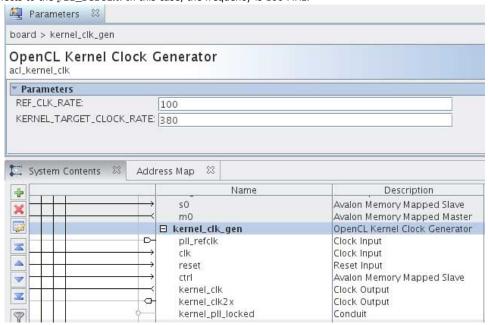

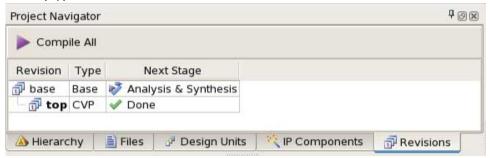

- 2. Resets and clocks must work together to propagate reset to all logic.