# AN 793: Intel® Arria® 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit Reference Design

AN-793 2017.06.13

# **Contents**

| Arr | ia® 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit | -  |

|-----|------------------------------------------------------------------------------|----|

|     | Reference Design                                                             |    |

|     | Clocking Scheme                                                              | ے  |

|     |                                                                              |    |

|     | DisplayPort IP Core                                                          |    |

|     | Video and Image Processing Block                                             |    |

|     | External Memory Interface                                                    |    |

|     | Nios II Processor                                                            |    |

|     | Transceiver                                                                  | 10 |

|     | Push Buttons and LEDs                                                        | 11 |

|     | Reference Design Folders and Files                                           |    |

|     | Quick Start Guide                                                            |    |

|     | Hardware and Software Requirements                                           |    |

|     | Compiling and Running the Reference Design                                   | 14 |

|     | Viewing the Result                                                           |    |

|     | Rebuilding the Nios II Software                                              | 18 |

|     | Reference Design Debug Features                                              |    |

|     | Known Issues                                                                 |    |

|     | Revision History                                                             | 22 |

|     |                                                                              |    |

# Arria<sup>®</sup> 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit Reference Design

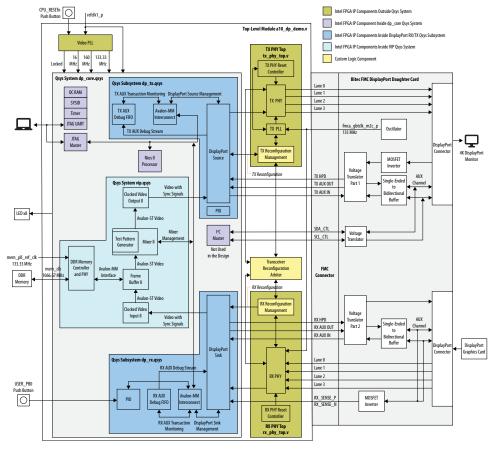

The Arria® 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit reference design demonstrates Intel's video connectivity, the DisplayPort Sink (RX) and Source (TX) functions using a video loop-through system.

Figure 1. Reference Design Block Diagram

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

- 1. The reference design receives video data (up to a resolution of 3840 pixels × 2160 lines) over the DisplayPort RX link.

- 2. The design then converts the received video to Avalon Streaming (Avalon-ST) image stream and stores into the external memory.

- 3. The design mixes the buffered image with a  $3840 \times 2160$  color bar background and sends the combined image to the DisplayPort Source.

- 4. The DisplayPort Source transmits the combined image to a DisplayPort capable monitor over the DisplayPort TX link.

- 5. The DisplayPort interface supports dynamic scaling between 1, 2 and 4 lanes:

- Reduced Bit Rate (RBR) @ 1.62 Gbps/lane

- High Bit Rate (HBR) @ 2.7 Gbps/lane

- High Bit Rate 2 (HBR2) @ 5.4 Gbps/lane

The TX and RX physical layer (PHY) are independent of each other although they are placed at the same transceiver channels; the DisplayPort Sink may run at 1 lane @ 2.7 Gbps while the DisplayPort Source runs at 4 lanes @ 5.4 Gbps concurrently. There is no audio or secondary stream being retransmitted in this reference design.

This reference design is implemented using Intel's Qsys integration tool and standalone HDL modules.

*Note:* The  $I^2C$  interface is not used in this design.

#### **Related Links**

- DisplayPort IP Core User Guide

- Video and Image Processing Suite User Guide

- Arria 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit Reference Design (Quartus Prime Pro Edition)

Click to get the reference design files using the Quartus Prime 17.0 Pro Edition software. Click on the tabs for other versions.

Arria 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit Reference Design (Quartus Prime Standard Edition)

Click to get the reference design files using the Quartus Prime 17.0 Standard Edition software. Click on the tabs for other versions.

Arria 10 GX FPGA Development Kit

Refer to this page for more information about the Arria 10 GX FPGA Development Kit.

FMC DisplayPort Daughter Card

# **Reference Design Components**

The reference design consists of Qsys, PHY, and Clock subsystems.

#### **Table 1.** Reference Design Components

The table lists the major components in the reference design.

| System          | Components                                                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

| Qsys subsystem  | DisplayPort Source and Sink cores                                                                                           |

|                 | Video and Image Processing IP cores  Clocked Video Input II (CVI)  Clocked Video Output II (CVO)  Frame Buffer II  Mixer II |

|                 | Nios II processor                                                                                                           |

|                 | DDR4 External Memory Interface                                                                                              |

|                 | Avalon Memory-Mapped (Avalon-MM) FIFO Memory                                                                                |

|                 | JTAG to Avalon-MM master bridge                                                                                             |

| PHY subsystem   | Simplex TX and RX Native PHY                                                                                                |

|                 | TX fPLL                                                                                                                     |

|                 | Intel® Transceiver PHY Reset Controller                                                                                     |

|                 | TX and RX Bitec reconfiguration module                                                                                      |

|                 | Transceiver reconfiguration arbiter                                                                                         |

| Clock subsystem | IO PLL for video data path                                                                                                  |

# **Clocking Scheme**

The reference design requires several clock sources from the FPGA development kit and the FMC daughter card for proper operation. The reference design uses the default clock frequency from the oscillator; no programming is required through the Clock Control application.

**Table 2. Clock Signals**

| Signal      | Description                                                   | Pin Number | I/O Standard | Usage                                                                 |  |  |  |

|-------------|---------------------------------------------------------------|------------|--------------|-----------------------------------------------------------------------|--|--|--|

| refclk1_p   | External 100 MHz clock from X3 programmable oscillator on the | AG37/AG38  | LVDS         | Avalon-MM interface for<br>DisplayPort and VIP IP cores               |  |  |  |

|             | FPGA development kit.                                         |            |              | Transceiver reconfiguration interface                                 |  |  |  |

|             |                                                               |            |              | TX and RX Bitec<br>reconfiguration management                         |  |  |  |

|             |                                                               |            |              | Transceiver reconfiguration arbiter                                   |  |  |  |

|             |                                                               |            |              | Intel PHY reset controller                                            |  |  |  |

|             |                                                               |            |              | TX PLL and TX/RX transceiver<br>channel reconfiguration<br>interfaces |  |  |  |

|             |                                                               |            |              | Nios II CPU and peripherals                                           |  |  |  |

|             |                                                               |            |              | Video PLL (IO PLL) input<br>reference clock                           |  |  |  |

| fmca_gbtclk | External 135 MHz clock from                                   | AL8/AL7    | LVDS         | TX PLL input reference clock                                          |  |  |  |

| _m2c_p      | Bitec FMC daughter card. The oscillator is not programmable.  |            |              | RX CDR input reference clock                                          |  |  |  |

|             | continued                                                     |            |              |                                                                       |  |  |  |

| Signal              | Description                                                                          | Pin Number | I/O Standard | Usage                                                                                                                                         |

|---------------------|--------------------------------------------------------------------------------------|------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| mem_pll_ref<br>_clk | External 133 MHz clock from U26 programmable oscillator on the FPGA development kit. | F34/F35    | LVDS         | DDR4 external memory interface input reference clock                                                                                          |

| dp_tx_vid_<br>clk   | Generated 133.33 MHz clock from video PLL.                                           |            | -            | DisplayPort Source-Clocked<br>Video Output interface                                                                                          |

| dp_rx_vid_<br>clk   | Generated 160 MHz clock from video PLL.                                              | -          | -            | DisplayPort Sink-Clocked<br>Video Output interface     Avalon-ST video data path                                                              |

| clk_16              | Generated 16MHz clock from video PLL                                                 | -          | -            | DisplayPort Sink and Source     Mbps AUX channel interface     DisplayPort Sink and Source     AUX debug FIFO                                 |

| clk_cal             | Derived 50MHz clock from refclk1                                                     | -          | -            | DisplayPort Sink and Source calibration. This clock must be synchronous to the clock used for the transceiver reconfiguration block (100 MHz) |

The 160 MHz clock output from the video PLL drives the DisplayPort Sink and Clocked Video Input interface. This interface runs at input video pixel clock domain; this clock frequency must be equal or greater than the required pixel clock frequency of the input video stream.

Note:

The ANSI/CEA-861-F standard requires the  $3840 \times 2160 \oplus 60$  Hz video stream to run at 594.0 MHz pixel clock. This design uses 4 pixels per clock so that the interface runs at 148.5 MHz (quarter rate of 594.0 MHz), but with 4 times video bus width between the DisplayPort Sink and Clocked Video Input. Because 160 MHz is higher than 148.5 MHz, this frequency is sufficient to support 4Kp60 input video stream.

The 133.33 MHz clock output from the video PLL drives the DisplayPort Source and Clocked Video Output interface. The CVT-RB specification states that the 133.33 MHz should be derived from the reduced blanking period of the 4K video output stream.

Table 3. 4Kp60 Video Stream Timing Information for Normal and Reduced Blanking

| H Active × V<br>Active | H Total | H Blank | V Total | V Blank | Pixel Frequency |

|------------------------|---------|---------|---------|---------|-----------------|

| Normal                 | 4,400   | 560     | 2,250   | 90      | 594.00 MHz      |

| Reduced                | 4,000   | 160     | 2,222   | 62      | 533.28 MHz      |

This design uses 4 pixels per clock so that the interface runs at 133.33 MHz (quarter rate of 533.28 MHz), but with 4 times wider video bus between the DisplayPort Source and Clocked Video Output.

# **DisplayPort IP Core**

The reference design uses specific DisplayPort IP core parameter settings.

**Table 4.** DisplayPort IP Core Settings for the Reference Design

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | tes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 bpc   | This reference design supports GPU and monitor up to a maximum of 10 bit-per-color depth.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4 Gbps |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | r 4Kp60, 10 bpc video stream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4        | through serial link:  Active video resolution = 3840 × 2160 pixels/frame  Total resolution (including reduced blanking) = 4000 × 2 pixels/frame  Refresh rate = 60 Hz or 60 frames per second  Bits per pixel = 10 bpc × 3 colors = 30 bits per pixel  Total bandwidth = (4000 × 2222) pixel/frame × 60 fram × 30 bits/pixel = 15.9984 Gbits/s  With 8b/10b encoding scheme, the actual bandwidth required = 15.9984 × 10/8 = 19.998 Gbps  With 4 lanes at 5.4 Gbps, the aggregated bandwidth of 2 Gbps is sufficient to support the 4K video stream at 60 Frefresh rate. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dual     | Symbol mode affects the transceiver parallel bus width ar the DisplayPort IP core clock frequency. The DisplayPort I core synchronizes with the transceiver parallel clock. The parallel clock frequency is link rate/transceiver parallel bu width.  The table below shows the frequency for HBR2 (5.4 Gbps                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          | Symbol Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Transceiver Recovered<br>Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          | Dual (20 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5400/20 = 270 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          | Quad (40 bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5400/40 = 135 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Quad     | Pixel mode affects the video clock frequency and width of the IP core.  For 4Kp60 video stream, the bandwidth requirer × 2222 × 60 pixel/s = 533280000 pixels/s. Becanigh bandwidth requirement, the design required quad pixel mode for timing closure.  Pixel Mode  Single (1 pixel/clock)  Dual (2 pixels/clock)  Quad (4 pixels/clock)  133.32 II  Quad (4 pixels/clock)                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          | 4 Dual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The bandwidth requirement for through serial link:  Active video resolution = 3840. Total resolution (including redupixels/frame)  Refresh rate = 60 Hz or 60 fra Bits per pixel = 10 bpc × 3 col Total bandwidth = (4000 × 22 × 30 bits/pixel = 15.9984 Gbit With 8b/10b encoding scheme required = 15.9984 × 10/8 = With 4 lanes at 5.4 Gbps, the Gbps is sufficient to support the refresh rate.  Dual  Symbol mode affects the transithe DisplayPort IP core clock from core synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transithe DisplayPort IP core clock from synchronizes with the transition of the provide synchronizes with the provi |

# **Video and Image Processing Block**

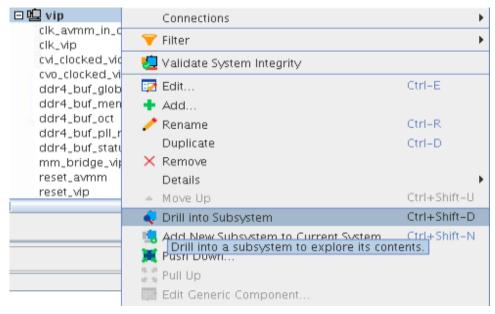

The Video and Image Processing (VIP) block is a subsystem within the Qsys system in the design.

The VIP block receives video data from the DisplayPort Sink, processes and transmits the processed data to the DisplayPort Source. To navigate to the VIP subsystem through dp\_core.qsys, right click **vip**, and select **Drill into subsystem**.

Figure 2. Navigating to the VIP Subsystem

The VIP block comprises the following components:

- Clocked Video Input II IP core: Converts the DisplayPort Sink video output format to Avalon-ST video protocol

- Frame Buffer II IP core: Handles mismatch in RX and TX video data rate through triple-buffering

- Mixer II IP core: Overlays the buffered image on top of the background color bar

- Clocked Video Output II IP core: Converts the Avalon-ST video protocol to the DisplayPort Source video input format

This reference design supports 4K resolution.

Table 5. VIP IP Core Settings for the Reference Design

| IP Core                | Parameter                              | Value    |

|------------------------|----------------------------------------|----------|

| Clocked Video Input II | Bits per pixel per color plane         | 10       |

|                        | Number of color planes                 | 3        |

|                        | Number of pixels in parallel           | 4        |

|                        | Use control port                       | Off      |

| Frame Buffer II        | Maximum frame width                    | 3840     |

|                        | Maximum frame height                   | 2160     |

|                        | Bits per pixel per color plane         | 10       |

|                        | Number of color planes                 | 3        |

|                        | Pixels in parallel                     | 4        |

|                        | Avalon-MM master (s) local ports width | 512      |

|                        | AV-MM burst target write               | 64       |

|                        |                                        | continue |

| IP Core                 | Parameter                                                      | Value                             |

|-------------------------|----------------------------------------------------------------|-----------------------------------|

|                         | AV-MM burst target read                                        | 64                                |

|                         | Frame dropping                                                 | On                                |

|                         | Frame repeating                                                | On                                |

|                         | Drop invalid frames                                            | On                                |

|                         | Run-time writer control                                        | Off                               |

| Mixer II                | Maximum output frame width                                     | 3840                              |

|                         | Maximum output frame height                                    | 2160                              |

|                         | Bits per pixel per color plane                                 | 10                                |

|                         | Number of pixels in parallel                                   | 4                                 |

|                         | Colorspace (used for background layer)                         | RGB                               |

|                         | Pattern                                                        | Color bars                        |

|                         | How user packets are handled                                   | Discard all user packets received |

| Clocked Video Output II | Image width / Active pixels                                    | 3840                              |

|                         | Image height / Active lines                                    | 2160                              |

|                         | Bits per pixel per color plane                                 | 10                                |

|                         | Number of color planes                                         | 3                                 |

|                         | Number of pixels in parallel                                   | 4                                 |

|                         | Separate syncs only - Frame/ Field 1<br>Horizontal sync        | 32                                |

|                         | Separate syncs only - Frame/ Field 1<br>Horizontal front porch | 48                                |

|                         | Separate syncs only - Frame/ Field 1<br>Horizontal back porch  | 80                                |

|                         | Separate syncs only - Frame/ Field 1 Vertical sync             | 5                                 |

|                         | Separate syncs only - Frame/ Field 1 Vertical front porch      | 3                                 |

|                         | Separate syncs only - Frame/ Field 1 Vertical back porch       | 54                                |

|                         | Pixel FIFO size                                                | 3840                              |

|                         | FIFO level at which to start output                            | 3839                              |

|                         | Use control port                                               | Off                               |

# **External Memory Interface**

The Frame Buffer II IP core uses the external SDRAM to triple-buffer video frames and handle mismatch in RX and TX video data rates.

The IP core writes to the memory to store input pixels and reads from the memory to retrieve video frames and transmit them. The Arria 10 FPGA Development Kit has a HiLo connector for the DDR4 module. The DDR4 module is part of the development kit. The module has x72 @ 1200 MHz interface.

The **Arria 10 GX FPGA Development Kit with DDR4 HiLo** preset applies to the External Memory Interface instance, except for DQ width set to 64. The Frame Buffer II IP core supports up to a DQ width of x64.

# **Nios II Processor**

The DisplayPort Source and Sink require a processor (e.g. Nios II processor) to act as link policy maker.

The design requires the **Enable GPU Control** option for the DisplayPort Sink to be turned on.

The Nios II processor performs the following functions:

- Runs software that acts as a DisplayPort link policy maker.

- Provides access to the DisplayPort IP core status and debug registers.

- Retrieves AUX channel transaction logs from the DisplayPort Source and Sink AUX debug FIFO.

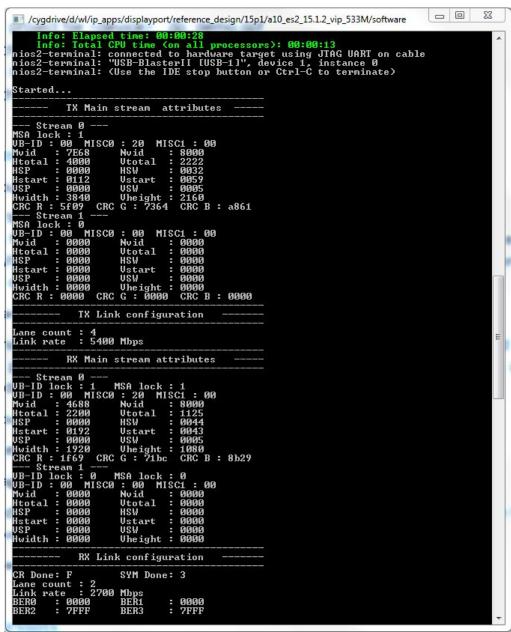

- Monitors push buttons to print Main Stream Attribute (MSA) values and AUX channel transaction logs to the Nios II terminal.

- Initializes the VIP Suite IP cores.

#### **Transceiver**

The DisplayPort main link uses the Native PHY IP core for serial communication between the GPU and monitor.

The reference design uses separate simplex TX and RX PHY blocks because the TX and RX channels may run at different data rates based on the link training results.

#### **Table 6.** Native PHY Parameter Settings

| Parameter                        | Value    | Corresponding DisplayPort Source/Sink<br>Parameters |

|----------------------------------|----------|-----------------------------------------------------|

| Number of data channels          | 4        | Maximum lane count = 4                              |

| Data rate (Mbps)                 | 5,400    | TX/RX maximum link rate = 5.4 Gbps                  |

| Standard PCS/PMA interface width | 20       | Symbol input/output mode = Dual                     |

| TX/RX byte serializer mode       | Disabled |                                                     |

The design uses two Intel transceiver PHY reset controllers to control the TX and RX PHY blocks independently.

Note:

The 70  $\mu$ s delay is not applied to the transceiver PHY reset controllers because the delay is too long for the DisplayPort Source and Sink cores to complete the link training. Instead, the design uses the acknowledgment model.

The Bitec reconfiguration management module controls the reset input of the PHY reset controllers, and manages the dynamic reconfiguration of the TX PHY, RX PHY and TX PLL blocks for data rate switch and PMA analog settings (TX VOD and preemphasis). To fulfill the simplex TX and RX PHY channel merging requirement, a transceiver arbiter is inserted in between the Bitec reconfiguration module Avalon-MM master and the PHY reconfiguration Avalon-MM slave interface.

# **Push Buttons and LEDs**

The reference design uses the push buttons and LEDs on the Arria 10 FPGA Development Kit as functional indicators.

#### Table 7. Push Buttons

| Function           | Pin Number/<br>I/O Standard | Schematic Net Name | Reference<br>Designator | Description                                                                          |

|--------------------|-----------------------------|--------------------|-------------------------|--------------------------------------------------------------------------------------|

| Reset              | BD27/1.8V                   | CPU_RESETn         | S4                      | Resets the reference design.                                                         |

| Display MSA values | T12/1.8V                    | USER_PB0           | S3                      | Display the current TX/RX MSA values and link configuration on the Nios II terminal. |

#### Table 8. LEDs

| Function                      | Pin Number/<br>I/O Standard                              | Schematic Net Name                                          | Reference<br>Designator    | Description                                                                                                                                                                                                                                                          |

|-------------------------------|----------------------------------------------------------|-------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DisplayPort Sink video locked | L28/1.8V                                                 | USER_LED_G0                                                 | D10                        | When illuminated, it indicates that the DisplayPort Sink video output stream to the Clocked Video Input IP core is stable.                                                                                                                                           |

| DisplayPort Sink lane count   | K26/1.8V<br>K25/1.8V<br>L25/1.8V<br>J24/1.8V<br>A19/1.8V | USER_LED_G1 USER_LED_G2 USER_LED_G3 USER_LED_G4 USER_LED_G5 | D9<br>D8<br>D7<br>D6<br>D5 | 5-bit indicator of the lane count at the DisplayPort Sink. The LED arrangement is {D5, D6, D7, D8, D9}:  • 00001 = 1 lane  • 00010 = 2 lanes  • 00100 = 4 lanes If LED D7 illuminates while other LEDs are off, the lane count at the DisplayPort Sink is 4.         |

| DisplayPort Sink link rate    | C18/1.8V<br>D18/1.8V                                     | USER_LED_G6<br>USER_LED_G7                                  | D4<br>D3                   | 2-bit indicator of the link rate at the DisplayPort Sink. The LED arrangement is {D3, D4}:  • 00 = 1.62 Gbps (RBR)  • 01 = 2.70 Gbps (HBR)  • 10 = 5.40 Gbps (HBR2)  If LED D3 illuminates while LED D4 is off, the DisplayPort Sink is operating at HBR2 link rate. |

# **Reference Design Folders and Files**

All the relevant design files reside in the project folder.

# Table 9.

| Folder/File Name                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rtl/core/altera_avalon_i2c                                                                                                           | Contains $I^2C$ master source files. $I^2C$ master is not used in this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| rtl/core/dp_core                                                                                                                     | Contains the generated IP files and subfolders in dp_core.qsys of the Qsys system.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| rtl/core/ip/dp_rx                                                                                                                    | Contains the generated IP files and subfolders in dp_rx.qsys of the Qsys subsystem  Note: Only for Quartus® Prime Pro Edition.                                                                                                                                                                                                                                                                                                                                                                                            |

| rtl/core/ip/dp_tx                                                                                                                    | Contains the generated IP files and subfolders in dp_tx.qsys of the Qsys subsystem.  Note: Only for Quartus Prime Pro Edition.                                                                                                                                                                                                                                                                                                                                                                                            |

| rtl/core/ip/vip                                                                                                                      | Contains the generated IP files and subfolders in vip.qsys of the Qsys subsystem.  Note: Only for Quartus Prime Pro Edition.                                                                                                                                                                                                                                                                                                                                                                                              |

| master_image                                                                                                                         | Contains precompiled .sof and .elf files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| rtl/rx_phy/gxb_rx                                                                                                                    | Contains generated RX PHY IP files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| rtl/rx_phy/gxb_rx_reset                                                                                                              | Contains generated RX PHY reset controller IP files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| rtl/tx_phy/gxb_tx                                                                                                                    | Contains generated TX PHY IP files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| rtl/tx_phy/gxb_tx_fpll                                                                                                               | Contains generated TX fPLL IP files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| rtl/tx_phy/gxb_tx_reset                                                                                                              | Contains generated RX PHY reset controller IP files.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| rtl/i2c_gpio_buf                                                                                                                     | Contains generated IO buffer IP files for the $\rm I^2C$ master interface. $\rm I^2C$ master is not used in this reference design.                                                                                                                                                                                                                                                                                                                                                                                        |

| rtl/video_pll_a10                                                                                                                    | Contains generated IO PLL IP files for video PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| software                                                                                                                             | Contains the Nios II software project. The <code>dp_demo.zip</code> file contains the software project; the <code>dp_demo</code> folder contains the <code>.qip</code> and <code>.hex</code> files of the software project.                                                                                                                                                                                                                                                                                               |

| tcl                                                                                                                                  | Contains the TCL script for debugging purpose.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| software/main.c,<br>software/rx_utils.c,<br>software/tx_utils.c,<br>software/tx_utils.h,<br>software/config.h, and<br>software/vip.h | These are the C source code and header files. You can customize these files for your applications. These files will be copied to the software folder when you run the build_sw.sh script.                                                                                                                                                                                                                                                                                                                                 |

| top.qpf and top.qsf                                                                                                                  | The Quartus Prime project and setting files for this reference design.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <pre>rtl/core/dp_core.qsys, rtl/core/dp_rx.qsys, rtl/core/dp_tx.qsys, and rtl/core/vip.qsys</pre>                                    | The dp_core.qsys file belongs to the top level Qsys system. The dp_rx.qsys file belongs to the DisplayPort RX Qsys subsystem, the dp_tx.qsys file belongs to the DisplayPort TX Qsys subsystem, and the vip.qsys file belongs to the VIP Qsys subsystem. The design includes the dp_rx.qsys, dp_tx.qsys, and the vip.qsys files so that dp_core.qsys loads correctly into Qsys.  **Note:* For Quartus Prime Standard Edition designs, do not include the dp_rx.qsys, dp_tx.qsys, and vip.sys files in the top.qsf file to |

| rtl/rx_phy/qxb_rx.qsys                                                                                                               | avoid synthesis error.  RX Native PHY instance variant file.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| rtl/rx_phy/gxb_rx_reset.qsys                                                                                                         | RX Native PHY's transceiver PHY reset controller instance variant file.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| rtl/tx_phy/gxb_tx.qsys                                                                                                               | TX Native PHY instance variant file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                      | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Folder/File Name             | Description                                                                                                                                                                                   |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| rtl/tx_phy/gxb_tx_reset.qsys | TX Native PHY's transceiver PHY reset controller instance variant file.                                                                                                                       |  |

| rtl/tx_phy/gxb_tx_fpll.qsys  | TX Native PHY's FPLL instance variant file.                                                                                                                                                   |  |

| rtl/i2c_gpio_buf.qsys        | I <sup>2</sup> C buffer instance variant file. This buffer is not used in this reference design.                                                                                              |  |

| rtl/video_pll_a10.qsys       | IO PLL instance variant file.                                                                                                                                                                 |  |

| rtl/example.sdc              | Top level SDC timing constraint file.                                                                                                                                                         |  |

| script/build_sw.sh           | Shell script to re-build the NIOS II software.                                                                                                                                                |  |

| script/rerun.sh              | Shell script to load the FPGA hardware image (.sof) and software image (.elf).                                                                                                                |  |

| dp_core.sopcinfo             | The build_sw.sh script uses this file to rebuild the Nios II software for the control Qsys system.                                                                                            |  |

| Others sopcinfo files        | These files are not needed to rebuild the Nios II software.                                                                                                                                   |  |

| quartus/dp_vip_xcvr.stp      | SignalTap II file for debug purpose.                                                                                                                                                          |  |

| rtl/a10_reconfig_arbiter.sv  | HDL module to arbitrate access to the Avalon-MM interface of the TX and RX Native PHY. This module is needed for merging simplex TX/RX Native PHY into the same physical transceiver channel. |  |

| rtl/mr_rate_detect.v         | HDL module to measure clock frequency.                                                                                                                                                        |  |

| rtl/a10_dp_demo.v            | Top-level HDL file for this reference design.                                                                                                                                                 |  |

| rtl/bitec_reconfig_alt_a10.v | HDL module to dynamically reconfigure the TX/RX Native PHY and TX fPLL for data rate switching.                                                                                               |  |

| filelist.txt                 | A list of all the files consisting in this design.                                                                                                                                            |  |

# **Quick Start Guide**

The reference design features a hardware design that supports compilation and hardware testing.

# **Hardware and Software Requirements**

To test the reference design, ensure that you have the appropriate hardware and software.

#### **Hardware**

- Arria 10 GX FPGA Development Kit (10AX115S2F45I1SG)

- DDR4 HiLo module installed on the development kit

- Bitec FMC daughter card revision 5.0 or later

- 2 DisplayPort cables

- Micro USB cable

- PC with graphic card that supports 3840 × 2160 resolution

- Monitor that supports 3840 × 2160 resolution

#### **Software**

• Intel Quartus Prime (for hardware testing)

The reference design is tested with AMD Radeon HD 7700 graphic card, and NVIDIA\* NVS\* 310 and ASUS\* MG28UQ 4K monitors.

#### **Related Links**

Arria 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit Reference Design (Quartus Prime Pro Edition)

Click to get the reference design files using the Quartus Prime 17.0 Pro Edition software. Click on the tabs for other versions.

Arria 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit Reference Design (Quartus Prime Standard Edition)

Click to get the reference design files using the Quartus Prime 17.0 Standard Edition software. Click on the tabs for other versions.

Arria 10 GX FPGA Development Kit

Refer to this page for more information about the Arria 10 GX FPGA Development Kit.

FMC DisplayPort Daughter Card

# **Compiling and Running the Reference Design**

Use the provided design files to run the reference design. Intel also provides precompiled alo\_dp\_demo.sof and dp\_demo.elf files as part of the project file in the master image directory.

Follow these steps to run the reference design:

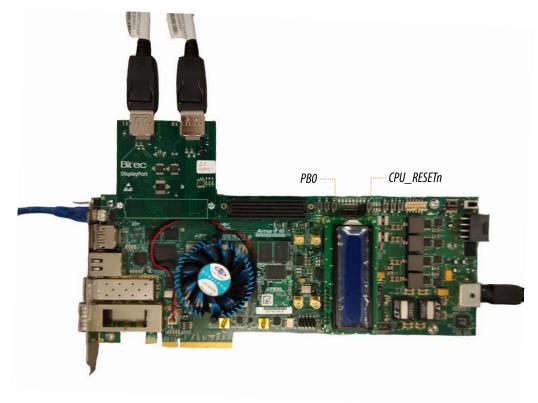

- 1. Configure your PC to produce an image at resolution of  $1920 \times 1080$ .

- 2. Install the Bitec FMC daughter card at FMC port A of the development kit.

- 3. Install the DDR4 HiLo module onto the development kit.

- 4. Connect the development kit to your PC using a micro USB cable.

- 5. Connect the DisplayPort cable from your monitor to the TX DisplayPort connector on the FMC daughter card.

- 6. Connect the DisplayPort cable from your PC to the RX DisplayPort connector on the FMC daughter card.

- 7. Power up the development kit.

- 8. Extract the reference design to your PC.

- 9. Launch the Nios II command shell. Navigate to the script directory in the reference design project folder.

- 10. Load the design into the FPGA by typing ./rerun.sh at the Nios II command shell.

- a. To use the precompiled alo\_dp\_demo.sof and dp\_demo.elf files, make sure the files are in the following directory in the rerun.sh script:

```

SOPC_DIR=../master_image

APP_DIR=../master_image

```

b. To use your own compiled .sof file and rebuild the .elf file, make sure the files are in the following directory in the rerun.sh script and the name of the .sof file is correct:

```

SOPC_DIR=../quartus

```

APP\_DIR=../software/dp\_demo SOF\_NAME=top.sof

11. The script loads the .sof file, then the .elf file and launches the Nios II terminal.

Note: If you have more than 1 development kit or Intel FPGA Download Cable connected to your PC, you need to type ./rerun.sh<use cable number>. To find the cable number, type jtagconfig at the DOS command prompt.

12. Extract the dp\_demo.zip file and place the extracted folders in the software folder. The dp\_demo.zip file contains the .hex file for the Nios II software image. (Optional)

# **Viewing the Result**

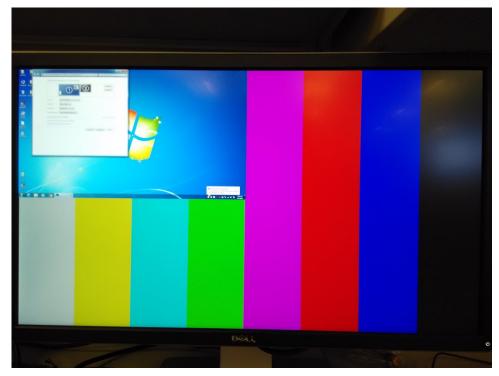

The result shows if your design runs correctly.

After you run the design, you should see the image from your PC overlapping with the color bar background.

Note:

If you do not see visible output on the monitor, press push button CPU\_RESETn (S4) to generate a reset, causing the DisplayPort TX core to retrain the link.

Figure 3. Arria 10 FPGA Development Kit Hardware Setup

Figure 4. **Image from PC Mixed with Color Bar Background**

You can scale the image to the maximum resolution of 3840  $\times$  2160. You should see the image getting refreshed on the screen.

Figure 5. No Color Bar Background at 3840 × 2160 Image Resolution

At this resolution, the image from the PC covers the entire color bar background.