#### intel.

# Automotive

#### Paving the way to productivity

#### CONNECTIVITY

FUNCTIONAL SAFETY

EMBEDDED VISION

IP

POWER

#### MOTOR CONTROL

**DESIGN TOOLS**

FPGAs

AUTOSAR

SaCa

SoCs

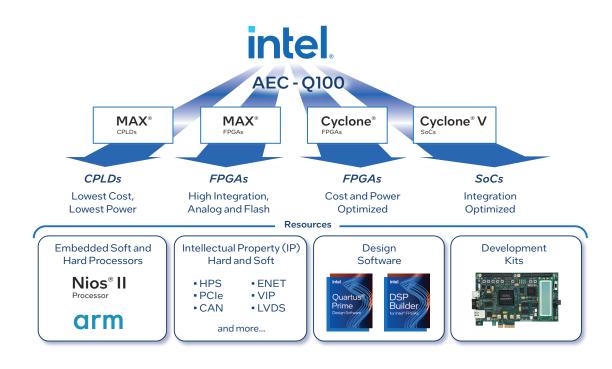

For more than twelve years, Intel has been delivering AEC-Q100 qualified programmable logic devices (PLD), including Intel® MAX® CPLDs, Intel® Cyclone®, and Intel® MAX 10 family of FPGAs and SoCs, to our valued automotive OEM and Tier 1 customers. We understand the rigorous quality, reliability, and supply-chain requirements of our automotive customers and have implemented several programs to address these requirements, such as zero defect philosophy, continuous improvement, and product lifecycles of more than 15 years.

# Why FPGA?

Market research indicates FPGAs and PLDs in automotive will grow at double digit compound annual growth rates (CAGR) over the next several years. Intel's key automotive focus areas include some of the fastest growing segments in the industry, such as Infotainment and Driver Information, Advanced Driver Assistance System (ADAS), and E-Vehicle and Powertrain. Each of these application areas are undergoing a metamorphosis sparked by the proliferation of electronic content in vehicles and the associated megatrends driving them. Why the need for programmable logic in automotive? Three reasons: Scalability, flexibility, and raw performance. FPGAs are the only solution that are able to truly scale architectures from entry-level to luxury model vehicles by offering a wide range of logic densities, optional embedded Arm cores and peripherals, and a single software development flow. This helps engineering managers and system designers get their products to market faster, more efficiently, and at a lower total cost of ownership, while maintaining the ability to make last minute tweaks prior to production launch.

### Get to Market Faster

Intel's total solution offering helps our customers go from proof-of-concept to production in the shortest possible time. How? By complementing our silicon with development tools to help software and hardware engineers port their designs to FPGA or create new ones from the ground up. We've got you covered whether it's industry standards like Open Computing Language (OpenCL<sup>™</sup>), AUTOSAR, Intel® Quartus® Prime Software development tool, or complementary solutions such as DSP Builder for Intel® FPGAs that bridge between the Intel Quartus Prime Software and MATLAB/Simulink. Many of our design tools and methodologies have been certified by TÜV Rheinland to ensure the highest level of quality, integrity, and safety. Lastly, every programmable logic device requires power management and Intel is the only FPGA supplier to offer optimized power management solutions. Intel's power management products deliver the industry's first family of PowerSoC DC-DC converters featuring integrated inductors. They provide an industry-leading combination of highefficiency, small-footprint, and low-noise performance in an integrated product. Unlike discrete power products, these turnkey solutions give designers complete power systems that are fully simulated, characterized, and production qualified. With our new AEC-Q100 qualified PowerSoCs, automotive system designers can now leverage both power management and programmable logic from a single trusted supplier. Intel is here to help you deliver a total proven solution on time.

<sup>1</sup> Certified by TÜV Rheinland

## Safety First

Functional safety has long been a key strategic imperative for us, and Intel was the first FPGA supplier to achieve IEC 61508 functional safety certification<sup>1</sup> for the industrial market. That early commitment and investment has put us in a leading position to execute on our ISO 26262 functional safety plan for automotive applications. The Cyclone V SoC safety manual (automotive functional safety data pack) and device level FMEDA are available now, and the full qualification to ISO 26262 is expected by mid-2015. Intel is an active member of the ISO 26262 working group and our functional safety manager co-chairs the ISO 19451 PLD sub-group, which helps to drive PLD requirements into the 2nd edition of the ISO 26262 standard.

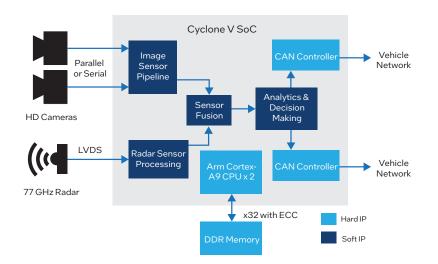

### Advanced Driver Assistance Systems

Our FPGAs can help you keep pace with the rapid advancements in driver assistance technology and address the key challenges you face, including:

- Running multiple ADAS algorithms in parallel in a single low-cost SoC

- Delivering a scalable, low-cost solution tailored to address the requirements of different vehicle models

- Leveraging your intellectual property (IP) investments across multiple products

- Operating within the power and thermal limits of small camera modules without active cooling

- Incorporating new features to differentiate your products in the market

Our FPGAs provide an ideal platform for developing highperformance, low-power, low-cost ADAS systems with the optimal level of integration and flexibility. You can incorporate changes late in the design cycle and deploy in-field upgrades that let you differentiate your products and keep pace with your customers' expectations.

### Benefits of Intel FPGAs in ADAS Applications

- Parallel-processing architecture to run multiple ADAS algorithms simultaneously

- Scalability and differentiation, which allows you to include the latest features that can be deployed into all vehicle platforms

- Increased productivity using software-based design methodologies with open standards like OpenCL and model-based design using MATLAB and DSP Builder for Intel FPGAs

- Simplified software development with an AUTOSARcompliant MCAL layer developed using an ASIL-B methodology supported in our Cyclone V SoCs

- Ability to deliver the highest performance/watt vs. CPU, graphics processing unit (GPU), and ASSP devices

- Flexibility to be used as either the main processing device or a companion FPGA to offload high-performance processing tasks and incorporate new features

#### **FPGA** Applications

- Forward, surround-view cameras

- 77-79 GHz digital radar

- V2X communications

- Radar and video sensor fusion

#### Cyclone V SoC Development Resources

- OpenCL-based design flow

- MATLAB to DSP Builder for Intel FPGAs model-based design

- AUTOSAR v4.0.3 MCAL

- ISO 26262 functional safety data package

**Forward Camera Sensor Fusion**

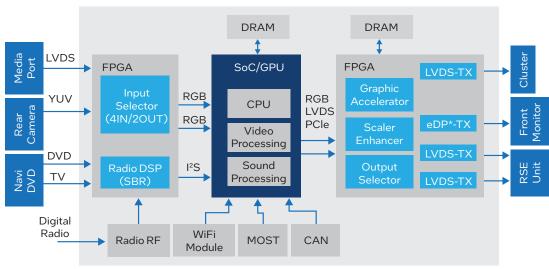

### Infotainment

Automotive infotainment systems are an integral part of modern vehicle design and greatly influence global vehicle sales. You need to continually create compelling new technology that both rivals and complements the latest consumer devices while keeping up with the pace of product obsolescence common in consumer electronics.

It is important to select the right main system processor to differentiate the system's user interface with the latest graphics. Should you choose a high-performance SoC with a GPU or a CPU with applications that can be upgraded with software?

With multiple models to support, you may need to select several different SoCs due to system variations and emerging interfacing technologies. This is neither cost effective nor efficient usage of engineering resources.

By using our FPGAs as an I/O companion, you can support any combination of I/O interfaces. You may also leverage the FPGA as an efficient coprocessor to offload functions from your host main processor such as video scaling and graphics acceleration. With an FPGA, your system becomes easily scalable, enabling you to upgrade firmware on the fly to support multiple manufacturers, regions, and models with minimum changes to the hardware.

Pre and Post Video Processing Video Companion Application

### Benefits of Intel FPGAs in Infotainment Applications

- Support multiple camera inputs in any bit rate or resolution via video select and front-end processing

- Support multiple display interfaces and offloads GPU

- Optimize system performance by integrating 2D/3D graphic accelerator, scalar, image enhancer, and interface protocol bridge

- Reduce cost by integrating radio digital signal processing (DSP) into FPGA with software-based radio IP

- Accelerate time to market by supporting the latest generation of interface standards in programmable logic

- Minimize PCB spins and future-proof your system with in-field upgrades to the FPGA

\* Embedded Display Port

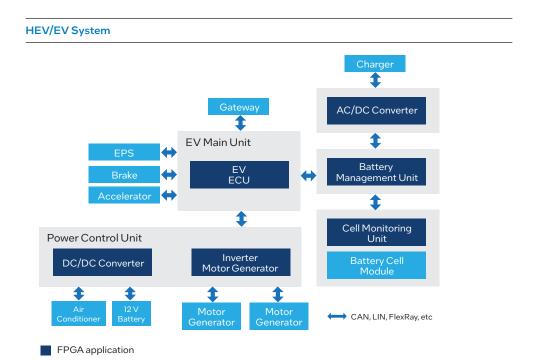

### Electric Vehicles and Powertrain

The introduction of hybrid-electric vehicles (HEV) and electric vehicles (EV) have enabled breakthrough innovations and greater efficiency in electric motor controls, power conversion, and battery management systems.

The algorithms driving these systems require continuous upgrades and design changes to optimize performance. ASIC development cycles are too long to meet these market demands and microcontroller units (MCUs) are unable to keep up with performance requirements. Our FPGAs deliver hardware failsafe logic for insulated gate bipolar transistor (IGBT) bridge protection, efficient motor control with our model-based DSP Builder for Intel FPGAs design flow, and hardware acceleration with faster control loops to improve energy efficiency, reduce noise, and improve reliability of electrical motors.

You can use FPGAs or CPLDs anywhere DSP is needed to improve system performance, such as the AC/DC converters, DC/DC converters, battery management systems, and motor inverter systems.

To accelerate your time to market and increase productivity, Intel and its partner network offer a variety of IP and tools. Our motor control IP includes pulse-width modulation (PWM), analog-to-digital (ADC) and digital encoder interfaces, and integrated customizable field-oriented control (FOC) reference designs.

### Benefits of Intel FPGAs in HEV/EV Applications

- Improve system performance by using hardware coprocessor to accelerate your motor control algorithm

- Shorten design cycles with model-based design tools, safety methodology, and pre-qualified devices

- Designed for functional safety with IEC 61508-certified design tools, IP, and products (ISO 26262 certification expected mid 2015 for Cyclone V SoC)

- Low latency and fast response in FPGA logic for motor control loops

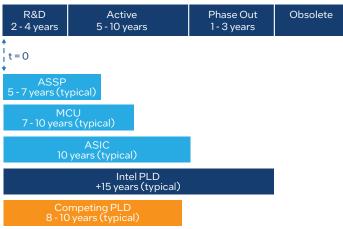

### Driving Quality Designs

As automotive digital content and control systems move to high definition, wireless communication, and multi-gigabit bandwidths, automakers and system OEMs will continue to demand top-notch quality semiconductor devices. With tens of millions of programmable logic devices shipped to automotive customers worldwide since 2003, we are well positioned for high-volume automotive production.

As an active member of the Automotive Electronics Council (AEC), Intel has chaired two AEC subcommittees and qualifies all of its automotive or "A" grade products to the AEC-Q100 standard. Our production part approval process (PPAP) includes the AEC-Q100 qualification results in the document package we provide to qualify your products. The PPAP provides the base- line product details including die, package, wafer fabrication process, package assembly process, and constituent materials.

We have a zero-defect philosophy, with rigorous procedures at each phase of development to ensure the highest quality and lowest defective parts per million (DPPM). Our wafer fabs, package, assembly, test, and programming facilities are TS-16949 certified for a quality management system that provides for continual improvement, emphasizes defect prevention, and reduces variation and waste in the supply chain.

We take business continuity planning (BCP) seriously and employ several initiatives to ensure you have a continuous supply of product, including use of six fabs across four locations, dual

fab strategy by Fabmatch methodology, multiple assembly site sourcing, and sub-material sourcing control.

We understand that you need to support your products and vehicles for a minimum of 10 years after release. Our average product cycle is 15 years, with many of our products having lifetimes in excess of 20 years, so you can design in our products with confidence. When change is absolutely mandatory, we take exceptional care to provide special product change notifications so you can manage the delicate rollout of changes to your customers —the automakers—in a coordinated and well-orchestrated manner.

#### Intel's TS-16949 Compliant Manufacturing Flow

Life Cycle Comparison

#### Alignment to application life cycle dynamics

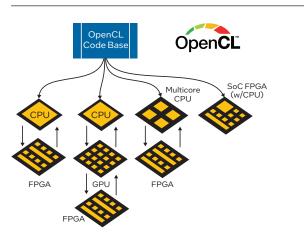

### OpenCL Development Flow Delivers Prototypes in Minutes

OpenCL enables FPGAs to be programmed in a C-like language instead of the traditional register transfer level (RTL) programming language. This enables FPGAs to be more accessible to software engineers who traditionally do not use RTL and are more familiar with C-based languages. Using this methodology, software engineers can now target FPGAs to increase performance and flexibility over CPU or GPU-based systems while using significantly less power. This combination of increased performance, flexibility and reduced power is ideal for automotive designs that require semiconductor devices to process huge volumes of data in an energy-efficient fashion. OpenCL design is supported today in Intel's automotive qualified Cyclone V SoC family.

#### Portability Across Heterogeneous Platforms

### Safety First! Intel's Leadership in Functional Safety Expands to ISO 26262

The automotive industry is adding multiple active safety systems to reduce the risk of injury and harm. Adapted from the IEC 61508 functional safety standard, the ISO 26262 automotive electronic system safety standard helps you avoid systematic faults and also detect, control, and mitigate any random hardware faults that may cause a malfunction of the system.

To simplify and speed up your certification process, we are working with TÜV Rheinland, an independent third-party assessor specializing in functional safety testing and certification, to receive qualification to ISO 26262. Intel is the first FPGA supplier whose FPGAs, diagnostics IP, development tools, and FPGA design flow are all certified for the IEC 61508 functional safety standard. Our Functional Safety Data Pack (FSDP) typically saves customers 12-18 man months in certifying their safety applications.

Intel's Cyclone V SoC family will be the first family qualified for ISO 26262 with our Automotive Functional Safety Data Pack (AFSDP). A detailed safety manual and general FMEDA application note are available now to start your design along with a suite of diagnostics IP. Additionally, we are developing a detailed FMEDA calculator tool to support required hardware architectural metric calculations. Audit and certification are scheduled for mid-2015.

#### Development Without "TüV-Qualified Safety Package"

Intel's functional safety approach is a holistic one, which provides guidance in methodology, backed up with qualified tools that increase your tool confidence and may eliminate the use of redundant tool chains. Next, we offer a safety- ready suite of diagnostics IP and expert technical support along with our certified PLDs. Functional safety documentation, reliability reports, and our TÜV certificate will assist you in the certification of your systems. Safety first!

For additional details on our ISO 26262 functional safety program, please visit:

www.intel.com/content/www/us/en/automotive/products/ programmable/applications.html

### Common Automotive IP – Intel and Partne

Intel and its partners offer a broad portfolio of off-the-shelf, configurable IP cores for our devices. This pre-validated IP can help you further accelerate your design flow. Examples include:

| INTERFACE IP                                  |                  |  |  |  |  |  |  |  |

|-----------------------------------------------|------------------|--|--|--|--|--|--|--|

| Connectivity                                  | Provider(s)      |  |  |  |  |  |  |  |

| CAN                                           | Bosch, CAST, IFI |  |  |  |  |  |  |  |

| LIN                                           | Bosch, CAST      |  |  |  |  |  |  |  |

| FlexRay                                       | Bosch            |  |  |  |  |  |  |  |

| DisplayPort / eDP                             | Intel / Bitec    |  |  |  |  |  |  |  |

| PCI Express <sup>®</sup> (PCIe <sup>®</sup> ) | Intel FPGA IP    |  |  |  |  |  |  |  |

| OpenLDI                                       | Intel FPGA IP    |  |  |  |  |  |  |  |

| GRAPHICS IP                                                                         |                   |

|-------------------------------------------------------------------------------------|-------------------|

| Function                                                                            | Provider(s)       |

| Video and Image Processing suite:<br>scaler, converters, Alpha Blender, and<br>more | Intel             |

| 2D/3D Graphics, HMIs, Video I/O                                                     | TES               |

| Video and graphics                                                                  | Imagem Technology |

| DisplayPort / eDP                                                                   | Intel/Bitec       |

| Video codec                                                                         | CAST              |

### Graphic and Video IP – Partners

When graphical needs exceed 7-segment or matrix displays, and a dedicated GPU is over-kill, enhanced graphics can be implemented with partner IP in the FPGA fabric. This can range from dedicated functions, such as 3D format conversion, image warping, to full 2D or 3D capable soft GPUs. The table below highlights two examples from the large Intel network of IP providers with unique graphical IP solutions.

| FUNCTIONALITY<br>/IP                                                                                                                                 | ATTRIBUTES                                                                                                       | PARTNER/BRAND/<br>WEBSITE                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| <ul> <li>HMI solutions</li> <li>Video Frame<br/>Grabber</li> <li>Graphics<br/>Rendering</li> <li>ML-Display<br/>Controller</li> </ul>                | <ul> <li>Deployed in</li> <li>&gt;3M vehicles</li> <li>Small<br/>footprint</li> <li>Low-power<br/>GPU</li> </ul> | Imagem Technology<br>ATHLET<br>www.imagem-<br>technology.com             |

| <ul> <li>HMI System<br/>Solutions</li> <li>2D / 3D Soft GPUs</li> <li>Warping</li> <li>Video IOs,<br/>Multiview</li> <li>3D Surround View</li> </ul> | <ul> <li>IPs</li> <li>System<br/>solutions</li> <li>Services</li> </ul>                                          | TES Electronic<br>Solutions<br>D/AVE, GUILIANI<br><u>www.tes-dst.com</u> |

## Intel FPGA Development Boards

Jump start your prototype with an Intel FPGA development board. You can purchase Intel Cyclone FPGA development boards from Intel Solutions Marketplace. Additional boards and daughtercards are available from partners.

| FAMILY/DENSITY                                                                               | PARTNUMBER        | IMAGE |

|----------------------------------------------------------------------------------------------|-------------------|-------|

| <b>Cyclone V SX SoC</b><br>Dual-core Arm Cortex-A9 processor,<br>110K LE, 3 Gbps Transceiver | DK-DEV-5CSXC6N/ES |       |

| <b>Cyclone V GT</b><br>301K LE, 5 Gbps Transceiver                                           | DK-DEV-5CGTD9N    |       |

| <b>Cyclone V E</b><br>149K LE                                                                | DK-DEV-5CEA7N     |       |

| <b>Cyclone IV GX</b><br>149.8K LE, 3 Gbps Transceiver                                        | DK-DEV-4CGX150N   |       |

| <b>Cyclone IV GX Starter</b><br>14.4K LE, 2.5 Gbps Transceiver                               | DK-START-4CGX15N  |       |

| <b>Intel MAX 10</b><br>50K LE, ADC                                                           | DK-DEV-10M50-A    |       |

| Intel MAX 10<br>8K LE, ADC                                                                   | EK-10M08E144ES    |       |

| <b>MAX V</b><br>570 LE                                                                       | DK-DEV-5M570ZN    |       |

### Automotive Grade Products

Our automotive-grade devices feature junction temperature support from -40°C to +125°C (or higher on selected devices). These devices meet or exceed ISO 9001:2001 and AEC-Q100 standards. All our automotive-grade devices are manufactured at fully TS-16949-registered/certified sites using some of programmable logic industry's smallest, highest reliability, and mainstream semiconductor fabrication processes. Our automotive-grade portfolio spans CPLDs to FPGA and also includes SoCs as well as power management PowerSoCs.

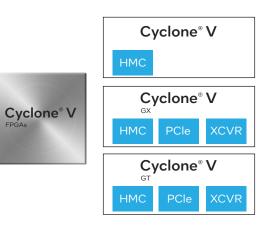

### Introducing the Cyclone V SoC

The Cyclone V SoC integrates an Arm-based hard processor system (HPS) with our FPGA fabric. These user-customizable SoCs increase system performance, lower power consumption, and reduce board space requirements, all designed to help you lower your overall system cost.

#### Cyclone V SoC key features:

- AEC-Q100 automotive-grade options

- Dual-core Arm Cortex A9 processors, 700 MHz

- Vertical and horizontal migration

- 3 Gbps and 5 Gbps transceiver options

- Hard IP: Dual CAN, Dual EMAC, Dual PCIe

- Safety ready Error correction code (ECC) support

#### CYCLONE V SOC PACKAGE / MAXIMUM USER I/O MATRIX

Automotive-grade products are highlighted in yellow.</mark> Others are available for auto qualification upon request.

Functional Safety Certified products are highlighted in green. Others are available for auto qualification upon request.

|                     |         |         |              |      |     |          |         |        | F      | ACKAG   | E TYPE/   | PIN COUI | Т       |           |        |           |      |      |

|---------------------|---------|---------|--------------|------|-----|----------|---------|--------|--------|---------|-----------|----------|---------|-----------|--------|-----------|------|------|

|                     |         |         |              |      | UB  | GA-484 ( | U19)    |        |        | UB      | GA-672 (I | J23)     |         |           | FBG    | GA-896 (F | 31)  |      |

|                     |         |         |              |      |     |          |         |        |        | BALI    | SPACIN    | G (MM)   |         |           |        |           |      |      |

|                     |         | LOGIC   | PLL          |      |     | 0.8      |         |        |        |         | 0.8       |          |         | 1.0       |        |           |      |      |

| FAMILY              | PRODUCT | DENSITY | FPGA/<br>HPS |      |     |          |         |        |        | DIM     | ENSION    | 5 (MM)   |         |           |        |           |      |      |

|                     |         | (KLES)  | (COUNT)      |      |     | 19 x 19  |         |        |        |         | 23 x 23   |          |         | 31×31     |        |           |      |      |

|                     |         |         | (00011)      |      |     |          | FPGA I/ | OS/PRC | CESSOF | RI/OS/L | VDS I/OS  | S/TRANS  | SCEIVER | S (XCVR ( | COUNT) |           |      |      |

|                     |         |         |              | FPGA | HPS | LVDS     | LVDS    | XCVR   | FPGA   | HPS     | LVDS      | LVDS     | XCVR    | FPGA      | HPS    | LVDS      | LVDS | XCVR |

|                     |         |         |              | I/O  | I/O | тх       | RX      |        | I/O    | I/O     | тх        | RX       |         | I/O       | I/O    | тх        | RX   |      |

|                     | 5CSE-A2 | 25      | 5/3          | 66   | 151 | 15       | 18      | -      | 145    | 181     | 31        | 35       | -       | -         | -      | -         | -    | -    |

| Cyclone V           | 5CSE-A4 | 40      | 5/3          | 66   | 151 | 15       | 18      | -      | 145    | 181     | 31        | 35       | -       | -         | -      | -         | -    | -    |

| SE SoC              | 5CSE-A5 | 85      | 6/3          | 66   | 151 | 15       | 18      | -      | 145    | 181     | 31        | 35       | -       | 288       | 181    | 72        | 72   | -    |

|                     | 5CSE-A6 | 110     | 6/3          | 66   | 151 | 15       | 18      | -      | 145    | 181     | 31        | 35       | -       | 288       | 181    | 72        | 72   | -    |

|                     | 5CSX-C2 | 25      | 5/3          | -    | -   | -        | -       | -      | 145    | 181     | 31        | 35       | 6       | -         | -      | -         | -    | -    |

| Cyclone V<br>SX SoC | 5CSX-C4 | 40      | 5/3          | -    | -   | -        | -       | -      | 145    | 181     | 31        | 35       | 6       | -         | -      | -         | -    | -    |

| (3 Gbps)            | 5CSX-C5 | 85      | 6/3          | -    | -   | -        | -       | -      | 145    | 181     | 31        | 35       | 6       | 288       | 181    | 72        | 72   | 9    |

|                     | 5CSX-C6 | 110     | 6/3          | -    | -   | -        | -       | -      | 145    | 181     | 31        | 35       | 6       | 288       | 181    | 72        | 72   | 9    |

| Cyclone V           | 5CST-D5 | 85      | 6/3          | -    | -   | -        | -       | -      | -      | -       | -         | -        | -       | 288       | 181    | 72        | 72   | 9    |

| ST SoC<br>(5 Gbps)  | 5CST-D6 | 110     | 6/3          | -    | -   | -        | -       | -      | -      | -       | -         | -        | -       | 288       | 181    | 72        | 72   | 9    |

AEC-Q100 Package options available with automotive-grade variants.

ISO-26262 Available in functional safety certified variants.

### Cyclone V FPGA

Cyclone V FPGAs provide the industry's lowest system cost and power, along with performance levels that make the device family ideally suited for differentiating your high-volume applications.

#### Cyclone V FPGA key features:

- Up to 40% power savings over prior generation

- Vertical migration across logic densities

- 3 Gbps and 5 Gbps transceiver options

- PCIe interface (hard IP)

- Memory controller (hard IP)

- Variable-precision DSP blocks

- 4 to 8 phase-locked loop (PLL)

#### CYCLONE V PACKAGE / MAXIMUM USER I/O MATRIX

Automotive-grade products are highlighted in yellow. Others are available for auto qualification upon request.

Functional Safety Certified products are highlighted in green. Others are available for auto qualification upon request.

|                             |         |                  |         |                       |                       |                       | PA                    | ACKAGE TYP            | PE/ PIN COUN          | т                     |                       |                       |                        |

|-----------------------------|---------|------------------|---------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|------------------------|

|                             |         |                  |         | MBGA<br>-301<br>(M11) | MBGA<br>-383<br>(M13) | MBGA<br>-484<br>(M15) | FBGA<br>-256<br>(F17) | UBGA<br>-324<br>(U15) | UBGA<br>-484<br>(U19) | FBGA<br>-484<br>(F23) | FBGA<br>-672<br>(F27) | FBGA<br>-896<br>(F31) | FBGA<br>-1152<br>(F35) |

| FAMILY                      | PRODUCT | LOGIC<br>DENSITY | PLL     |                       |                       |                       |                       | BALL SPA              | CING (MM)             | 1                     |                       |                       |                        |

| PAMILI                      | LINE    | (K LES)          | (COUNT) | 0.5                   | 0.5                   | 0.5                   | 1.0                   | 0.8                   | 0.8                   | 1.0                   | 1.0                   | 1.0                   | 1.0                    |

|                             |         |                  |         |                       |                       |                       |                       | DIMENSI               | ONS (MM)              | 1                     |                       |                       |                        |

|                             |         |                  |         | 11 x 11               | 13 x 13               | 15 x 15               | 17 x 17               | 15 x 15               | 19 x 19               | 23 x 23               | 27 x 27               | 31 x 31               | 35 x 35                |

|                             |         |                  |         |                       |                       |                       | I/OS/L                | VDS/TRAN              | SCEIVERS (CO          | OUNT)                 |                       |                       |                        |

|                             | 5CE-A2  | 25               | 4       | -                     | 223/50*               | -                     | 128/32                | 176/44                | 224/56                | 224/56                | -                     | -                     | -                      |

|                             | 5CE-A4  | 49               | 4       | -                     | 223/50*               | -                     | 128/32                | 176/44                | 224/56                | 224/56                | -                     | -                     | -                      |

| CYCLONE V<br>E              | 5CE-A5  | 77               | 6       | -                     | 175/38*               | -                     | -                     | -                     | 224/56                | 240/60                | -                     | -                     | -                      |

| E                           | 5CE-A7  | 149.5            | 6       | -                     | -                     | 240/<br>60            | -                     | -                     | 240/60                | 240/60                | 336/84                | 480/<br>120           | -                      |

|                             | 5CE-A9  | 301              | 6       | -                     | -                     | -                     | -                     | -                     | 240/122               | 224/56                | 336/84                | 480/<br>120           | -                      |

|                             | 5CGX-C3 | 35.5             | 4       | -                     | -                     | -                     | -                     | 144/36/<br>3          | 208/52/3              | 208/52/<br>3          | -                     | -                     | -                      |

|                             | 5CGX-C4 | 50               | 6       | 129/21*/ 4            | 175/38*/6             | -                     | -                     | -                     | 224/56/6              | 240/60/<br>6          | 336/84/<br>6          | -                     | -                      |

| CYCLONE V<br>GX<br>(3 GBPS) | 5CGX-C5 | 77               | 6       | 129/21*/ 4            | 175/38*/6             | -                     | -                     | -                     | 224/56/6              | 240/60/<br>6          | 336/84/<br>6          | -                     | -                      |

|                             | 5CGX-C7 | 149.5            | 7       | -                     | -                     | 240/<br>60/3          | -                     | -                     | 240/60/6              | 240/60/<br>6          | 336/84/<br>9          | 480/<br>120/9         | -                      |

|                             | 5CGX-C9 | 301              | 8       | -                     | -                     | -                     | -                     | -                     | 240/60/5              | 224/56/<br>6          | 336/84/<br>9          | 480/<br>120/12        | 560/<br>140/12         |

|                             | 5CGT-D5 | 77               | 6       | 129/21*/4             | 175/38*/6             | -                     | -                     | -                     | 224/56/6              | 240/60/<br>6          | 336/84/<br>6          | -                     | -                      |

| CYCLONE V<br>GT<br>(5 GBPS) | 5CGT-D7 | 149.5            | 7       | -                     | -                     | 240/<br>60/3          | -                     | -                     | 240/60/6              | 240/60/<br>6          | 336/84/<br>9          | 480/<br>120/9         | -                      |

|                             | 5CGT-D9 | 301              | 8       | -                     | -                     | -                     | -                     | -                     | 240/60/5              | 224/56/<br>6          | 336/84/<br>9          | 480/<br>120/12        | 560/<br>140/12         |

AEC-Q100 Package options available with automotive-grade variants.

ISO-26262 Available in functional safety certified variants.

True LVDS I/O count only. Does not inlcude eTX. \*Additional RX available.

#### CYCLONE IV E PACKAGE / MAXIMUM USER I/O MATRIX

Automotive-grade products are highlighted in yellow. Others are available for auto qualification upon request.

|                 |          |                  |         |                    | I                  | 1                  | PACKAGE TY         | PE/PIN COUNT       |                    | 1                  |                    |  |  |  |  |  |

|-----------------|----------|------------------|---------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|--|--|--|--|

|                 |          |                  |         | EQFP-144<br>(E144) | MBGA-164<br>(M164) | UBGA-256<br>(U256) | FBGA-256<br>(F256) | UBGA-484<br>(U484) | FBGA-324<br>(F324) | FBGA-484<br>(F484) | FBGA-780<br>(F780) |  |  |  |  |  |

| FAMILY          | PRODUCT  | LOGIC<br>DENSITY | PLL     |                    |                    |                    | BALL SP            | ACING (MM)         |                    |                    |                    |  |  |  |  |  |

| PAMILT          | LINE     | (K LES)          | (COUNT) | 0.5                | 0.5                | 0.8                | 1.0                | 0.8                | 1.0                | 1.0                | 1.0                |  |  |  |  |  |

|                 |          |                  |         | DIMENSIONS (MM)    |                    |                    |                    |                    |                    |                    |                    |  |  |  |  |  |

|                 |          |                  |         | 22 x 22            | 8 x 8              | 14 x 14            | 17 x 17            | 19 x 19            | 19 x 19            | 23 x 23            | 29 x 29            |  |  |  |  |  |

|                 |          |                  |         |                    |                    |                    | I/OS/LVDS          | I/OS(COUNT)        |                    |                    |                    |  |  |  |  |  |

|                 | EP4CE6   | 6.3              | 2       | 91/21              | -                  | 179/66             | 179/66             | -                  | -                  | -                  | -                  |  |  |  |  |  |

|                 | EP4CE10  | 10.3             | 2       | 91/21              | -                  | 179/66             | 179/66             | -                  | -                  | -                  | -                  |  |  |  |  |  |

|                 | EP4CE15  | 15.4             | 4       | 81/18              | 74/21              | 165/53             | 165/53             | 346/140            | -                  | 343/137            | -                  |  |  |  |  |  |

|                 | EP4CE22  | 22.3             | 4       | 79/17              | -                  | 153/52             | 153/52             | -                  | -                  | -                  | -                  |  |  |  |  |  |

| Cyclone IV<br>E | EP4CE30  | 28.8             | 4       | -                  | -                  | -                  | -                  | -                  | 193/61             | 328/124            | 532/224            |  |  |  |  |  |

|                 | EP4CE40  | 39.6             | 4       | -                  | -                  | -                  | -                  | 328/124            | 193/61             | 328/124            | 532/224            |  |  |  |  |  |

|                 | EP4CE55  | 55.9             | 4       | -                  | -                  | -                  | -                  | 324/132            | -                  | 324/132            | 374/160            |  |  |  |  |  |

|                 | EP4CE75  | 75.4             | 4       | -                  | -                  | -                  | -                  | 292/110            | -                  | 292/110            | 426/178            |  |  |  |  |  |

|                 | EP4CE115 | 114.5            | 4       | -                  | -                  | -                  | -                  | -                  | -                  | 280/103            | 528/230            |  |  |  |  |  |

AEC-Q100 Package options available with automotive-grade variants.

LVDS count includes dedicated and emulated LVDS pairs, see Cyclone IV Device Handbook.

#### CYCLONE IV GX PACKAGE / MAXIMUM USER I/O MATRIX

Automotive-grade products are highlighted in yellow. Others are available for auto qualification upon request.

|                |                 |         |                |     |         |      |     |         |      |                               | PACK    | AGETY   | PE/ PII | N COUN  | т    |     |         |      |     |         |      |  |

|----------------|-----------------|---------|----------------|-----|---------|------|-----|---------|------|-------------------------------|---------|---------|---------|---------|------|-----|---------|------|-----|---------|------|--|

|                |                 |         |                |     | QFN-14  | 8    |     | FBGA-1  | 69   | I                             | BGA-3   | 24      |         | FBGA-4  | 84   | 1   | BGA-6   | 72   |     | FBGA-8  | 96   |  |

|                |                 |         |                |     | (N148)  | )    |     | (F169)  | )    |                               | (F324)  | )       |         | (F484   | )    |     | (F672)  | )    |     | (F896)  | )    |  |

|                |                 | LOGIC   |                |     |         |      |     |         |      |                               | В       | ALL SPA | CING    | (MM)    |      |     |         |      |     |         |      |  |

| FAMILY         | PRODUCT<br>LINE | DENSITY | PLL<br>(COUNT) |     | 0.5     |      |     | 1.0     |      |                               | 1.0     |         |         | 1.0     |      |     | 1.0     |      |     | 1.0     |      |  |

|                |                 | (K LES) | (COUNT)        |     |         |      |     |         |      |                               | [       | DIMENS  | IONS (  | MM)     |      |     |         |      |     |         |      |  |

|                |                 |         |                |     | 11 x 11 |      |     | 14 x 14 |      |                               | 19 x 19 |         |         | 23 x 23 | 3    |     | 27 x 27 | ,    |     | 31 x 31 |      |  |

|                |                 |         |                |     |         |      |     |         |      | I/OS/LVDS/TRANSCEIVERS(COUNT) |         |         |         |         |      |     |         |      |     |         |      |  |

|                |                 |         |                | I/O | LVDS    | XCVR | I/O | LVDS    | XCVR | I/O                           | LVDS    | XCVR    | 1/0     | LVDS    | XCVR | 1/0 | LVDS    | XCVR | I/O | LVDS    | XCVR |  |

|                | EP4CGX15        | 14.4    | 3              | 72  | 25      | 2    | 72  | 25      | 2    | -                             | -       | -       | -       | -       | -    | -   | -       | -    | -   | -       | -    |  |

|                | EP4CGX22        | 21.3    | 4              | -   | -       | -    | 72  | 25      | 2    | 150                           | 64      | 4       | -       | -       | -    | -   | -       | -    | -   | -       | -    |  |

| CYCLONE        | EP4CGX30        | 29.4    | 4/6            | -   | -       | -    | 72  | 25      | 2    | 150                           | 64      | 4       | 290     | 130     | 4    | -   | -       | -    | -   | -       | -    |  |

| IV GX<br>(2.5/ | EP4CGX50        | 49.9    | 8              | -   | -       | -    | -   | -       | -    | -                             | -       | -       | 290     | 130     | 4    | 310 | 140     | 8    | -   | -       | -    |  |

| 3 GBPS)        | EP4CGX75        | 73.9    | 8              | -   | -       | -    | -   | -       | -    | -                             | -       | -       | 290     | 130     | 4    | 310 | 140     | 8    | -   | -       | -    |  |

|                | EP4CGX110       | 109.4   | 8              | -   | -       | -    | -   | -       | -    | -                             | -       | -       | 270     | 120     | 4    | 393 | 181     | 8    | 475 | 220     | 8    |  |

|                | EP4CGX150       | 149.8   | 8              | -   | -       | -    | -   | -       | -    | -                             | -       | -       | 270     | 120     | 4    | 393 | 181     | 8    | 475 | 220     | 8    |  |

AEC-Q100 Package options available with automotive-grade variants.

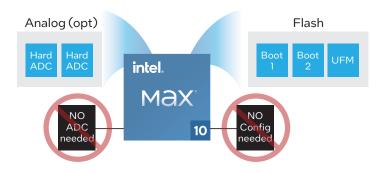

### Introducing the Intel MAX 10 FPGA (2.5V, 1.2V Core)

Intel MAX<sup>®</sup> 10 FPGAs revolutionize non-volatile integration by delivering advanced processing capabilities in a low-cost, instant-on, small form factor programmable logic device.

#### Intel MAX 10 FPGA key features:

- 2 to 50k LE logic density

- Dual-image configuration

- Instant-on configuration

- Dual or single core rail options

- Optional analog-to-digital converters (ADCs)

- Variable-precision DSP blocks

#### INTEL MAX 10 FPGA DUAL (CORE) SUPPLY DEVICE PACKAGE / MAXIMUM USER I/O MATRIX Automotive-grade products are highlighted in yellow. Others are available for auto qualification upon request.

|            |          |         | -          |                    |   |                       |          |                   | PACKAG        | SE TYPE/ PI | N COUNT         |                    |                |               |         |

|------------|----------|---------|------------|--------------------|---|-----------------------|----------|-------------------|---------------|-------------|-----------------|--------------------|----------------|---------------|---------|

|            |          |         |            | 36-WLCSF<br>(V36)* | > | 81-WLCS               | P (V81)* |                   | -FBGA<br>256) | 324-UBC     | GA (U324)       | 484-FBGA<br>(F484) |                | 672-F<br>(F6  |         |

|            |          | LOGIC   |            |                    |   |                       |          |                   | PAD/B         | ALL SPACI   | NG (MM)         |                    |                |               |         |

| FAMILY     | PRODUCT  | DENSITY | PLL        | 0.4                |   | 0.4                   | 4        |                   | 1.0           | C           | ).8             |                    | 1.0            | 1.0           | )       |

|            |          | (K LES) | (COUNT)    |                    |   |                       |          |                   | DIM           | IENSIONS (  | (MM)            | 1                  |                | I             |         |

|            |          |         |            | 3x3                |   | 4 x                   | 4        | 17                | 7 x 17        | 15          | x 15            | 23                 | 3 x 23         | 27 x          | 27      |

|            |          |         |            |                    |   |                       | м        | AXIMUMI           | OS - TRUE RX  | (/TRUETX    | /EMULATE        | отх (сои           | NT)            |               |         |

|            |          |         |            | IOs-RX/<br>TX/eTX  |   | IOs - RX /<br>TX/ eTX |          | IOs-RX/<br>TX/eTX |               |             | - RX /<br>/ eTX |                    | s-RX/<br>:/eTX | IOs -<br>TX / |         |

|            | 10M02D 2 | 1*/2    | 27 - 7/3/7 |                    |   |                       |          | 160 - 47/9/47     |               |             |                 |                    |                |               |         |

|            |          | 2       | 172        | С                  |   | _                     |          |                   | -             |             |                 |                    | -              | -             |         |

|            | 10M04D   | 4       | 2          | · ·                |   | _                     |          | 178 - 5           | 54/13/54      | 246-8       | 31/15/81        | _                  |                |               |         |

|            | 10M04D   |         |            | _                  |   |                       |          | С                 | А             | С           | А               | _                  |                | _             |         |

|            | 10M08D   | 8       | 1*/2       |                    |   | 56 - 17               | /7/17    | 178 - 5           | 54/13/54      | 246-8       | 31/15/81        | 250 -              | 83/15/83       |               |         |

| Intel MAX  | 1014080  | 0       | 172        |                    |   | С                     | F        | С                 | А             | C, C_6      | А               | C, C-6             | А              |               |         |

| 10<br>FPGA | 10M16D   | 16      | 4          | _                  |   | _                     |          | 178 - 5           | 54/13/54      | 246-8       | 31/15/81        | 320 - 116/22/116   |                | _             |         |

| "D"        |          | 10      | -          |                    |   |                       |          | С                 | А             | C, C_6      | А               | C, C_6 A           |                |               |         |

|            | 10M25D   | 25      | 4          | _                  |   | _                     |          | 178 - 5           | 54/13/54      |             | _               | 360 - 1            | 36/24/136      | _             |         |

|            |          |         |            |                    | _ |                       |          | С                 | А             |             |                 | C, C_6             | А              |               |         |

|            | 10M40D   | 40      | 4          | _                  |   | _                     |          | 178 - 5           | 54/13/54      |             | -               | 360 - 1            | 36/24/136      | 500 - 192     | /30/192 |

|            |          |         |            |                    | - |                       |          | С                 | А             |             |                 | C, C_6             | A              | С             | A       |

|            | 10M50D   | 50      | 4          |                    | _ |                       | 54/13/54 | _                 |               | -           |                 | 500 - 192/30/192   |                |               |         |

|            |          |         |            |                    |   |                       |          | С                 | А             |             |                 |                    |                | С             | А       |

Note: Feature set options: C = Base, F = Dual Configuration CFM, A = Dual Configuration CFM + Analog Features

Note: RX = True LVDS RX, TX = True LVDS TX, eTX = emulated LVDS TX, additional LOW SPEED eTX/RX IO provided.

Note: "\_6" denotes special FAST speed grade supported, A6G suffix. Contact factory on availability.

AEC-Q100 Package options available in Intel Quartus development software with automotove-grade variants.

AEC-Q100 Planned package option - available upon request / approval. A-Grade production 2H2015-IH2016 - device dependent. See Website for updated information.

INTEL MAX 10 FPGA SINGLE (CORE) SUPPLY DEVICE PACKAGE / MAXIMUM USER I/O MATRIX (3.0V OR 3.3V CORE) Automotive-grade products are highlighted in yellow. Others are available for auto qualification upon request.

|                |          |          |         |                |                                                       | PACKAGE T | YPE/ PIN COUNT |            |          |  |  |  |  |

|----------------|----------|----------|---------|----------------|-------------------------------------------------------|-----------|----------------|------------|----------|--|--|--|--|

|                |          |          |         | 144-EQF        | FP (E144)                                             | 153-ME    | 3GA (M153)     | 169-UBG    | A (U169) |  |  |  |  |

|                |          | LOGIC    |         |                |                                                       | PAD / BAL | L SPACING (MM) | 1          |          |  |  |  |  |

| FAMILY         | PRODUCT  | DENSITY  | PLL     | 0              | .5                                                    |           | 0.5            | 0.8        |          |  |  |  |  |

| TAMILI         | LINE     | (K LES)  | (COUNT) |                |                                                       | DIMEN     | SIONS (MM)     |            |          |  |  |  |  |

|                |          | (11 220) |         | 22 :           | x 22                                                  | ٤         | 3 x 8          | 11 x       | : 11     |  |  |  |  |

|                |          |          |         |                | MAXIMUM IOS - TRUE RX / TRUE TX / EMULATED TX (COUNT) |           |                |            |          |  |  |  |  |

|                |          |          |         | IOs - RX /     | ′ TX / eTX                                            | IOs - Rλ  | ( / TX / eTX   | IOs - RX / | TX / eTX |  |  |  |  |

|                | 10M02S   | 2        | 1       | 101 - 2        | 7/7/27                                                | 112 -     | 29/9/29        | 130 - 3    | 8/9/38   |  |  |  |  |

|                | 1014023  | 2        |         | С              |                                                       | С         |                | С          |          |  |  |  |  |

|                | 10M04S   | 4        | 1       | 101 - 27/10/27 |                                                       | 112 -     | 29/9/29        | 130 - 3    | 8/9/38   |  |  |  |  |

|                | 101/1045 |          | 1       | С              | А                                                     | С         | А              | С          | А        |  |  |  |  |

|                | 10M08S   | 8        | 1       | 101 - 2        | 7/10/27                                               | 112 -     | 29/9/29        | 130 - 3    | 8/9/38   |  |  |  |  |

|                | 1014085  | 0        | 1       | С              | А                                                     | С         | А              | С          | А        |  |  |  |  |

| MAX 10<br>FPGA | 10M16S   | 16       | 1       | 101 - 2        | 7/10/27                                               |           | _              | 130 - 3    | 8/9/38   |  |  |  |  |

| "S"            |          | 10       |         | С              | А                                                     |           |                | С          | А        |  |  |  |  |

|                | 10M25S   | 25       | 1       | 101 - 2        | 7/10/27                                               |           | _              |            | _        |  |  |  |  |

|                |          |          | •       | С              | A                                                     |           |                |            |          |  |  |  |  |

|                | 10M40S   | 40       | 1       | 101 - 2        | 8/10/28                                               |           | _              | -          | _        |  |  |  |  |

|                |          |          |         | С              | A                                                     |           |                |            |          |  |  |  |  |

|                | 10M50S   | 50       | 1       | 101 - 2        | 8/10/28                                               |           | _              | _          |          |  |  |  |  |

|                | 10M50S   | 50       | 1 -     | 1 -            | C A                                                   |           |                |            | -        |  |  |  |  |

Note: Feature set options: C = Base, F = Dual Configuration CFM, A = Dual Configuration CFM + Analog Features

Note: RX = True LVDS RX, TX = True LVDS TX, eTX = emulated LVDS TX, additional LOW SPEED eTX/RX IO provided.

**AEC-Q100** Package options available in Intel Quartus development softare with automotove-grade variants.

AEC-Q100 Planned package option - available upon request / approval. A-Grade production 2H2015-1H2016 - device dependent. See website for updated information.

#### MAX V (CPLD) DEVICE PACKAGE / MAXIMUM USER I/O MATRIX

Automotive-grade products are highlighted in yellow. Others are available for auto qualification upon request.

|        |         | LOGIC<br>DENSITY<br>(LES) |                   |                  |                  | PACKAGE TY         | PE/ PIN COUN       | т                  |                    |                    |  |  |  |  |  |  |

|--------|---------|---------------------------|-------------------|------------------|------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--|--|--|--|--|--|

|        |         |                           | MBGA-64<br>(M64)  | EQFP-64<br>(E64) | MBGA-68<br>(M68) | TQFP-100<br>(T100) | MBGA-100<br>(M100) | TQFP-144<br>(T144) | FBGA-256<br>(F256) | FBGA-324<br>(F324) |  |  |  |  |  |  |

|        | PRODUCT |                           | BALL SPACING (MM) |                  |                  |                    |                    |                    |                    |                    |  |  |  |  |  |  |

| FAMILY | LINE    |                           | 0.5               | 0.4              | 0.5              | 0.5                | 0.5                | 0.5                | 1.0                | 1.0                |  |  |  |  |  |  |

|        |         |                           |                   | DIMENSIONS (MM)  |                  |                    |                    |                    |                    |                    |  |  |  |  |  |  |

|        |         |                           | 4.5 x 4.5         | 9 x 9            | 5 x 5            | 16 x 16            | 6 x 6              | 22 x 22            | 17 x 17            | 19 x 19            |  |  |  |  |  |  |

|        |         |                           | I/OS (COUNT)      |                  |                  |                    |                    |                    |                    |                    |  |  |  |  |  |  |

|        | 5M40Z   | 40                        | 30                | 54               | -                | -                  | -                  | -                  | -                  | -                  |  |  |  |  |  |  |

|        | 5M80Z   | 80                        | 30                | 54               | 52               | 79                 | -                  | -                  | -                  | -                  |  |  |  |  |  |  |

|        | 5M160Z  | 160                       | -                 | 54               | 52               | 79                 | 79                 | -                  | -                  | -                  |  |  |  |  |  |  |

| MAX V  | 5M240Z  | 240                       | -                 | -                | 52               | 79                 | 79                 | 114                | -                  | -                  |  |  |  |  |  |  |

|        | 5M570Z  | 570                       | -                 | -                | -                | 74                 | 74                 | 114                | 159                | -                  |  |  |  |  |  |  |

|        | 5M1270Z | 1270                      | -                 | -                | -                | -                  | -                  | 114                | 211                | 271                |  |  |  |  |  |  |

|        | 5M2210Z | 2210                      | -                 | -                | -                | -                  | -                  | -                  | 203                | 271                |  |  |  |  |  |  |

AEC-Q100 Package options available with automotive-grade variants.

#### Notes:

1. For a specific list of part numbers for automotive-grade devices, consult the Automotive-Grade Device Handbook.

2. For details on additional product line features (i.e., hard IP blocks, on-chip memory, and so on), consult the online device handbook.

3. Other automotive-grade options might be available upon request. Consult your Intel sales representative to submit your request.

4. For full specifications, features, and I/O count for GPIO, HPS, LVDS, emulated LVDS, and transceivers, refer to the Intel Quartus Prime Pro and Standard Software User Guides.

Visit our website for information on legacy automotivegrade devices:

- Cyclone III FPGAs

- Cyclone II FPGAs

- Cyclone FPGAs

- MAX II CPLDs

- MAX 7000A CPLDs

# Want to Dig Deeper?

To learn more about Intel's automotive-grade products, contact your local FAE or sales representative. You can download automotive handbooks, white papers, and application notes at <u>FPGA Automotive Documentation web page</u>.

#### intel

Performance varies by use, configuration and other factors. Learn more at www.Intel.com/PerformanceIndex.

Performance results are based on testing as of dates shown in configurations and may not reflect all publicly available updates. See backup for configuration details. No product or component can be absolutely secure.

Your costs and results may vary.

Intel does not control or audit third party data. You should consult other sources for accuracy.

Intel technologies may require enabled hardware, software or service activation.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.