MAX+PLUS® II AHDI

# MAX+PLUS® II

**Programmable Logic Development System**

**AHDL**

Altera Corporation 101 Innovation Drive San Jose, CA 95134 (408) 544-7000 Altera, MAX, MAX+PLUS, FLEX, and FLEX Ability are registered trademarks of Altera Corporation. The following are trademarks of Altera Corporation: Classic, MAX 5000, MAX 5000A, FLEXlogic, FLASHlogic, MAX 7000, MAX 7000E, MAX 7000S, FLEX 8000, FLEX 8000A, FLEX 8000M, MAX 9000, FLEX 10K, MAX+PLUS II, PLDshell Plus, FastTrack, AHDL, MPLD, Turbo Bit, BitBlaster, PLS-ES, PLSM-VHDL, PLSM-VHDLWS, EP220, EP330, EP610, EP610I, EP910, EP910I, EP1810, EP1810T, EP610T, EP910T, EPM5016, EPM5032, EPM5032A, EPM5064, EPM5064A, EPM5128, EPM5128A, EPM5130A, EPM5130A, EPM5192, EPM5192A, EPX740, EPX780, EPX880, EPX8160, EPM7032, EPM7032V, EPM7064, EPM7096, EPM7182E, EPM7160E, EPM7192E, EPM7256E, EPM7032S, EPM7064S, EPM7096S, EPM7128S, EPM7160S, EPM7192S, EPM7256S, EPC1, EPC1064, EPC1064V, EPC1213, EPF8282, EPF8282V, EPF8282A, EPF8282AV, EPF8452A, EPF8636A, EPF8820A, EPF8820 EPF81188, EPF81188A, EPF81500, EPF81500A, EPF8050M, EPM9320, EPM9400, EPM9480, EPM9560, EPF10K10, EPF10K20, EPF10K30, EPF10K40, EPF10K50, EPF10K70, EPF10K100. Product design elements and mnemonics are Altera Corporation copyright. Altera Corporation acknowledges the trademarks of other organizations for their respective products or services mentioned in this document, specifically: UNIX is a trademark of AT&T Bell Laboratories. Verilog is a registered trademark of Cadence Design Systems, Incorporated. Data I/O is a registered trademark of Data I/O Corporation. FLEXIm is a registered trademark of Globetrotter Software, Inc. HP is a registered trademark of Hewlett-Packard Company. IBM is a registered trademark and IBM PC and IBM RISC System/6000 are trademarks of International Business Machines Corporation. Intel is a registered trademark, and Pentium is a trademark of Intel Corporation. Mentor Graphics is a registered trademark of Mentor Graphics Corporation Microsoft, MS-DOS, and Windows are registered trademarks and Win32s and Windows NT are trademarks of Microsoft Corporation. OrCAD is a trademark of OrCAD Systems Corporation. SPARCstation is a trademark of SPARC International, Inc. and is licensed exclusively to Sun Microsystems, Inc. Sun Workstation and Solaris are registered trademarks, and Sun, SunOS, and OpenWindows are trademarks of Sun Microsystems, Incorporated. Synopsys is a registered trademark of Synopsys, Inc. Viewlogic is a registered trademark of Viewlogic Systems, Incorporated. Altera acknowledges the trademarks of other organizations for their respective products or services mentioned in this document.

Altera reserves the right to make changes, without notice, in the devices or the device specifications identified in this document. Altera advises its customers to obtain the latest version of device specifications to verify, before placing orders, that the information being relied upon by the customer is current. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty. Testing and other quality control techniques are used to the extent Altera deems such testing necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed. In the absence of written agreement to the contrary, Altera assumes no liability for Altera applications assistance, customer's product design, or infringement of patents or copyrights of third parties by or arising from use of semiconductor devices described herein. Nor does Altera warrant or represent any patent right, copyright, or other intellectual property right of Altera covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

Altera's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Altera Corporation. As used herein:

- 1. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Products mentioned in this document are covered by one or more of the following U.S. patents: 4,020,469; 4,609,986; 4,617,479; 4,677,318; 4,713,792; 4,774,421; 4,785,423; 4,831,573; 4,864,161; 4,871,930; 4,899,067; 4,899,070; 4,903,223; 4,912,342; 4,930,097; 4,930,098; 4,930,107; 4,969,121; 5,045,772; 5,066,873; 5,091,661; 5,097,208; 5,111,423; 5,121,006; 5,128,565; 5,138,576; 5,144,167; 5,162,680; 5,166,604; 5,187,392; 5,200,920; 5,220,214; 5,220,533; 5,237,219; 5,241,224; 5,243,233; 5,247,477; 5,247,478; 5,258,668; 5,260,610; 5,260,611; 5,268,598; 5,272,368; 5,274,581; 5,280,203; 5,285,153; 5,294,975; 5,301,416; 5,309,046; 5,315,172; 5,317,210; 5,317,212; 5,329,487; 5,341,044; 5,341,048; 5,341,308; 5,349,255; 5,350,954; 5,352,940; 5,353,248; 5,359,242; 5,359,243; 5,369,314; 5,371,422; 5,375,086; 5,376,844; 5,384,499; 5,399,922; 5,414,312; 5,432,467; 5,434,514; 5,436,574; 5,436,575; 5,438,295; 5,444,394 and certain foreign patents.

U.S. and European patents pending Copyright © 1995 Altera Corporation. All rights reserved.

# **Contents**

| Preface                                                                                                                                                                     |                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| MAX+PLUS II Documentation                                                                                                                                                   |                            |

| MAX+PLUS II Documents                                                                                                                                                       |                            |

| MAX+PLUS II Help                                                                                                                                                            |                            |

| How to Use MAX+PLUS II Documentation                                                                                                                                        |                            |

| Documentation Conventions                                                                                                                                                   |                            |

| Terminology                                                                                                                                                                 | xiv                        |

| Typographic Conventions                                                                                                                                                     | xv                         |

| Key Combinations                                                                                                                                                            |                            |

| Backus-Naur Form                                                                                                                                                            |                            |

| MAX+PLUS II Help Updates                                                                                                                                                    | xiii                       |

| Sample Files                                                                                                                                                                | xix                        |

| About MAX+PLUS II AHDL                                                                                                                                                      | xx                         |

|                                                                                                                                                                             |                            |

| Section 1 Introduction                                                                                                                                                      |                            |

|                                                                                                                                                                             |                            |

| AHDL Design Entry                                                                                                                                                           | 2                          |

| AHDL Design Entry                                                                                                                                                           | 2                          |

| How Does AHDL Work?                                                                                                                                                         | 2                          |

| How Does AHDL Work?  Text Design File Structure                                                                                                                             | 2                          |

| How Does AHDL Work?  Text Design File Structure  Text Design File Sections                                                                                                  | 2<br>4                     |

| How Does AHDL Work?  Text Design File Structure                                                                                                                             |                            |

| How Does AHDL Work?  Text Design File Structure  Text Design File Sections  Files in a Project Hierarchy  Include Files                                                     | 2<br>4<br>7                |

| How Does AHDL Work?  Text Design File Structure  Text Design File Sections  Files in a Project Hierarchy  Include Files  MAX+PLUS II Text Editor                            | 2<br>4<br>7<br>7           |

| How Does AHDL Work?  Text Design File Structure  Text Design File Sections  Files in a Project Hierarchy  Include Files                                                     | 2<br>4<br>7<br>7<br>9      |

| How Does AHDL Work?  Text Design File Structure  Text Design File Sections  Files in a Project Hierarchy  Include Files  MAX+PLUS II Text Editor  AHDL Templates & Examples | 2<br>4<br>7<br>7<br>9<br>9 |

| Error Location                                  | 12 |

|-------------------------------------------------|----|

| Compiling AHDL Text Design Files                | 13 |

| Golden Rules                                    | 14 |

| General Design Entry Golden Rules               | 15 |

| General MAX+PLUS II Golden Rules                | 16 |

|                                                 |    |

| Section 2 How to Use AHDL                       |    |

| Introduction                                    | 10 |

| Using Numbers                                   |    |

| Using Constants & Evaluated Functions           |    |

| Inserting an AHDL Template                      |    |

| AHDL Examples                                   |    |

| Combinatorial Logic                             |    |

| Implementing Boolean Expressions & Equations    | 25 |

|                                                 |    |

| Declaring Nodes Defining Groups                 |    |

|                                                 |    |

| Implementing Conditional Logic                  |    |

| If Then Statement Logic                         |    |

| Case Statement Logic                            | 32 |

| If Then Statement vs. Case Statement            |    |

| Creating Decoders                               |    |

| Using Default Values for Variables              |    |

| Implementing Active-Low Logic                   |    |

| Implementing Bidirectional Pins                 |    |

| Implementing Tri-State Buses                    |    |

| Sequential Logic                                | 47 |

| Declaring Registers                             | 47 |

| Declaring Registered Outputs                    | 50 |

| Creating Counters                               |    |

| State Machines                                  |    |

| Implementing State Machines                     |    |

| Setting Clock, Reset & Enable Signals           |    |

| Assigning State Machine Bits & Values           |    |

| State Machines with Synchronous Outputs         |    |

| State Machines with Asynchronous Outputs        |    |

| Recovering From Illegal States                  |    |

| Implementing a Hierarchical Project             |    |

| Using Altera-Provided Unparameterized Functions |    |

| Using Altera-Provided Parameterized Functions   |    |

| Using Custom Megafunctions & Macrofunctions     |    |

| Importing & Exporting State Machines            |    |

| Implementing LCELL & SOFT Primitives            |    |

| Implementing RAM & ROM                          |    |

| Naming a Boolean Operator or Comparator         | 84 |

| Using Iteratively Generated Logic                         | 86  |

|-----------------------------------------------------------|-----|

| Using Conditionally Generated Logic                       | 87  |

| Using the Assert Statement                                | 89  |

|                                                           |     |

| Section 3 Elements                                        |     |

| Reserved Keywords & Identifiers                           | 92  |

| Reserved Keywords                                         | 92  |

| Reserved Identifiers                                      |     |

| Symbols                                                   | 94  |

| Quoted & Unquoted Names                                   | 97  |

| Groups                                                    | 99  |

| Group Notations                                           |     |

| Group Ranges & Subranges                                  | 100 |

| Numbers in AHDL                                           |     |

| Arithmetic Expressions                                    |     |

| Boolean Expressions                                       |     |

| Logical Operators                                         |     |

| Boolean Expressions Using NOT                             |     |

| Boolean Expressions Using AND, NAND, OR, NOR, XOR, & XNOR |     |

| Arithmetic Operators in Boolean Expressions               |     |

| Comparators                                               | 111 |

| Boolean Operator & Comparator Priorities                  | 112 |

| Primitives                                                |     |

| Buffer Primitives                                         |     |

| CARRY Primitive                                           | 114 |

| CASCADE Primitive                                         | 116 |

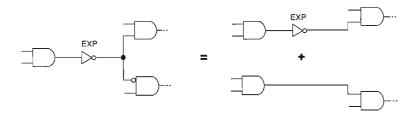

| EXP Primitive                                             |     |

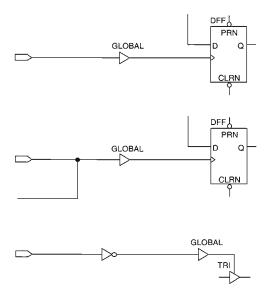

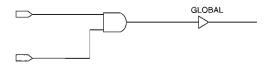

| GLOBAL Primitive                                          | 118 |

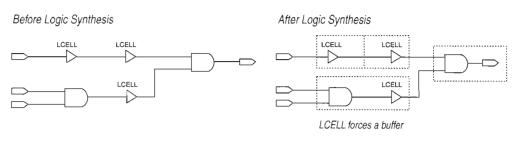

| LCELL Primitive                                           |     |

| OPNDRN Primitive                                          | 122 |

| SOFT Primitive                                            | 123 |

| TRI Primitive                                             | 125 |

| Flipflop & Latch Primitives                               | 125 |

| Primitive/Port Interconnections                           |     |

|                                                           |     |

| MegafunctionsOld-Style Macrofunctions                     | 131 |

| Ports                                                     | 132 |

| Ports of the Current File                                 |     |

| Ports of Instances                                        | 133 |

| Parameters                                                | 136 |

#### Section 4 Design Structure

| Overview                         | 140  |

|----------------------------------|------|

| Title Statement                  | 141  |

| Parameters Statement             | 142  |

| Include Statement                |      |

| Constant Statement               |      |

| Define Statement                 |      |

| Function Prototype Statement     | 151  |

| Options Statement                | 154  |

| Assert Statement                 |      |

| Subdesign Section                |      |

| Variable Section                 |      |

| Instance Declaration             |      |

| Node Declaration                 |      |

| Register Declaration             |      |

| State Machine Declaration        | 165  |

| Machine Alias Declaration        | 166  |

| Logic Section                    | 168  |

| Boolean Equations                |      |

| Boolean Control Equations        | 171  |

| Case Statement                   |      |

| Defaults Statement               | 173  |

| If Then Statement                |      |

| If Generate Statement            |      |

| For Generate Statement           |      |

| In-Line Logic Function Reference |      |

| Truth Table Statement            |      |

| Trutt Table Statement            | 103  |

|                                  |      |

| Section 5 Style Guide            |      |

| 0 10 1 0 111                     | 4.00 |

| General Style Guidelines         |      |

| White Space                      | 190  |

| Comments & Documentation         |      |

| Naming Conventions               |      |

| Indentation Guidelines           | 193  |

|                                  |      |

| Glossary                         | 197  |

| •                                |      |

| I- J                             | 000  |

# **Illustrations**

| Figure |                                 | Page |

|--------|---------------------------------|------|

| 1-1    | MAX+PLUS II & AHDL Design Entry | 3    |

| 1-2    | AHDL Text Design File Structure |      |

| 2-1    | decode1.tdf                     |      |

| 2-2    | decode1.gdf                     |      |

| 2-3    | decode2.tdf                     |      |

| 2-4    | strcmp.tdf                      | 21   |

| 2-5    | minport.tdf                     |      |

| 2-6    | AHDL Template Dialog Box        | 23   |

| 2-7    | Defaults Statement Template     | 23   |

| 2-8    | boole1.tdf                      | 26   |

| 2-9    | boole1.gdf                      | 26   |

| 2-10   | boole2.tdf                      | 27   |

| 2-11   | boole2.gdf                      | 28   |

| 2-12   | group1.tdf                      | 29   |

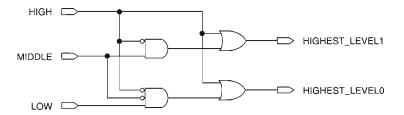

| 2-13   | priority.tdf                    | 31   |

| 2-14   | priority.gdf                    | 32   |

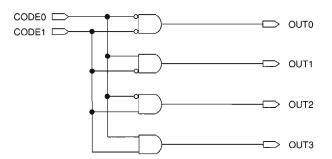

| 2-15   | decoder.tdf                     | 33   |

| 2-16   | decoder.gdf                     | 33   |

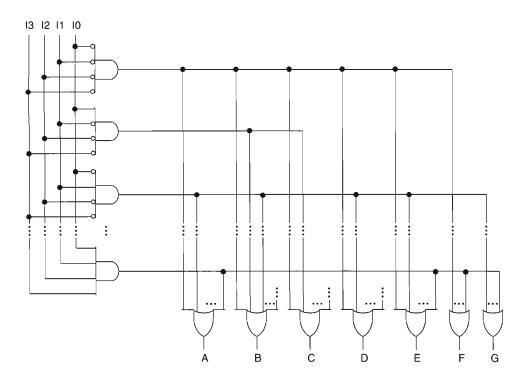

| 2-17   | 7segment.tdf                    |      |

| 2-18   | 7segment.gdf                    |      |

| 2-19   | decode3.tdf                     | 37   |

| 2-20   | decode4.tdf                     | 38   |

| 2-21   | default1.tdf                    | 39   |

| 2-22   | default2.tdf                    |      |

| 2-23   | default2.gdf                    | 41   |

|        |                                 |      |

| Figure |                                  | Page |

|--------|----------------------------------|------|

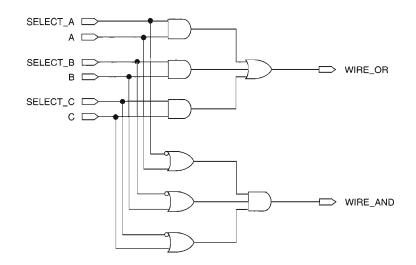

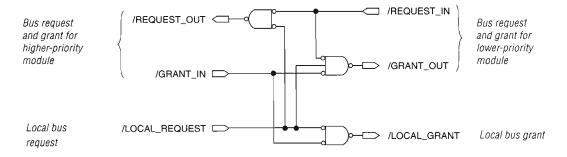

| 2-24   | daisy.tdf                        | 42   |

| 2-25   | daisy.gdf                        | 43   |

| 2-26   | bus_reg2.tdf                     |      |

| 2-27   | bus_reg2.gdf                     |      |

| 2-28   | bidir1.tdf                       |      |

| 2-29   | tri_bus.tdf                      | 45   |

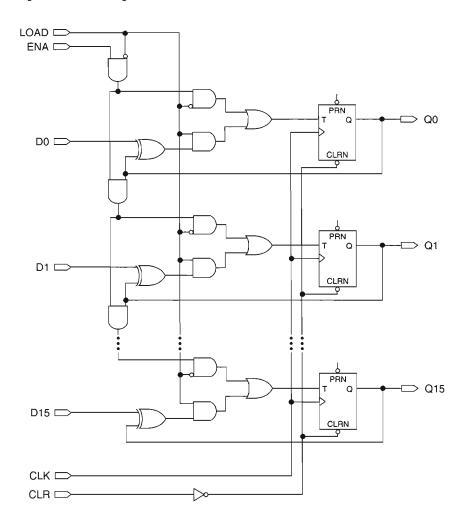

| 2-30   | bur_reg.tdf                      | 48   |

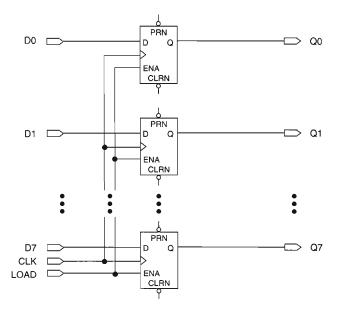

| 2-31   | lpm_reg.tdf                      | 49   |

| 2-32   | reg.gdf                          | 49   |

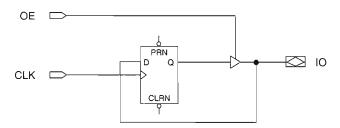

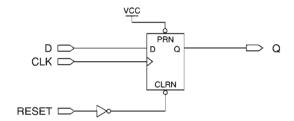

| 2-33   | reg_out.tdf                      | 50   |

| 2-34   | ahdlent.tdf                      | 51   |

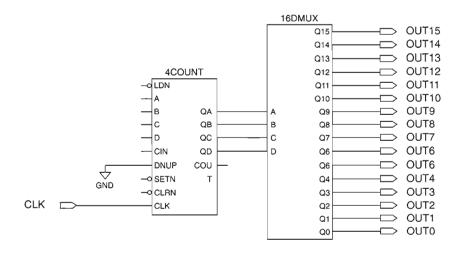

| 2-35   | lpm_cnt.tdf                      | 52   |

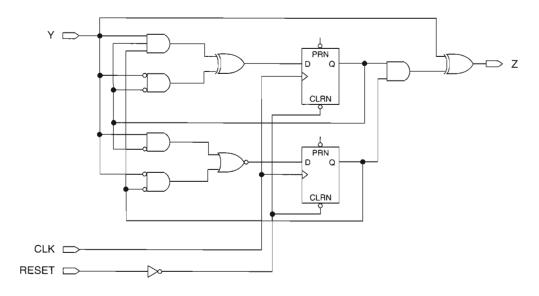

| 2-36   | count.gdf                        | 53   |

| 2-37   | simple.tdf                       | 55   |

| 2-38   | simple.gdf                       | 56   |

| 2-39   | simple1.tdf                      | 57   |

| 2-40   | stepper.tdf                      | 59   |

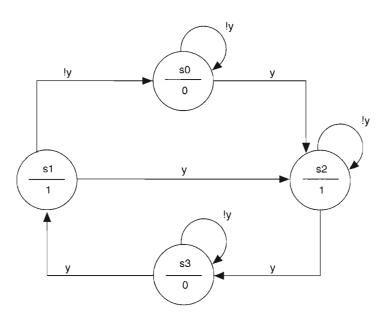

| 2-41   | Moore State Machine Diagram      | 60   |

| 2-42   | moore1.tdf                       |      |

| 2-43   | moore1.gdf                       | 62   |

| 2-44   | moore2.tdf                       | 63   |

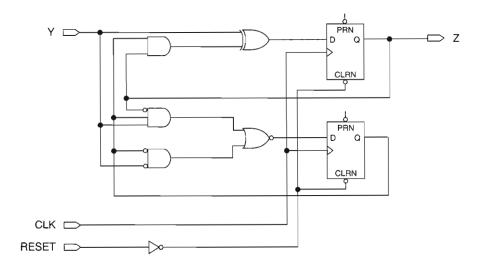

| 2-45   | Mealy State Machine Diagram      | 64   |

| 2-46   | mealy.tdf                        | 65   |

| 2-47   | mealy.gdf                        | 66   |

| 2-48   | recover.tdf                      | 68   |

| 2-49   | macro1.tdf                       | 70   |

| 2-50   | macro2.tdf                       | 71   |

| 2-51   | macro.gdf                        | 72   |

| 2-52   | lpm_add1.tdf                     | 74   |

| 2-53   | lpm_add2.tdf                     | 75   |

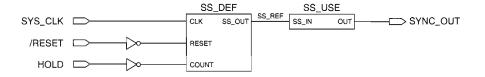

| 2-54   | ss_def.tdf                       | 78   |

| 2-55   | ss_use.tdf                       | 78   |

| 2-56   | top1.tdf                         |      |

| 2-57   | top1.gdf                         | 79   |

| 2-58   | top2.tdf                         |      |

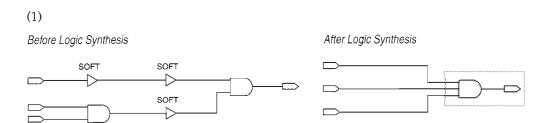

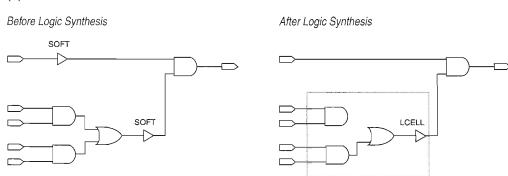

| 2-59   | NODE Variables & SOFT Primitives | 82   |

| 2-60   | boole3.tdf                       | 84   |

| 2-61   | boole3.rpt & boole1.rpt Excerpts | 85   |

| 2-62   | iter_add.tdf                     | 86   |

| 2-63   | condlog1.tdf                     | 87   |

| 2-64   | condlog2.tdf                     |      |

# **Tables**

| Table |                                                         | Page |

|-------|---------------------------------------------------------|------|

| 3-1   | AHDL Symbols                                            | 94   |

| 3-2   | Quoted & Unquoted Names                                 |      |

| 3-3   | Arithmetic Operators and Comparators Used in Arithmetic |      |

|       | Expressions                                             | 103  |

| 3-4   | Logical Operators Used in Boolean Expressions           | 107  |

| 3-5   | Arithmetic Operators Used in Boolean Expressions        | 109  |

| 3-6   | Comparators Used in Boolean Expressions                 | 111  |

| 3-7   | Boolean Operator & Comparator Priorities                | 112  |

| 3-8   | Global Signal Availability                              | 118  |

| 3-9   | MAX+PLUS II Flipflops & Latches                         | 126  |

| 3-10  | Primitive/Port Interconnections                         | 127  |

| 3-11  | Primitive/Port to Register Connections                  | 128  |

| 3-12  | MAX+PLUS II Megafunctions                               | 129  |

| 3-13  | Commonly Used Ports                                     |      |

#### **Preface**

# MAX+PLUS II Fundamentals

This section describes the MAX+PLUS II manual and on-line help documentation and conventions. You should be familiar with this information before using MAX+PLUS II documentation.

| MAX+PLUS II Documentation | xii   |

|---------------------------|-------|

|                           |       |

| MAX+PLUS II Help Updates  | xviii |

|                           |       |

| About MAX+PLUS II AHDL    |       |

## **MAX+PLUS II Documentation**

MAX+PLUS II documentation is designed for the novice as well as for the experienced user. It includes manuals and extensive, illustrated Help.

#### **MAX+PLUS II Documents**

MAX+PLUS II printed documents contain the following information:

| MAX+PLUS II<br>Getting Started | Contains step-by-step instructions on how to install MAX+PLUS II hardware, software, and licenses on PCs and workstations. It also provides an overview of the entire MAX+PLUS II system, and a tutorial that takes you from design entry to device programming. In addition, it contains information about MAX+PLUS II command-line operation and Altera's support services. |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX+PLUS II<br>AHDL            | Contains complete information on the Altera Hardware Description Language (AHDL), including a detailed <i>How to Use AHDL</i> section with many examples.                                                                                                                                                                                                                     |

| MAX+PLUS II<br>VHDL            | Provides information on how to use the Very High Speed Integrated Circuit (VHSIC) Hardware Description Language (VHDL) with MAX+PLUS II, including a <i>How to Use MAX+PLUS II VHDL</i> section with many examples. (Available if you purchase PLSM-VHDL or PLSM-VHDLWS.)                                                                                                     |

| MAX+PLUS II<br>Help Poster     | Provides handy and colorful descriptions of how to use on-line help in MAX+PLUS II.                                                                                                                                                                                                                                                                                           |

MAX+PLUS II for workstations also includes the following Software Interface Guides:

- Cadence & MAX+PLUS II Software Interface Guide

- Mentor Graphics & MAX+PLUS II Software Interface Guide

- Synopsys & MAX+PLUS II Software Interface Guide

- Viewlogic Powerview & MAX+PLUS II Software Interface Guide

#### MAX+PLUS II Help

Your primary source of information on MAX+PLUS II is the complete online help. All of the information necessary to enter, compile, and verify a design and to program an Altera device is available in MAX+PLUS II Help.

Help also provides introductions to all MAX+PLUS II applications, guidelines for designing circuits with MAX+PLUS II, pin and logic cell numbers for each Altera device package, and summaries of other Altera documents, such as application notes, that can assist you with logic design.

# Preface

MAX+PLUS II Fundamentals

#### How to Use MAX+PLUS II Documentation

How you use MAX+PLUS II documentation depends on your level of expertise and your approach to learning how to use a new tool.

If you are a novice user, you should take time to read the *MAX+PLUS II Getting Started* manual and complete the *MAX+PLUS II Tutorial*. Once you begin using MAX+PLUS II applications, you will find that the easy-to-use, extensive on-line help can quickly turn you into an expert MAX+PLUS II user. For basic information on using on-line help, refer to the *MAX+PLUS II Help Poster*. More detailed information on using Help is available in *MAX+PLUS II — A Perspective* in *MAX+PLUS II Getting Started*.

If you are an experienced circuit designer or one who prefers to learn by experimenting, you will find the on-line help invaluable. Context-sensitive and menu-driven help give instant access to all MAX+PLUS II information.

Regardless of your level of expertise, you must follow the installation instructions provided in *MAX+PLUS II Getting Started*. Before you install the MAX+PLUS II hardware and software, you should also read the read.me file provided on the first Install diskette or on the CD-ROM. If you are using the CD-ROM on a PC, the read.me file is located in the \pc\maxplus2 directory; on a workstation, it is located in the /cdrom directory. Once you have installed MAX+PLUS II, you can open the read.me file through the Help menu in MAX+PLUS II.

Altera Applications Engineers are also available to answer your questions. For more information about Altera's technical support services, see *Appendix B: Altera Support Services* in *MAX+PLUS II Getting Started*.

# **Documentation Conventions**

MAX+PLUS II manuals and MAX+PLUS II Help use the following conventions to make it easy for you to find and interpret information.

#### **Terminology**

The following terminology is used throughout MAX+PLUS II Help and manuals:

| Term:                | Meaning:                                                                                                                                                                                                                                                                                                           |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Button 1             | Left mouse button.                                                                                                                                                                                                                                                                                                 |

| Button 2             | Right button on a two-button mouse, or middle and right buttons on a three-button mouse.                                                                                                                                                                                                                           |

| "point to"           | Indicates that you should move the mouse so that the pointer is over the specified item.                                                                                                                                                                                                                           |

| "press"              | Indicates that you must hold down a mouse button or key.                                                                                                                                                                                                                                                           |

| "click"              | Indicates a quick press and release of a mouse button.                                                                                                                                                                                                                                                             |

| "double-click"       | Indicates two clicks in rapid succession.                                                                                                                                                                                                                                                                          |

| "choose"             | Indicates that you need to use a mouse or key combination to start an action. For example, when you use the mouse to choose a button, you point to the button and click Button 1. When you use the keyboard to choose a command, you press Alt and then type letters that are underlined in the menu bar and menu. |

| "select"             | Indicates that you need to highlight text and/or objects or an option in a dialog box with a key combination or the mouse. A selection does not start an action. For example: Select the AND2 primitive, then choose <b>Delete</b> from the Edit menu.                                                             |

| "turn on"/"turn off" | Indicates that you must click Button 1 on a checkbox or choose a menu command to turn a function on or off.                                                                                                                                                                                                        |

# **Typographic Conventions**

MAX+PLUS II documentation uses the following typographic conventions:

| Tiolac                      | İ |

|-----------------------------|---|

| MAX+PLUS II<br>Fundamentals |   |

| Visual Cue:             | Meaning:                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Initial Capitals   | Command names, dialog box titles, button names, and diskette names are shown in bold, with initial capital letters. For example: Find Text command, Save As dialog box, Start button, and Install diskette.                                                                                                                                                                                                           |

| bold                    | Directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold. Examples: \maxplus2 directory, d: drive, chiptrip.gdf file. These items are not casesensitive in the Windows environment; however, they are case-sensitive in the workstation environment. MAX+PLUS II Help shows these items in the case appropriate to the workstation environment. |

| Initial Capitals        | Keyboard keys, user-editable application window fields, and menu names are shown with initial capital letters. For example: Delete key, the Start Time field, the Options menu.                                                                                                                                                                                                                                       |

| "Subheading Title"      | Subheadings within a manual section are enclosed in quotation marks. In manuals, titles of help topics are also shown in quotation marks.                                                                                                                                                                                                                                                                             |

| Italic Initial Capitals | Help categories, section titles in manuals, application note and brief names, checkbox options, and options in dialog boxes are shown in italics with initial capital letters. For example: <i>Text Editor Procedures</i> , the <i>Check Outputs</i> option, the <i>Directories</i> box in the <b>Open</b> dialog box.                                                                                                |

| italics                 | Variables are enclosed in angle brackets (< >) and shown in italics. For example: <filename>, <pre>, cproject name&gt;.acf file.</pre></filename>                                                                                                                                                                                                                                                                     |

| Bold Italics            | Manual titles are shown in bold italics with initial capital letters. For example: MAX+PLUS II Getting Started.                                                                                                                                                                                                                                                                                                       |

| Visual Cue:                                  | Meaning:                                                                                                                                                                                                                                                                                                                              |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Courier font                                 | Anything that must be typed exactly as it appears is shown in Courier. For example: c:\max2work\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), and primitive and macrofunction names (e.g., DFF and 16CUDSLR) are shown in Courier. |  |

| Bold Courier font                            | In syntax descriptions, bold Courier may be used to help distinguish literal text from variables.                                                                                                                                                                                                                                     |  |

| 1., 2., 3.,, a., b., c.,, and i., ii., iii., | Numbered steps are used in a list of items when<br>the sequence of the items is important, such as<br>the steps listed in a procedure.                                                                                                                                                                                                |  |

| •                                            | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                                  |  |

| ✓                                            | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                                   |  |

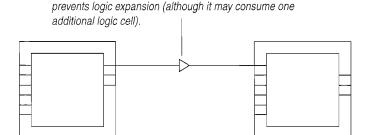

|                                              | The hand points to information that requires special attention.                                                                                                                                                                                                                                                                       |  |

|                                              | In MAX+PLUS II manuals, the feet show you where to go for more information on a particular topic.                                                                                                                                                                                                                                     |  |

| õ)                                           | In MAX+PLUS II Help, the upward-pointing hand indicates that you can click Button 1 (the left mouse button) on any portion of the illustration that follows it to get help on that item. The mouse pointer changes to an upward-pointing hand when it is over a picture or word for which help is available.                          |  |

| Special symbols                              | Special symbols are used for these items:                                                                                                                                                                                                                                                                                             |  |

|                                              | <ul><li>← Enter key (manuals only)</li><li>J Low-to-high transition</li><li>Ligh-to-low transition</li></ul>                                                                                                                                                                                                                          |  |

#### **Key Combinations**

Key combinations and sequences appear in the following format:

| Format Cue: | Meaning:                                                                                                                                                                                          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Key1+Key2   | A plus (+) symbol indicates that you must hold down the first key when you press the second key. For example: Ctrl+L means that you must hold down Ctrl while pressing L, then release both keys. |

| Key1,Key2   | A comma (,) indicates that you must press the keys sequentially. For example: Alt,F1 means that you must press the Alt key and release it, then press the F1 key and release it.                  |

#### **Backus-Naur Form**

The Backus-Naur Form (BNF) defines the syntax of the text file formats and message variables. BNF uses the following notation:

| Characters:  | Meaning:                                                                                                                                                       |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ::=          | "is defined as"                                                                                                                                                |

| <>           | Identifiers (i.e., variables)                                                                                                                                  |

| []           | Optional items                                                                                                                                                 |

| { }          | Repeated items (zero or more times)                                                                                                                            |

| 1            | Indicates a choice between items                                                                                                                               |

| :n:n         | Suffix indicates a range (e.g., < name char>:1:8 means "from 1 to 8 name characters")                                                                          |

| italics      | Variables in syntax descriptions                                                                                                                               |

| Courier font | Literal text in syntax descriptions. Bold Courier font is sometimes used to help distinguish literal text from <i>italic variables</i> in syntax descriptions. |

## MAX+PLUS II Help Updates

MAX+PLUS II Help is updated whenever the MAX+PLUS II software is updated; therefore, the on-line information is always current.

If you find a discrepancy between a MAX+PLUS II manual and the MAX+PLUS II on-line Help, you should rely on the MAX+PLUS II Help information.

You can get information on changes to MAX+PLUS II software and Help by choosing **New Features in this Release** (Help Menu) in MAX+PLUS II. Latebreaking news on Help and software is also available with the **READ.ME** command (Help menu).

## Sample Files

A number of sample design files are copied to your hard disk when you install MAX+PLUS II. The installation procedure automatically creates subdirectories for these files.

The pathnames below are shown using the PC pathname convention of backslash (\) characters, but UNIX pathnames use forward slash (/) characters. On a UNIX workstation, the /max2work directory is a subdirectory of the /usr directory. Otherwise, the file and directory organization is identical.

- The \max2work\chiptrip directory contains all files for the chiptrip tutorial project that is described in *MAX+PLUS II Getting Started*.

- The \max2work\ahdl directory contains all sample files used to illustrate AHDL features in MAX+PLUS II Help and in the MAX+PLUS II AHDL manual.

- The \max2work\vhdl directory contains all sample files used to illustrate VHDL features in MAX+PLUS II Help and in the MAX+PLUS II VHDL manual.

- The \max2work\edif directory contains all sample files used to illustrate EDIF features in MAX+PLUS II Help.

Go to "MAX+PLUS II File Organization" in the *MAX+PLUS II Installation* section of the *MAX+PLUS II Getting Started* manual for more information about MAX+PLUS II directory structure.

Go to the Altera-provided Software Interface Guide for your third-party environment for information on the directory structure and sample files installed for third-party interfaces to MAX+PLUS II.

Preface

MAX+PLUS I Fundamental

#### About MAX+PLUS II AHDL

#### *MAX+PLUS II AHDL* contains the following sections:

Section 1: Introduction discusses basic AHDL features and the order in which AHDL statements appear in a Text Design File (.tdf). This section also summarizes essential rules and guidelines that will help you use AHDL effectively.

Section 2: How to Use AHDL describes how to develop a successful AHDL design. Altera recommends that you read the topics in this section sequentially.

Section 3: Elements describes the basic elements of a TDF. These elements are used in the behavioral statements described in Section 4: Design Structure.

Section 4: Design Structure describes all behavioral statements and sections used in AHDL.

Section 5: Style Guide provides guidelines for formatting TDFs to improve readability and avoid errors.

Glossary

Index

# Introduction

This section provides an overview of the Altera Hardware Description Language (AHDL). Some of the characteristics that distinguish AHDL as a hardware description language are discussed, and AHDL file structure is briefly described. This section also describes how to enter and process an AHDL file, and provides essential rules and guidelines for using AHDL effectively.

|     | AHDL Design Entry       | 2 |

|-----|-------------------------|---|

|     |                         |   |

|     | MAX+PLUS II Text Editor |   |

| 100 |                         |   |

|     | Golden Rules            |   |

Go to MAX+PLUS II Help for complete and up-to-date information on AHDL.

# **AHDL Design Entry**

The Altera Hardware Description Language (AHDL) is a high-level, modular language that is completely integrated into the MAX+PLUS II system. It is especially well suited for designing complex combinatorial logic, group operations, state machines, truth tables, and parameterized logic. You can use the MAX+PLUS II Text Editor or another text editor to create AHDL Text Design Files (.tdf). You can then compile TDFs to create output files for simulation, timing analysis, and device programming. In addition, the MAX+PLUS II Compiler can generate AHDL Text Design Export File (.tdx) and Text Design Output File (.tdo) that can be saved as TDFs and re-used as design files.

#### **How Does AHDL Work?**

AHDL statements and elements are powerful, versatile, and easy to use. You can create entire hierarchical projects with AHDL, or mix AHDL TDFs with other types of design files in a hierarchical design (called a "project" in MAX+PLUS II). In addition, AHDL TDFs can be parameterized.

Although you can use any ASCII text editor to create AHDL designs, the MAX+PLUS II Text Editor allows you to take advantage of features available only in MAX+PLUS II while you enter, compile, and debug an AHDL design.

AHDL designs are easily incorporated into a design hierarchy. In the Text Editor, you can automatically create a symbol that represents a TDF and incorporate it into a Graphic Design File (.gdf). Similarly, you can incorporate custom functions, and over 300 Altera-provided megafunctions and macrofunctions—including Library of Parameterized Modules (LPM) functions—into any TDF by automatically creating an Include File (.inc) in the Text Editor. Altera provides Include Files for all mega- and macrofunctions shipped with MAX+PLUS II.

You can use Assign menu commands or an Assignment & Configuration File (.acf) to make resource and device assignments to allocate device resources for AHDL TDFs. You can also check AHDL syntax or perform a full compilation to debug and process your project. Any errors can be automatically located by the Message Processor and highlighted in the Text Editor window.

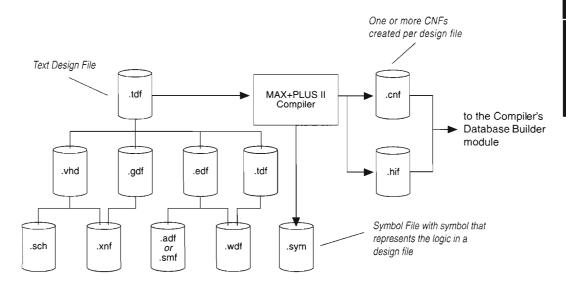

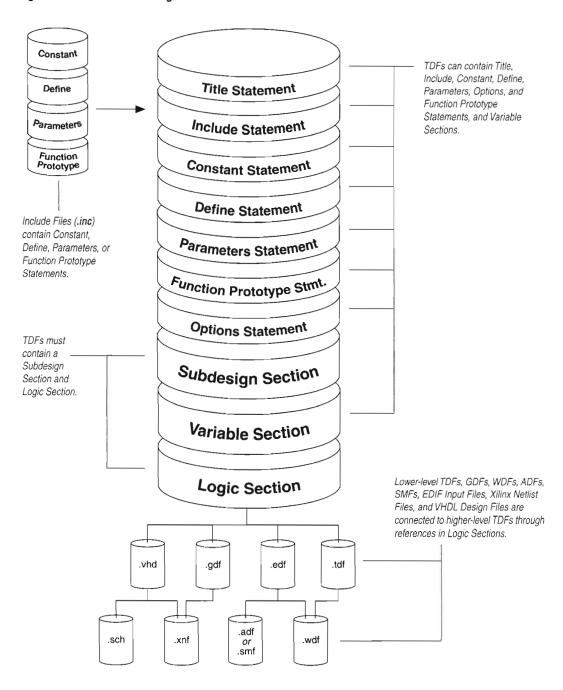

Figure 1-1 shows how TDFs can be integrated into the MAX+PLUS II system. A hierarchical project can contain TDFs, GDFs, EDIF Input Files (.edf), OrCAD Schematic Files (.sch), and VHDL Design Files (.vhd) at any level of the project hierarchy. In contrast, Waveform Design Files (.wdf), Altera Design Files (.adf), State Machine Files (.smf), and Xilinx Netlist Format Files (.xnf) can be used only at the lowest level of a project hierarchy, unless the entire project consists of a single WDF, ADF, SMF, or XNF File.

Figure 1-1. MAX+PLUS II & AHDL Design Entry

## **Text Design File Structure**

A Text Design File (.tdf) is an ASCII text file, written in AHDL, that can be entered with the MAX+PLUS II Text Editor or any standard text editor.

#### **Text Design File Sections**

The following AHDL sections and statements are listed in the order in which they appear in a TDF. Figure 1-2 also shows a TDF and the AHDL sections and statements that it can contain, and how Include Files and files in a project hierarchy can be used with AHDL.

- (Optional) Title Statement provides comments for the Report File (.rpt) generated by the MAX+PLUS II Compiler.

- (Optional) Include Statement specifies an Include File that replaces the Include Statement in the TDF.

- (Optional) Constant Statement specifies a symbolic name that can be substituted for a constant.

- (Optional) Define Statement defines an evaluated function, which is a mathematical function that returns a value that is based on optional arguments.

- (Optional) Parameters Statement declares one or more parameters that control the implementation of a parameterized megafunction or macrofunction. A default value can be specified for each parameter.

- (Optional) Function Prototype Statement declares the ports of a logic function and the order in which those ports must be declared in an in-line reference. In parameterized functions, it also declares the parameters used by the function.

- (Optional) Options Statement sets the default bit-ordering for the file, or for the project if the file is a top-level TDF.

- (Optional) Assert Statement allows you to test the validity of an arbitrary expression and report the results.

- (Required) Subdesign Section declares the input, output, and bidirectional ports of an AHDL TDF.

- (Optional) Variable Section declares variables that represent and hold internal information. Variables can be declared for ordinary or tri-state nodes, primitives, megafunctions, macrofunctions, and state machines. Variables can also be generated conditionally with an If Generate Statement. The Variable Section can include any of the following constructs:

- Instance Declaration

- Node Declaration

- Register Declaration

- State Machine Declaration

- Machine Alias Declaration

- If Generate Statement

- (Required) Logic Section defines the logical operations of the file. The Logic Section can define logic with Boolean equations, conditional logic, and truth tables. It also supports conditional and iterative logic generation, and the capability to test the validity of an arbitrary expression and report the results. The Logic Section can include any of the following constructs:

- Defaults Statement

- Assert Statement

- Boolean Equations

- Boolean Control Equations

- Case Statement

- For Generate Statement

- If Generate Statement

- If Then Statement

- In-Line Logic Function Reference

- Truth Table Statement

Figure 1-2. AHDL Text Design File Structure

AHDL is a concurrent language. All behavior specified in the Logic Section of a TDF is evaluated at the same time rather than sequentially. Equations that assign multiple values to the same AHDL node or variable are logically connected (ORed if the node or variable is active high, ANDed if it is active low). See "Defaults Statement" on page 173 in Design Structure and "Using Default Values for Variables" on page 39 in How to Use AHDL for more information.

A TDF must contain a Subdesign Section and a Logic Section. It can optionally contain a single Variable Section, Options Statement, Title Statement, and Defaults Statement, and one or more Include, Constant, Define, and Function Prototype Statements.

The last entries in a TDF are the Subdesign Section, Variable Section (optional), and Logic Section, which together contain the behavioral description of the TDF.

See Design Structure on page 139 for more information about AHDL statements. Go to the Backus-Naur Form (BNF) syntax descriptions of each AHDL section in MAX+PLUS II Help using Search for Help on (Help menu).

#### Files in a Project Hierarchy

Files in a project hierarchy can be TDFs, GDFs, WDFs, ADFs, SMFs, EDIF Input Files, OrCAD Schematic Files, AHDL Design Files, or Xilinx Netlist Format Files. Each logic function is connected through its input and output ports to the design file at the next higher level. For more information, see "Implementing a Hierarchical Project" on page 69 in *How to Use AHDL*.

#### Include Files

An Include File is an ASCII text file (with the extension .inc) that can be imported into a TDF with an AHDL Include Statement. The contents of the Include File replace the Include Statement that calls the file. Include Files can contain Function Prototype, Constant, Define, and Parameters Statements.

Each Altera-provided megafunction and macrofunction has an Include File that contains its Function Prototype:

- The Include Files for megafunctions, including LPM functions, are located in the maxplus2\max2lib\mega\_lpm directory created during installation.

- The Include Files for macrofunctions are located in the \maxplus2\max2inc directory created during installation.

On UNIX workstations, the **maxplus2** directory is a subdirectory of the **/usr** directory.

When you have a design file open in a Graphic, Text, or Waveform Editor window, you can choose **Create Default Include File** (File menu) to automatically generate an Include File that contains a default Function Prototype for the design file. You can also manually create an Include File with the MAX+PLUS II Text Editor or another standard text editor.

Go to "Creating a Default Include File" in MAX+PLUS II Help for more information.

### MAX+PLUS II Text Editor

AHDL Text Design Files (with the extension .tdf) can be entered with the MAX+PLUS II Text Editor or any other text editor that follows standard ASCII character conventions. If your text editor has both document and nondocument modes, you must use non-document mode, i.e., save the file as text only.

The MAX+PLUS II Text Editor allows you to take advantage of the following unique MAX+PLUS II features while you enter, compile, and debug an AHDL TDF:

- AHDL templates and examples

- AHDL context-sensitive help

- Syntax coloring

- Resource and device assignments

- Error location

Go to MAX+PLUS II Text Editor Help for more information on using the MAX+PLUS II Text Editor.

#### AHDL Templates & Examples

MAX+PLUS II provides both AHDL templates and AHDL examples to make design entry easier for you.

- AHDL Templates—You can insert AHDL templates into your TDF, then replace placeholder variables in the templates with your own identifiers and expressions.

- AHDL Examples—MAX+PLUS II provides a number of AHDL examples that are used to illustrate AHDL features in the How to Use AHDL section of this manual. These examples are available in the **\max2work\ahdl** directory (a subdirectory of the **/usr** directory on a UNIX workstation), and in MAX+PLUS II AHDL Help. You can customize these examples to fit your needs.

Go to "Inserting an AHDL Template" on page 22 and "AHDL Examples" on page 24 in How to Use AHDL for more information on using AHDL templates and examples.

#### **AHDL Context-Sensitive Help**

If the current file has the extension .tdf, the MAX+PLUS II Text Editor provides context-sensitive help on all AHDL keywords, operators, comparators, and punctuation, as well as on all MAX+PLUS II-provided primitives, megafunctions, and macrofunctions.

When you choose the context-sensitive Help button ( ? ) from the toolbar or press Shift+F1, the pointer turns into a question mark pointer. You can then click Button 1 on a word or character in an AHDL. If context-sensitive help is available for that item, the relevant information is displayed. Otherwise, Help shows a list of all items for which context-sensitive help is available.

#### Syntax Coloring

The MAX+PLUS II Text Editor allows you to view various elements of a TDF in different colors. Syntax coloring can help you improve file readability and accuracy. For instance, it can help you identify misspelled keywords and sections of files that have been commented out by mistake.

To turn the syntax coloring feature on or off:

✓ Choose Syntax Coloring from the Options menu.

You can also use the **Color Palette** command (Options menu) to customize the assigned colors for comments, illegal characters, megafunctions and macrofunctions, reserved identifiers and keywords, strings, and text.

Go to "Using Syntax Coloring in Text Files" and "Changing Colors in MAX+PLUS II" in MAX+PLUS II Help for more information.

#### Resource & Device Assignments

You can specify resource assignments—i.e., pin, logic cell, I/O cell, embedded cell, Logic Array Block (LAB), Embedded Array Block (EAB), row, column, chip, clique, logic option, connected pin, and timing assignments—as well as device assignments for a TDF to guide logic synthesis and fitting for your project. You can choose to have the Compiler automatically fit your project into the best combination of devices from a target device family and assign the resources within them. You can also select a node or pin name in the Text Editor and enter a specific assignment for it with the Pin/Location/Chip, Clique, Logic Options, Timing **Requirements**, Connected Pins, and other commands on the Assign menu. (Assign menu commands are also available in all other MAX+PLUS II applications.) You can also enter assignments with the Floorplan Editor or by editing the Assignment & Configuration File (.acf) in the Text Editor.

For example, you can assign a logic synthesis style that tailors logic synthesis to your needs, and specify precisely how to divide a large project into multiple devices, and make timing assignments to achieve speed performance on individual logic functions.

MAX+PLUS II provides the *Use LPM for AHDL Operators* logic option, which allows the Compiler to substitute lpm\_add\_sub and lpm\_compare functions automatically for the following operators and comparators:

| Operator/<br>Comparator: | Description:             |

|--------------------------|--------------------------|

| +                        | addition                 |

| -                        | subtraction              |

| ==                       | numeric equality         |

| ! =                      | not equal to             |

| >                        | greater than             |

| >=                       | greater than or equal to |

| <                        | less than                |

| <=                       | less than or equal to    |

Go to MAX+PLUS II Help for more information on making resource and device assignments.

#### **Error Location**

MAX+PLUS II interactively reports and locates errors that occur as you process your project. As you compile a project, a Message Processor window opens and lists error, information, and warning messages for the project. You can locate the source(s) of a message by double-clicking Button 1 on the message text. MAX+PLUS II then automatically opens the design file that contains the source of the message, regardless of its location in the project hierarchy or the type of application that created it. If the error occurs in a TDF, MAX+PLUS II opens a Text Editor window and highlights the text that caused the error. You can also locate errors in the assignment floorplan for the project in the MAX+PLUS II Floorplan Editor.

Go to "Locating the Source of a Message" using **Search for Help on** (Help menu) for more information on error location.

# **Compiling AHDL Text Design Files**

MAX+PLUS II automatically compiles AHDL TDFs. When you have finished entering a TDF, you can check its syntax with the **Project Save & Check** command (File menu), or compile all files in a project with the **Project Save & Compile** command (File menu). If you wish to generate an AHDL Text Design Output File (.tdo) for a compiled project, you can turn on the Compiler's **Generate AHDL TDO File** command (Processing menu) before compiling the project. After the project has compiled successfully, you can perform optional simulation and timing analysis, and then program one or more devices.

For complete on-line information on the MAX+PLUS II Text Editor, go to MAX+PLUS II Help. For detailed instructions and suggestions on how to use AHDL sections and statements to develop a project, go to *How to Use AHDL* on page 17. For a step-by-step tutorial on how to enter, compile, simulate, and program a project that includes AHDL TDFs with MAX+PLUS II, go to *MAX+PLUS II Tutorial* in the *MAX+PLUS II Getting Started* manual.

#### **Golden Rules**

The following golden rules will help you use AHDL effectively:

- Use the Text Editor's Syntax Coloring command (Options menu) to help you identify typographical errors and different sections of AHDL code.

- Follow the formatting and naming guidelines described in the *Style Guide* on page 187 to improve readability and avoid errors.

- Although AHDL is not case-sensitive, Altera recommends that you follow the capitalization rules in the *Style Guide* to improve readability.

- Use constants and evaluated functions, which are created in Constant and Define Statements, to improve readability and to avoid errors.

- You do not need to create AHDL Function Prototypes for primitives. However, you can redefine primitives with a Function Prototype Statement to change the calling order of inputs in your TDF.

- Do not use nested If Then Statements when a Case Statement can be used instead.

- When you use the MAX+PLUS II Text Editor to create a TDF, each line can be up to 255 characters long. However, the ideal line length is the number of characters your screen can accommodate. Press Enter to end a line.

- You can start new lines wherever white space (i.e., blank lines, tabs, and spaces) is allowed, without any effect on meaning. White space is allowed between major AHDL constructs.

- Keywords, names, and numbers must be separated by the appropriate symbols or operators, and one or more spaces.

- Comments must be enclosed in percent symbols (%). A comment can include any character except %, since the MAX+PLUS II Compiler ignores everything between the percent symbols. Comments enclosed in percent symbols cannot be nested .

VHDL-style comments (--) can be nested within %-style comments. If you use VHDL-style comments for documentation-type comments, you can use the %-style comments to exclude sections of code from compilation (i.e., "comment out" sections of code).

- When connecting a primitive to another primitive, you must use only "legal" interconnections; not all primitives may connect to all other primitives. For a list of legal interconnections for primitives, see "Primitive/Port Interconnections" on page 127 in *Elements*.

- Do not create your own cross-coupled structures; use only the expdff, explatch, inpltch, nandltch, and norltch macrofunctions provided with MAX+PLUS II. (These macrofunctions are not optimized for FLEX 8000 and FLEX 10K architectures.) Avoid tying multiple instances of expdff, explatch, inpltch, nandltch, and norltch macrofunctions together. Multiple instances of these macrofunctions should always be separated by LCELL primitives.

#### **General Design Entry Golden Rules**

- You should use Altera-provided primitives and AHDL logical operators rather than the equivalent LPM functions in most cases: they are much more convenient to instantiate. For example, if you wish to load a register on a specific rising edge of the global Clock, Altera recommends that you use the Clock Enable input of one of the DFFE, TFFE, JKFFE, or SRFFE Enable-type flipflops to control when the register is loaded.

- Use LPM megafunctions rather than equivalent old-style macrofunctions in most cases: the former are more convenient to instantiate and easier to modify if your design changes.

- Use the Design Doctor to check the reliability of your project logic during compilation. Go to "Project Reliability Guidelines" in MAX+PLUS II Help for information on how to create reliable projects.

- Do not attempt to create your own logic functions to implement RAM or ROM: use Altera-provided megafunctions instead.

- When you start a new design file, specify the target device family with **Device** (Assign menu) right away, so that you can take advantage of

family-specific macrofunctions. If you do not specify a device family, the family for the current project is assumed.

#### General MAX+PLUS II Golden Rules

- When you start work on a new design file, name it as the current project with Project Set Project to Current File or Project Name (File menu) right away so that you can compile it easily. You can always change the project name later.

- Use the built-in hierarchy traversal features in MAX+PLUS II to move between design files for the current hierarchy tree. To open a lower-level file in a hierarchy, open the top-level file and then use the Hierarchy Display window or **Hierarchy Down** (File menu) to open the lower-level files. If you choose **Open** or **Retrieve** (File menu) to open a lower-level file, that file is considered to be the top of a different hierarchy tree, and resource, device, and probe assignments that you enter are saved only for that hierarchy, not for the project.

- When you create an editable ancillary file for a project, the icon for the file will appear in the Hierarchy Display if you use the same filename as the project.

- Don't edit any MAX+PLUS II system files, including HIFs, TOK files, maxplus2.idx files, or the maxplus2.ini file.

- Use the Save As command (File menu) if you wish to rename a design file or an ancillary file. Do not rename design files from outside of the MAX+PLUS II system (e.g., from DOS or with the Windows File Manager).

- When you have completed a project, use **Project Archive** (File menu) to save a complete backup copy of all project files that will not be affected by future edits or deletions.

2

# How to Use AHDL

This section describes how to develop a successful AHDL design. All sample files shown in this section are also available in the \max2work\ahdl directory created during MAX+PLUS II installation. (On a UNIX workstation, the max2work directory is a subdirectory of the /usr directory.)

Design practices are discussed in the following order:

| Introduction                            | 18 |

|-----------------------------------------|----|

| Combinatorial Logic                     | 25 |

| Sequential Logic                        |    |

| State Machines                          |    |

| Implementing a Hierarchical Project     | 69 |

| Implementing LCELL & SOFT Primitives    |    |

| Implementing RAM & ROM                  |    |

| Naming a Boolean Operator or Comparator | 84 |

| Using Iteratively Generated Logic       |    |

| Using Conditionally Generated Logic     |    |

| Using the Assert Statement              |    |

|                                         |    |

2

How to Use AHDL

## Introduction

AHDL is an easy-to-use text entry language for describing logic designs. You can use the MAX+PLUS II Text Editor or your own text editor to create AHDL Text Design Files (.tdf), which can be incorporated into a project hierarchy together with other design files. You can then compile the project, simulate it, and program Altera devices.

AHDL consists of a variety of elements that are used in behavioral statements to describe logic. This section includes information on how these elements and statements are used; for detailed descriptions and rules, refer to *Elements* and *Design Structure*.

The following topics are discussed:

| 64 | Using Numbers                         | 18 |

|----|---------------------------------------|----|

|    | Using Constants & Evaluated Functions |    |

|    | Inserting an AHDL Template            | 22 |

|    | ¥                                     |    |

|    | 1                                     |    |

## **Using Numbers**

Numbers are used to specify constant values in Boolean expressions and equations, arithmetic expressions, and parameter values. AHDL supports all combinations of decimal, binary, octal, and hexadecimal numbers.

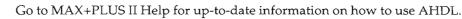

The **decode1.tdf** file shown in Figure 2-1 is an address decoder that generates an active-high chip enable when the address is 370 Hex.

#### Figure 2-1. decode1.tdf

```

SUBDESIGN decode1

(

address[15..0] :INPUT;

chip_enable :OUTPUT;

)

BEGIN

chip_enable = (address[15..0] == H*0370*);

END;

```

In this sample file, the decimal numbers 15 and 0 are used to specify bits of the address bus. The hexadecimal number H " 0370 " specifies the address that is decoded.

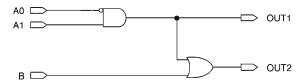

Figure 2-2 shows a Graphic Design file (.gdf) that is equivalent to decode1.tdf.

Figure 2-2. decode1.gdf

Go to the following topics for more information:

## **Using Constants & Evaluated Functions**

You can use a constant in an AHDL file to give a descriptive name to a number or text string. Similarly, you can use an evaluated function to give a descriptive name to an arithmetic expression. This name, which can be used throughout a file, can be more informative and readable than the number, string, or arithmetic expression. For example, the numeric constant UPPER\_LIMIT is more informative than the number 130.

<sup>&</sup>quot;Numbers in AHDL" on page 102 in Elements

<sup>&</sup>quot;Parameters Statement" on page 142 in Design Structure

<sup>&</sup>quot;Using Constants & Evaluated Functions" on page 19 in this section

Constants and evaluated functions are especially useful if the same number, text string, or arithmetic expression is repeated several times in a file: if it changes, only one statement needs to be changed. In AHDL, constants are implemented with Constant Statements, and evaluated functions are implemented with Define Statements.

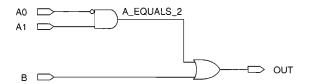

The **decode2.tdf** file shown in Figure 2-3 has the same functionality as **decode1.tdf** (shown in Figure 2-1 on page 18), but uses the constant IO\_ADDRESS instead of the number H " 0370".

#### Figure 2-3. decode2.tdf

```

CONSTANT IO_ADDRESS = H"0370";

SUBDESIGN decode2

(

a[15..0] : INPUT;

ce : OUTPUT;

)

BEGIN

ce = (a[15..0] == IO_ADDRESS);

END;

```

You can define constants and evaluated functions with arithmetic expressions. Constants and evaluated functions can also be defined with previously defined constants, evaluated functions, or parameters.

In the following example, the constant foo is defined with an arithmetic expression and the constant foo\_plus\_one is defined with the previously defined constant foo:

```

CONSTANT foo = 1 + 2 DIV 3 + LOG2(256);

CONSTANT foo_plus_one = foo + 1;

```

In the following example, the evaluated function CEILING\_ADD is defined on the basis of the previously defined evaluated function MAX:

```

DEFINE MAX(a,b) = (a > b) ? a : b;

DEFINE CEILING_ADD(a,b) = MAX(a,b) + 1;

```

The Compiler evaluates arithmetic operators in arithmetic expressions and reduces them to numerical values. No logic is generated for these expressions.

The **strcmp.tdf** file shown in Figure 2-4 defines the constant FAMILY and uses it in an Assert Statement to check whether the current device family is FLEX 8000.

#### Figure 2-4. strcmp.tdf

```

PARAMETERS

DEVICE_FAMILY % DEVICE_FAMILY is a predefined Altera parameter %

);

CONSTANT FAMILY = "FLEX8000";

SUBDESIGN strcmp

(

a : INPUT;

b : OUTPUT;

BEGIN

IF (DEVICE_FAMILY == FAMILY) GENERATE

ASSERT

REPORT "Detected compilation for FLEX8000 family"

SEVERITY INFO;

b = a;

ELSE GENERATE

ASSERT

REPORT "Detected compilation for % family"

DEVICE_FAMILY

SEVERITY ERROR;

b = a;

END GENERATE;

END;

```

The **minport.tdf** file shown in Figure 2-5 defines the evaluated function MAX, which ensures a minimum port width in the Subdesign Section:

#### Figure 2-5. minport.tdf

```

PARAMETERS (WIDTH);

DEFINE MAX(a,b) = (a > b) ? a : b;

SUBDESIGN minport

(

dataA[MAX(WIDTH,0)..0] : INPUT;

dataB[MAX(WIDTH,0)..0] : OUTPUT;

)

BEGIN

dataB[] = dataA[];

END;

```

Go to the following topics for more information:

"Constant Statement" on page 147 in Design Structure

"Define Statement" on page 149 in Design Structure

"Quoted & Unquoted Names" on page 97 in Elements

"Using Default Values for Variables" on page 39 in this section

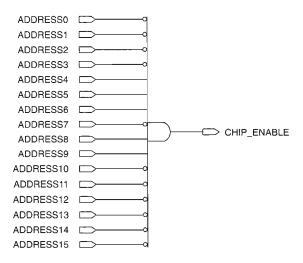

## **Inserting an AHDL Template**

The fastest way to create AHDL designs in MAX+PLUS II is to use the Altera-provided AHDL templates. With the **AHDL Template** command (Templates menu), available in the MAX+PLUS II Text Editor, you can insert AHDL templates into your TDF to speed design entry.

A single template is available for the overall AHDL file structure. This template, called "Overall Structure," lists all AHDL constructs in separate comment lines in the order in which they appear in a TDF. The syntax of these sections and statements is not included; you must replace the comment line with the correct AHDL syntax for each section you wish to use in your file.

Use the following steps to insert an AHDL template at the current insertion point in a MAX+PLUS II Text Editor file:

- 1. Save your file with the .tdf extension.

- 2. Choose **AHDL Template** (Templates menu). The **AHDL Template** dialog box is displayed, as shown in Figure 2-6:

Figure 2-6. AHDL Template Dialog Box

- 3. Select a name in the *Template Section* box.

- 4. Choose **OK**.

- 1. Shortcuts are available for this command. Go to "AHDL Template command" in MAX+PLUS II Help for details.

- 2. All AHDL templates are also available in the ASCII ahdl.tpl file, which is automatically installed in the \maxplus2 directory (a subdirectory of the /usr directory on a UNIX workstation).

Once you have inserted a template into your TDF, you must replace all variables in the template with your own logic. Figure 2-7 shows the Defaults Statement template.

Figure 2-7. Defaults Statement Template

```

DEFAULTS

__node_name = __constant_value;

END DEFAULTS;

```