Step by Step Procedure to run the Intel® Arria® 10 SoCFPGA-HardwareLib-Ethernet-A10-ARMCC example in Intel® SoC FPGA Embedded Development Suite (SoC EDS) Professional Edition Software Version 2020.1

Open SoC EDS Command Shell using the below command-For 20.1 Pro: Start menu > Intel FPGA 20.1 Pro Edition > SoC EDS Command Shell.

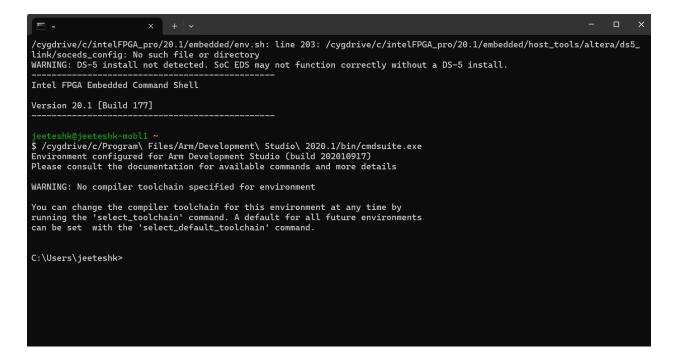

Run the cmdsuite program

/cygdrive/c/Program\ Files/Arm/Development\ Studio\ 2020.1/bin/cmdsuite.exe

- 3. If needed, run the **select\_toolchain** command to select between Arm Compiler 5 and Arm Compiler 6

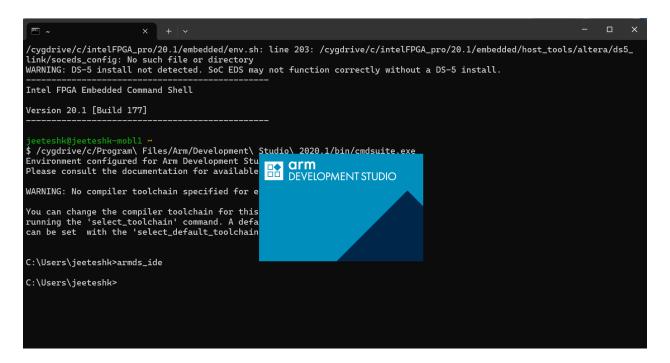

- 4. Run the **armds\_ide** command.

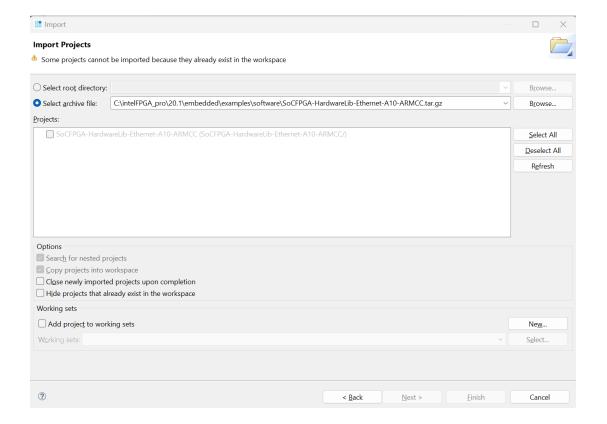

- 5. Click on File → Import Projects

- 6. Select Archive file and browse the SoCFPGA-HardwareLib-Ethernet-A10-ARMCC, select all and Finish.

- 7. Boot the Intel® Arria® 10 SX SoC Development Kit from the SD Card.

- 8. Press any key to stop at u-boot.

```

U-Boot SPL 2023.04 (Oct 03 2023 - 08:37:14 +0000)

FPGA: Checking FPGA configuration setting ...

FPGA: Start to program peripheral/full bitstream ...

FPGA: Early Release Succeeded.

FPGA: Checking FPGA configuration setting ...

FPGA: Start to program peripheral/full bitstream ...

FPGA: Early Release Succeeded.

U-Boot SPL 2023.04 (Oct 03 2023 - 08:37:14 +0000)

DDRCAL: Success

DDRCAL: Scrubbing ECC RAM (1024 MiB).

DDRCAL: SDRAM-ECC initialized success with 332 ms

FPGA: Checking FPGA configuration setting ...

FPGA: Skipping configuration ...

WDT: Started watchdog@ffd00300 with servicing every 1000ms (10s timeout)

Trying to boot from MMC1

U-Boot 2023.04 (Oct 03 2023 - 08:37:14 +0000)socfpga_arria10

Altera SoCFPGA Arria 10

BOOT: SD/MMC External Transceiver (1.8V)

Model: Altera SOCFPGA Arria 10

DRAM: 1 GiB

Core: 77 devices, 20 uclasses, devicetree: separate

Started watchdog@ffd00300 with servicing every 1000ms (10s timeout)

MMC:

dwmmc0@ff808000: 0

Loading Environment from MMC... *** Warning - bad CRC, using default environment

In:

serial

Out: serial

Err:

serial

Model: Altera SOCFPGA Arria 10

Warning: ethernet@ff800000 (eth0) using random MAC address - 3a:fc:65:32:f3:4e

eth0: ethernet@ff800000

Hit any key to stop autoboot: 0

=>

=>

```

9. Run these below commands at uboot.

```

=> setenv autoload no

=> dhcp

Speed: 1000, full duplex

BOOTP broadcast 1

DHCP client bound to address 10.227.90.150 (9 ms)

=> dcache off

=> icache off

```

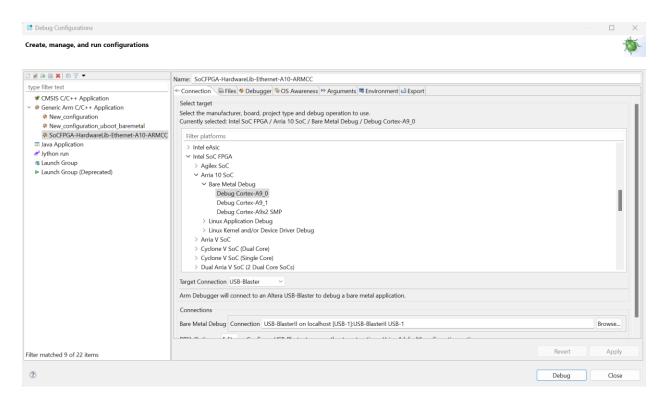

10. Right click on SoCFPGA-HardwareLib-Ethernet-A10-ARMCC in Project Explorer and select the Debug As→Debug Configurations and make changes to Connection tab as below snapshot.

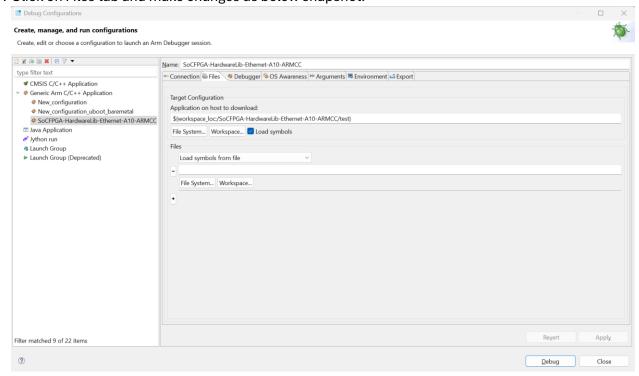

11. Click on Files tab and make changes as below snapshot.

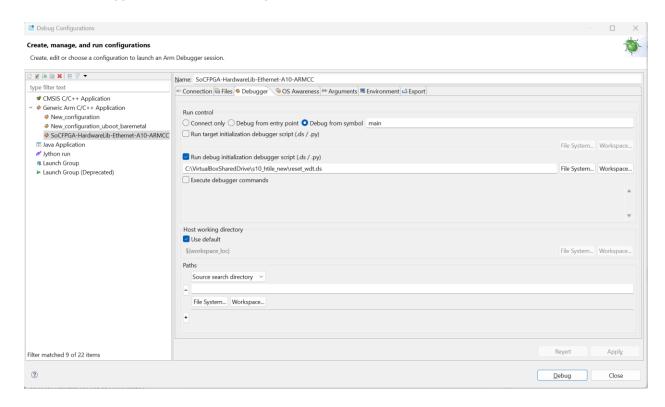

12. Create a file naming with reset\_wdt.ds and copy the below lines in reset\_wdt.ds file.

set var \$Peripherals::\$i\_rst\_mgr::\$i\_rst\_mgr\_per1modrst.watchdog0 = 0x1 set var \$Peripherals::\$i\_rst\_mgr::\$i\_rst\_mgr\_per1modrst.watchdog1 = 0x1

13. Click on Debugger tab and make changes as below snapshot.

- 14. Click on Apply and Debug.

- 15. You will see that ethernet application starts printing on App Console

```

© Console ■ Commands ** Variables ■ Registers ■ Memory *** Disassembly ■ Target Console ■ App Conso

```

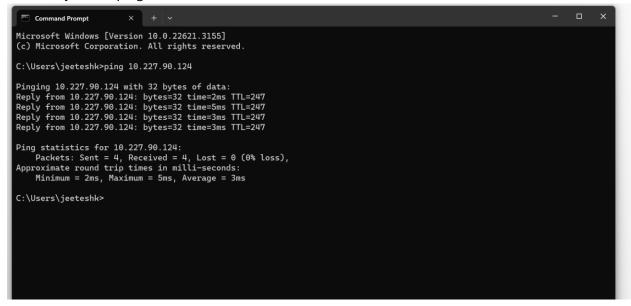

16. From the above snapshot, you will see that board received the IP address from the server i.e. 10.227.90.124

From PC you can ping the board IP address 10.227.90.124