# Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Family

Datasheet

October 2008

Document Number: 319973-003

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The Intel<sup>®</sup> I/O Controller Hub 10 (ICH10) Family chipset component may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel<sup>®</sup> Active Management Technology requires the computer system to have an Intel<sup>®</sup> AMT-enabled chipset, network hardware and software, as well as connection with a power source and a corporate network connection. Setup requires configuration by the purchaser and may require scripting with the management console or further integration into existing security frameworks to enable certain functionality. It may also require modifications of implementation of new business processes. With regard to notebooks, Intel AMT may not be available or certain capabilities may be limited over a host OS-based VPN or when connecting wirelessly, on battery power, sleeping, hibernating or powered off. For more information, see www.intel.com/technology/jnlatform-technology/intel-amt/

Intel<sup>®</sup> Virtualization Technology requires a computer system with an enabled Intel<sup>®</sup> processor, BIOS, virtual machine monitor (VMM) and, for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary depending on hardware and software configurations and may require a BIOS update. Software applications may not be compatible with all operating systems. Please check with your application vendor.

No computer system can provide absolute security under all conditions. Intel<sup>®</sup> Trusted Execution Technology (Intel<sup>®</sup> TXT) requires a computer system with Intel<sup>®</sup> Virtualization Technology, an Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured launched environment (MLE). The MLE could consist of a virtual machine monitor, an OS or an application. In addition, Intel TXT requires the system to contain a TPM v1.2, as defined by the Trusted Computing Group and specific software for some uses. For more information, see http://www.intel.com/technology/security

Home networking capability and many Intel<sup>®</sup> Viiv<sup>™</sup> technology-based usage models will require additional hardware devices, software or services. Functionality of Intel<sup>®</sup> Viiv<sup>™</sup> technology verified devices will vary; check product details for desired features. System and component performance and functionality will vary depending on your specific hardware and software configurations. See www.intel.com/go/viiv\_info for more information.

Intel<sup>®</sup> High Definition Audio requires a system with an appropriate Intel chipset and a motherboard with an appropriate codec and the necessary drivers installed. System sound quality will vary depending on actual implementation, controller, codec, drivers and speakers. For more information about Intel<sup>®</sup> HD audio, refer to http://www.intel.com/

Intel, Intel logo, Intel SpeedStep, Intel Viiv, and Intel vPro are trademarks of Intel Corporation in the U.S. and other countries

\*Other names and brands may be claimed as the property of others.

Copyright © 2008, Intel Corporation

# Contents

| 1 | Intro        | 33                                                                                                                         | 3        |

|---|--------------|----------------------------------------------------------------------------------------------------------------------------|----------|

|   | 1.1          | About This Manual                                                                                                          | 3        |

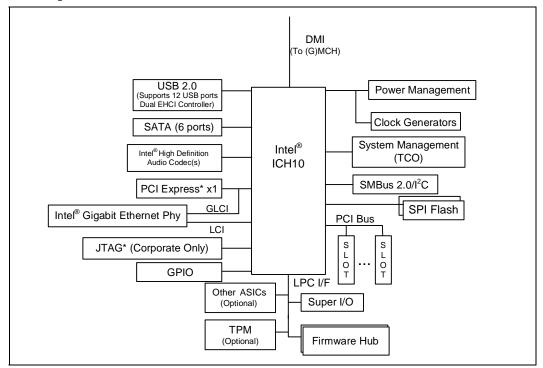

|   | 1.2          | Overview                                                                                                                   | 7        |

|   | 1.3          | 1.2.1       Capability Overview       39         Intel <sup>®</sup> ICH10 Family High-Level Component Differences       44 | 1        |

| • |              |                                                                                                                            |          |

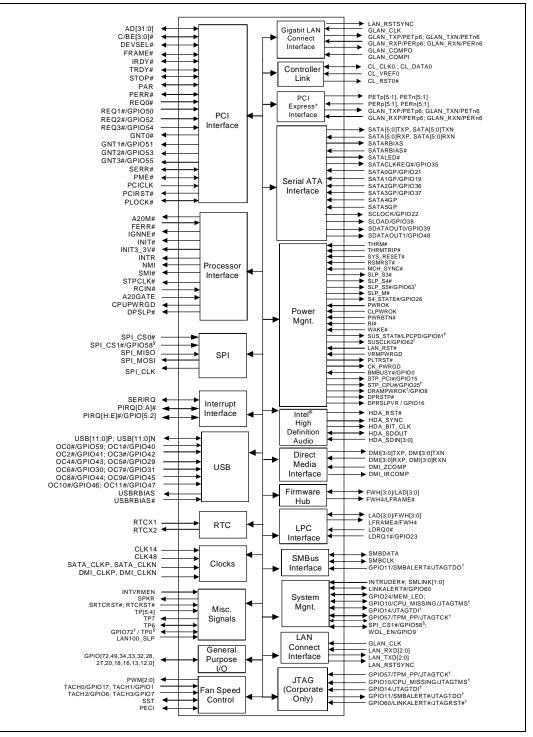

| 2 |              | I Description       45         Direct Media Interface (DMI) to Host Controller       47                                    | כ<br>ד   |

|   | 2.1<br>2.2   | PCL Express* Interface (DMT) to Host Controller                                                                            | /<br>2   |

|   | 2.3          | PCI Express* Interface                                                                                                     | ś        |

|   | 2.4          | Gigabit LAN Connect Interface                                                                                              | 9        |

|   | 2.5          | Firmware Hub Interface                                                                                                     | )        |

|   | 2.6<br>2.7   | PCI Interface                                                                                                              | ר<br>כ   |

|   | 2.8          | LPC Interface                                                                                                              | 5        |

|   | 2.9          | Interrupt Interface                                                                                                        | 5        |

|   | 2.10         | USB Interface                                                                                                              | ć        |

|   | 2.11<br>2.12 | Processor Interface                                                                                                        | 3<br>1   |

|   | 2.12         | SMBus Interface                                                                                                            | 2        |

|   | 2.14         | System Management Interface                                                                                                | 3        |

|   | 2.15         | Real Time Clock Interface                                                                                                  | 4        |

|   | 2.16<br>2.17 | Other Clocks                                                                                                               | 2<br>5   |

|   | 2.18         | Intel <sup>®</sup> High Definition Audio Link                                                                              | <i>5</i> |

|   | 2.19         | Intel <sup>®</sup> High Definition Audio Link                                                                              | 7        |

|   | 2.20         | Controller Link                                                                                                            | 3        |

|   | 2.21<br>2.22 | Intel <sup>®</sup> Quiet System Technology                                                                                 | 3<br>2   |

|   | 2.23         | JTAG Signals (Intel <sup>®</sup> ICH10 Corporate Family Only)                                                              | Ś        |

|   | 2.24         | Power and Ground Signals                                                                                                   | 3        |

|   | 2.25         | Pin Straps                                                                                                                 | 2        |

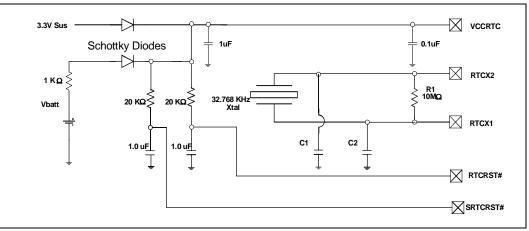

|   |              | 2.25.2 External RTC Circuitry                                                                                              | נ<br>ק   |

| 3 | Intel        | ICH10 Pin States                                                                                                           |          |

| 5 | 3.1          | Integrated Pull-Ups and Pull-Downs                                                                                         | 1        |

|   | 3.2          | Output and I/O Signals Planes and States                                                                                   | 3        |

|   | 3.3          | Power Planes for Input Signals 88                                                                                          | 3        |

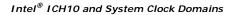

| 4 | Intel        | <sup>9</sup> ICH10 and System Clock Domains                                                                                | 1        |

| 5 |              | ional Description                                                                                                          |          |

| 0 | 5.1          | DMI-to-PCI Bridge (D30:F0)                                                                                                 | 3        |

|   |              | 5.1.1 PCI Bus Interface 93                                                                                                 | 3        |

|   |              | <ul> <li>5.1.2 PCI Bridge As an Initiator</li></ul>                                                                        | 3        |

|   |              | <ul> <li>5.1.3 Parity Error Detection and Generation</li></ul>                                                             | с<br>6   |

|   |              | 5.1.5 Peer Cycles                                                                                                          | <i>5</i> |

|   |              | 5.1.6 PCI-to-PCI Bridge Model                                                                                              | 6        |

|   |              | 5.1.7       IDSEL to Device Number Mapping       97         5.1.8       Standard PCI Bus Configuration Mechanism       97  | 7        |

|   | 5.2          | 5.1.8 Standard PCI Bus Configuration Mechanism                                                                             | 7        |

|   | 0.2          | 5.2.1 Interrupt Generation                                                                                                 | 7        |

|   |              | 5.2.2 Power Management                                                                                                     | В        |

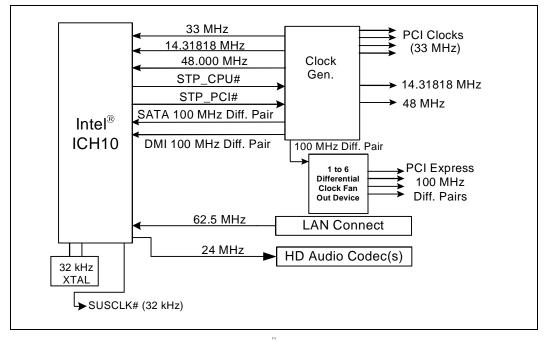

|   |              | 5.2.3 SERR# Generation                                                                                                     |          |

|   | 5.3          | 5.2.4 Hot-Plug                                                                                                             |          |

|   | 5.5          | 5.3.1 Gigabit Ethernet PCI Bus Interface                                                                                   | 2        |

|   |              | 5.3.2 Error Events and Error Reporting                                                                                     | 3        |

|   |              | 5.3.3 Ethernet Interface                                                                                                   |          |

|   |              | 5.3.4         PCI Power Management         104           5.3.5         Configurable LEDs         105                       |          |

|   |              |                                                                                                                            | 1        |

|      | 5.3.6 Function Level Reset Support (FLR)<br>LPC Bridge (w/ System and Management Functions) (D31:F0)        | 106 |

|------|-------------------------------------------------------------------------------------------------------------|-----|

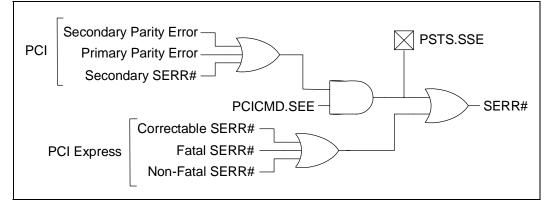

| 5.4  | LPC Bridge (w/ System and Management Functions) (D31:F0)                                                    | 107 |

|      | 5.4.1 LPC Interface                                                                                         | 107 |

|      | 5.4.1 LFO INTEFICIE                                                                                         | 107 |

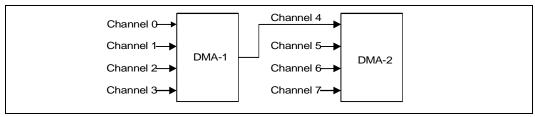

| 5.5  | DMA Operation (D31:F0)                                                                                      | 112 |

|      | 5.5.1 Channel Priority                                                                                      | 113 |

|      | 5.5.2Address Compatibility Mode5.5.3Summary of DMA Transfer Sizes                                           | 112 |

|      | 5.5.2 Address compatibility mode                                                                            | 113 |

|      | 5.5.3 Summary of DMA Transfer Sizes                                                                         | 114 |

|      | 5.5.4 Autoinitialize                                                                                        | 114 |

|      | 5.5.5 Software Commands                                                                                     | 115 |

|      | 5.5.5 Software commands                                                                                     | 115 |

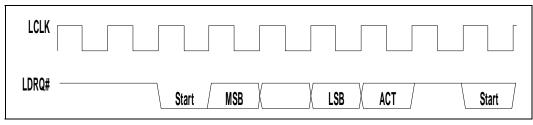

| 5.6  | LPC DMA                                                                                                     | 115 |

|      | 5.6.1 Asserting DMA Requests                                                                                | 115 |

|      | 5.4.2 Abordon DMA Dervosta                                                                                  | 117 |

|      | 5.6.2 Abandoning DMA Requests                                                                               | 110 |

|      | 5.6.2Abandoning DMA Requests5.6.3General Flow of DMA Transfers                                              | 116 |

|      | 5.6.4 Terminal Count                                                                                        | 116 |

|      | 5.0.4 Terminal Count.                                                                                       |     |

|      | 5.6.5 Verify Mode                                                                                           | 117 |

|      | 5.6.6 DMA Request Deassertion                                                                               | 117 |

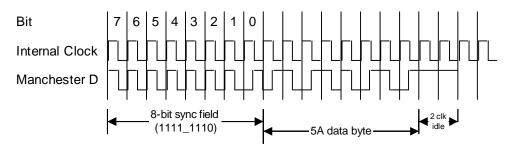

|      | 5.6.7 SYNC Field / LDRQ# Rules                                                                              | 110 |

|      | 5.6.7 STNC FIELD / LDRU# Rules                                                                              | 110 |

| 5.7  | 8254 Timers (D31:F0)                                                                                        | 118 |

|      | 5.7.1 Timer Programming                                                                                     | 119 |

|      | 5.7.2 Deciding from the later of Timer                                                                      | 100 |

| _    | 5.7.2 Reading from the Interval Timer                                                                       | 120 |

| 5.8  | 8259 Interrupt Controllers (PIC) (D31:F0)                                                                   | 121 |

|      | 5.8.1 Interrupt Handling                                                                                    | 122 |

|      | 5.0.1 Interrupt funding                                                                                     | 100 |

|      | 5.8.2 Initialization Command Words (ICWx)                                                                   | 123 |

|      | 5.8.3 Operation Command Words (OCW)                                                                         | 124 |

|      | 5.8.4 Modes of Operation                                                                                    | 12/ |

|      |                                                                                                             | 124 |

|      | 5.8.5 Masking Interrupts                                                                                    | 127 |

|      | 5.8.6 Steering PCI Interrupts<br>Advanced Programmable Interrupt Controller (APIC) (D31:F0)                 | 127 |

| 5.9  | Advanced Programmable Interrupt Controller (APIC) (D21-EQ)                                                  | 170 |

| 5.9  | Advanced Flogrammable Interrupt Controller (AFIC) (DS1.FO)                                                  | 120 |

|      | 5.9.1 Interrupt Handling                                                                                    | 128 |

|      | 5.9.2 Interrupt Mapping                                                                                     | 128 |

|      | 5.9.3 PCI / PCI Express* Message-Based Interrupts                                                           | 120 |

|      | 5.9.5 PCI / PCI Express Message-based Interrupts                                                            | 129 |

|      | 5.9.4 Front Side Bus Interrupt Delivery                                                                     | 129 |

|      | 5.9.5 IOVAPIC Address Remanning                                                                             | 131 |

|      | 5.0 / External Interview Control In Summert                                                                 | 101 |

|      | 5.9.6 External Interrupt Controller Support                                                                 | 131 |

| 5.10 | 5.9.5 IOxAPIC Address Remapping<br>5.9.6 External Interrupt Controller Support<br>Serial Interrupt (D31:F0) | 132 |

|      | 5.10.1 Start Frame                                                                                          | 122 |

|      | 5.10.1 Start Halle                                                                                          | 102 |

|      | 5.10.2 Data Frames                                                                                          | 133 |

|      | <ul><li>5.10.3 Stop Frame</li><li>5.10.4 Specific Interrupts Not Supported via SERIRQ</li></ul>             | 133 |

|      | 5 10.4 Specific Interrupts Not Supported via SERIPO                                                         | 122 |

|      | 5.10.4 Specific Interrupts for Supported Via SERING.                                                        | 100 |

|      | 5.10.5 Data Frame Format                                                                                    | 134 |

| 5.11 | Real Time Clock (D31:F0)                                                                                    | 135 |

| 0    | E 11 1 Undate Cycles                                                                                        | 125 |

|      | 5.11.1 Update Cycles                                                                                        | 130 |

|      | 5.11.2 Interrupts                                                                                           | 136 |

|      | 5.11.3 Lockable RAM Ranges                                                                                  | 136 |

|      | 5 11 4 Contury Pollovor                                                                                     | 124 |

|      | 5.11.4 Century Rollover                                                                                     | 130 |

|      | 5.11.4 Century Rollover<br>5.11.5 Clearing Battery-Backed RTC RAM                                           | 136 |

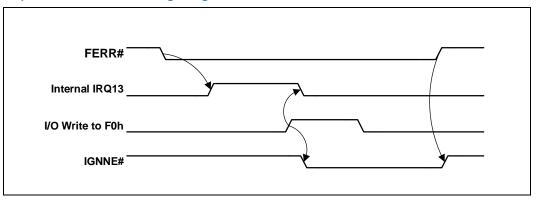

| 5.12 | Processor Interface (D31:F0)                                                                                | 138 |

|      | 5.12.1 Processor Interface Signals                                                                          | 120 |

|      |                                                                                                             | 130 |

|      | 5.12.2 Dual-Processor Issues                                                                                | 141 |

| 5.13 | Power Management (D31:F0)                                                                                   | 142 |

| 0.10 |                                                                                                             |     |

|      | 5.13.1 Features                                                                                             | 142 |

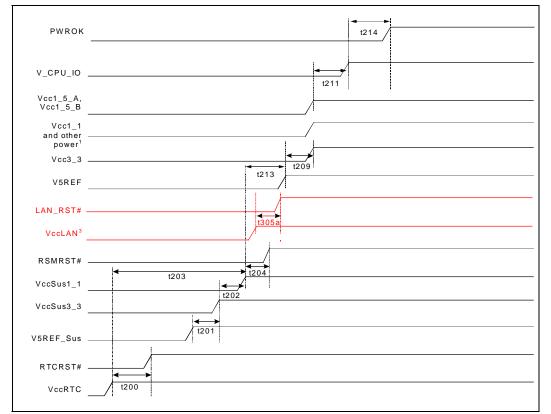

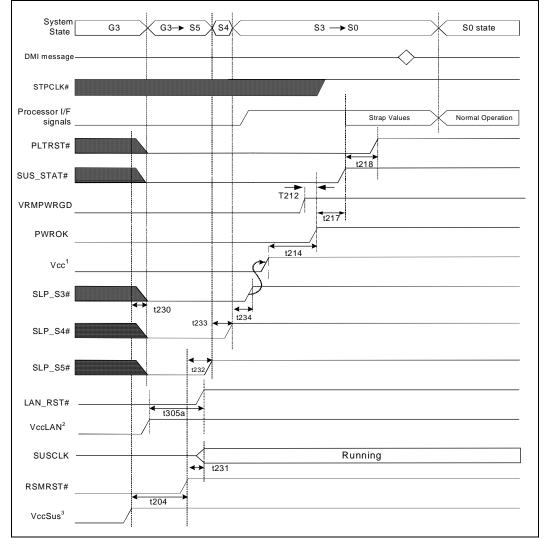

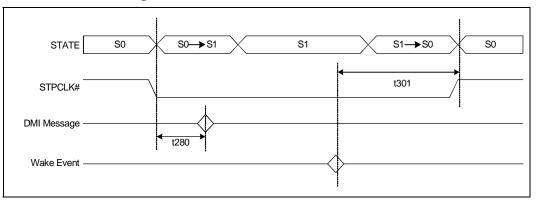

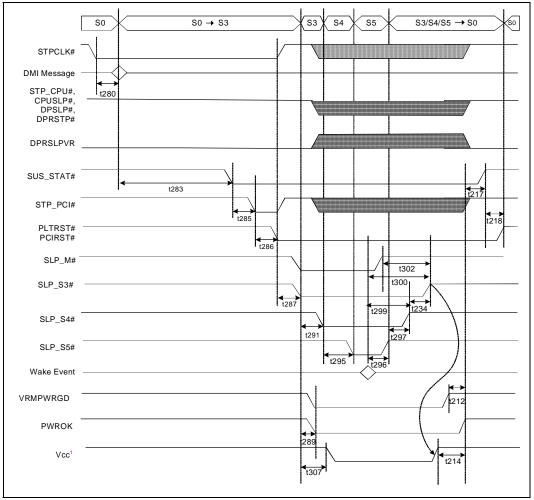

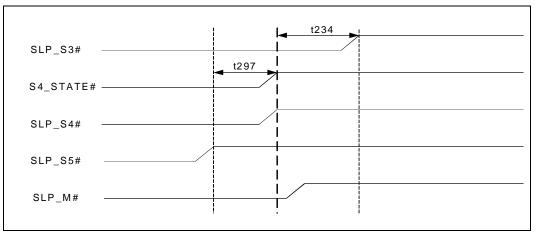

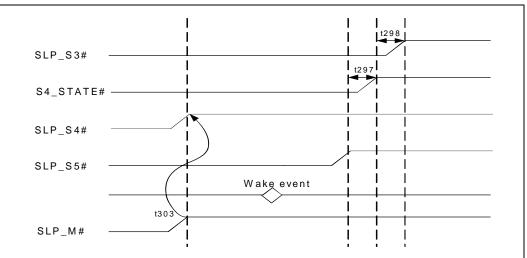

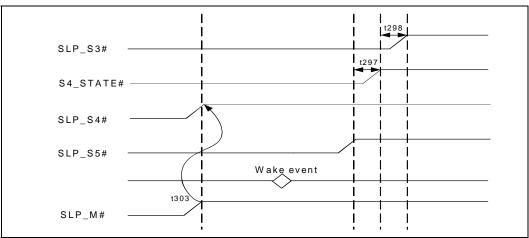

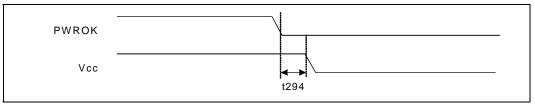

|      | 5.13.2 Intel <sup>®</sup> ICH10 and System Power States                                                     | 142 |

|      | 5.13.3 System Power Planes                                                                                  | 145 |

|      |                                                                                                             |     |

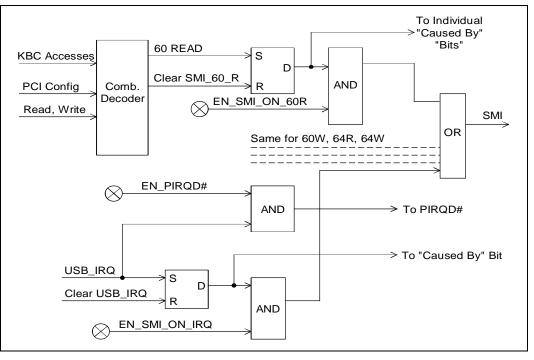

|      | 5.13.4 SMI#/SCI Generation                                                                                  |     |

|      | 5.13.5 Dynamic Processor Clock Control                                                                      | 148 |

|      | 5.13.6 Sleep States                                                                                         |     |

|      | 5.13.0 Sicep States                                                                                         |     |

|      | 5.13.7 Thermal Management                                                                                   | 154 |

|      | 5.13.8 Event Input Signals and Their Usage                                                                  | 155 |

|      | 5.13.9 ALT Access Mode                                                                                      |     |

|      | 5.10.7 ALL ACCESS MODE                                                                                      | 1/0 |

|      | 5.13.10 System Power Supplies, Planes, and Signals                                                          | 162 |

|      | 5.13.11 Clock Generators                                                                                    | 164 |

|      | 5.13.12 Legacy Power Management Theory of Operation                                                         | 165 |

|      |                                                                                                             |     |

|      | 5.13.13 Reset Behavior                                                                                      | 165 |

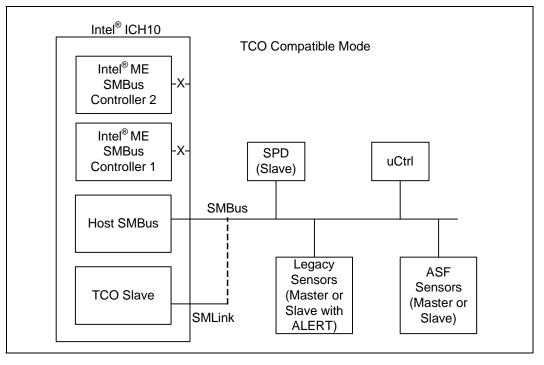

| 5.14 | System Management (D31:F0)                                                                                  | 167 |

|      | 5.14.1 Theory of Operation                                                                                  | 167 |

|      |                                                                                                             | 107 |

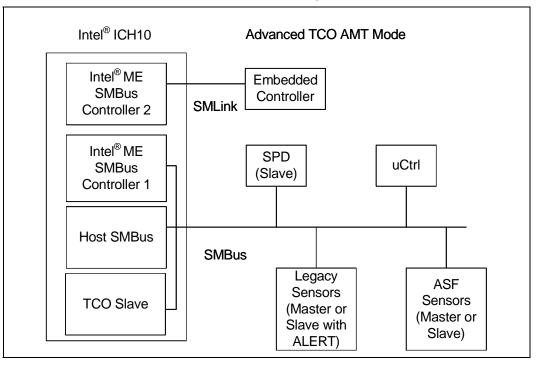

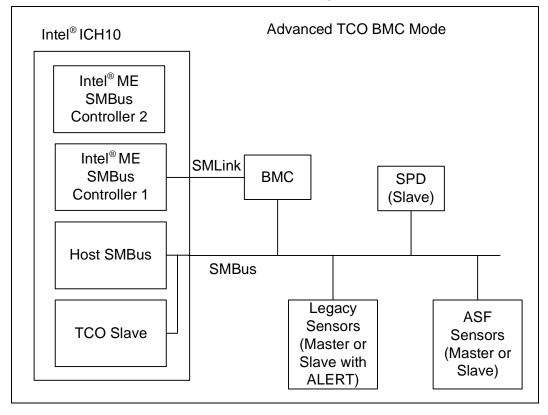

|      | 5.14.2 TCO Modes                                                                                            | 169 |

| 5.15 | General Purpose I/O (D31:F0)                                                                                | 173 |

|      |                                                                                                             |     |

|      | 5.15.1 Power Wells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 173 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | 5.15.2 SMI# and SCI Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 173 |

|      | E 15.2 Similar and Ser Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 170 |

|      | 5.15.3 Triggering<br>5.15.4 GPIO Registers Lockdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 173 |

|      | 5.15.4 GPIU Registers Lockdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1/3 |

|      | 5.15.5 Serial POST Codes Over GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 174 |

|      | 5 15 6 Intel Management Engine GPIOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 176 |

| 5.16 | SATA Host Controller (D31:F2, F5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 176 |

| 5.10 | E 1 ( 1 CATA Footure Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 170 |

|      | 5.10.1 SATA Feature Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1// |

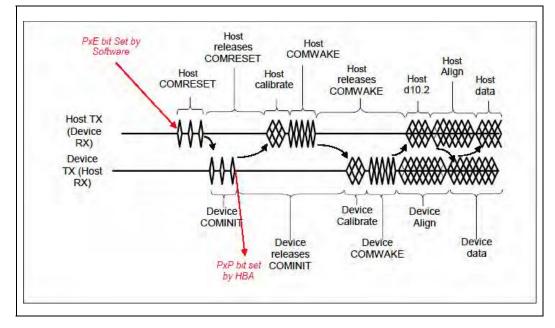

|      | 5.16.2 Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 178 |

|      | 5.16.2 Theory of Operation<br>5.16.3 SATA Swap Bay Support<br>5.16.4 Hot Plug Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 178 |

|      | 5.16.4 Hot Plug Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 178 |

|      | 5.16.5 Eurotion Lovel Poset Support (ELP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 170 |

|      | 5.10.5 Tuttel® Matche Charge Table a land a second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1/7 |

|      | 5.16.6 Intel <sup>®</sup> Matrix Storage Technology Configuration<br>5.16.7 Power Management Operation<br>5.16.8 SATA Device Presence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 180 |

|      | 5.16.7 Power Management Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 181 |

|      | 5.16.8 SATA Device Presence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 183 |

|      | 5.16.9 SATA LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 184 |

|      | 5.16.7 SATA LED operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101 |

|      | 5. To. TOAHCI Operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 184 |

|      | 5.16.10AHCI Operation<br>5.16.11Serial ATA Reference Clock Low Power Request (SATACLKREQ#)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 184 |

|      | 5.16.12SGPIO Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 185 |

|      | 5.16.13External ŠATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 189 |

| 5.17 | High Precision Event Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 120 |

| 5.17 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107 |

|      | 5.17.1 Timer Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 189 |

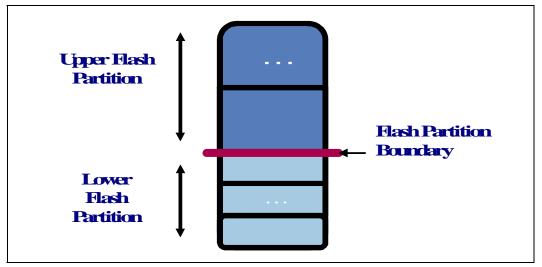

|      | 5.17.2 Interrupt Mapping<br>5.17.3 Periodic vs. Non-Periodic Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 190 |