## Programming Guide

# Intel® Microarchitecture Codename Nehalem Performance Monitoring Unit Programming Guide (Nehalem Core PMU)

## Table of Contents

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| 1. About this document.....                                               | 8  |

| 2. Nehalem-based PMU Architecture.....                                    | 9  |

| 3. The Nehalem Core PMU.....                                              | 11 |

| 3.1. Global Control and Status Registers .....                            | 13 |

| 3.1.1. IA32_PERF_CAPABILITIES.....                                        | 13 |

| 3.1.2. IA32_DEBUGCTL.....                                                 | 15 |

| 3.1.3. IA32_PERF_GLOBAL_CTRL.....                                         | 17 |

| 3.1.4. IA32_PERF_GLOBAL_STATUS.....                                       | 19 |

| 3.1.5. IA32_PERF_GLOBAL_OVF_CTRL.....                                     | 20 |

| 3.1.6. IA32_FIXED_CTR_CTRL .....                                          | 22 |

| 3.2. Programmable Counter Control Registers .....                         | 24 |

| 3.2.1. PerfEvtSelX .....                                                  | 24 |

| 3.3. Counter Registers.....                                               | 27 |

| 3.3.1. PERF_FIXED_CTRX and IA32_PMCX Registers.....                       | 27 |

| 3.4. Off-core Response Event Programming.....                             | 28 |

| 3.5. The PEBS Facility .....                                              | 32 |

| 3.5.1. IA32_PEBS_ENABLE .....                                             | 32 |

| 3.5.2. PEBS Record Format.....                                            | 34 |

| 3.5.3. Programming the PEBS Facility.....                                 | 35 |

| 3.6. Counter Prioritization.....                                          | 38 |

| 3.7. The Load Latency Facility.....                                       | 39 |

| 3.8. The Last Branch Record Facility.....                                 | 43 |

| 3.8.1. LBR Filtering.....                                                 | 44 |

| 3.8.2. Storing Branch Trace Messages in the Branch Trace Store.....       | 45 |

| 3.8.3. Storing Branch Trace Messages in the Last Branch Record Stack..... | 47 |

| 3.9. The RDPMC Instruction .....                                          | 50 |

| 4. Detecting the Nehalem Processor .....                                  | 52 |

| 4.1. CPUID identification.....                                            | 52 |

| 4.2. Architectural PerfMon .....                                          | 52 |

| 4.3. Other Considerations.....                                            | 54 |

## List of Figures

|                                                                        |           |

|------------------------------------------------------------------------|-----------|

| <b>Figure 1: IA32_PERF_CAPABILITIES MSR Definition</b>                 | <b>13</b> |

| <b>Figure 2: IA32_DEBUGCTL MSR Definition</b>                          | <b>15</b> |

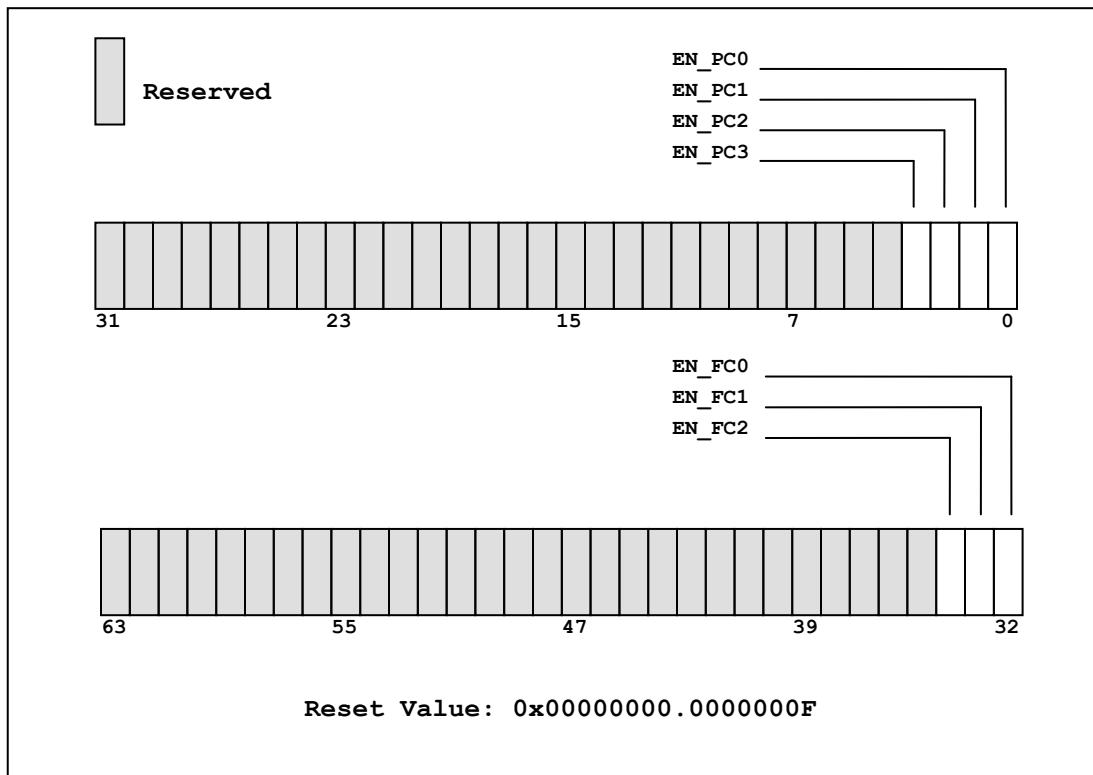

| <b>Figure 3: IA32_PERF_GLOBAL_CTRL MSR Definition</b>                  | <b>18</b> |

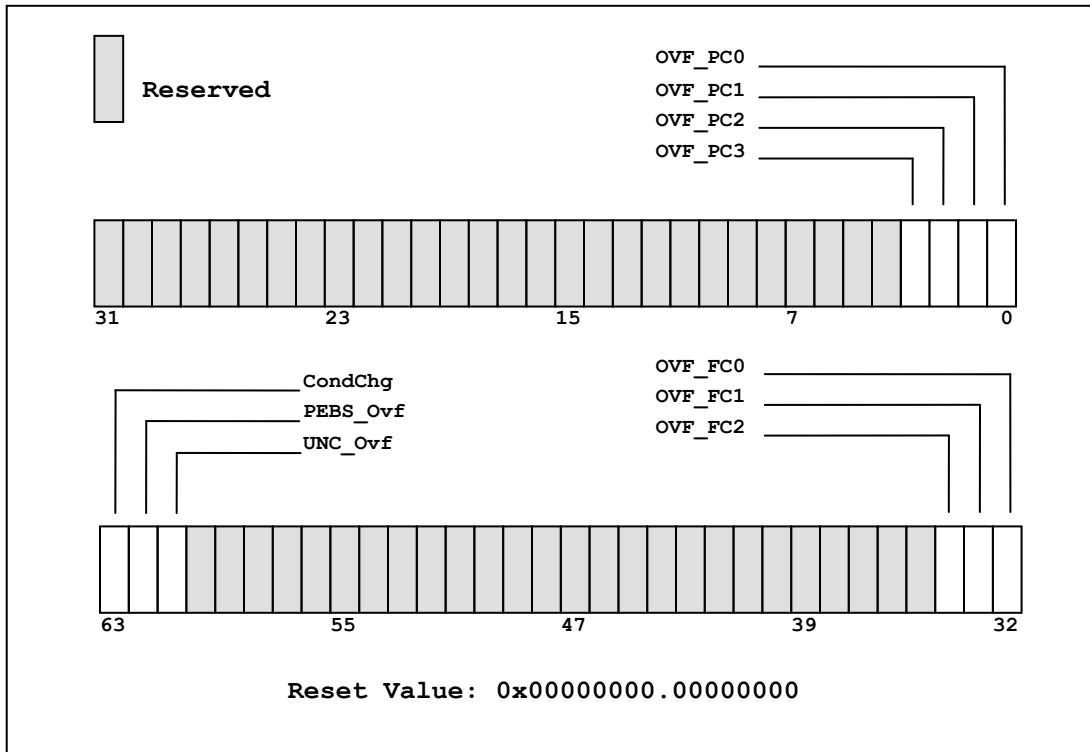

| <b>Figure 4: IA32_PERF_GLOBAL_STATUS MSR Definition</b>                | <b>19</b> |

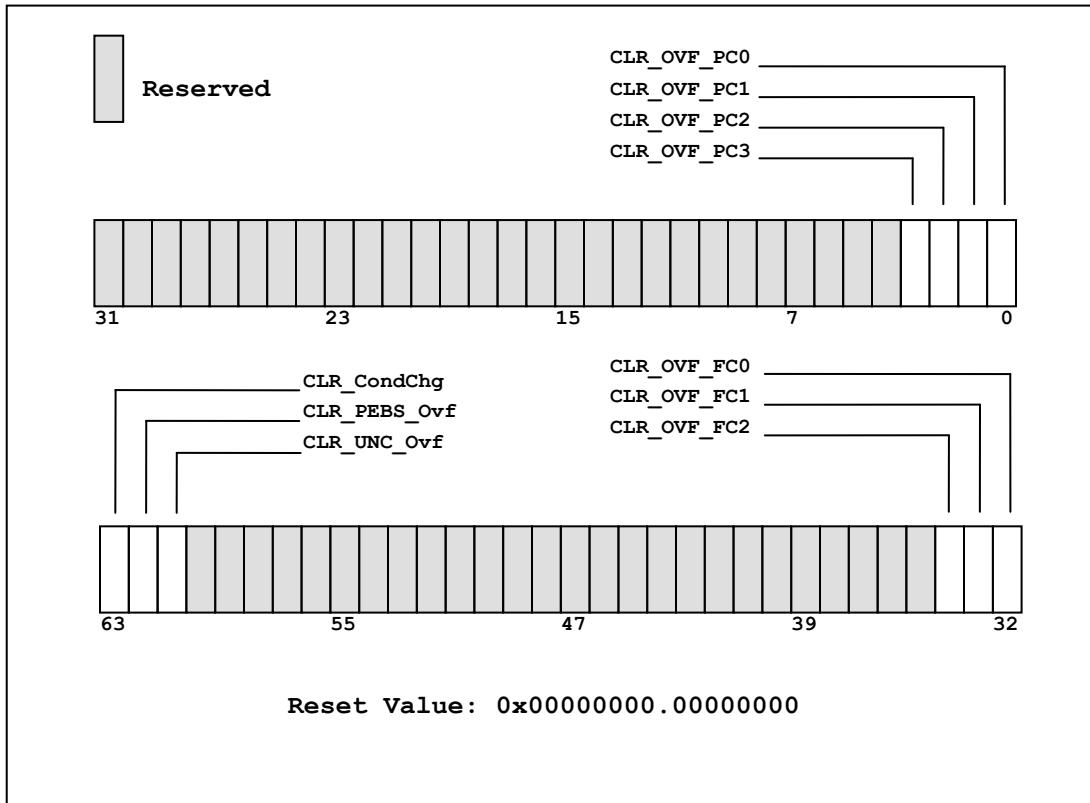

| <b>Figure 5: IA32_PERF_GLOBAL_OVF_CTRL MSR Definition</b>              | <b>21</b> |

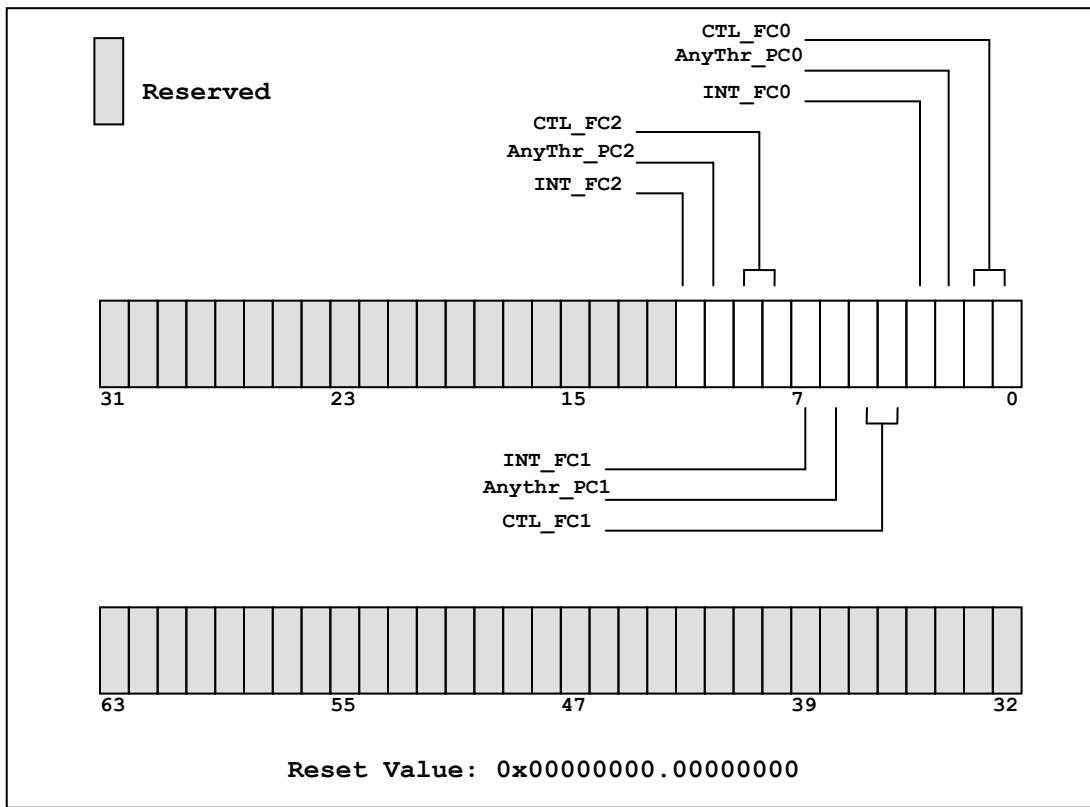

| <b>Figure 6: IA32_FIXED_CTR_CTRL MSR Definition</b>                    | <b>23</b> |

| <b>Figure 7: PerfEvtSelX MSR Definition</b>                            | <b>25</b> |

| <b>Figure 8: PERF_FIXED_CTRX and IA32_PMCX MSR Definition</b>          | <b>27</b> |

| <b>Figure 9: OFFCORE_RSP_X MSR Definition</b>                          | <b>29</b> |

| <b>Figure 10: IA32_PEBS_ENABLE MSR Definition</b>                      | <b>33</b> |

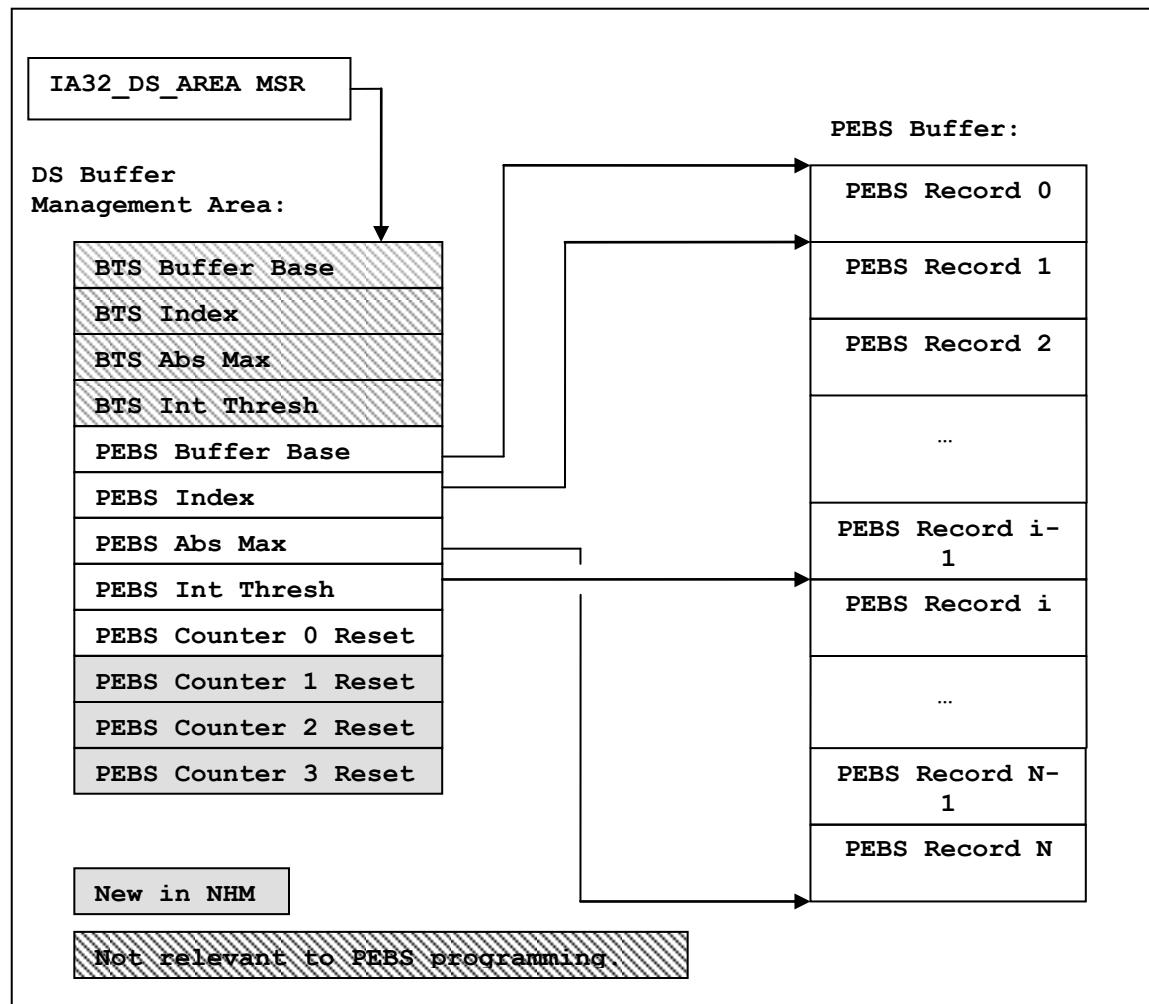

| <b>Figure 11: PEBS Programming Overview</b>                            | <b>36</b> |

| <b>Figure 12: IA32_DS_AREA MSR Definition</b>                          | <b>38</b> |

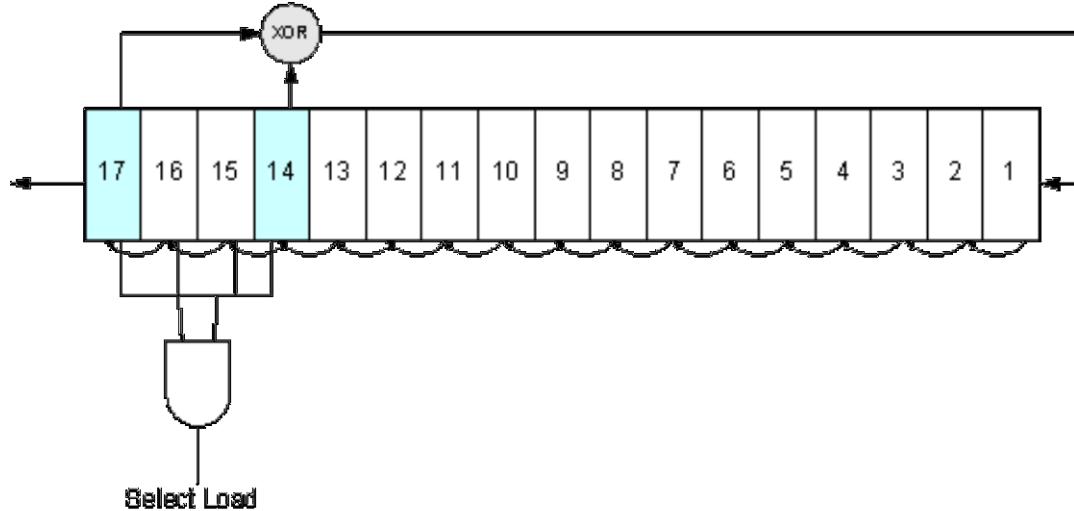

| <b>Figure 13: LFSR for Tagging Memory Load Instructions</b>            | <b>40</b> |

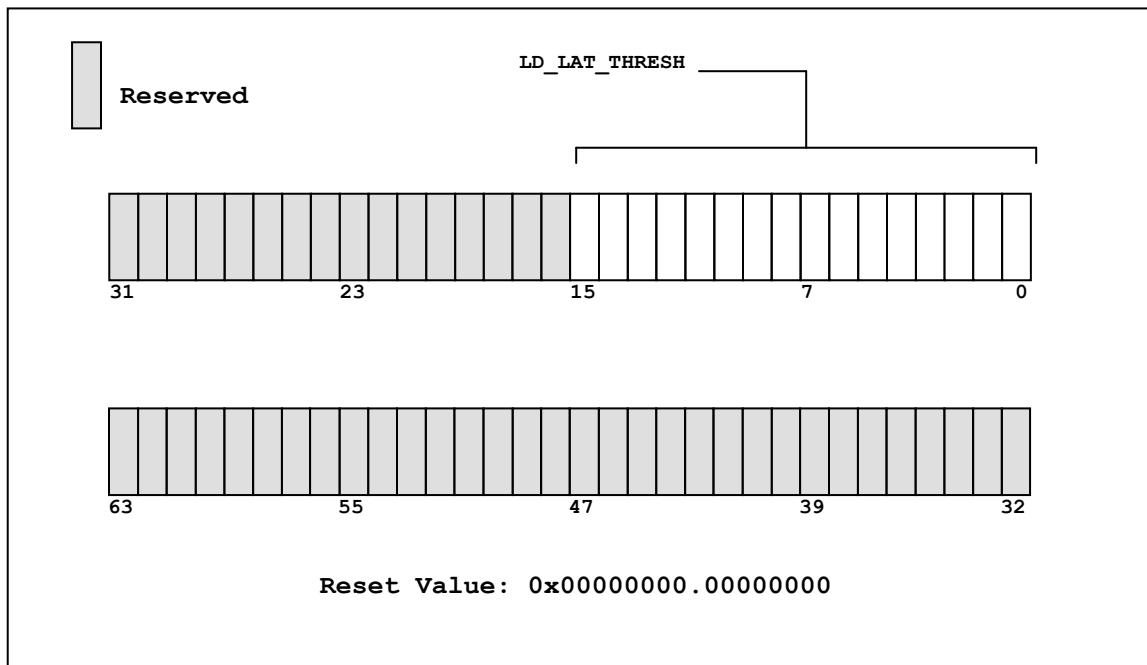

| <b>Figure 14: PEBS_LD_LAT_THRESHOLD MSR Definition</b>                 | <b>42</b> |

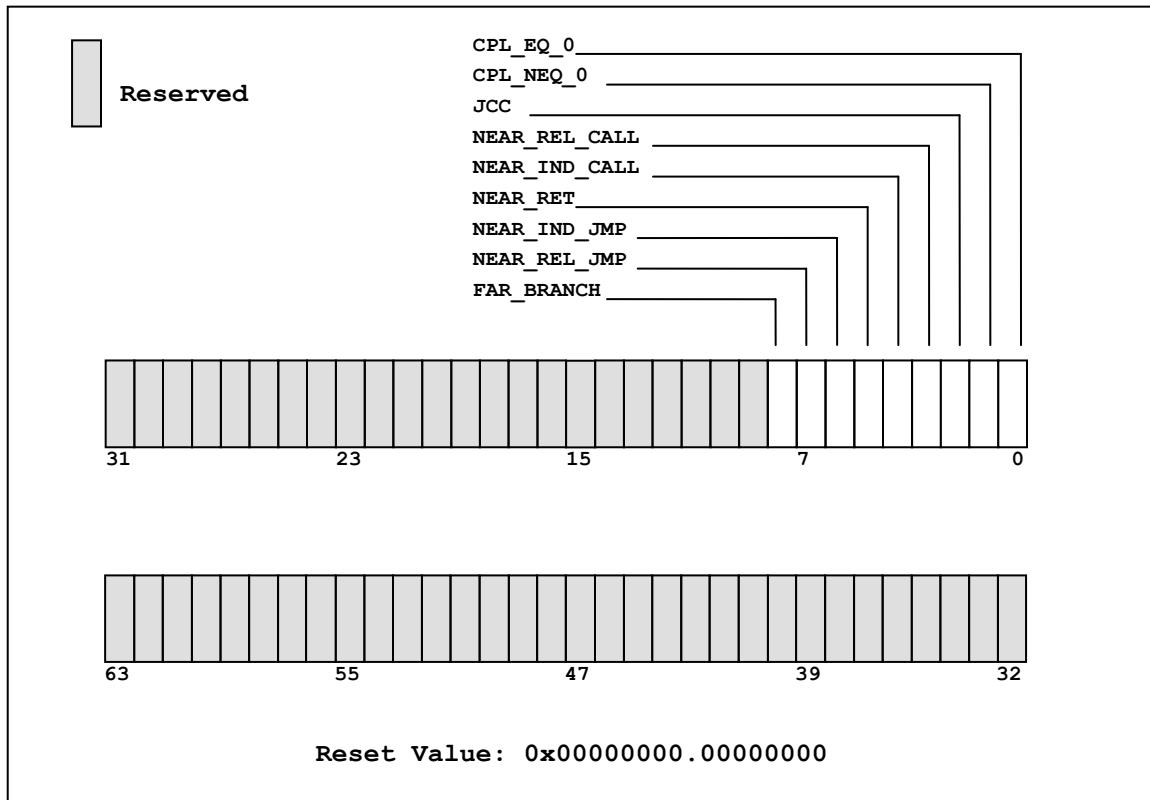

| <b>Figure 15: LBR_SELECT MSR Programming</b>                           | <b>44</b> |

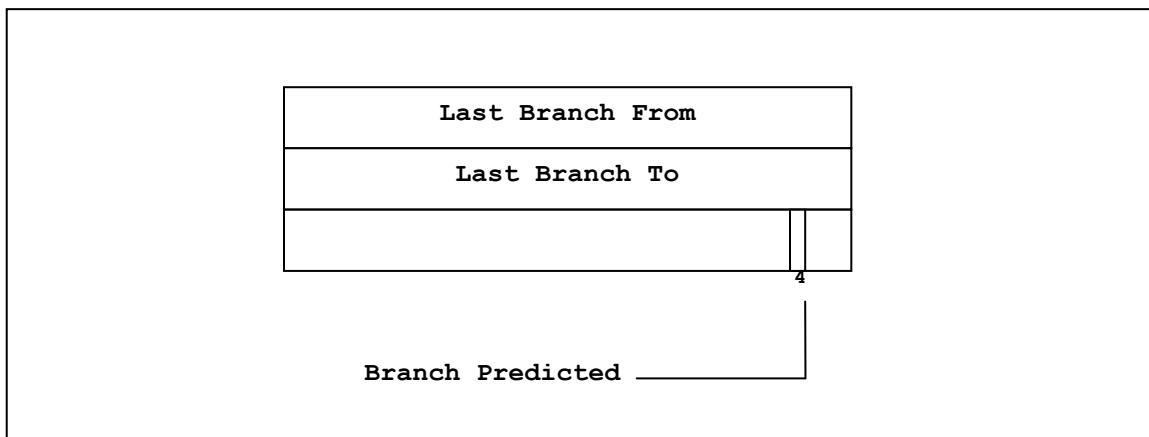

| <b>Figure 16: Format of Branch Trace Message in Branch Trace Store</b> | <b>45</b> |

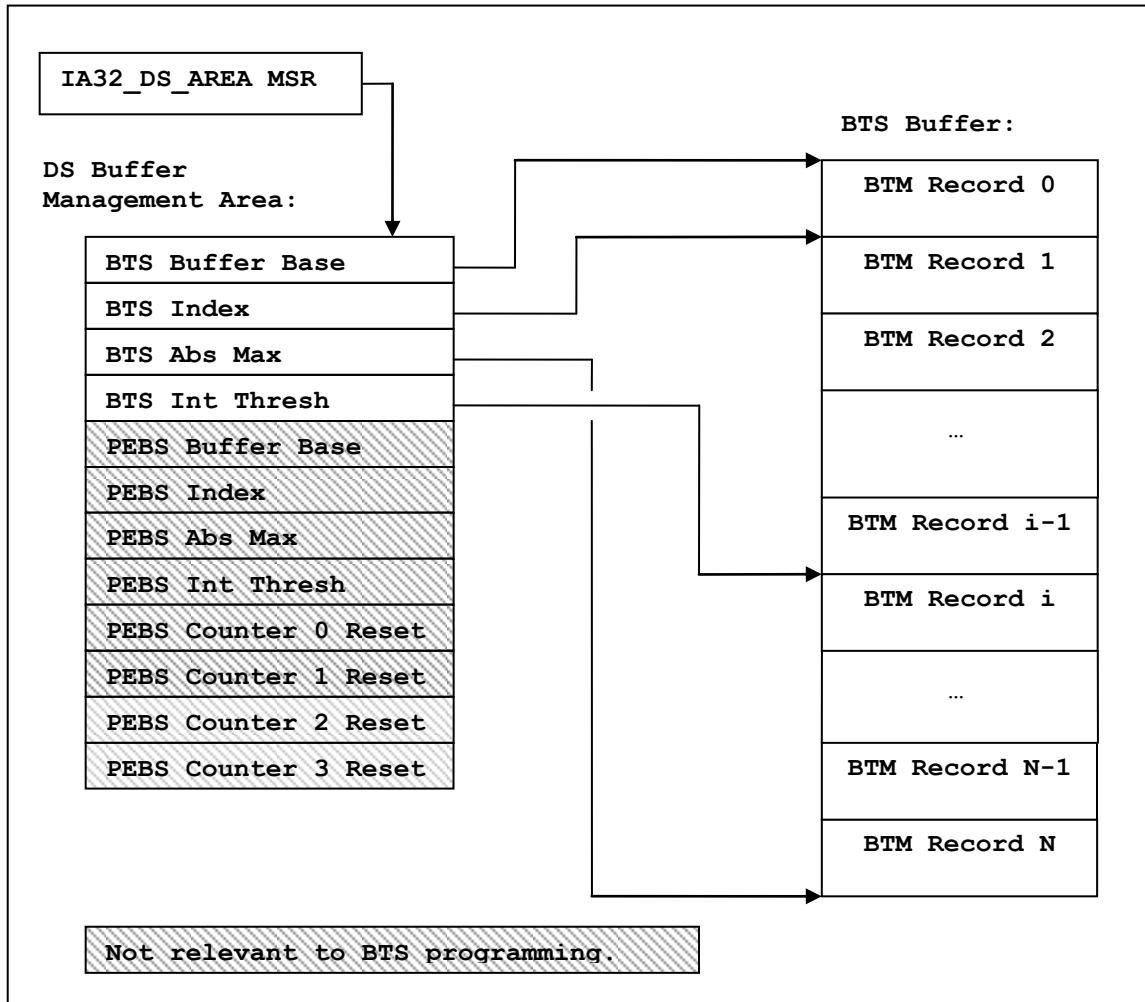

| <b>Figure 17: Branch Trace Store Programming Overview</b>              | <b>47</b> |

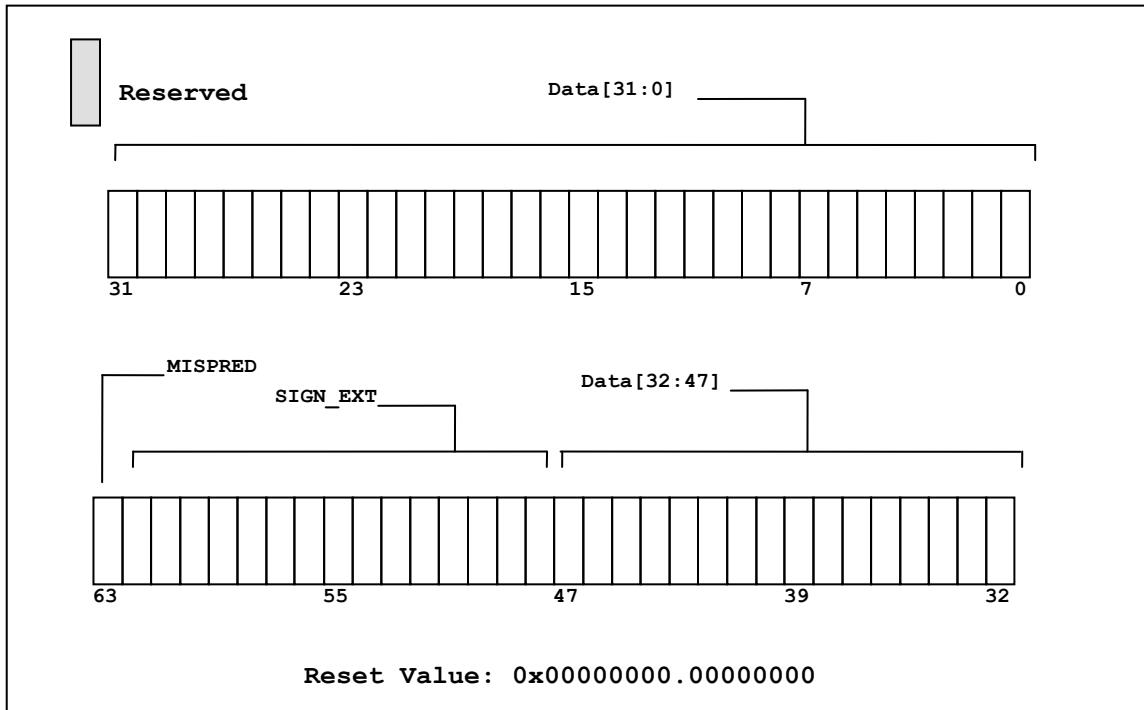

| <b>Figure 18: MSR_LASTBRANCH_x_FROM_IP MSR Definition</b>              | <b>48</b> |

| <b>Figure 19: MSR_LASTBRANCH_x_TO_IP MSR Definition</b>                | <b>49</b> |

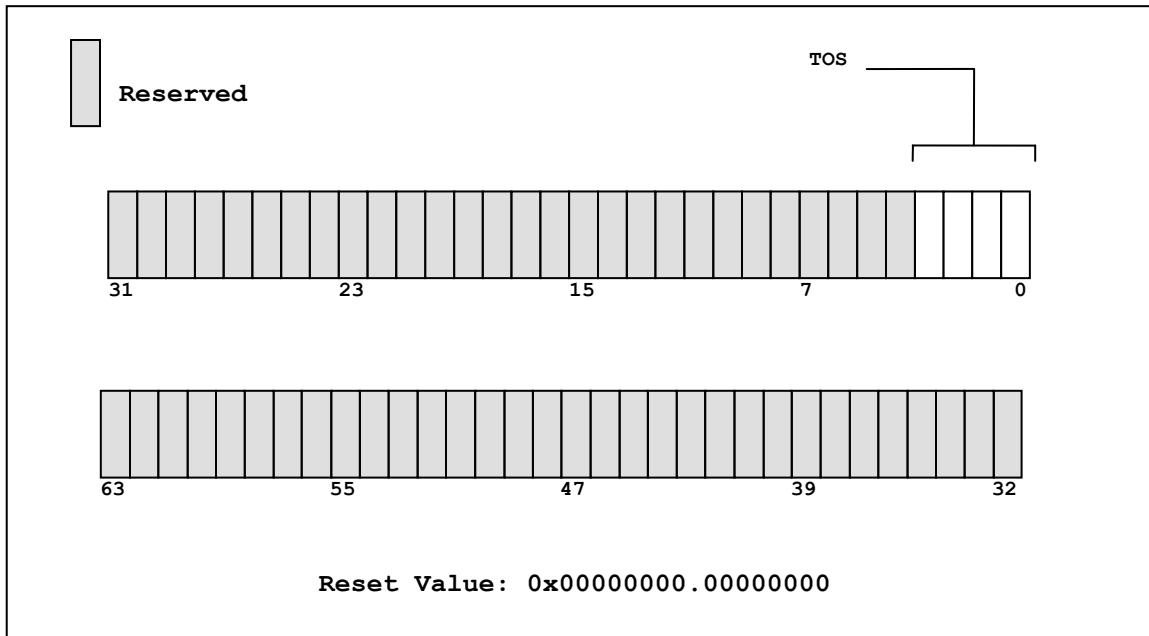

| <b>Figure 20: MSR_LASTBRANCH_TOS MSR Definition</b>                    | <b>50</b> |

## List of Tables

|                                                                              |    |

|------------------------------------------------------------------------------|----|

| Table 1: List of Terms.....                                                  | 5  |

| Table 2: Performance Monitoring Architecture Comparison.....                 | 11 |

| Table 3: IA32_PERF_CAPABILITIES Programming .....                            | 13 |

| Table 4: IA32_DEBUGCTL Programming.....                                      | 15 |

| Table 5: IA32_PERF_GLOBAL_CTRL Programming .....                             | 18 |

| Table 6: IA32_PERF_GLOBAL_STATUS Programming .....                           | 19 |

| Table 7: IA32_PERF_GLOBAL_OVF_CTRL Programming .....                         | 21 |

| Table 8: IA32_FIXED_CTR_CTRL Programming.....                                | 23 |

| Table 9: Summary of CTL bit Programming for Fixed Counters .....             | 24 |

| Table 10: PerfEvtSelX Programming .....                                      | 25 |

| Table 11: Offcore Response Events Encoding .....                             | 28 |

| Table 12: OFFCORE_RSP_X Event Programming .....                              | 29 |

| Table 13: Offcore Response Programming Example .....                         | 31 |

| Table 14: IA32_PEBS_ENABLE Programming .....                                 | 33 |

| Table 15: PEBS Record Format.....                                            | 34 |

| Table 16: Data Souce Encodings in Load Latency Records.....                  | 41 |

| Table 17: PEBS_LD_LAT_THRESHOLD Programming.....                             | 42 |

| Table 18: Programming the BTS Facility .....                                 | 43 |

| Table 19: LBR_SELECT Programming.....                                        | 45 |

| Table 20: MSR_LASTBRANCH_x_FROM_IP Programming .....                         | 48 |

| Table 21: MSR_LASTBRANCH_x_TO_IP Programming .....                           | 49 |

| Table 22: MSR_LASTBRANCH_TOS Programming .....                               | 50 |

| Table 23: Legal Index (ECX) Values for Executing the RDPMC Instruction ..... | 51 |

| Table 38: Nehalem CPUID Processor Signatures .....                           | 52 |

| Table 39: CPUID.A Information.....                                           | 53 |

| Table 40: NHM Core PMU Register List.....                                    | 57 |

## Preface

This document contains advance information. While every effort has been made to ensure the accuracy of the information contained herein, some errors may occur. Please contact [thomas.m.johnson@intel.com](mailto:thomas.m.johnson@intel.com) if you have questions or comments.

This document describes the programming interface to the performance monitoring hardware on the Nehalem processor core. This document does not exhaustively describe all of the performance monitoring events which may be counted in the Nehalem. A detailed description of these events may be released separately.

## Terms

Table 1: List of Terms

| Term  | Definition                                                                                                                                                                                                                                       |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BTM   | Branch Trace Message. A message sent on the system bus which external hardware can capture and thereby develop a reconstruction of program control flow.                                                                                         |

| BTS   | Branch Trace Store. A memory buffer containing a collection of branch trace messages.                                                                                                                                                            |

| Clear | In reference to register programming, this means a bit is programmed to binary zero (0).                                                                                                                                                         |

| CPL   | Current Privilege Level. The current privilege level at which the processor is executing (Ring 0, 1, 2, or 3).                                                                                                                                   |

| DCU   | Data cache. The cache closest to the processor core. This cache provides data to the core with the minimum latency.                                                                                                                              |

| EBS   | Event Based Sampling. A technique in which counters are pre-loaded with a large negative count, and they are configured to interrupt the processor on overflow. When the counter overflows the interrupt service routine capture profiling data. |

| GO    | Globally Observable. The point in time at which data in the machine is architecturally observable.                                                                                                                                               |

| GP    | General Protection (fault).                                                                                                                                                                                                                      |

| ISR   | Interrupt Service Routine.                                                                                                                                                                                                                       |

| LBR   | Last Branch Record. A facility which provides branch trace information either through special bus cycles on the system bus, or through records written to a user defined                                                                         |

|                                        |                                                                                                                                                                                                                                                                                                            |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | memory buffer (the BTS).                                                                                                                                                                                                                                                                                   |

| LLC                                    | Last-level cache. The lowest level of cache, after which memory requests must be satisfied by system memory.                                                                                                                                                                                               |

| MLC                                    | Mid-level cache. This is the intermediate level cache which lies between the DCU and LLC.                                                                                                                                                                                                                  |

| MSR                                    | Model Specific Register. PMU counter and counter control registers are implemented as MSR registers. They are accessed via the <code>rdmsr</code> and <code>wrmsr</code> instruction. Certain counter registers can be accessed via the <code>rdpmc</code> instruction.                                    |

| NHM                                    | Nehalem. Specifically the Nehalem processor core.                                                                                                                                                                                                                                                          |

| PEBS                                   | Precise Event Based Sampling. A special counting mode in which counters can be configured to overflow, interrupt the processor, and capture machine state at that point.                                                                                                                                   |

| PerfMon                                | Short for Performance Monitoring                                                                                                                                                                                                                                                                           |

| PMI                                    | Performance Monitoring Interrupt. This interrupt is generated when a counter overflows and has been programmed to generate an interrupt, or when the PEBS interrupt threshold has been reached.<br>The interrupt vector for this interrupt is controlled through the Local Vector Table in the Local APIC. |

| PMU                                    | Performance Monitoring Unit                                                                                                                                                                                                                                                                                |

| RFO                                    | Read for ownership. When a cache line is written that misses in the cache, it must first be read into the cache so that the line exists in cache and can then be modified.                                                                                                                                 |

| RO                                     | A bit is read-only.                                                                                                                                                                                                                                                                                        |

| RW                                     | A bit is readable and writeable.                                                                                                                                                                                                                                                                           |

| Set                                    | In reference to register programming, this means a bit is programmed to binary one (1).                                                                                                                                                                                                                    |

| SMM                                    | System Management Mode.                                                                                                                                                                                                                                                                                    |

| SMT                                    | Simultaneous Multi-threading.                                                                                                                                                                                                                                                                              |

| Supervisor (SUP), or privilege level 0 | Supervisor state is the most privileged state of execution. Typically operating system code executes in privilege level 0.                                                                                                                                                                                 |

| TBS                                    | Time Based Sampling. A technique in which a time base is used to determine when to capture profiling data. This                                                                                                                                                                                            |

|                                           |                                                                                                                                                                                                                                                                                    |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | time base can be a timer interrupt or the occurrence of a certain number of other events, such clock ticks or instructions retired.                                                                                                                                                |

| Thread                                    | A hardware thread of execution. In other words, Hyper-Threading Technology.                                                                                                                                                                                                        |

| Uop                                       | Micro-operation. Macro instruction are broken down into uops within the machine, and these uops are executed by the execution units.                                                                                                                                               |

| User (USR), or privilege level 1, 2, or 3 | Intel processors operate in privilege levels zero through three, where lower numbered privilege levels operate in a more privileged state. User (or privilege levels 1, 2, or 3) refers to less privileged states of execution. User code typically executes at privilege level 3. |

| W0                                        | A bit is write-only.                                                                                                                                                                                                                                                               |

| W01                                       | A bit is write-only, and should be written to a '1' (set).                                                                                                                                                                                                                         |

## 1. About this document

This is a programmer's reference manual for the Nehalem core performance monitoring units (PMU). This is targeted for current tool owners requiring documentation updates for Nehalem based platforms. It is not intended for first time tool developers or as a user analysis guide. Additional documents will be available at a later date targeted at providing that information.

## 2. Nehalem-based PMU Architecture

Intel processor cores for many years included a Performance Monitoring Unit (PMU). This unit provided the ability to count the occurrence of micro-architectural events which expose some of the inner workings of the processor core as it executes code.

One usage of this capability is to create a list of events from which certain performance metrics can be calculated. Software configures the PMU to count events over an interval of time and report the resulting event counts. Using this methodology, performance analysts can characterize overall system performance.

The PMU also provides facilities to generate a hardware interrupt through the Local APIC integrated within the processor core or logical thread. In this case software can pre-load event counter registers with a "sample after value," in which case a hardware interrupt is generated after the occurrence of N number of events. In the interrupt handler software collects additional architectural state which provides analysts with information regarding the performance of specific areas of application code. This methodology is sometimes referred to as profiling the execution of an application.

Products based on the Nehalem processor core include the capability to collect event data under both of these scenarios. In addition, these products include various platform features (uncore) integrated on the same die as the processor core. The uncore is essentially everything on the processor chip that is not part of the core. This includes point-to-point interconnect logic, memory controllers, and last-level caches, among other things. The uncores also provide an additional PMU facility that has the ability to interrupt the processor core in order that profiling information may be collected. This document describes the Nehalem processor core PMU.

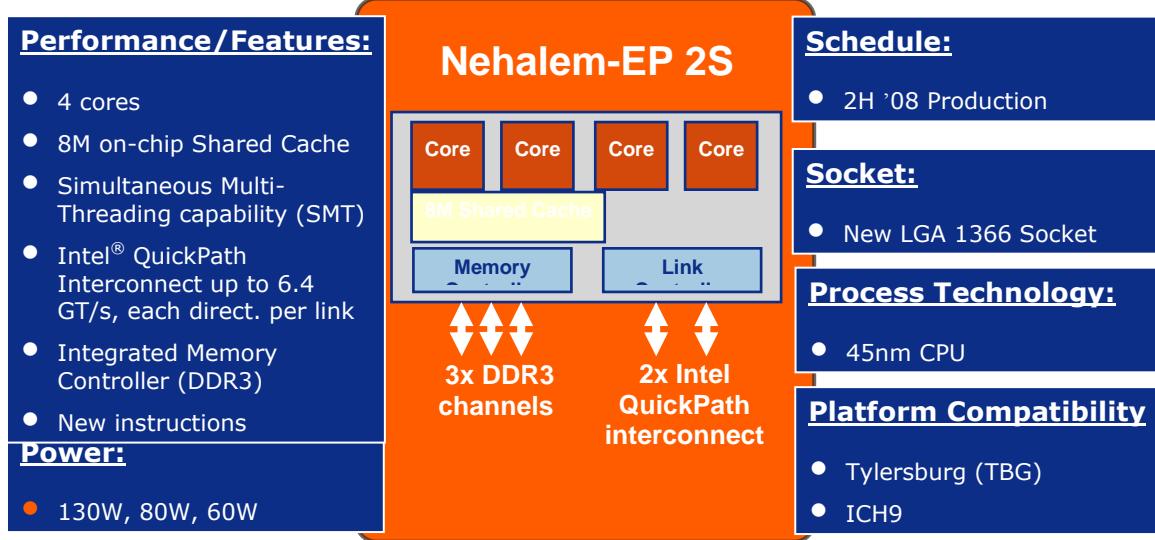

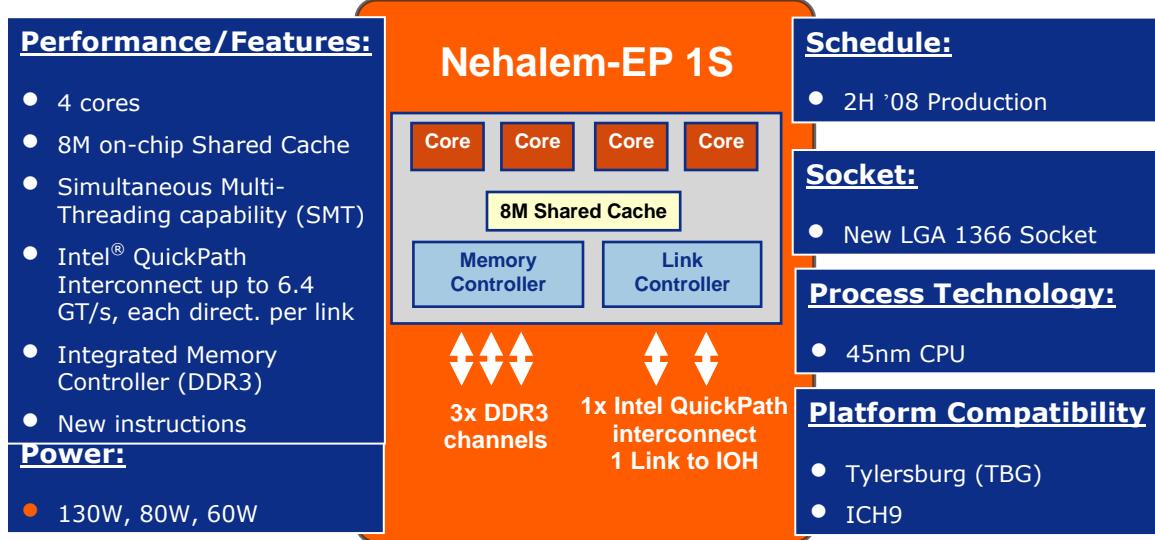

| Platform Name    | Processor     | CPU Core | Processor Code Name | Chipset    |

|------------------|---------------|----------|---------------------|------------|

| Tylersburg-EP 2S | Nehalem-EP 2S | Nehalem  | Gainstwon           | Tylersburg |

| Tylersburg-EP 1S | Nehalem-EP 1S | Nehalem  |                     | Tylersburg |

| Boxboro-EX       | Nehalem-EX    | Nehalem  | Beckton             | Boxboro    |

The PMU differences between Nehalem-EP 2S and Nehalem-EP 1S will solely be reflected in the event list. The programming and architecture list will not differ. Supplemental documentation will be published for Nehalem-EX. Nehalem-EX uncore has a significantly different architecture and therefore programming.

## Nehalem-EP 2S CPU Summary

## Nehalem-EP 1S CPU Summary

### 3. The Nehalem Core PMU

The table below summarizes the differences between the Nehalem core (NHM) PMU features and that of previous products in the Intel® Core™ and Pentium 4® processor families. Nehalem adheres to Architectural Performance Monitoring Version 3.

The table includes architectural and non-architectural features. Architectural features are listed in the top of the table with intercepts highlighted.

Table 2: Performance Monitoring Architecture Comparison

| Feature                                   | Description                                                                                                  | P4                                 | Yonah<br>(V1*) | Merom<br>(V2*) | Penryn<br>(V2*) | Nehalem<br>(V3*)                      |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|-----------------|---------------------------------------|

| Number of General Counters                | Number of general counters per logical CPU.                                                                  | 18                                 | 2              | 2              | 2               | 4                                     |

| Number of Fixed Counters                  | Examples include instructions retired, un-halted core clock ticks, un-halted reference clock ticks, etc.     | 0                                  | 0              | 3              | 3               | 3                                     |

| Number of Selection and Control Registers | Used to select events and configure the general counters.                                                    | 45 ESCR, 18 CCCR                   | 2              | 2              | 2               | 4                                     |

| Architectural Events                      | Architectural events retain a consistent definition and encoding across product implementations.             | 0                                  | 7              | 7              | 7               | 7                                     |

| Global Counter Controls                   | Single MSR to globally enable and disable all counters.                                                      | No                                 | Yes            | Yes            | Yes             | Yes                                   |

| Freeze on Overflow Interrupt              | Ability to freeze (disable) counters on occurrence of overflow interrupt. Freeze occurs before PMI delivery. | No                                 | No             | Yes            | Yes             | Yes                                   |

| VT VMCS                                   | Add global enable MSR to guest and host VMCS.                                                                | No                                 | No             | No             | Yes             | Yes                                   |

| Freeze Counters on SMI                    | Add support for save/disable/restore on SMI.                                                                 | No                                 | No             | No             | Yes             | Yes                                   |

| AnyThread                                 | Enable bit for counting when an event is active across any hardware thread for fixed and general counters.   | Yes<br>Thread specific programming | No             | No             | No              | Yes<br>Thread independent programming |

|                                        |                                                                                                                       |                              |       |                              |                              |                           |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------|-------|------------------------------|------------------------------|---------------------------|

| PEBS                                   | Precise Event Based Sampling. Includes mechanisms to store branch and machine state information on counter overflow.  | Limited to certain counters. | No    | Limited to certain counters. | Limited to certain counters. | Available on any counter. |

| Load Latency                           | A PEBS record extension which allows sampling load instruction latency, load target address, and instruction pointer. | No                           | No    | No                           | No                           | Yes                       |

| Last Branch Record (LBR)               | Circular ring of MSRs which record branch target and source instruction pointers.                                     | 8 LIP                        | 4 EIP | 4 EIP                        | 4 LIP                        | 16 EIP                    |

| Freeze LBR Stack on Overflow Interrupt | Ability to freeze (disable) capture of LBR information on occurrence of overflow interrupt.                           | No                           | No    | Yes                          | Yes                          | Yes                       |

| SMI Counter                            | Free running read-only SMI counters (used like time stamp counter).                                                   | No                           | No    | No                           | No                           | Yes                       |

| Branch Trace Store                     | Branch trace store feature uses LBR MSRs.                                                                             | Yes                          | No    | Yes                          | Yes                          | Yes                       |

\*Denotes the version of Architectural Performance Monitoring supported by this product.

The Nehalem core supports event counting with seven event counters. Three of these counters are fixed function counters; the events counted by each of these counters are fixed in hardware. Software can determine whether counting is enabled during user or supervisor code execution, or both. The four remaining counters are programmable, and can be configured to count a variety of events. There are some restrictions on individual counters. Fixed counters are controlled by bit fields in a global control register. Programmable counters are controlled by a separate control register, one for each counter.

PMU resources are available and must be programmed for each hardware thread (logical processor), if threading is enabled. Otherwise they are programmed for each core. PMU resources available in each thread do not accumulate to the core when hardware threading is disabled. Thus the PMU programming model remains consistent in any case. To successfully program all PMU resources, software must affinize itself to each processor the operating system exposes. Counter registers are 48 bits in extent.

Writing a binary one to any reserved bit in any counter or counter control register is undefined and may cause a general protection fault.

The following sections describe the programming the counter and counter control registers used to program the NHM PMU.

### 3.1. Global Control and Status Registers

There are a set of global control and status registers which control the fixed and programmable counters, and provide status indications of the NHM PMU in general. The following sections describe these global registers.

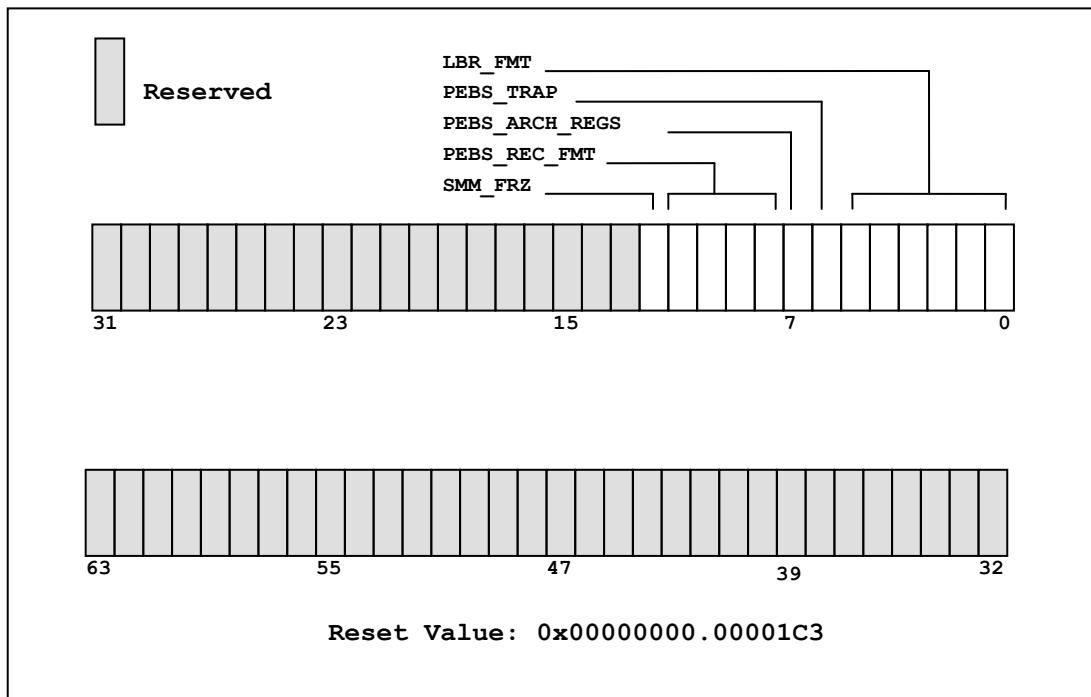

### 3.1.1. IA32\_PERF\_CAPABILITIES

This register provides availability status information regarding the capabilities supported by this implementation of the performance monitoring hardware. This is a read-only register.

Figure 1: IA32\_PERF\_CAPABILITIES MSR Definition

**Table 3: IA32\_PERF\_CAPABILITIES Programming**

| Bit | Bit Position | Access | Description |

|-----|--------------|--------|-------------|

|-----|--------------|--------|-------------|

|               |      |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LBR_FMT       | 5:0  | RO | Branch to/from information contains:<br>00000b: 32-bit offset in current code segment.<br>00001b: 64-bit LIP<br>00010b: 64-bit EIP                                                                                                                                                                                                                                                                                                                                                                   |

| PEBS_TRAP     | 6    | RO | If clear indicates the PEBS assist is trap-like. The assist occurs at the end-of-macro (EOM) instruction boundary after machine state is committed. The PEBS record will reflect the state of the machine after this instruction executed.<br>If set, indicates the PEBS assist is fault-like. The assist will occur before the current instruction retires, and the PEBS record will reflect the pre-retirement state of the machine.<br>See section 3.5.2 for more information on the PEBS record. |

| PEBS_ARCH_REG | 7    | RO | If set, indicates that the PEBS record contains the architectural registers in addition to the return instruction pointer and flags. If clear, only return the instruction pointer and flags are recorded.                                                                                                                                                                                                                                                                                           |

| PEBS_REC_FMT  | 11:8 | RO | 0000b: Only the return instruction pointer, flags, and general purpose registers are recorded in the PEBS record.<br>0001b: In addition to the information contained in option 0 above, the PEBS record contains the global overflow status and load latency information.<br>Other values are reserved.                                                                                                                                                                                              |

| SMM_FRZ       | 12   | RO | If set, indicates this implementation has the ability to freeze the PMU on entry to SMM mode. This means all counters and profiling hardware will be disabled while in SMM mode. Upon exit from SMM mode, normal operation will resume. No freeze capability is supported otherwise.                                                                                                                                                                                                                 |

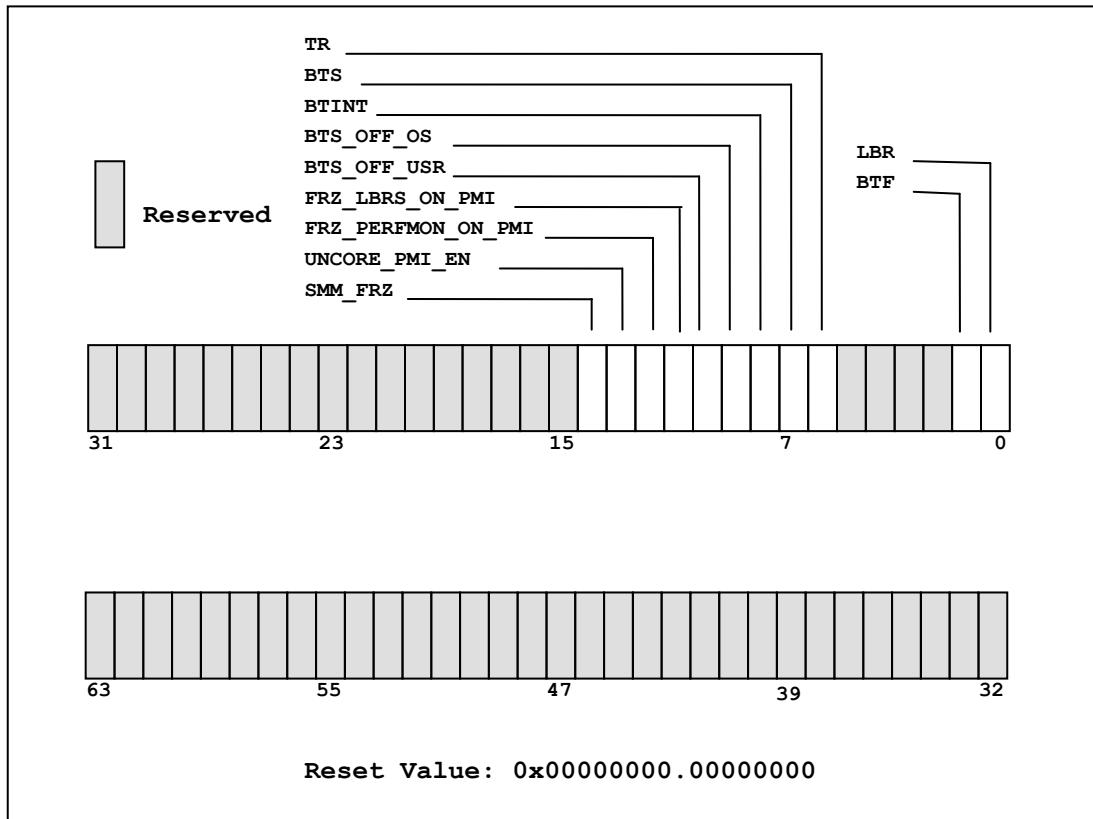

### 3.1.2. IA32\_DEBUGCTL

This register controls tracing, single stepping, and last branch record (LBR) collection, and certain freeze functions related to the PMU. The programming for this register is summarized in the figure and table below.

Figure 2: IA32\_DEBUGCTL MSR Definition

Table 4: IA32\_DEBUGCTL Programming

| Bit | Bit Position | Access | Description                                                                                                                                                                                                                                                                                |

|-----|--------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LBR | 0            | RW     | When set, the processor records a running trace of the most recent branches, interrupts, and exceptions taken by the processor in the LBR stack. Because last branch recording and branch trace messages share common hardware, this bit should not be set at the same time as the TR bit. |

| BTF | 1            | RW     | When set, the processor treats the TF flag in the EFLAGS register                                                                                                                                                                                                                          |

|                    |    |    |  |                                                                                                                                                                                                                                                               |

|--------------------|----|----|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |    |    |  | as a 'single-step on branches' flag rather than a 'single-step on instructions' flag. This will cause a debug exception to be posted when a taken branch occurs while TF is set.                                                                              |

| TR                 | 6  | RW |  | When set, branch trace messages are enabled. Upon detection of a branch, interrupt, or exception the processor sends a branch record to the system bus as a branch trace message (BTM).                                                                       |

| BTS                | 7  | RW |  | When set, the flag enables branch trace store (BTS) facilities to log BTMs to a memory buffer (the Branch Trace Store).                                                                                                                                       |

| BTINT              | 8  | RW |  | When set, the BTS facilities generate an interrupt when the BTS buffer is full. When clear, the BTS buffer behaves as a circular buffer and older records are overwritten.                                                                                    |

| BTS_OFF_OS         | 9  | RW |  | When set, BTMs will not be written to the system bus or the BTS when the CPL is equal to zero.                                                                                                                                                                |

| BTS_OFF_USR        | 10 | RW |  | When set, BTMs will not be written to the system bus or the BTS when the CPL is not equal to zero.                                                                                                                                                            |

| FRZ_LBRS_ON_PMI    | 11 | RW |  | When set, the LBR stack is frozen on a hardware PMI request. Software must explicitly re-enable the LBR capture mechanism.<br><br>Note: the freeze is currently triggered by counter overflow, and may result in freezing the LBR stack sooner than expected. |

| FRZ_PERFMON_ON_PMI | 12 | RW |  | When set, a PMI request clears each of the enable bits in the                                                                                                                                                                                                 |

|               |    |    |                                                                                                                                                                                                      |

|---------------|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |    |    | IA32_PERF_GLOBAL_CTRL MSR, disabling all event counting.<br>Software must explicitly re-enable the counters by setting the enable bits in the IA32_PERF_GLOBAL_CTRL register before exiting the ISR. |

| UNCORE_PMI_EN | 13 | RW | When set, this logical processor is enabled to receive an uncore counter overflow interrupt.                                                                                                         |

| SMM_FRZ       | 14 | RW | When set, event counters are disabled while the processor is in system management mode.                                                                                                              |

### 3.1.3. IA32\_PERF\_GLOBAL\_CTRL

This register globally controls the fixed and programmable counters. If a control bit in this register is clear, all other control register programming for the corresponding counter will be ignored and the counter will not count.

Counters that are disabled by this register cannot count, overflow, or subsequently generate overflow interrupts. It is possible that a disabled counter may generate a PEBS assist. This can occur as follows. While the counter is enabled it can overflow (to zero) and arm the PEBS hardware. The next event (the counter transitions from zero to one) will cause the PEBS assist to occur. At this point the PEBS assist will occur even if an intervening write to this register disables the counter.

Note that the state of the IA32\_PERF\_GLOBAL\_CTRL register is preserved across entry and exit to probe mode (halting with an ITP). Writes to this register during probe mode will be lost upon exit from probe mode.

Figure 3: IA32\_PERF\_GLOBAL\_CTRL MSR Definition

Table 5: IA32\_PERF\_GLOBAL\_CTRL Programming

| Bit                                                                | Bit Position | Access | Description                                                                                       |

|--------------------------------------------------------------------|--------------|--------|---------------------------------------------------------------------------------------------------|

| EN_PC0                                                             | 0            | RW     | Enable bit for programmable counter 0. If clear, disable the counter. If set, enable the counter. |

| EN_PC1                                                             | 1            | RW     | Enable bit for programmable counter 1. If clear, disable the counter. If set, enable the counter. |

| EN_PC2                                                             | 2            | RW     | Enable bit for programmable counter 2. If clear, disable the counter. If set, enable the counter. |

| EN_PC3                                                             | 3            | RW     | Enable bit for programmable counter 3. If clear, disable the counter. If set, enable the counter. |

| EN_FC0                                                             | 32           | RW     | Enable bit for fixed counter 0. If clear, disable the counter. If set, enable the counter.        |

| EN_FC1                                                             | 33           | RW     | Enable bit for fixed counter 1. If clear, disable the counter. If set, enable the counter.        |

| EN_FC2                                                             | 34           | RW     | Enable bit for fixed counter 2. If clear, disable the counter. If set, enable the counter.        |

| Software must read-modify-write or explicitly clear reserved bits. |              |        |                                                                                                   |

### 3.1.4. IA32\_PERF\_GLOBAL\_STATUS

This register indicates the overflow status of each of the fixed and programmable counters. The upper bits provide additional status information of the PerfMon facilities. A set bit indicates an overflow has occurred in the corresponding counter. Overflow status bits in this register are cleared by writing the IA32\_PERF\_GLOBAL\_OVF\_CTRL register.

Status bit indications in this register have no affect on interrupts or pending interrupts.

Figure 4: IA32\_PERF\_GLOBAL\_STATUS MSR Definition

Table 6: IA32\_PERF\_GLOBAL\_STATUS Programming

| Bit     | Bit Position | Access | Description                                                                                                                        |

|---------|--------------|--------|------------------------------------------------------------------------------------------------------------------------------------|

| OVF_PC0 | 0            | RO     | Indicates the overflow status of programmable counter 0. If this bit is clear no overflow occurred. If set then overflow occurred. |

| OVF_PC1 | 1            | RO     | Indicates the overflow status of programmable counter 1. If this bit is clear no overflow occurred. If set then overflow occurred. |

|                                                                    |    |    |                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------|----|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OVF_PC2                                                            | 2  | RO | Indicates the overflow status of programmable counter 2. If this bit is clear no overflow occurred. If set then overflow occurred.                                                                                                                                                                                                                                     |

| OVF_PC3                                                            | 3  | RO | Indicates the overflow status of programmable counter 3. If this bit is clear no overflow occurred. If set then overflow occurred.                                                                                                                                                                                                                                     |

| OVF_FC0                                                            | 32 | RO | Indicates the overflow status of fixed counter 0. If this bit is clear no overflow occurred. If set then overflow occurred.                                                                                                                                                                                                                                            |

| OVF_FC1                                                            | 33 | RO | Indicates the overflow status of fixed counter 1. If this bit is clear no overflow occurred. If set then overflow occurred.                                                                                                                                                                                                                                            |

| OVF_FC2                                                            | 34 | RO | Indicates the overflow status of fixed counter 2. If this bit is clear no overflow occurred. If set then overflow occurred.                                                                                                                                                                                                                                            |

| UNC_Ovf                                                            | 61 | RO | Indicates a counter in the uncore overflowed. Software must perform further queries to determine which specific counter overflowed.                                                                                                                                                                                                                                    |

| PEBS_Ovf                                                           | 62 | RO | Indicates that the PEBS buffer threshold was reached and microcode scheduled a performance interrupt to indicate this condition.                                                                                                                                                                                                                                       |

| CondChg                                                            | 63 | RO | Indicates that the state of the PerfMon hardware has changed. A change in this bit indicates the hardware has become available or unavailable. Software can execute CPUID leaf 0xA to confirm the availability of PerfMon hardware. This is a sticky bit, and must be explicitly cleared by writing to one the corresponding bit in the IA32_PERF_GLOBAL_OVF_CTRL MSR. |

| Software must read-modify-write or explicitly clear reserved bits. |    |    |                                                                                                                                                                                                                                                                                                                                                                        |

### 3.1.5. IA32\_PERF\_GLOBAL\_OVF\_CTRL

The IA32\_PERF\_GLOBAL\_OVF\_CTRL provides software the ability to clear status bits set in the IA32\_PERF\_GLOBAL\_STATUS register, described in the preceding

section. This is a write-only register. To clear overflow or condition change status in the global status register, software must write the corresponding bits in this register to binary one.

Figure 5: IA32\_PERF\_GLOBAL\_OVF\_CTRL MSR Definition

Table 7: IA32\_PERF\_GLOBAL\_OVF\_CTRL Programming

| Bit         | Bit Position | Access | Description                                                                                                    |

|-------------|--------------|--------|----------------------------------------------------------------------------------------------------------------|

| CLR_OVF_PC0 | 0            | W01    | Setting this bit will clear the status bit in the IA32_PERF_GLOBAL_STATUS register for programmable counter 0. |

| CLR_OVF_PC1 | 1            | W01    | Setting this bit will clear the status bit in the IA32_PERF_GLOBAL_STATUS register for programmable counter 1. |

| CLR_OVF_PC2 | 2            | W01    | Setting this bit will clear the status bit in the IA32_PERF_GLOBAL_STATUS register for programmable counter 2. |

| CLR_OVF_PC3 | 3            | W01    | Setting this bit will clear the status bit in the IA32_PERF_GLOBAL_STATUS register for programmable counter 3. |

|                                                                       |    |     |                                                                                                         |

|-----------------------------------------------------------------------|----|-----|---------------------------------------------------------------------------------------------------------|

| CLR_OVF_FC0                                                           | 32 | W01 | Setting this bit will clear the status bit in the IA32_PERF_GLOBAL_STATUS register for fixed counter 0. |

| CLR_OVF_FC1                                                           | 33 | W01 | Setting this bit will clear the status bit in the IA32_PERF_GLOBAL_STATUS register for fixed counter 1. |

| CLR_OVF_FC2                                                           | 34 | W01 | Setting this bit will clear the status bit in the IA32_PERF_GLOBAL_STATUS register for fixed counter 2. |

| CLR_UNC_Ovf                                                           | 61 | W01 | Setting this bit clears the UNC_Ovf status bit in the IA32_PERF_GLOBAL_STATUS register.                 |

| CLR_PEBS_Ovf                                                          | 62 | W01 | Setting this bit clears the PEBS_Ovf status bit in the IA32_PERF_GLOBAL_STATUS register.                |

| CLR_CondChg                                                           | 63 | W01 | Setting this bit clears the CondChg status bit in the IA32_PERF_GLOBAL_STATUS register.                 |

| Note: Writing any value other than '1' to these bits will be ignored. |    |     |                                                                                                         |

### 3.1.6. IA32\_FIXED\_CTR\_CTRL

This register controls the fixed counters, and determines whether these counters count in USR or SUP mode, or both, and whether these counters are enabled to generate performance interrupts.

Figure 6: IA32\_FIXED\_CTR\_CTRL MSR Definition

Table 8: IA32\_FIXED\_CTR\_CTRL Programming

| Bit        | Bit Position | Access | Description                                                                                                                                                                                        |

|------------|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTL_FC0    | 1:0          | RW     | See Table 9.                                                                                                                                                                                       |

| AnyThr_FC0 | 2            | RW     | If clear the counter will count only events which occur on its own thread. If set, the counter will count events that occur on all threads in the core containing this thread (logical processor). |

| INT_FC0    | 3            | RW     | When set counter 0 is enabled to generate overflow interrupts. Interrupts are disabled if clear.                                                                                                   |

| CTL_FC1    | 5:4          | RW     | See Table 9.                                                                                                                                                                                       |

| AnyThr_FC1 | 6            | RW     | If clear the counter will count only events which occur on its own thread. If set, the counter will count events that occur on all threads in the core containing this thread (logical processor). |

|                                                                    |     |    |                                                                                                                                             |

|--------------------------------------------------------------------|-----|----|---------------------------------------------------------------------------------------------------------------------------------------------|

| INT_FC1                                                            | 7   | RW | When set counter 1 is enabled to generate overflow interrupts. Interrupts are disabled if clear.                                            |

| CTL_FC2                                                            | 9:8 | RW | See Table 9.                                                                                                                                |

| AnyThr_FC2                                                         | 10  | RW | If clear the counter will count only events which occur on its own thread. If set, the counter will count events that occur on all threads. |

| INT_FC2                                                            | 11  | RW | When set counter 2 is enabled to generate overflow interrupts. Interrupts are disabled if clear.                                            |

| Software must read-modify-write or explicitly clear reserved bits. |     |    |                                                                                                                                             |

Table 9: Summary of CTL bit Programming for Fixed Counters

| CTL_FCx Bit Field <sup>1</sup> | Description                                                                                  |

|--------------------------------|----------------------------------------------------------------------------------------------|

| 00b                            | Disable the counter.                                                                         |

| 01b                            | Count events when the logical processor is executing in privilege level 0.                   |

| 10b                            | Count events when the logical processor is executing in privilege levels one, two, or three. |

| 11b                            | Count events when the logical processor is executing at any privilege level.                 |

<sup>1</sup> CTL\_FCO, CTL\_FC1, or CTL\_FC2.

The all/my thread control bit (AnyThr\_FCx) is always readable and writeable, even when Hyper-Threading Technology is disabled on the NHM processor. If Hyper-Threading Technology is disabled then setting these bits will have no effect.

## 3.2. Programmable Counter Control Registers

This section describes the control registers for the four programmable counters.

### 3.2.1. PerfEvtSelX

The PerfEvtSelX registers control the four programmable counters. Using these control registers, software can select the event to be counted, and the constraints under which those events are counted. Each counter must be locally enabled by this register, as well as globally enabled, in order to operate correctly.

The layout of this register is similar to previous Intel Core Architecture implementations. However, the pin control (PC) bit is now reserved. Also, NHM is the first Intel Core Architecture processor that implements SMT. NHM implements an additional event modifier bit, **AnyThr**, which controls counting events for the counter's logical processor only, or for all logical processors in the core which contains the counter.

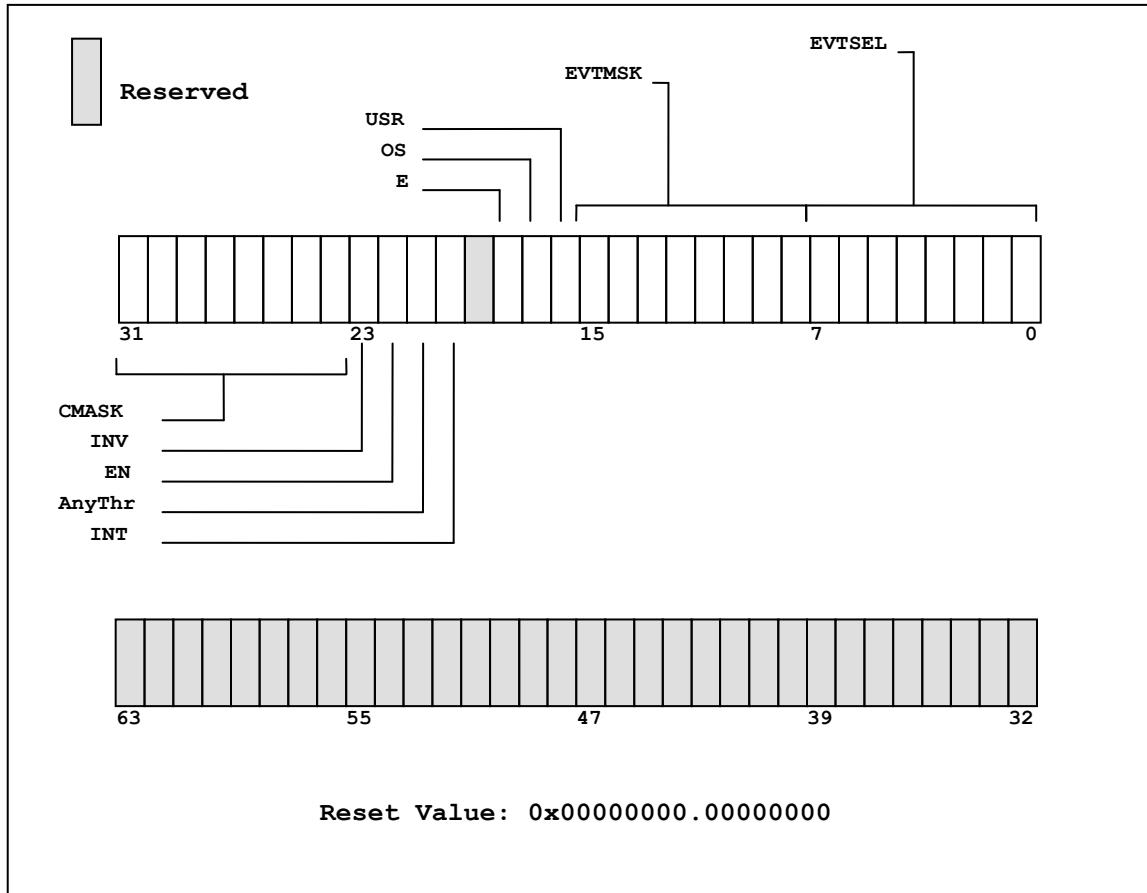

Figure 7: PerfEvtSelX MSR Definition

Table 10: PerfEvtSelX Programming

| Bit    | Bit Position | Access | Description                                                                                                                                                          |

|--------|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EVTSEL | 7:0          | RW     | Selects the event logic unit used to detect micro-architectural conditions.                                                                                          |

| EVTMSK | 15:8         | RW     | Condition qualifiers for the event selection logic specified in the EVTSEL field.                                                                                    |

| USR    | 16           | RW     | When set, indicates that the event specified by bit fields EVTSEL and EVTMSK is counted only when the logical processor is operating and privilege level 1, 2, or 3. |

|                                                                    |       |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------|-------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OS                                                                 | 17    | Rw | When set, indicates that the event specified by bit fields EVTSEL and EVTMSK is counted only when the logical processor is operating and privilege level 0.                                                                                                                                                                                                                                                                                                                                                                           |

| E                                                                  | 18    | Rw | When set, causes the counter to increment when a deasserted to asserted transition occurs for the conditions that can be expressed by any of the fields in this register.                                                                                                                                                                                                                                                                                                                                                             |

| INT                                                                | 20    | Rw | When set, the logical processor generates an exception through its local APIC on counter overflow. Counters only count up, and interrupts are generated on a transition from maximum count to zero. There will be some latency from the time the counter triggers the interrupt until the interrupt handler is invoked.                                                                                                                                                                                                               |

| AnyThr                                                             | 21    | Rw | When clear, the counter increments only when event conditions are satisfied in its logical processor. When Set, the counter increments when event conditions are satisfied for any logical processor in the core in which this counter resides.                                                                                                                                                                                                                                                                                       |

| EN                                                                 | 22    | Rw | When clear, this counter is locally disabled. When set, this counter is locally enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INV                                                                | 23    | Rw | When clear, the CMASK field is interpreted as greater than or equal to. When set, the CMASK field is interpreted as less than.                                                                                                                                                                                                                                                                                                                                                                                                        |

| CMASK                                                              | 31:24 | Rw | <p>When this field is clear, it has no effect on counting. When set to a value other than zero, the logical processor compares this field to the event counts on each core clock cycle. If INV is clear and the event counts are greater than or equal to this field, the counter is incremented by one. If INV is set and the event counts are less than this field, the counter is incremented by one. Otherwise the counter is not incremented.</p> <p>Bits [31:29] are reserved to 0. Software must write these bits to zero.</p> |

| Software must read-modify-write or explicitly clear reserved bits. |       |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

The all/my thread control bit (AnyThr) is always readable and writeable, even when Hyper-Threading Technology is disabled on the NHM processor. If Hyper-Threading Technology is disabled then setting this bit will have no effect.

### 3.3. Counter Registers

This section describes the three fixed and four programmable counter registers.

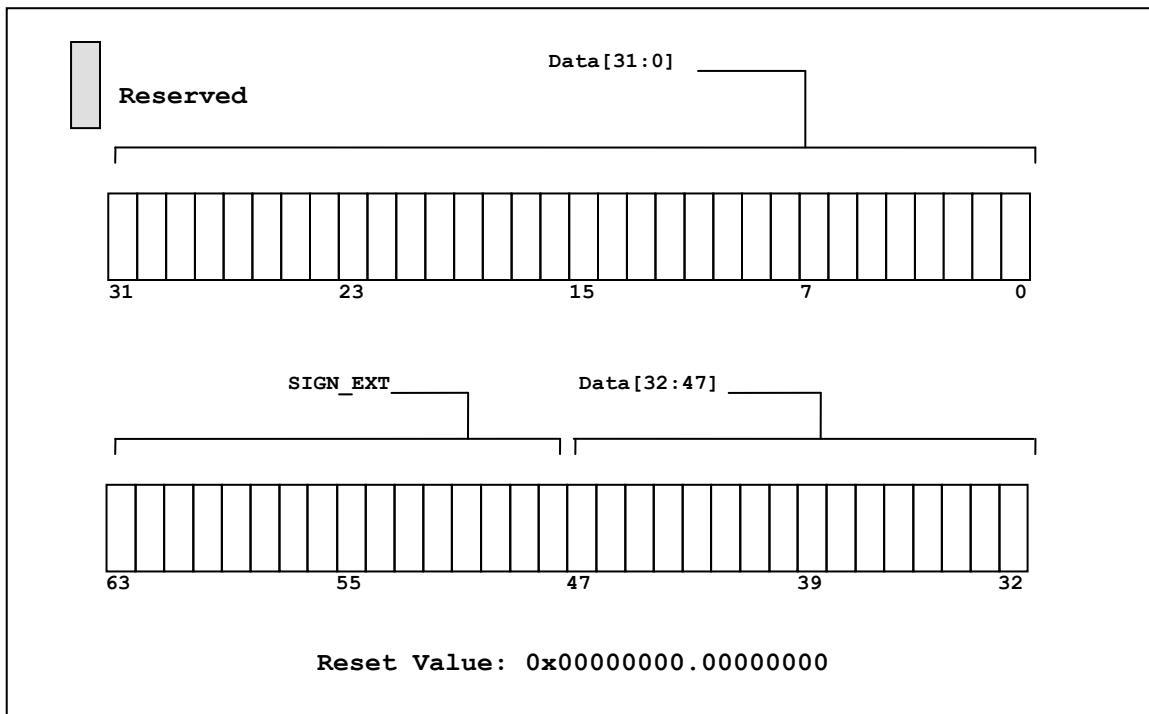

#### 3.3.1. `PERF_FIXED_CTRX` and `IA32_PMCX` Registers

Each counter register is 48-bits long. Counter registers can be cleared, or pre-loaded with count values as desired. This latter method is often used to set the point at which the counter will overflow, which is useful in event-based sampling. When writing the programmable counters using the `wrmsr` instruction, bits 32 through 47 cannot be written directly. They are sign-extended based on the value written to bit 31 of the counter register. When using the PEBS facility to re-load the programmable counters the entire 48-bit value is loaded from the DS Buffer Management area without any sign extension.

Previous implementations of Intel Core Architecture contained counters which were limited to 40 bits in length. Nehalem implements counters 48 bits in length. Counter width can be enumerated using the features in the `CPUD` instruction. See section 4.2 for more information.

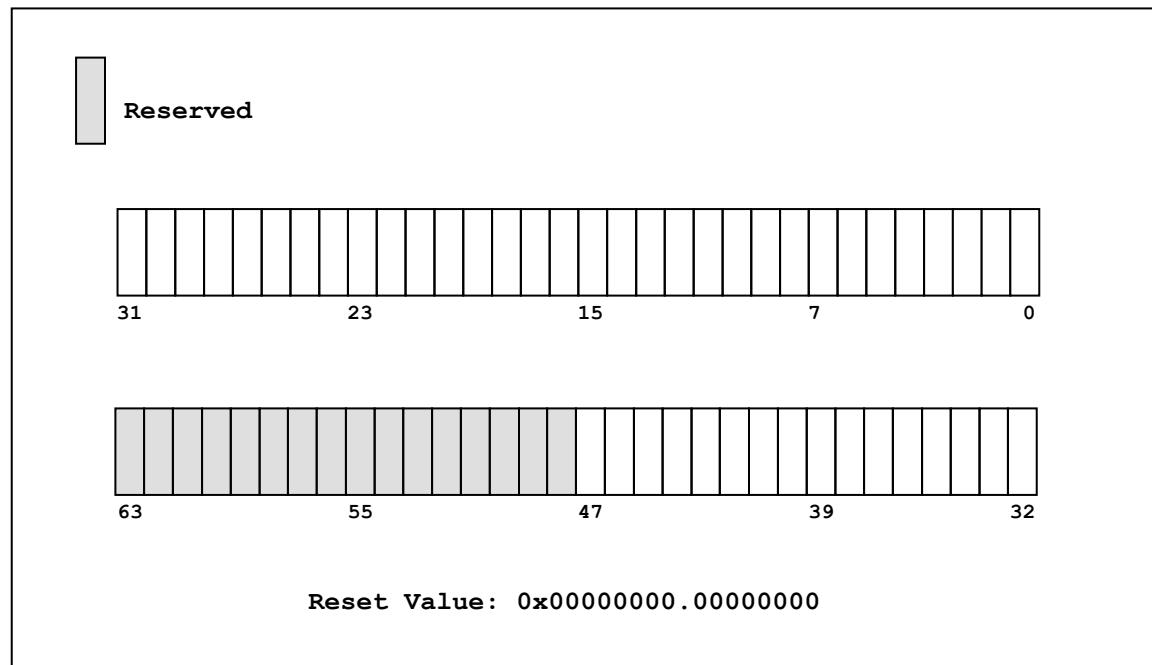

Figure 8: `PERF_FIXED_CTRX` and `IA32_PMCX` MSR Definition

### 3.4. Off-core Response Event Programming

NHM provides the ability to program two counters to report off-core response counts. These counters are programmed to detect the occurrence of off-core data requests that return with a particular response. To enable these events, software programs the PerfEvtSelX register as shown in the following table. This capability is not available in processors previous to NHM.

Table 11: Offcore Response Events Encoding

| Event Encoding<br>PerfEvtSelX[7:0] | Event Mask<br>PerfEvtSelX[15:8] | Extra MSR to<br>Program  |

|------------------------------------|---------------------------------|--------------------------|

| 0xB7                               | 0x01                            | 0x1A6<br>(OFFCORE_RSP_0) |

| 0xBB                               | 0x01                            | 0x1A7<br>(OFFCORE_RSP_1) |

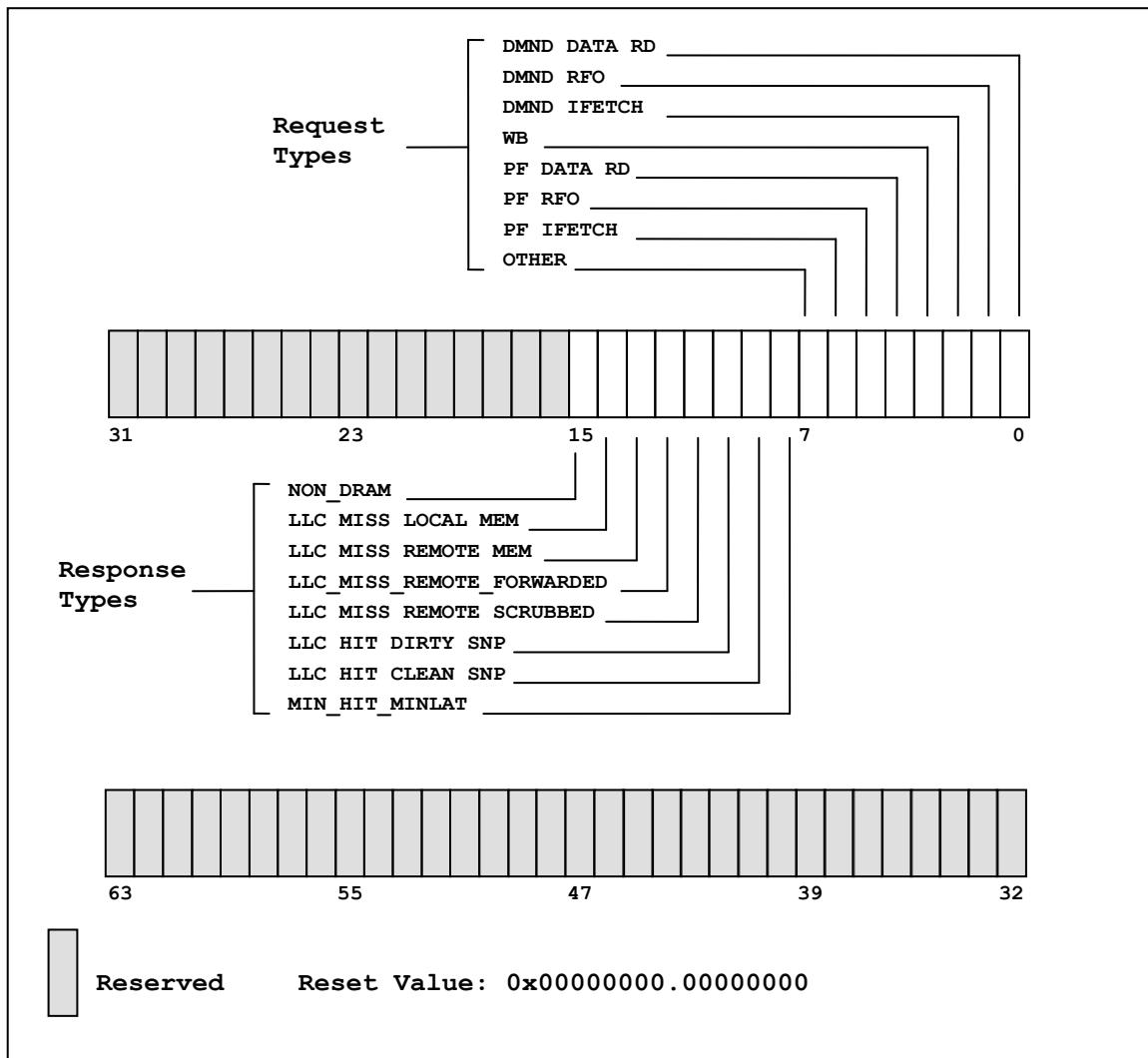

After programming the appropriate event in the PerfEvtSelX register, software must also program the “extra” register as shown in the figure below. To properly program this extra register, software must set at least one request type and one response type bit. Otherwise, the event count reported will be zero. It is legal and useful to set multiple request and response type bits in order to obtain various classes of off-core response events.

Figure 9: OFFCORE\_RSP\_X MSR Definition

Table 12: OFFCORE\_RSP\_X Event Programming

| Bit          | Bit Position | Access | Description                                                                                                                                                                                                     |

|--------------|--------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMND_DATA_RD | 0            | RW     | Counts the number of demand and DCU prefetch data reads of full and partial cachelines as well as demand data page table entry cacheline reads. Does not count MLC data read prefetches or instruction fetches. |

| DMND_RFO     | 1            | RW     | Counts the number of demand and DCU prefetch read for ownership (RFO) requests                                                                                                                                  |

|                    |   |    |  |                                                                                                                                                                                                                                                                                    |

|--------------------|---|----|--|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |   |    |  | generated by a write to data cacheline. Does not count MLC RFO prefetches.                                                                                                                                                                                                         |

| DMND_IFETCH        | 2 | RW |  | Counts the number of demand and DCU prefetch instruction cacheline reads. Does not count MLC code read prefetches.                                                                                                                                                                 |

| WB                 | 3 | RW |  | Counts the number of writeback (modified to exclusive) transactions.                                                                                                                                                                                                               |

| PF_DATA_RD         | 4 | RW |  | Counts the number of data cacheline reads generated by the MLC prefetchers.                                                                                                                                                                                                        |

| PF_RFO             | 5 | RW |  | Counts the number of read for ownerships (RFO) requests generated by the MLC prefetchers.                                                                                                                                                                                          |

| PF_IFETCH          | 6 | RW |  | Counts the number of code reads generated by the MLC prefetchers.                                                                                                                                                                                                                  |

| OTHER              | 7 | RW |  | Counts these transactions: read code cacheline generated by monitor instruction, LLC invalidate, I/O, Write data partial or full cacheline, USWC stores and non-temporal stores, cache line flush instruction generated by a cache line flush, fence, lock, unlock, or split-lock. |

| UNCORE_HIT         | 8 | RW |  | LLC Hit: local or remote home requests that hit last level cache in the uncore with no coherency actions required (snooping).                                                                                                                                                      |

| OTHER_CORE_HIT_SNP | 9 | RW |  | LLC Hit: local or remote home requests that hit the last level cache and was serviced by another core with a cross core snoop where no modified copies were found. (clean).                                                                                                        |

|                   |    |    |                                                                                                                                                                                                                                            |

|-------------------|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTHER_CORE_HITM   | 10 | RW | LLC Hit: local or remote home requests that hit the last level cache and was serviced by another core with a cross core snoop where modified copies were found. (HITM)                                                                     |

| REMOTE_CACHE_HITM | 11 | RW | LLC Miss: local or remote home requests that missed the last level cache and was serviced by forwarded data following a cross package snoop where a modified copy was found and coherency actions were taken. (Not supported until WSM-T0) |

| REMOTE_CACHE_FWD  | 12 | RW | LLC Miss: local homed requests that missed the last level cache and was serviced by forwarded data following a cross package snoop where no modified copies found. (Remote home requests are not counted).                                 |

| REMOTE_DRAM       | 13 | RW | LLC Miss: remote home requests that missed the last level cache and were serviced by remote DRAM.                                                                                                                                          |

| LOCAL_DRAM        | 14 | RW | LLC Miss: local home requests that missed the last level cache and were serviced by local DRAM.                                                                                                                                            |

| IO_CSR_MMIO       | 15 | RW | None: Non-DRAM requests that are serviced by IOH.                                                                                                                                                                                          |

As an example, assume software wishes to count demand data read requests that are satisfied by the LLC. To accomplish this, software could program the PMU registers as shown in the table below.

Table 13: Offcore Response Programming Example

| Register    | MSR Address | Programming | Comments                    |

|-------------|-------------|-------------|-----------------------------|

| PerfEvtSel0 | 0x186       | 0x4301B7    | Enable counting of off-core |

|               |       |      |                                                                                                                                              |

|---------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

|               |       |      | responses occurring in user and supervisor code.                                                                                             |

| OFFCORE_RSP_0 | 0x1A6 | 0x17 | Demand data reads satisfied by the LLC. Data could be owned by this core, or forwarded as clean or modified by another core on this package. |

| IA32_PMC0     | 0xC1  | --   | This counter will accumulate the event counts.                                                                                               |

## 3.5. The PEBS Facility

This section details the PEBS facility as implemented in the NHM processor. The PEBS facility allows software to profile workload behavior relative to a limited set of events. Event counters are preloaded so they will reach an overflow condition after the occurrence of a predefined number of events. On overflow of a PEBS-enabled counter, the PEBS facility is armed. At the occurrence of the next precise (PEBS) event, the processor will take an assist and capture machine state in a predefined memory buffer.

### 3.5.1. IA32\_PEBS\_ENABLE

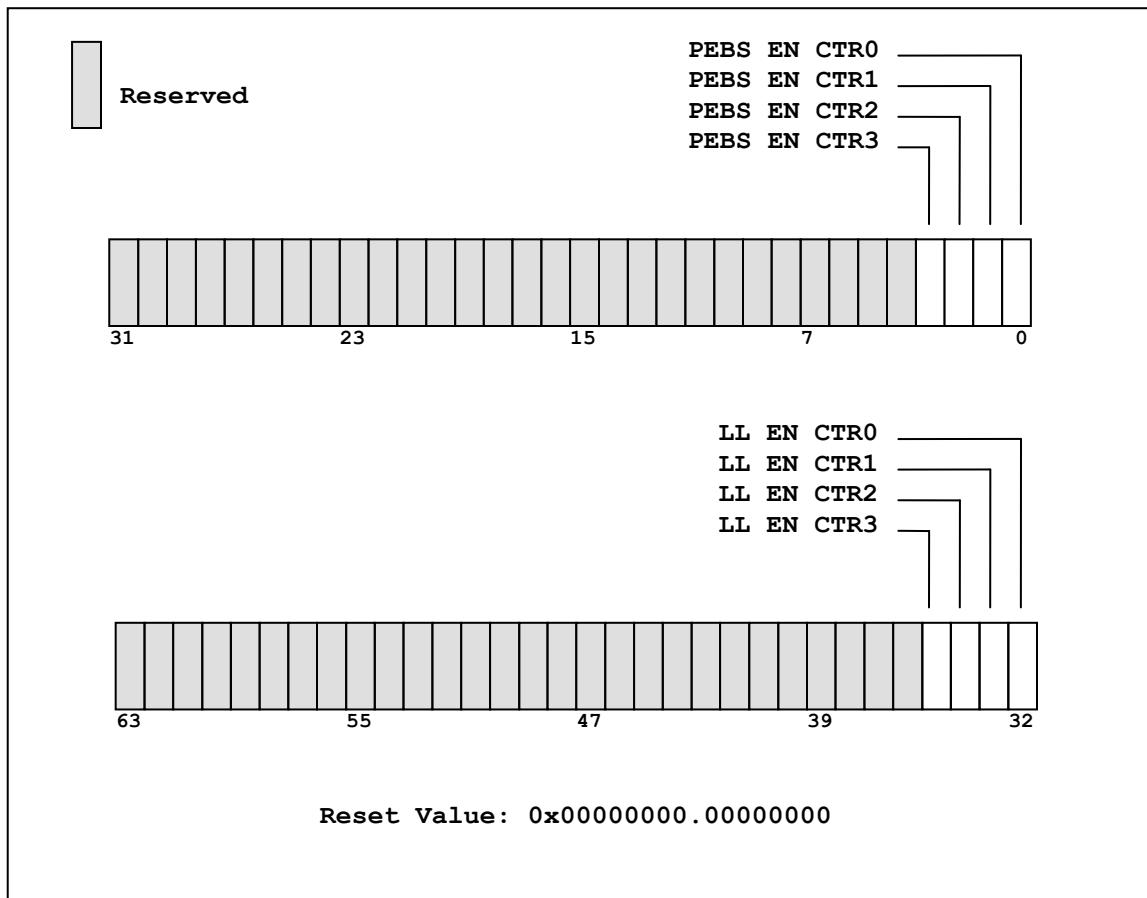

Counters can be configured to periodically capture machine state and load latency information as shown in Table 14. The IA32\_PEBS\_ENABLED register is used to enable this facility.

Previous implementations of Intel Core Architecture supported the PEBS facility in only one counter (counter 0). NHM supports PEBS mode in all four programmable counters. The ability to capture load latency information is also new to NHM and will be discussed in a subsequent section.

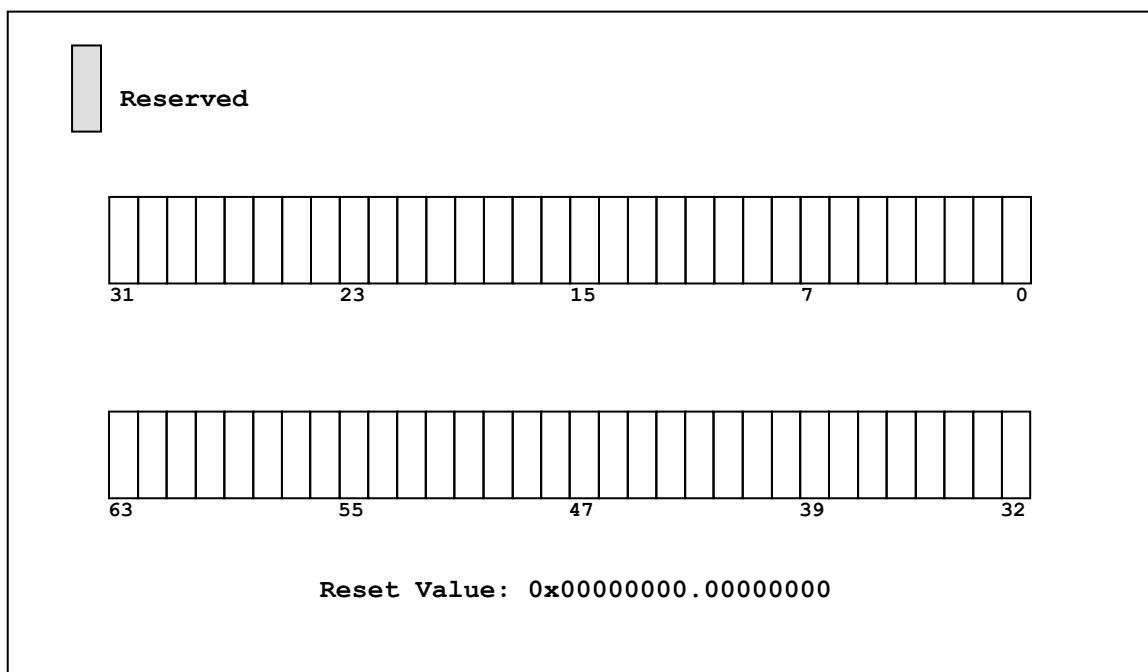

Figure 10: IA32\_PEBS\_ENABLE MSR Definition

Table 14: IA32\_PEBS\_ENABLE Programming

| Bit          | Bit Position | Access | Description                                            |

|--------------|--------------|--------|--------------------------------------------------------|

| PEBS_EN_CTR0 | 0            | RW     | Enable counter 0 to capture machine state on overflow. |

| PEBS_EN_CTR1 | 1            | RW     | Enable counter 1 to capture machine state on overflow. |

| PEBS_EN_CTR2 | 2            | RW     | Enable counter 2 to capture machine state on overflow. |

| PEBS_EN_CTR3 | 3            | RW     | Enable counter 3 to capture machine state on overflow. |

| LL_EN_CTR0   | 32           | RW     | Enable counter 0 to capture load latency information.  |